Область техники

Настоящее изобретение относится к устройству и способу итеративного декодирования для системы мобильной связи и, в частности, касается устройства и способа для нормализации значения метрики, накопленного в компонентном декодере итеративного декодера в системе мобильной связи.

Уровень техники

В целом итеративное декодирование используется в таких системах мобильной связи, как IMT-2000 (или системах множественного доступа с кодовым разделением каналов МДКР-2000 и UMTS), в которых применяется турбокод. Итеративное декодирование используется также в системах дальней космической связи и системах спутниковой связи, где применяются каскадные сверточные коды, каскадные блочные коды или композиционные коды. Техническая область итеративного декодирования связана с так называемыми "мягкими" (не строго определенными) решениями и оптимальными характеристиками кода с исправлением ошибок.

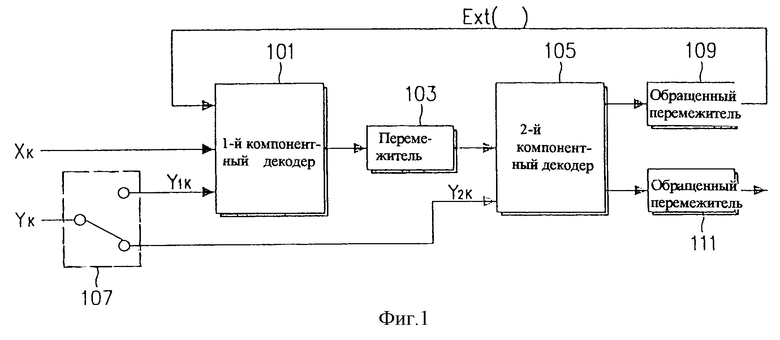

На фиг.1 показан известный итеративный декодер, включающий два компонентных декодера. Согласно фиг.1 первый компонентный декодер 101 принимает сигналы Хк систематического кода, первый сигнал контроля по четности Y1к, получаемый от демультиплексора 107 (который демультиплексирует входные сигналы контроля по четности Yк) и первый внешний информационный сигнал. Первый компонентный декодер 101 выполняет декодирование полученных сигналов, выдавая первично декодированный сигнал, связанный с результатами декодирования. Этот сигнал состоит из составляющей Хк сигналов систематического кода и второй внешней информационной составляющей. Перемежитель 103 выполняет перемежение первично декодированного сигнала. Второй компонентный декодер 105 получает первично декодированный сигнал, поступающий с выхода перемежителя 103, и второй сигнал контроля по четности Y2к, получаемый от демультиплексора 107. Второй компонентный декодер 105 декодирует полученные первично декодированные сигналы и второй сигнал контроля по четности Y2к, выдавая вторично декодированный сигнал на обращенный перемежитель 111. Далее второй компонентный декодер 105 через обращенный перемежитель 109 подает внешнюю информационную составляющую на первый компонентный декодер 101.

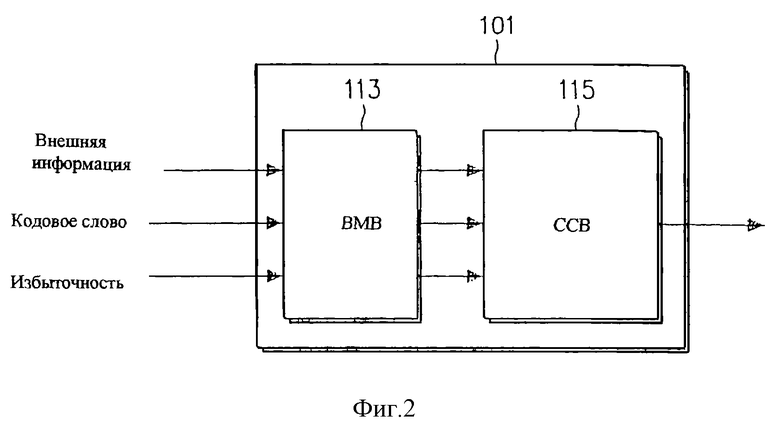

Как показано на фиг.2, первый компонентный декодер включает блок 113 вычисления метрик ветвления (ВМВ) для вычисления метрик ветвления и блок 115 суммирования-сравнения-выбора (ССВ) для вычисления метрик и выполнения сравнения в каждом состоянии для выбора пути с меньшим количеством ошибок.

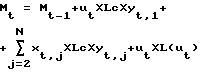

В общем случае указанный итеративный декодер вычисляет значение метрики Mt согласно приведенному ниже уравнению (1).

где Mt - накопленное значение метрики за время t;

Ut - кодовое слово для систематического бита, кодовое слово для каждого бита Хк;

xt,j - кодовое слово для избыточного бита;

yt,j - полученное значение для канала (систематическое + избыточное);

Lc - значение надежности канала, и

L(ut) - априорное значение надежности за время t.

Из уравнения (1) следует, что при каждом вычислении метрики значение метрики Мt непрерывно растет благодаря второму, третьему и четвертому членам. При аппаратной реализации значения метрик должны лежать в пределах заданного диапазона, чтобы избежать проблемы переполнения. Однако главным назначением итеративного декодера является выполнение итеративного декодирования с целью улучшения характеристик декодирования (то есть частоты ошибок по битам (ЧОБ) или частоты ошибок по кадрам (ЧОК)). Таким образом, в процессе выполнения итеративным декодером своей функции после ряда последовательных итераций значения метрик могут увеличиться и выйти за пределы заданного диапазона. Следовательно, если при разработке аппаратной части декодера предполагается задание определенного диапазона для значений метрик, значение метрик может превысить заданный диапазон, и возникнет проблема переполнения.

Сущность изобретения

Следовательно, задачей настоящего изобретения является создание устройства и способа для нормализации значения метрики компонентного декодера, причем при превышении всеми накопленными значениями метрик для текущих состояний некоторого порогового значения, эти накопленные значения метрик нормализуются до заданного уровня после вычитания из них заданного значения.

Для достижения вышеуказанного результата предлагается декодер, использующий изменение множества значений метрик на множестве временных отрезков. Декодер включает схему принятия решения, которая формирует сигнал решения, когда все значения метрик превысили заранее установленное значение. Вычитатель вычитает это заранее установленное значение из значений метрик в ответ на сигнал решения, чтобы нормализовать значения метрик. Схема принятия решения включает множество запоминающих устройств для запоминания соответствующих значений метрик с заранее установленным количеством битов. Логический элемент И-НЕ формирует сигнал решения ("1", или сигнал высокого уровня), когда все значения самых старших битов (ССБ), предусмотренных в соответствующих запоминающих устройствах, равны "1" (высокий уровень). Вычитатель устанавливает в ноль ССБ в каждом запоминающем устройстве, когда логический элемент И-НЕ выдает сигнал решения высокого уровня, в результате чего из каждого значения метрики вычитается заранее установленная величина.

Краткое описание чертежей

Вышеуказанные и другие задачи, признаки и преимущества настоящего изобретения поясняются в последующем подробном описании, иллюстрируемом чертежами, на которых представлено следующее:

фиг. 1 - блок-схема, показывающая итеративный декодер, содержащий два компонентных декодера;

фиг.2 - подробная блок-схема, показывающая компонентные декодеры по фиг. 1;

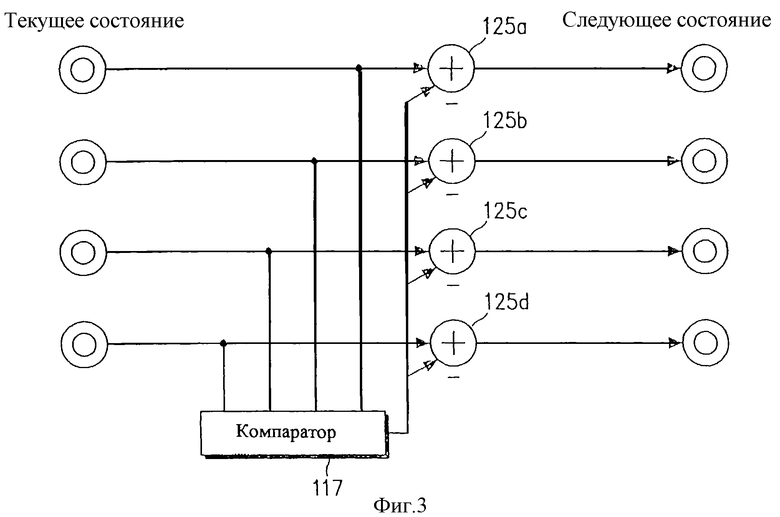

фиг. 3 - схема, иллюстрирующая операции ССВ компонентного декодера, который имеет устройство нормализации значений метрик в блоке ССВ компонентного декодера, согласно первому варианту настоящего изобретения;

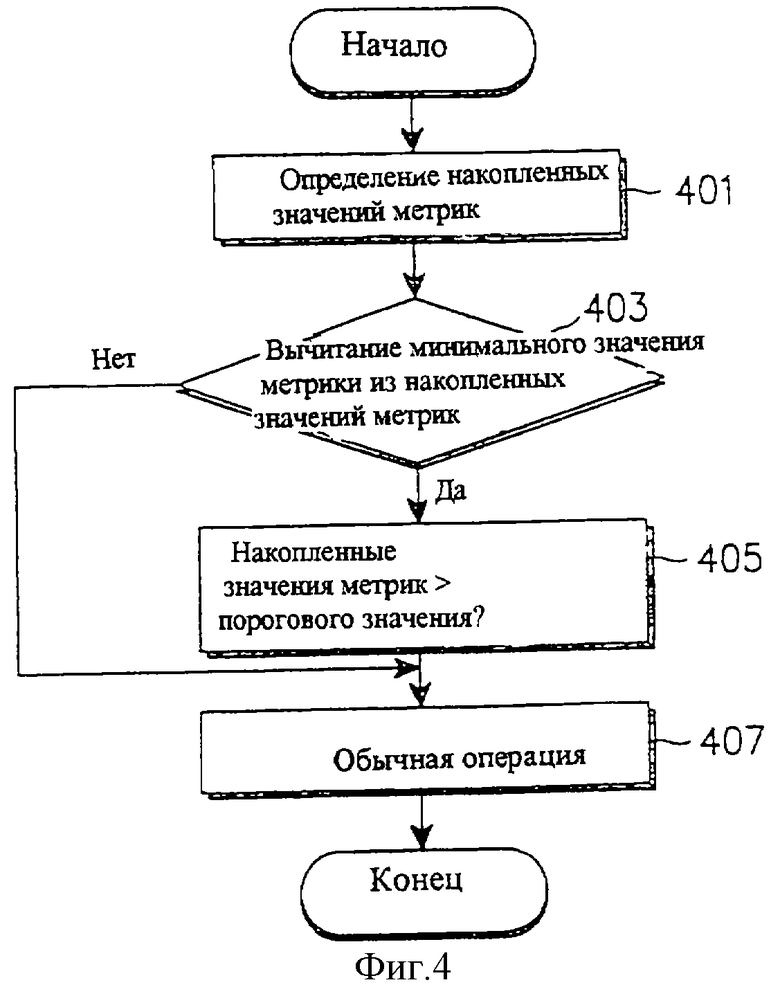

фиг. 4 - блок-схема, показывающая процедуру нормализации значений метрик согласно первому варианту настоящего изобретения;

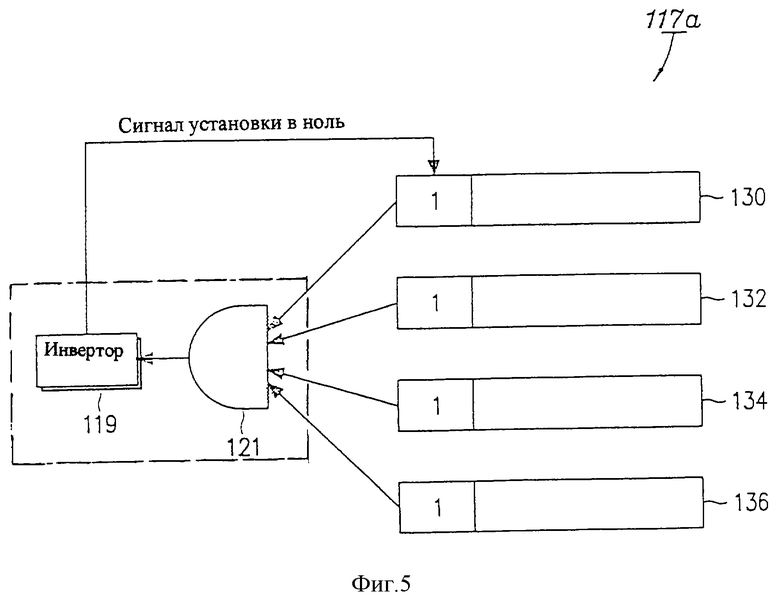

фиг. 5 - схема, иллюстрирующая операции ССВ компонентного декодера, который имеет устройство нормализации значений метрик в блоке ССВ компонентного декодера, согласно второму варианту настоящего изобретения;

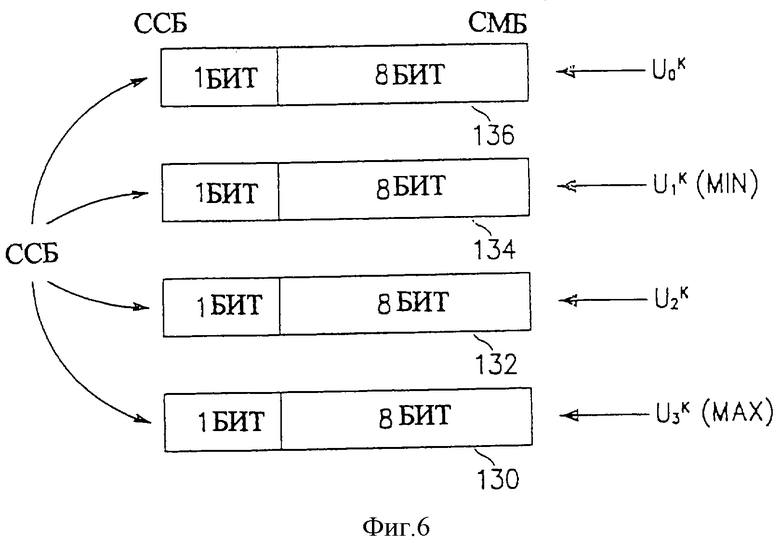

фиг. 6 - схема, где показан формат запоминающего устройства для значений метрик, для нормализации значений метрик согласно второму варианту настоящего изобретения;

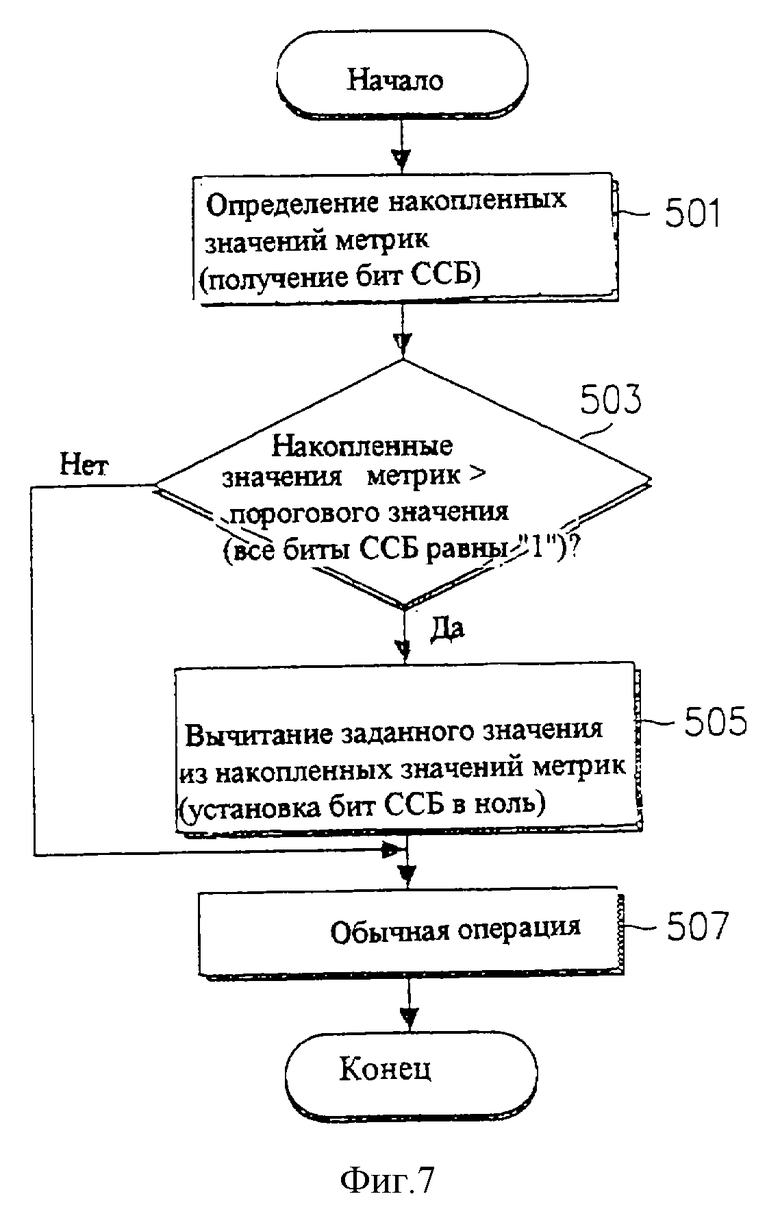

фиг. 7 - блок-схема, иллюстрирующая процедуру нормализации значений метрик согласно второму варианту настоящего изобретения;

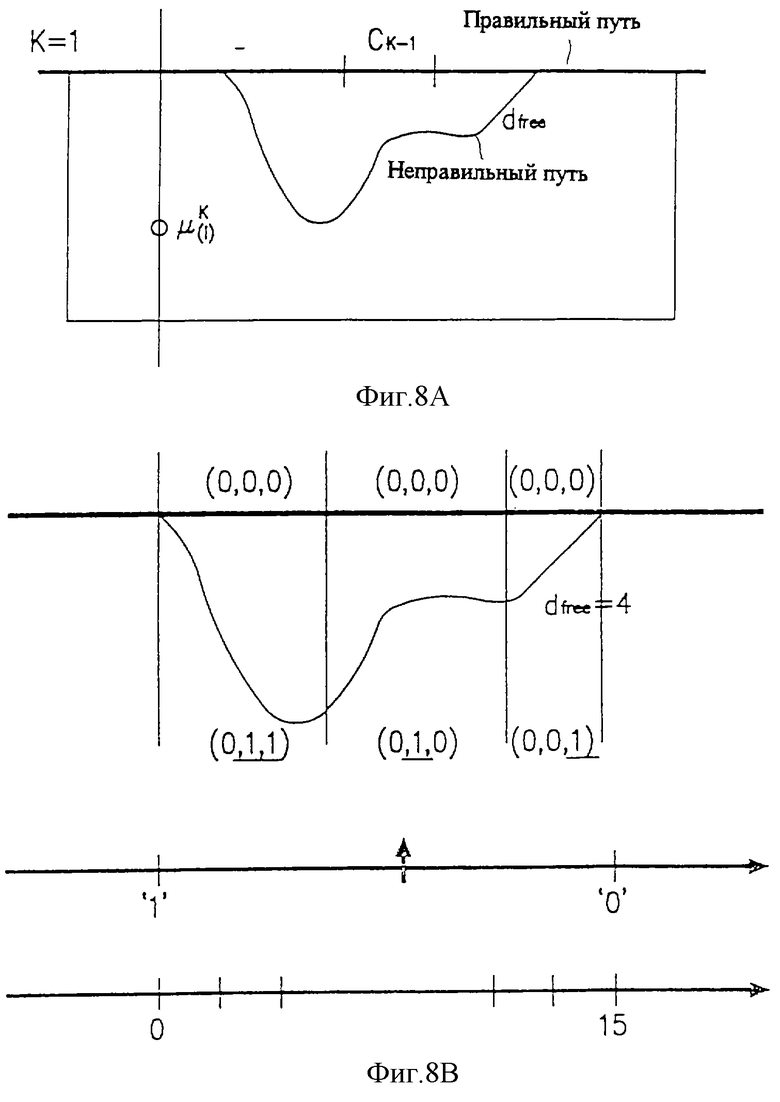

фиг. 8А и 8В - диаграммы, иллюстрирующие правильный путь, неправильный путь и разность путей, а также схему квантования для кодовых символов;

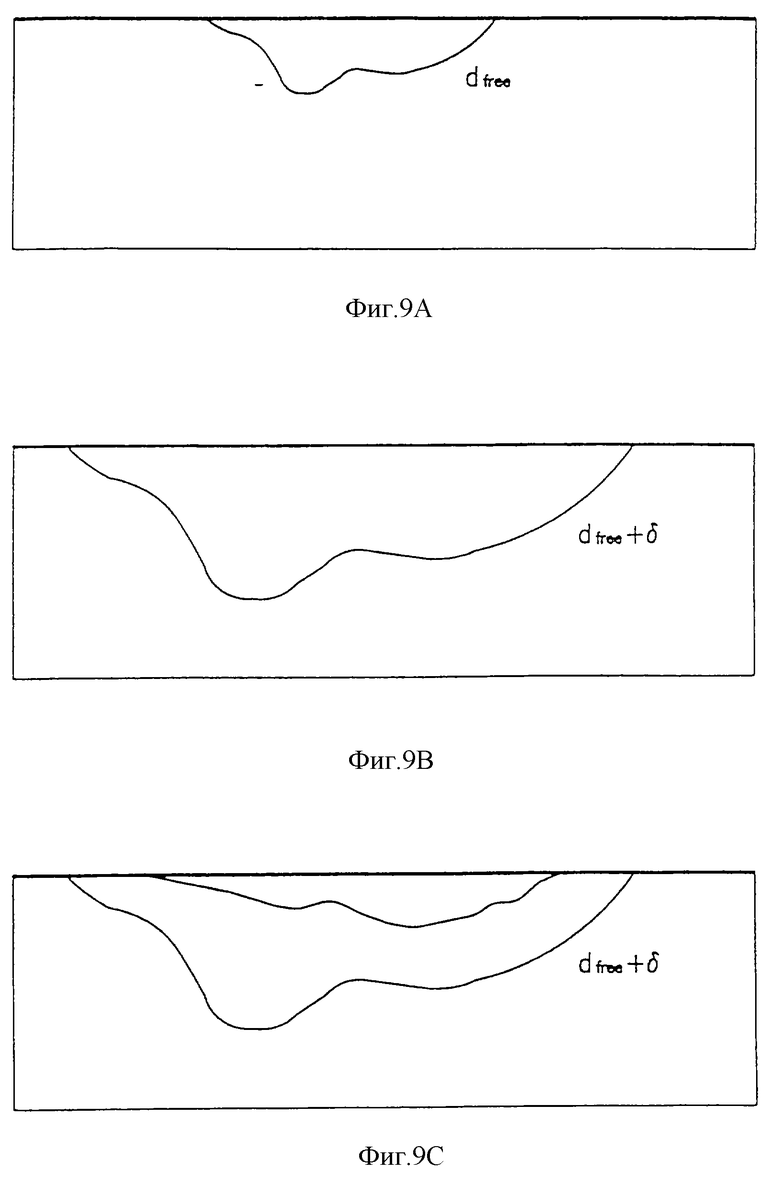

фиг. 9А-9С - диаграммы, иллюстрирующие правильный путь и неправильный путь в соответствии с отношением сигнал-шум; и

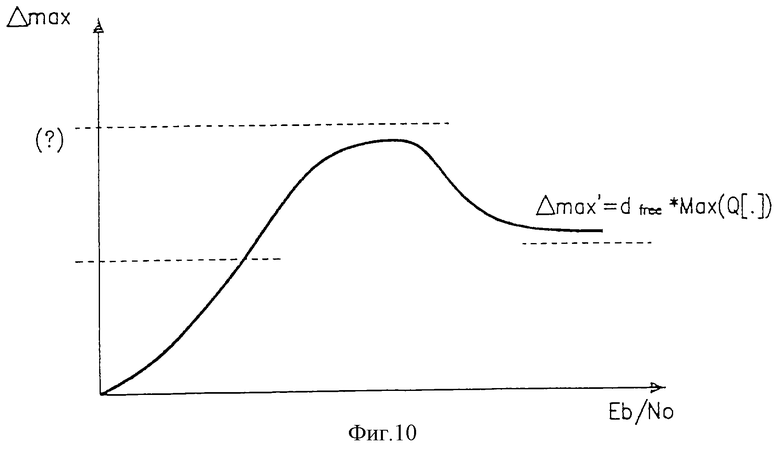

фиг. 10 - диаграмма, показывающая значение Δmax в состоянии насыщения в зависимости от отношения энергии (сигнала) к мощности шума Eb/No.

Подробное описание предпочтительного варианта осуществления изобретения

ССВ для компонентного декодера согласно настоящему изобретению нормализует значения метрик после вычитания из них заданного значения, когда значения метрик превышают пороговое значение.

Есть два способа для нормализации накопленных значений метрик согласно настоящему изобретению. Согласно первому способу накопленные значения метрик нормализуются с использованием минимального накопленного значения метрики, когда одно из накопленных значений метрик соответствующих состояний превышает пороговое значение. Согласно второму способу накопленные значения метрик нормализуются с использованием заранее установленного значения, когда все накопленные значения метрик превышают пороговое значение.

Нормализация для ССВ по настоящему изобретению может быть использована взамен нормализации для блока ССВ 115 итеративного декодера 101, описанного выше в связи с фиг.2.

А. Первый вариант

Далее со ссылками на фиг.3 описывается первый вариант осуществления изобретения. На фиг.3 показана структура блока ССВ, имеющего устройство нормализации значений метрик для кодового ограничения К=3 согласно первому варианту настоящего изобретения.

Ниже со ссылками на фиг.3 описано устройство нормализации значений метрик. На фиг.3 показаны четыре "текущих состояния", каждое из которых имеет значение метрики. При К=3 количество сдвиговых регистров для значений метрик равно 2, а количество возможных состояний 4. Компаратор 117, имеющий пороговое значение, определяет значение метрики для каждого состояния. Когда все определенные значения метрик превышают пороговое значение, компаратор 117 выдает заданное значение на сумматоры 125а - 125d, причем каждый сумматор подсоединен между одним текущим состоянием и одним следующим состоянием. Затем в сумматорах 125а - 125d из накопленных значений метрик для текущих состояний вычитается заданное значение, а полученные в результате значения выдаются в следующие состояния. В данном описании термин "накопленные значения метрик текущего состояния" используется взамен термина "значения метрик текущего состояния" и наоборот, чтобы подчеркнуть тот факт, что значения метрик для текущего состояния при последовательных вычислениях метрик накапливаются.

На фиг. 4 показана процедура для нормализации значений метрик согласно первому варианту настоящего изобретения. Согласно фиг.4 компаратор 117 на этапе 401 определяет значения метрик для четырех текущих состояний. После определения значений метрик компаратор 117 на этапе 403 проверяет, превышает ли по меньшей мере одно из определенных накопленных значений метрик пороговое значение. Если ни одно из накопленных значений метрик не превышает пороговое значение, то компаратор 117 переходит на этап 407 для выполнения обычной операции ССВ. Если по меньшей мере одно из накопленных значений метрик превышает пороговое значение, то компаратор 117 на этапе 405 выдает на сумматоры 125а-125d минимальное из четырех обнаруженных накопленных значений метрик. Затем в сумматорах 125а-125d из всех четырех накопленных значений метрик вычитается минимальное накопленное значение метрики, а затем выполняется переход в следующие состояния. После этого, как показано на этапе 407, декодер переходит к выполнению обычной операции ССВ.

В. Второй вариант

Ниже описывается второй вариант осуществления изобретения.

На фиг.5 показана структура блока нормализации ССВ согласно второму варианту настоящего изобретения. Согласно фиг.5 компаратор включает в себя множество запоминающих устройств 130, 132, 134 и 136 для запоминания накопленных значений метрик соответствующих состояний, логический элемент И 121 для определения того, все ли накопленные значения метрик, запомненные в запоминающих устройствах 130, 132, 134 и 136, превышают пороговое значение, и инвертор 119 для установки в ноль самого старшего бита (ССБ) соответствующих запоминающих устройств 130, 132, 134 и 136 в ответ на сигнал высокого уровня, выдаваемый логическим элементом И 121.

Формат запоминающих устройств описан со ссылками на фиг.6. Здесь предполагается, что каждое накопленное значение метрики u0 k, u1 k, u2 k, u3 k имеет 8 битов на выборку плюс один дополнительный бит для предотвращения переполнения накопленного значения метрики. Таким образом, накопленное значение метрики имеет всего 9 битов на выборку. Как показано на фиг.5, логический элемент И 121 получает девятый бит, который является самым старшим битом (ССБ) запоминающих устройств 130, 132, 134 и 136, и формирует выходной сигнал высокого уровня, когда все входные сигналы равны "1". То есть, когда ни один из ССБ запоминающих устройств 130, 132, 134 и 136 не равен "1", логический элемент И 121 не формирует выходной сигнал (сигнал низкого уровня). Когда все ССБ из запоминающих устройств имеют высокий уровень или "1", логический элемент И 121 формирует сигнал высокого уровня. Когда логический элемент И 121 выдает сигнал высокого уровня, инвертор 119 выдает сигнал установки в ноль бит ССБ запоминающих устройств 130, 132, 134, 136, устанавливая тем самым биты ССБ в ноль. Это эквивалентно вычитанию значения 256 из каждого накопленного значения метрики, что позволяет выразить накопленные значения метрик с помощью 8 битов.

Далее предположим, что разность между накопленными значениями метрик двух состояний составляет Δk = (u

Что касается переполнения, то, если все биты ССБ значений метрик в момент k равны "1", минимальное значение равно 256.

Согласно вышеуказанным допущениям, если ССБ для u3 k составляет "1", то ССБ других состояний будут равны "0", либо "1". Пока все биты ССБ для ui k (где 0≤i≤3) не станут равными "1", выходной сигнал переноса не появится, даже если ССБ u3 k (а возможно одно или два других значения метрик) равен "1". То есть, пока все биты ССБ не станут равными "1", выходной сигнал переноса на девятом бите не возникает для любого из них. Это означает, что Δk не превышает Δmax.

На фиг.7 показана блок-схема, иллюстрирующая процедуру нормализации значений метрик согласно второму варианту. Согласно фиг.5 и 7 на этапе 501 компаратор 117 определяет накопленные значения метрик в конкретных единицах, логический элемент И 121 в компараторе 117а определяет (или получает) биты ССБ накопленных значений метрик для соответствующих текущих состояний. Получив ССБ текущих состояний, компаратор 117 определяет, все ли накопленные значения метрик соответствующего текущего состояния превышают пороговое значение. То есть логический элемент 121 компаратора 117 определяет, все ли биты ССБ равны "1", как представлено в блоке принятия решений 503. Если ни один из ССБ не равен "1", то компаратор 117 переходит к этапу 507 для выполнения обычной операции ССВ. Если все биты ССБ накопленных значений метрик равны "1", то компаратор 117а переходит к этапу 505, где из каждого значения метрики вычитается пороговое значение. То есть все биты ССБ устанавливаются в ноль. Это соответствует логическому элементу И 121, подающему сигнал высокого уровня на инвертор 119, который в ответ на этот сигнал выдает сигнал установки в ноль битов ССБ соответствующих накопленных значений метрик, устанавливая тем самым ССБ в ноль. После установки битов ССБ в ноль компаратор 117а, как показано на этапе 507, выполняет обычную операцию ССВ.

Далее со ссылками на фиг. с 8А по 10 следует описание величины Δmax, определенной выше. При Δk<Δmax переполнение не возникает. Δmax имеет более низкое значение при низком значении отношения Eb/No и имеет более высокое значение при высоком значении отношения Eb/No. То есть разность между значениями метрик имеет более низкое значение при низком Eb/No и более высокое значение при высоком Eb/No. Причина этого заключается в том, что шум при низком Eb/No возрастает, приводя к уменьшению упомянутой разности, а при высоком Eb/No шум крайне мал, что увеличивает разность Δmax между значениями метрик. Следовательно, очень важно, каким устанавливается значение Δmax при высоком Eb/No. В первом случае можно просто считать, что Δmax имеет бесконечное значение при бесконечном значении Eb/No. Однако, например, в алгоритме Витерби с нестрого определенными ("мягкими") выходными данными (алгоритм SOVA) разность метрик ограничивается константой, определенной как dfree.

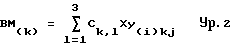

Например, предположим, что имеется 4 бита на выборку, скорость кода R= 1/3, К= 9 и сверточный код передает кодовое слово со всеми нулями "000". В этом случае при высоком значении отношения Eb/No большинство ошибок появляется во время сравнения/выбора между путем со всеми нулями и путем dfree, как показано на фиг.8А. Здесь значение метрики ветвлений и значение метрики пути вычисляется по приведенным ниже уравнениям (2) и (3) соответственно.

где 1=0, 1, 2 и 3, Ck,j - кодовое слово, y(i)k,j - принятый сигнал, r - данный момент времени, l - индекс кодового слова, a l - соответствующий индекс.

Следовательно, Δ

В данном состоянии "i" существует разность метрик между двумя путями: пути со всеми нулями и пути dfree. На фиг.8В показано, что разность между этими двумя путями зависит от кодового символа dfree.

Другими словами, метрика выбранного пути представляет собой значение, полученное путем суммирования метрики пути для нулевого пути со значением метрики в первом состоянии в предыдущий момент времени, а метрика конкурентного пути представляет собой значение, получаемое путем суммирования метрики пути, соответствующей конкурентному пути, со значением метрики во втором состоянии в предыдущий момент времени. В данный момент, поскольку метрика пути между вторым состоянием и временем сравнения больше, чем метрика пути между первым состоянием и временем сравнения, разность Δmax равна или больше Δ

Разность метрик задается следующим выражением:

(dfree (сверточного кодера)=18 для К=9, R=1/3)

где М обозначает значение метрики в точке ветвления выбранного пути и конкурентного пути. Следовательно, когда удовлетворяется условие Δmax≤270, значение разности между соответствующими состояниями не превышает Δmax. Поскольку предполагалось, что на выборку приходится 4 бита, количество запоминающих устройств для запоминания значения метрики составит 8, а поскольку для предотвращения переполнения добавляется 1-битовое запоминающее устройство, то Δmax = 29 = 512. Поскольку 270<512, вышеуказанное условие удовлетворяется.

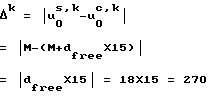

На фиг. 9А показано значение Δmax при высоком отношении сигнал-шум, при этом значение Δmax вычисляется по формуле

Δmax = dfree×Max(Q[ctot]) ... (4)

где Q обозначает уровень квантования, a Max(Q[.]) обозначает расстояние между "0" и "1". Например, для 4 битов на выборку Q=16 и Max(Q[.])= 15, а для 3 битов на выборку Q=8, a Max(Q[.])=7.

На фиг.9В показано значение Δmax при среднем отношении сигнал-шум, причем значение Δmax в этот момент вычисляется по формуле

Δmax = (dfree+δ)×Max(Q[.]) ... Ур.5

где величина δ, обусловленная шумами, имеет очень маленькое значение, причем оно меньше или равно 2 х dfree x Max(Q[.]) в сверточном кодере (СК). Однако это не так в случае, когда δ суммируется, как это показано в уравнении (5).

На фиг. 9С показано значение Δmax при низком отношении сигнал-шум, при этом в этот момент значение Δmax вычисляется по формуле

Δmax = (dfree-δ)×Max(Q[.]) ... (6)

Следовательно, как показано на фиг.10, необходимо отметить, что значение Δmax постепенно возрастает с ростом Eb/No, причем начиная с определенной точки возникает насыщение. Если Δmax удовлетворяет уравнению (5), уравнение (6) также удовлетворяется.

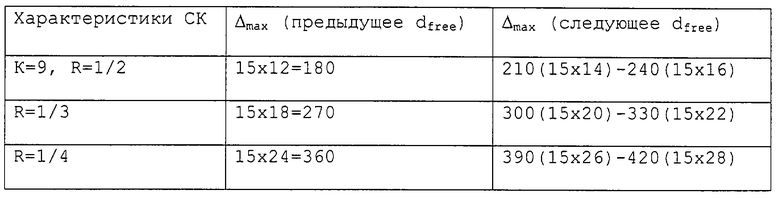

Далее описаны характеристики сверточного кодера в системе CDMA-2000.

Для К=9 и R=1/2, dfree=12, а следующее dfree⇒14, 16, 18, 20.

Для К=9 и R=1/3, dfree=18, а следующее dfree⇒20, 22.

Для К=9 и R=1/4, dfree=24, а следующее dfree⇒26, 18.

В таблице показано значение Δmax в сверточном кодере (СК).

Следовательно, количество битов, добавляемых для предотвращения переполнения для 8 битов на выборку, которые выделяются для значений метрик, определяется следующим образом.

Для R=1/2 количество битов равно 1, поскольку 28=256, а 180<256; для R= 1/3 количество битов равно 2, поскольку 29=512, а 270<512; для R=1/4 количество битов равно 2, поскольку 29=512, а 360<512. Другими словами, поскольку для скорости кода R=1/2 требуется 8 битов, для предотвращения переполнения необходимо добавить только 1 бит. Кроме того, поскольку для скорости кода R=1/3 необходимо 9 битов, то понадобится добавить 1 бит. Следовательно, можно предотвратить переполнение, добавив к количеству битов, необходимых для данной скорости кода, только 1 бит.

Как было описано выше, новое устройство может предотвратить появление ошибок из-за переполнения путем нормализации накопленных значений метрик для декодирования, в результате чего повышается эффективность использования памяти.

Хотя изобретение было продемонстрировано и описано со ссылками на конкретный предпочтительный вариант его осуществления, специалистам в данной области техники очевидно, что в него могут быть внесены различные изменения по форме и в деталях, не выходящие за рамки существа и объема изобретения, которые определены в формуле изобретения.

Изобретение относится к системам связи и может использоваться в средствах мобильной связи. Технический результат заключается в использовании изменения множества значений метрик на множестве временных отрезков. Декодер содержит схему принятия решения, которая формирует сигнал решения, когда все значения метрик превышают заранее установленное значение. Вычитатель вычитает заранее установленное значение из значений метрик в ответ на сигнал решения, чтобы нормализовать значение метрик. Схема принятия решений содержит множество запоминающих устройств, которые запоминают соответствующее значение метрик. 3 с. и 3 з.п.ф-лы, 13 ил., 1 табл.

| СИТНЯХОВСКИЙ И.В | |||

| и др | |||

| Цифровые системы передачи | |||

| - М.: Радио и связь, 1987, с.32-42, рис.2.10, 2.14, 2.15 | |||

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| US 5241383 А, 31.08.1993 | |||

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АКУСТИЧЕСКОЙ МОЩНОСТИ | 0 |

|

SU300775A1 |

| US 4379347 A, 05.04.1983. | |||

Авторы

Даты

2003-10-20—Публикация

1999-12-30—Подача