Область техники

Настоящее изобретение относится к приемнику коммуникационной системы, более конкретно к устройству и способу декодирования входного сигнала.

Предшествующий уровень техники

Передатчик в радиокоммуникационной системе, например спутниковой системе, или в системе стандарта W-CDMA, CDMA (MDKPK) 2000 может использовать код прямого исправления ошибок для обеспечения надежности передачи данных. В приемнике производится итеративное декодирование принятых данных, при котором выходной сигнал компонентного декодера подается в обратном направлении на вход декодирования. На выходе компонентного декодера получают не четко определенный сигнал, например сигнал высокого (+1) или низкого (-1) уровня, а "мягкую" величину (например, 0,7684, -0,6432...) сигнала.

Такая чередующаяся последовательность подается на вход второго компонентного декодера, который ее декодирует. Итеративный декодер состоит по меньшей мере из двух компонентных декодеров. Перемежитель, включенный между двумя компонентными декодерами меняет порядок битов в последовательности покадрового выхода от первого компонентного декодера, а обращенный перемежитель восстанавливает первоначальный порядок следования битов декодированного чередующегося сигнала.

Такой турбодекодер является наглядным примером итеративных канальных декодеров. Итеративные декодеры, такие как турбодекодер, обладают повышенной способностью исправления ошибок за счет многократных итераций декодирования.

В известном способе итеративного декодирования декодирование данных происходит заранее определенное количество раз без проверки возникновения ошибок во время итеративного декодирования. Наличие ошибок проверяется путем обращенного перемежителя декодирования сигнала с выхода обращенного перемежителя с жестким принятием решения.

Однако при общепринятом итеративном декодировании наибольший эффект обычно достигается во время первых двух или трех циклов декодирования, однако эта величина меняется в зависимости от параметров канала. Фактически способность к исправлению ошибок при итеративном декодировании может резко упасть после нескольких циклов декодирования. Более того, после определенного количества циклов итеративного декодирования ресурсы системы, такие как потребляемая мощность и задержка обработки, расходуются на достижение порогового прироста коэффициента усиления. Например, определенное количество циклов итеративного декодирования может вызвать осцилляцию сигнала из-за характеристик обратной связи итеративного декодера. Другими словами, данные с исправленными ошибками могут фактически начать генерировать ошибки при повторении декодирования.

Проблема порогового количества циклов итеративного декодирования (количество итераций, после которого может начаться генерирование ошибок) преодолевается путем выбора соответствующего количества итераций декодирования. Если можно определить, что вероятность исправления всех ошибок приблизительно равна единице, то итеративному декодеру нет необходимости продолжать декодирование входного сигнала. Момент завершения декодирования можно определить несколькими способами. Одним из них является контроль выхода декодера при помощи циклического избыточного кода (CRC). Поскольку контроль при помощи CRC не изменяет передаваемую информацию, при таком контроле исключена возможность генерирования ошибок в декодированной области. Однако перед конструктором систем всегда стоит задача ограничения дополнительных задержек, вызванных обработкой, которые появятся при использовании контроля на наличие ошибок при итеративном декодировании. Поэтому существует потребность в устройстве и способе ограничения количества итераций в итеративном декодере путем выполнения контроля на наличие ошибок в декодированных данных без внесения чрезмерных задержек обработки.

Раскрытие изобретения

В основу настоящего изобретения поставлена задача создания итеративного декодера и способа итеративного декодирования для динамического определения необходимого числа итераций декодирования принятых данных.

Настоящее изобретение также предусматривает создание итеративного декодера и способа итеративного декодирования, в которых выходной сигнал каждого компонентного декодера проверяется на наличие или отсутствие ошибок декодирования.

Настоящее изобретение также направлено на создание итеративного декодера и способа итеративного декодирования, в котором выходной сигнал каждого компонентного декодера проверяется на наличие или отсутствие ошибок декодирования и при котором декодирование останавливается немедленно в случае обнаружения отсутствия ошибок.

Настоящее изобретение также предусматривает создание итеративного декодера и способа итеративного декодирования, в котором задержка обработки минимизируется во время контроля выходного сигнала каждого компонентного декодера на наличие ошибки во время декодирования.

Настоящее изобретение также направлено на создание итеративного декодера и способа итеративного декодирования, в котором выходной сигнал каждого компонентного декодера непрерывно проверяется на наличие или отсутствие ошибок при декодировании и декодирование прекращается немедленно, если не было обнаружено ошибок.

Настоящее изобретение также предусматривает создание итеративного декодера и способа итеративного декодирования, в котором выходной сигнал каждого компонентного декодера непрерывно проверяется на наличие или отсутствие ошибок в момент, когда выходной сигнал компонентного декодера группируется в первоначальном порядке и декодирование прекращается немедленно, если не было обнаружено ошибок.

Настоящее изобретение также направлено на создание итеративного декодера и способа итеративного декодирования, в котором каждый компонентный декодер работает в непрерывном режиме, один кадр проверяется на наличие ошибок одновременно с завершением декодирования этого кадра в первом компонентном декодере и декодирование немедленно прекращается, если ошибок не обнаружено.

Вышеуказанная задача решается за счет создания итеративного декодера. В итеративном декодере первый сумматор имеет первый порт для приема символов информации и второй порт; первый компонентный декодер соединен с первым сумматором для приема первых символов четности и декодирования информационных символов с использованием первых символов четности и выходного сигнала первого сумматора; первое вычитающее устройство имеет третий порт для получения сигнала с выхода первого компонентного декодера и четвертый порт; перемежитель, соединенный с выходом первого вычитающего устройства для перемежения декодированных информационных символов, полученных от первого компонентного декодера; второй компонентный декодер принимает сигнал с выхода перемежителя и вторые символы четности и декодирует информационные символы на выходе перемежителя с использованием полученных сигналов; обращенный перемежитель обращает перемеженный сигнал с выхода второго компонентного декодера.

Второе вычитающее устройство имеет пятый порт для приема сигнала с выхода обращенного перемежителя и шестой порт для приема инвертированного сигнала с выхода первого вычитающего устройства, при этом выход второго вычитающего устройства соединен со вторым портом, а инвертированный выходной сигнал второго вычитающего устройства подается на четвертый порт; логическое устройство преобразует декодированные символы, полученные от первого компонентного декодера в двоичные информационные биты; детектор ошибок проверяет наличие ошибок в двоичных информационных битах, полученных от логического устройства, и генерирует сигнал об отсутствии ошибок, если никаких ошибок не обнаружено; и выходной буфер хранит двоичные информационные биты, полученные от логического устройства, и выводит хранимые двоичные информационные биты в ответ на сигнал об отсутствии ошибок.

Способ итеративного декодирования с заранее определенным максимальным числом итераций, содержащий этапы, при которых итеративно декодируют входной блок данных фиксированного формата, до достижения заранее определенного числа итераций проверяют декодированные данные блока на ошибки и выводят декодированный блок в случае отсутствия ошибок.

Краткое описание чертежей

В дальнейшем настоящее изобретение поясняется описанием вариантов его осуществления со ссылками на прилагаемые чертежи, на которых:

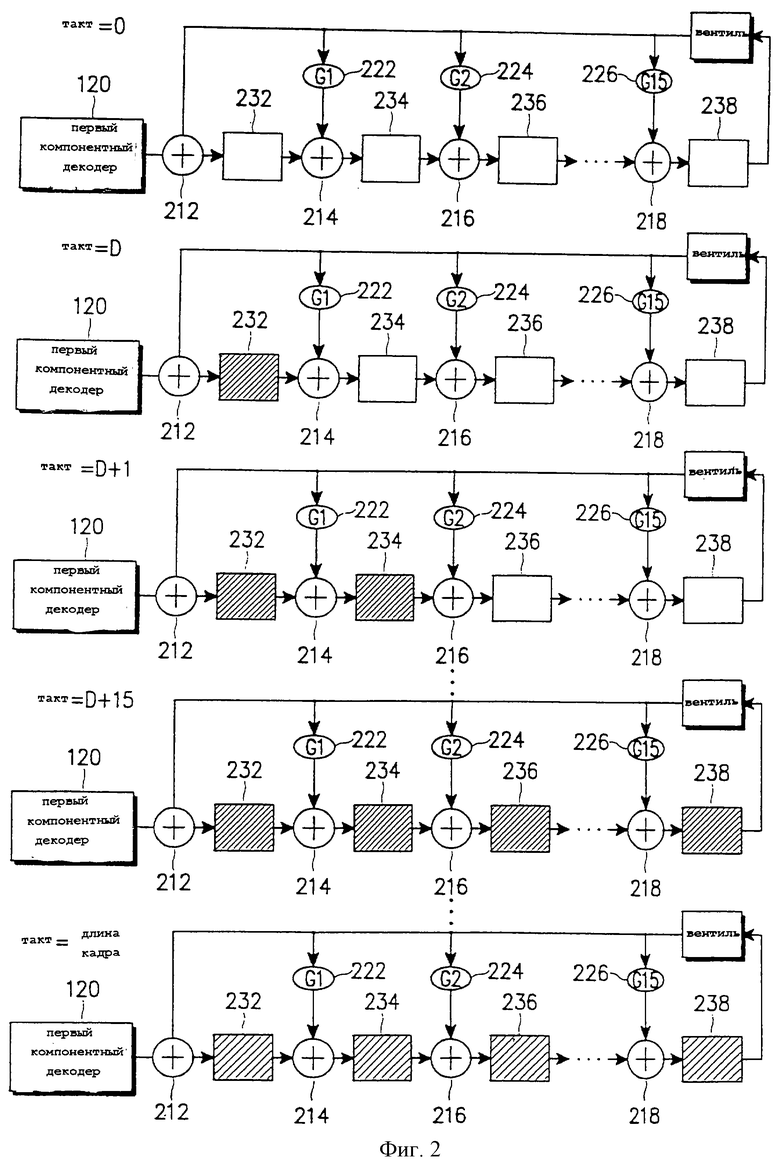

фиг. 1 изображает блок-схему итеративного декодера с кодовым отношением 1/3 по одному из вариантов осуществления настоящего изобретения;

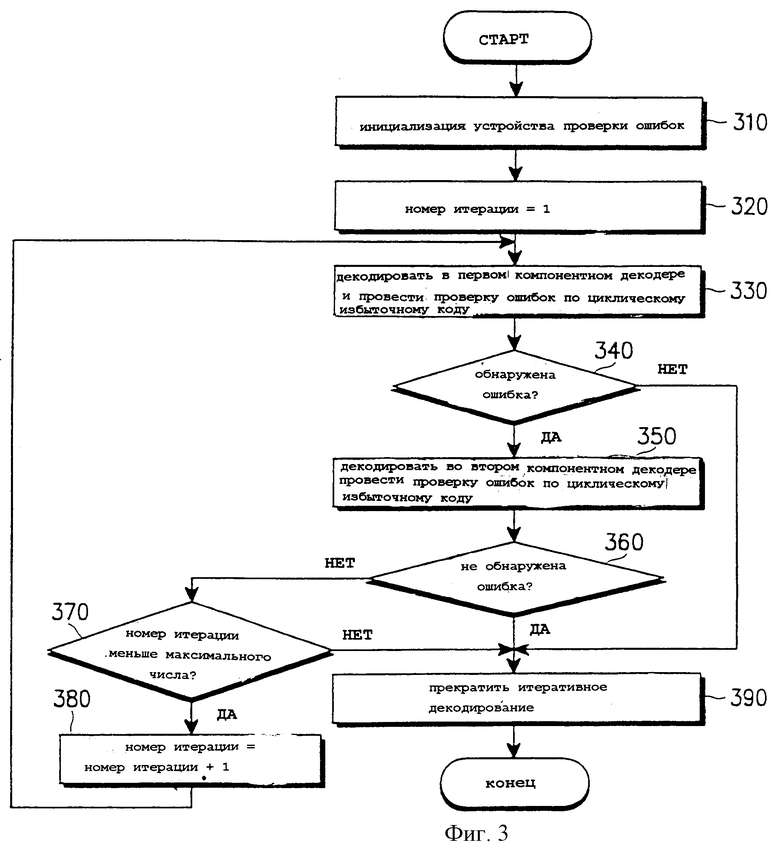

фиг.2 - блок-схему устройства проверки на ошибки, показанного на фиг.1,

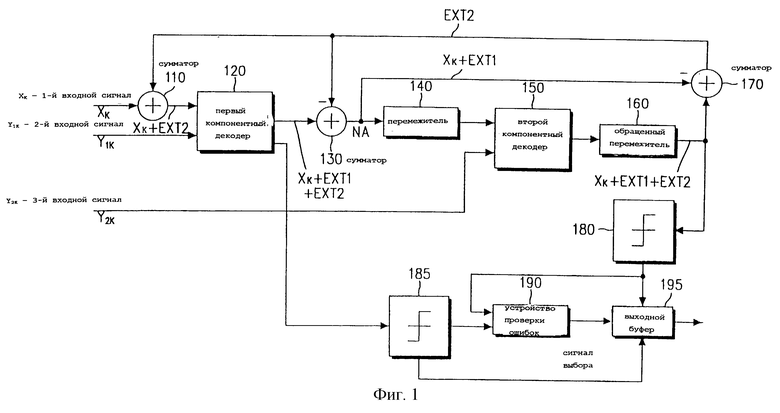

фиг. 3 - диаграмму, иллюстрирующую способ итеративного декодирования по одному из вариантов осуществления настоящего изобретения.

Лучший вариант осуществления настоящего изобретения

Ниже следует описание предпочтительного варианта осуществления настоящего изобретения со ссылками на прилагаемые чертежи. При этом не приводится подробное описание хорошо известных функций и конструкций, с целью избежать перегрузки описания излишними деталями.

Согласно фиг.3, первый, второй и третий входные сигналы являются сигналами демодулированными и квантованными в демодуляторе (не показан) приемника (не показан). Первый, второй и третий сигналы являются соответственно систематическим сигналом ХK сигналом четности Y1K и другим сигналом четности Y2K. Второй и третий входные сигналы представляют собой избыточные величины, складываемые с первоначальными данными для коррекции ошибок и турбокодируемые и перемежаемые в передатчике.

Первый и второй компонентные декодеры 120 и 150 соответственно могут работать в непрерывном режиме. В качестве первого и второго компонентных декодеров 120 и 150 могут использоваться декодеры RESOVA (Register Exchange Soft Output Viterbi Algorithm, алгоритм декодирования Витерби с обменом данными между регистрами и "мягким" выводом). Для ввода каждой "мягкой" величины сигнала из группы битов, например, кадра, первый и второй компонентный декодеры 120 и 150 последовательно выводят каждую "мягкую" величину декодированного сигнала. В непрерывном режиме первый и второй компонентные декодеры 120 и 150 выводят одну "мягкую" величину сигнала на каждую введенную на другом конце "мягкую" величину сигнала без задержки, если задержка соответствует размеру первоначального окна или глубина декодирования D не учитывается. Каждая декодированная "мягкая" величина сигнала, выводимая с первого компонентного декодера, преобразуется в величину с высоким или низким значением на определителе 185, в котором используется жесткая логика, и затем без задержки подается на устройство 190 проверки ошибок. Устройство 190 может быть устройством контроля с помощью циклического избыточного кода (CRC).

Поскольку величины сигнала подаются без какой-либо задержки, устройство 190 проверки ошибок завершает проверку одного кадра "мягких" величин сигнала в тот момент, когда первый компонентный декодер 120 полностью декодирует этот же кадр "мягких" величин сигнала. То есть, каждая "мягкая" величина декодированного сигнала, выводимая с первого компонентного декодера 120 преобразуется в величину высокого или низкого уровня по жесткой логике в определителе 185 и затем побитно подается на устройство 190 проверки ошибок. Значение выходного сигнала определителя 185 хранится в выходном буфере 195. С точки зрения аппаратной части, первый компонентный декодер 120 выводит одну декодированную "мягкую" величину сигнала при каждом такте и подает ее на каждый регистр устройства 190 проверки ошибок без какой-либо задержки. Поэтому декодирование одного кадра в первом компонентном декодере 120 завершается одновременно с проверкой ошибок в кадре устройством 190.

Если во входном кадре ошибок не обнаружено, устройство 190 проверки ошибок останавливает режим итеративного декодирования и выводит декодированный кадр, хранящийся в выходном буфере 195. С другой стораны, при обнаружении ошибки, устройство 190 проверки ошибок вновь выполняет проверку на наличие ошибок во время декодирования во втором компонентном декодере 150. Итеративное декодирование может осуществляться с использованием заранее определенного количества итераций.

Сумматор 110 складывает сигнал ХK с внешним сигналом ЕХТ2 подаваемом по контуру обратной связи от второго вычитающего устройства 170. Сигнал ЕХТ2 не существует при первоначальном декодировании и является компонентом сигнала, полученным в результате декодирования во втором компонентном декодере 150. Суммарный сигнал (ХK+ЕХТ2) с выхода первого сумматора 110 и сигнала Y1K первый компонентный декодер 120 выводит первичный декодированный сигнал, содержащий компоненты ХK, ЕХТ1 и ЕХТ2. Первое вычитающее устройство 130 вычитает компоненту ЕХТ2 из выходного сигнала первого компонентного декодера 120. То есть, в узле NA сигнал состоит из компонентов ХK и ЕХТ1. Логическое устройство 185 преобразует выходной сигнал первого компонентного декодера 120 (содержащий компоненты ХK, ЕХТ1 и ЕХТ2), с восстановленным первоначальным порядком величин данных в высокие или низкие значения данных с применением жесткой логики и без задержки подает преобразованные величины на устройство 190 проверки ошибок.

Перемежитель 140 меняет порядок битов в сигнале (ХK+ЕХТ1), полученный с первого вычитающего устройства 130 методом перемежения и выводит перемеженный сигнал, содержащий компоненты ХK и ЕХТ1. Второй компонентный декодер 150 декодирует сигнал с выхода перемежителя 140 и Y2K, и выводит вторичный декодированный сигнал, содержащий компоненты ХK, ЕХТ1 и ЕХТ2. Обращенный перемежитель 160 восстанавливает первоначальный порядок данных в сигнале с выхода второго компонентного декодера 150 путем обращенного перемежения. Второе вычитающее устройство 170 вычитает сигнал (ХK и EXT1) на узле NA из восстановленного декодированного "мягкого" сигнала, содержащего компоненты ХK, ЕХТ1 и ЕХТ2, принятого от обращенного перемежителя 160. Разностный сигнал подается по контуру обратной связи как внешний информационный сигнал ЕХТ1 на первый сумматор 110.

После того как обращенный перемежитель восстанавливает первоначальный порядок данных в компоненте ХK путем обращенного перемежения вывода второго компонентного декодера, как указано выше, устройство 190 проверки ошибок может проверять наличие ошибок в выводе обращенного перемежителя 160, полученного через логическое устройство 180.

Во время вышеописанного процесса итеративного декодирования "мягкие" величины сигнала, выводимого с первого или второго компонентного декодера 120 или 150, в целом имеют улучшенные характеристики наличия ошибок. Устройство 190 проверки ошибок проверяет наличие ошибок на выходе каждого компонентного декодера до тех пор, пока сигнал на выходе одного из декодеров в определенный момент не окажется "безошибочным". Когда это происходит, устройство 190 проверки ошибок останавливает процесс итеративного декодирования и с выхода выходного буфера 195 снимают не содержащий ошибок декодированный сигнал. То есть, если декодированные данные не содержат ошибок еще до достижения заранее определенного числа итераций декодирования, итеративное декодирование останавливается и не содержащие ошибок декодированные данные выводятся и вводится следующий кадр.

В итеративном декодере, показанном на фиг.1, проверка на наличие ошибок выходного сигнала каждого компонентного декодера может происходить одновременно без дополнительной задержки в аппаратных средствах. Если при проверке ошибок не обнаруживается, итеративное декодирование может быть остановлено немедленно. Следовательно, предотвращается избыточное декодирование и, тем самым, избыточное использование ресурсов системы и возникновение ошибок, вызываемых чрезмерным декодированием.

Обращенный перемежитель 160 восстанавливает первоначальный порядок данных в выходном сигнале второго декодера 150 с помощью обращенного перемежения до того, как сигнал с выхода второго декодера 150 будет проверен на наличие ошибок на устройстве 190 проверки ошибок. Следовательно, устройство 190 проверки ошибок может проверять сигнал с выхода второго компонентного декодера 150 после задержки в один кадр. Выходной сигнал итеративного декодера подвергается проверке на наличие ошибок, когда восстанавливается первоначальный порядок данных.

На фиг. 2 показана блок-схема работы устройства 190 проверки ошибок по фиг. 1 согласно предпочтительному варианту осуществления настоящего изобретения. Предполагается, что устройство проверки ошибок 190 является устройством, использующим циклический избыточный код.

Как показано на фиг.2, устройство проверки ошибок состоит из сдвиговых регистров 232-238, включенных последовательно. Полиномиальные коэффициенты циклического избыточного кода с G1 222 по G15 226 присутствуют в виде 0 или 1. Вентили XOR 212-218 подвергают логической операции "исключающее ИЛИ" указанные коэффициенты и выходные сигналы сдвиговых регистров. Когда номер такта равен 0, на выходе первого компонентного декодера 120 нет данных и устройство проверки ошибок не задействовано. Когда номер такта равен D, где D соответствует глубине декодирования первого компонентного декодера 120, устройство проверки ошибок проверяет сигнал на выходе первого компонентного декодера 120, сдвигая его побитно как показано на фиг. 2. То есть сигнал с выхода первого компонентного декодера подается на сдвиговый регистр при каждом такте и одновременно устройство проверки ошибок с помощью циклического избыточного кода рассчитывает остаток при делении кода сигнала на производящий многочлен. Следовательно, устройство проверки ошибок может проверять ошибки в кадре одновременно с завершением декодирования этого кадра первым компонентным декодером.

Подробное описание работы устройства проверки ошибок с помощью циклического избыточного кода приведено в публикации Error Control Coding: Fundamentals and Applications, Shu Lin and Daniel J. Costello Jr., Prentice Hall, p.99.

На фиг.3. показан алгоритм, иллюстрирующий работу способа декодирования согласно предпочтительному варианту осуществления настоящего изобретения.

Как показано на фиг.3, на этапе 310 устройство 190 проверки ошибок инициализируется под управлением контроллера. Инициализация устройства 190 проверки ошибок эквивалентна инициализации сдвиговых регистров. На этапе 320 контроллер устанавливает порядковый номер итерации на 1 и первый компонентный декодер декодирует входные "мягкие" величины сигнала и последовательно на этапе: 330 выводит декодированные "мягкие" величины. Одновременно устройство 190 проверки ошибок получает без задержки вывод полученный с помощью жесткой логики выходной сигнал с первого компонентного декодера 120 и проверяет наличие ошибок в принятом сигнале под управлением контроллера. Таким образом, декодирование и проверка на ошибки одного кадра завершаются одновременно в первом компонентном декодере 120 и в устройстве 190 проверки ошибок соответственно.

Если на этапе 340 устройство 190 проверки ошибок не обнаруживает ошибок, оно останавливает итеративное декодирование и выводит один декодированный кадр через выходной буфер 195 под управлением контроллера на этапе 390. С другой стороны, если на этапе 340 существует ошибка, второй компонентный декодер 150 декодирует кадр "мягких" величин сигнала под управлением контроллера и на этапе 350 последовательно выводит декодированные "мягкие" величины сигнала. Устройство 190 проверки ошибок под управлением контроллера проверяет ошибки на выходе обращенного перемежителя, обработанном методом жесткой логики, т.е. на выходе второго компонентного декодера 150. Если на этапе 360 не возникает ошибок, устройство 190 проверки ошибок под управлением контроллера переходит к этапу 390. Если на этапе 360 обнаруживаются ошибки, контроллер на шаге 370 определяет, превышает ли текущий номер итерации максимально допустимое число. Если этот номер равен или превышает максимально допустимое число итераций, контроллер стирает содержимое выходного буфера 195. В противном случае, контроллер на этапе 380 осуществляет приращение номера итерации на единицу и возвращается к этапу 330.

Согласно итеративному декодеру и способу итеративного декодирования согласно предпочтительному варианту осуществления настоящего изобретения, описанному выше, итеративное декодирование останавливается немедленно, если множество выходных сигналов декодируются без ошибок и проверка ошибок не вызывает задержек в обработке, чем экономит ресурсы системы.

Несмотря на то, что изобретение было описано со ссылками на конкретный вариант осуществления, специалистам в данной области техники представляется очевидным, что в него могут быть внесены различные изменения, касающиеся формы и деталей, не выходящие за рамки изобретения, определяемые прилагаемой формулой изобретения.

Изобретение относится к приемнику коммуникационной системы, в частности к устройству и способу декодирования входного сигнала. Технический результат заключается в создании итеративного декодера и способа итеративного декодирования для динамического определения необходимого числа итераций декодирования принятых данных. При этом итеративное декодирование останавливается немедленно, если множество выходных сигналов декодируются без ошибок и проверка ошибок не вызывает задержек в обработке, чем экономит ресурсы системы. 3 с. и 18 з.п. ф-лы, 3 ил.

| US 4257520 А, 02.06.1981 | |||

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 1995 |

|

RU2117388C1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| 0 |

|

SU203722A1 | |

| ЕР 0551973 А, 21.07.1993. | |||

Авторы

Даты

2003-11-20—Публикация

1999-12-30—Подача