Текст описания в факсимильном виде (см. графическую часть).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2002 |

|

RU2233481C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2002 |

|

RU2233482C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2001 |

|

RU2206123C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА КОНТРОЛЯ И УПРАВЛЕНИЯ ТЕХНИЧЕСКИМ СОСТОЯНИЕМ ИЗДЕЛИЯ | 2011 |

|

RU2479041C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ЭКСПЛУАТАЦИОННЫХ ХАРАКТЕРИСТИК ОБСЛУЖИВАЕМЫХ ИЗДЕЛИЙ | 2012 |

|

RU2525754C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 1990 |

|

RU2009543C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОЙ ПЕРИОДИЧНОСТИ КОНТРОЛЯ СОСТОЯНИЯ ИЗДЕЛИЯ | 2011 |

|

RU2476934C1 |

| Устройство для определения оптимального периода технического состояния изделия | 1990 |

|

SU1767510A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ЭКСПЛУАТАЦИОННЫХ ХАРАКТЕРИСТИК ИЗДЕЛИЯ | 2011 |

|

RU2476935C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2007 |

|

RU2361276C1 |

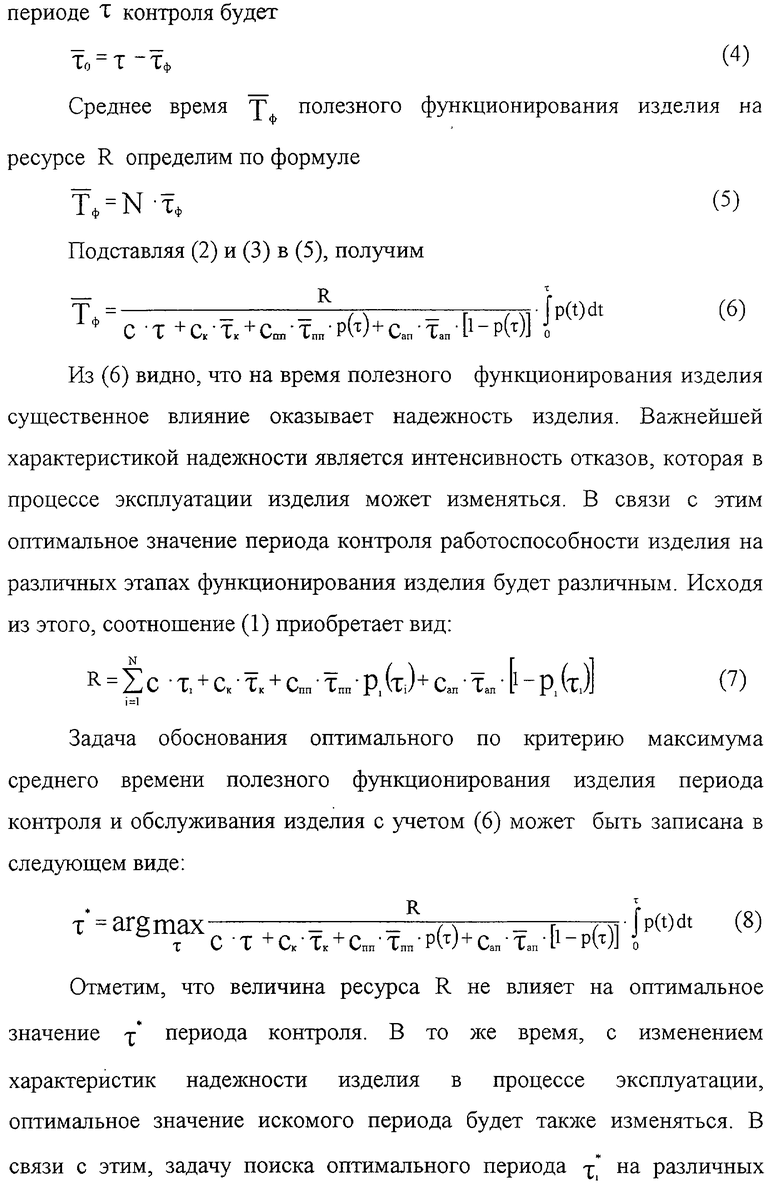

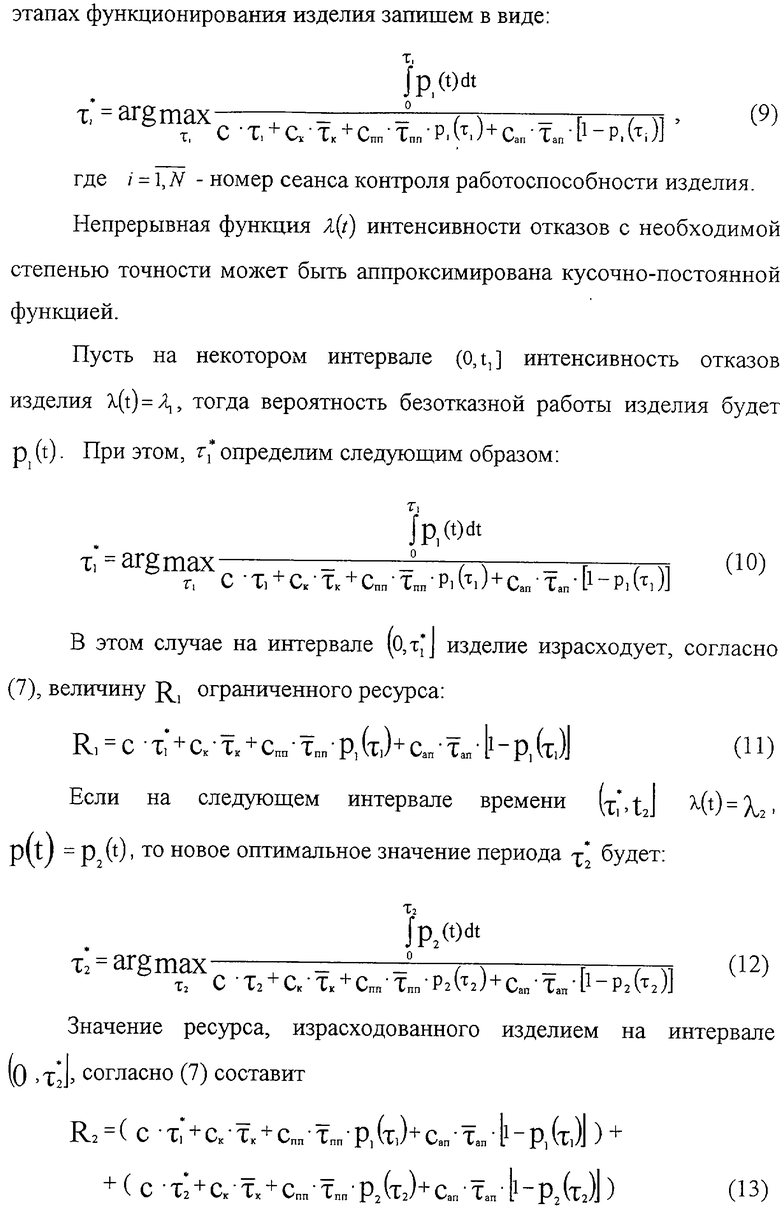

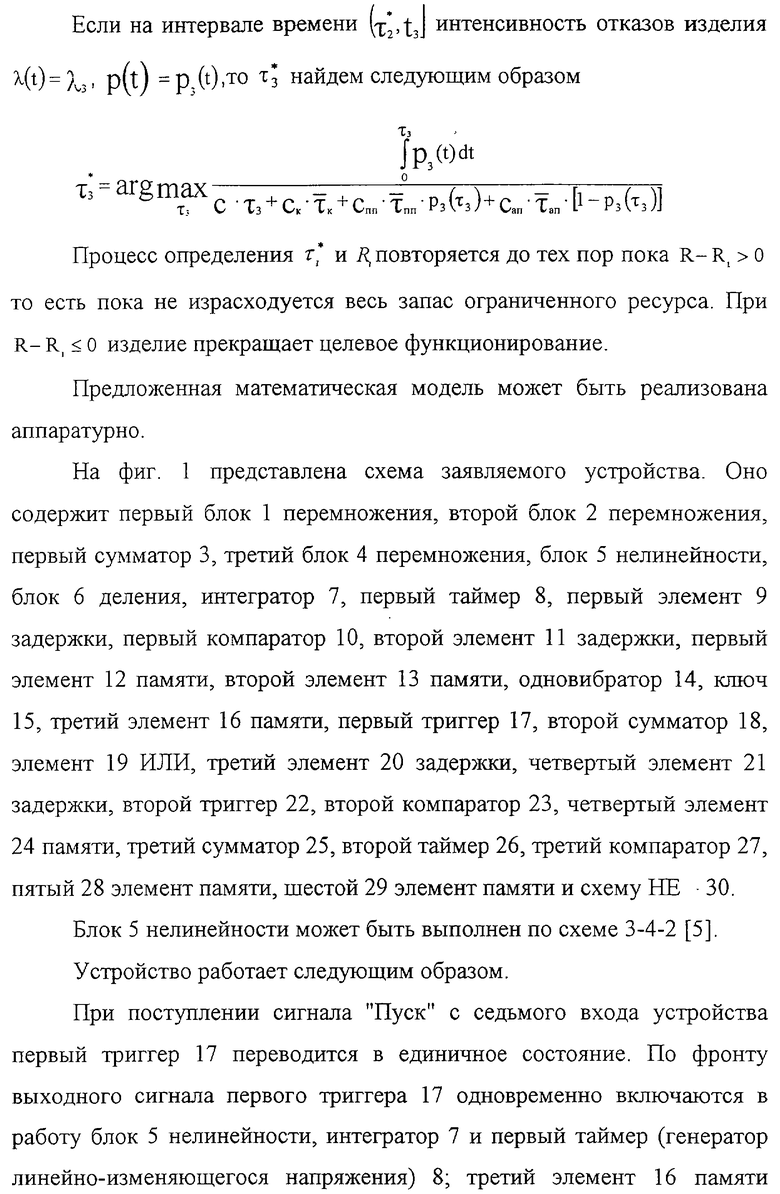

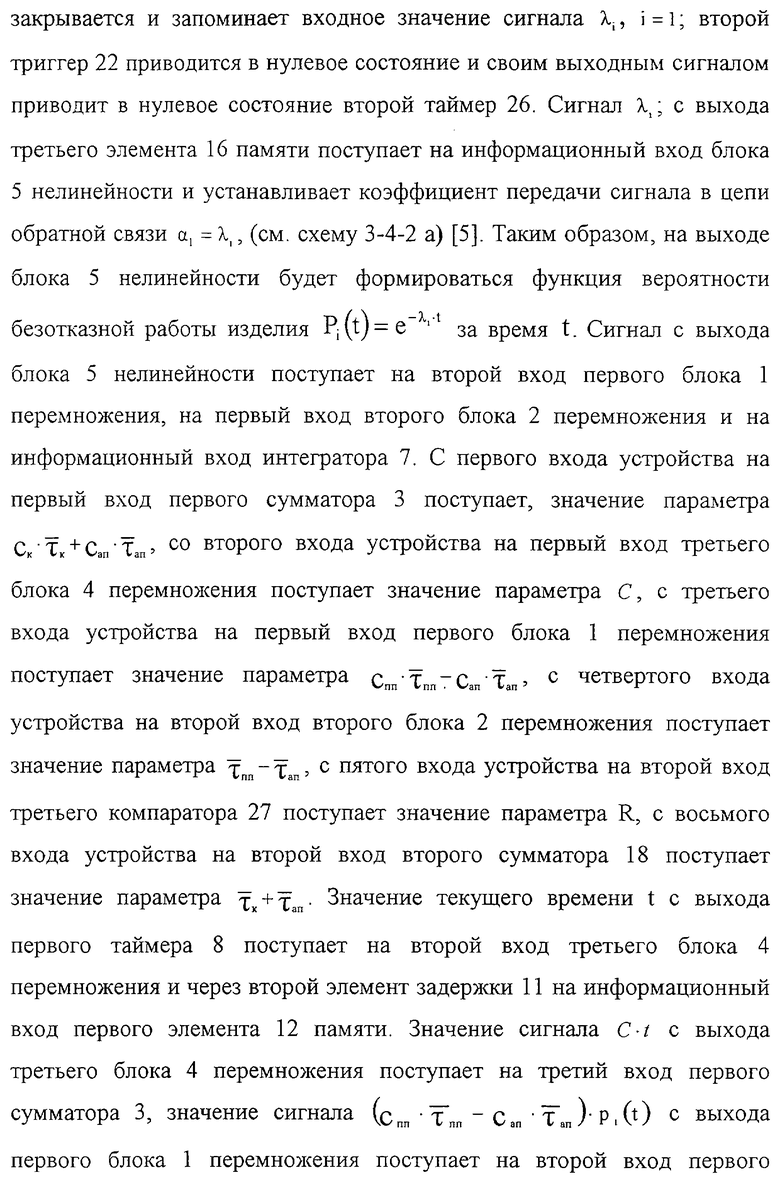

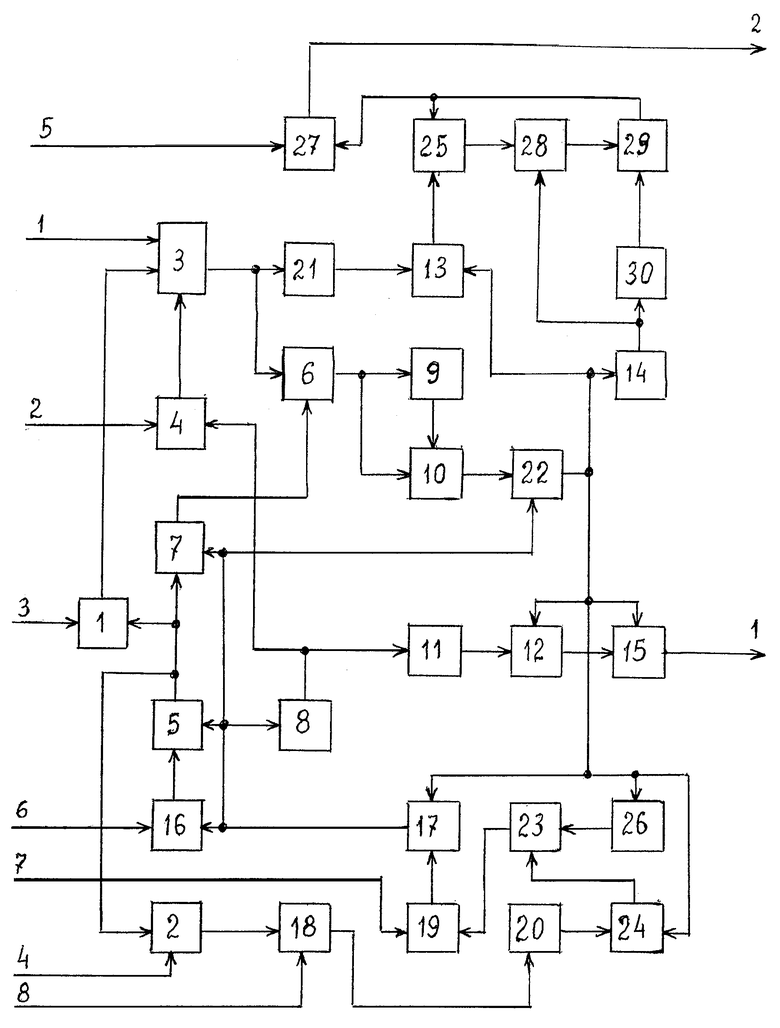

Изобретение относится к вычислительной технике, в частности к устройствам контроля, и может быть использовано в научных исследованиях и технике, где требуется определять оптимальные сроки технического обслуживания изделий. Техническим результатом является расширение области применения устройства. Для этого устройство содержит сумматоры, блок умножения, блок деления, одновибратор, ключ, таймеры, элемент задержки, блок нелинейности, компараторы, триггеры, схему ИЛИ, элементы памяти, интегратор, схему НЕ. 1 ил.

Устройство для определения оптимального периода технического обслуживания изделия, содержащее первый сумматор, один вход которого является первым входом устройства, второй вход через третий блок умножения соединен со вторым входом устройства, третий вход через первый блок умножения подключен к третьему входу устройства, а выход соединен с первым входом блока деления, четвертый элемент задержки своим выходом соединен с информационным входом второго элемента памяти, выход которого подключен к первому входу третьего сумматора, а управляющий вход вместе с управляющими входами одновибратора, ключа, первого и четвертого элементов памяти, второго таймера и входом установки нуля первого триггера соединен с выходом второго триггера, вход установки единицы которого подключен к выходу первого компаратора, один вход которого непосредственно, а второй вход через первый элемент задержки соединены с выходом блока деления, второй вход которого подключен к выходу интегратора, информационный вход которого связан со вторым входом первого блока умножения, с выходом блока нелинейности и со вторым входом второго блока умножения, первый вход которого является четвертым входом устройства, а выход подключен ко второму входу второго сумматора, первый вход которого является восьмым входом устройства, а выход через третий элемент задержки соединен с информационным входом четвертого элемента памяти, выход которого подключен к первому входу второго компаратора, второй вход которого соединен с выходом второго таймера, а выход соединен со вторым входом схемы ИЛИ, выход которой подключен к входу установки единицы первого триггера, а первый вход является седьмым входом устройства, шестой вход которого подключен к информационному входу третьего элемента памяти, выход которого соединен с информационным входом блока нелинейности, а управляющий вход связан с выходом первого триггера, с входом установки нуля второго триггера и с управляющими входами блока нелинейности, интегратора и первого таймера, выход которого через второй элемент задержки подключен к информационному входу первого элемента памяти, выход которого соединен с информационным входом ключа, выход которого является первым выходом устройства, второй выход которого соединен с выходом третьего компаратора, второй вход которого является пятым входом устройства, отличающееся тем, что в него введены схема НЕ, пятый и шестой элементы памяти, причем выход одновибратора соединен непосредственно с управляющим входом пятого элемента памяти и через схему НЕ с управляющим входом шестого элемента памяти, выход которого связан с первым входом третьего компаратора и со вторым входом третьего сумматора, а информационный вход подключен к выходу пятого элемента памяти, информационный вход которого соединен с выходом третьего сумматора, вход четвертого элемента задержки соединен с выходом первого сумматора, выход первого таймера связан со вторым входом третьего блока умножения.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 1990 |

|

RU2009543C1 |

Авторы

Даты

2004-04-27—Публикация

2002-03-13—Подача