Область техники

Изобретение относится к схеме фазовой подстройки частоты (ФАПЧ), которая формирует снимаемый с ее выхода сигнал, имеющий заданную взаимосвязь с сигналом опорной частоты, и, в частности, к схеме ФАПЧ, которая восстанавливает нормальный режим работы при прекращении действия ФАПЧ.

Предшествующий уровень техники

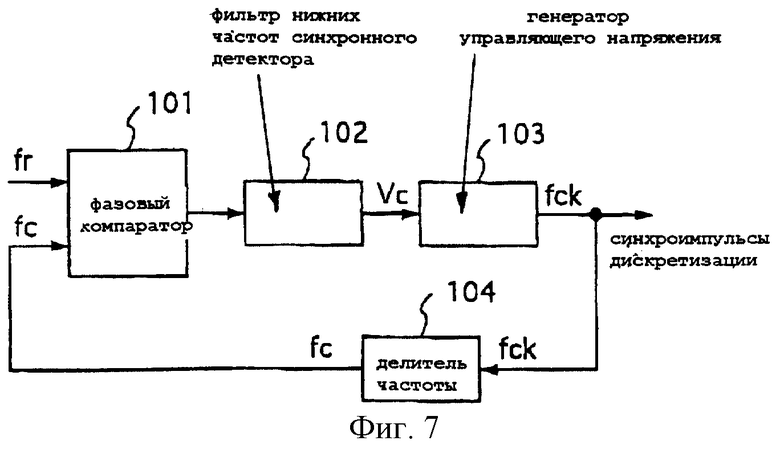

Согласно фиг.7, в схеме ФАПЧ фазы опорного сигнала fr и сигнала сравнения fc сравнивают в фазовом компараторе 101, который выполнен в виде схемы ИСКЛЮЧАЮЩЕЕ ИЛИ или аналогичной схемы. Результирующий сигнал сравнения сглаживают в фильтре 102 нижних частот синхронного детектора с получением управляющего напряжения Vc. Частота, формируемая генератором управляющего напряжения 103, регулирует указанным управляющим напряжением Vc, и получаемый при этом сигнал с частотой fck является выходным сигналом. Указанный выходной сигнал с частотой fck подают на частотный делитель 104, преобразующий частоту сигнала в 1/N, и получаемый сигнал подают в качестве сигнала сравнения fc на фазовый компаратор 101.

Схема ФАПЧ функционирует таким образом, что если частоты опорного сигнала fr, сигнала сравнения fc и сигнала с частотой fck равны соответственно fr, fc, fck в синхронизированном режиме, то выполняются соотношения fr≅fc, fc=fsc/N, в результате чего сигнал сравнения fc всегда отслеживает опорный сигнал fr.

При обработке аналогового сигнала изображения описываемая схема Ф-АПЧ используется для формирования синхроимпульсов дискретизации. Частота синхроимпульсов дискретизации находится в широком диапазоне от 10 до 100 МГц или более в зависимости от типа сигнала изображения.

Поэтому имеются случаи, когда от генератора 103 управляющего напряжения требуется, чтобы отношение максимальной и минимальной частот его колебаний равнялось по меньшей мере двум и чтобы частота колебаний была равна 200 МГц или более. Для учета таких ситуаций применяют широкодиапазонный генератор управляющего напряжения.

В то же время схема ФАПЧ, снабженная генератором вышеуправляющего напряжения вышеуказанного широкого частотного диапазона, при частоте колебаний, превышающей искомую, возможно, не сможет отслеживать опорный сигнал и действие ФАПЧ может прекратиться. Такой случай возникает, например, когда опорный сигнал fr резко изменяется (входной сигнал становится сигналом включения/выключения и т.п.), и частота колебаний существенно изменяется до достижения устойчивого синхронизированного режима, или когда частота опорного сигнала fr и частота колебаний значительно повышаются, и т.п.

В этих случаях в режиме деления частота схемы 104 деления частоты не сможет отслеживать опорный сигнал и выходной сигнал, то есть сигнал сравнения fc пропадает. Поэтому фазовый компаратор 101 принимает решение о том, что произошло падение частоты колебаний генератора 103 управляющего напряжения, действует на повышение частоты колебаний и поднимает частоту колебаний управляющего напряжения Vc до максимального значения. При возникновении этого состояния, даже если оно временное, работа не сможет сама по себе вернуться в свой нормальный режим.

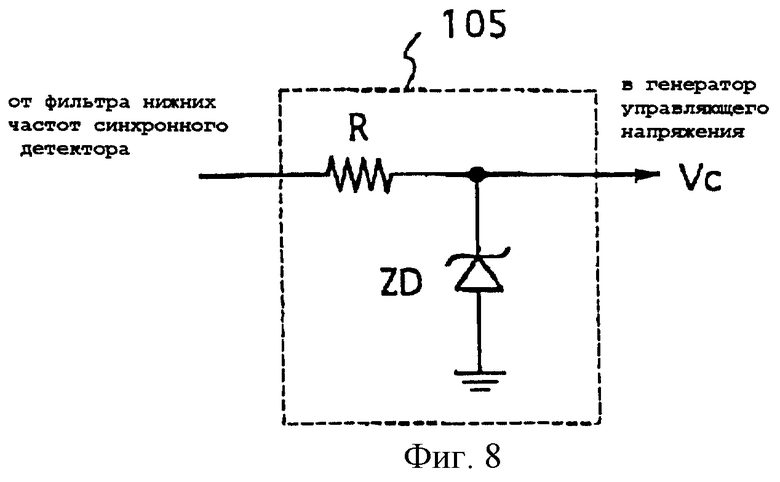

Поэтому для того, чтобы частота колебаний fck генератора 103 управляющего напряжения не превысила рабочие предельные значения частот других схем, входящих в схему ФАПЧ, обычно вводят цепь 105 ограничения напряжения, изображаемую, например, на фиг.8, между генератором 103 управляющего напряжения и фильтром 102 нижних частот синхронного детектора, для обеспечения верхнего предела управляющего напряжения Vc.

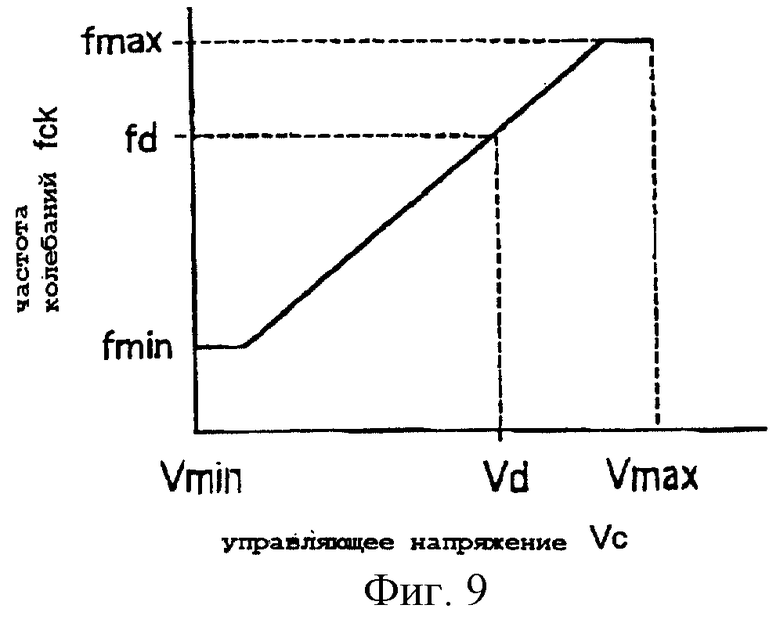

В цепи 105 ограничения напряжения согласно фиг.8 максимальное значение управляющего напряжения Vc ограничивают диодом ZD регулирования напряжения, и согласно фиг.9 частоту колебаний генератора 103 управляющего напряжения ограничивают до величины fd, являющейся в достаточной мере ниже максимального значения fmax. При этом частота fck, генерируемая генератором 103 управляющего напряжения, находится в пределах от минимального значения частоты fmin до верхнего предельного значения частоты fd, что позволяет решить вышеупомянутую проблему.

Однако способ, согласно которому управляющее напряжение Vc, подаваемое на генератор 103 управляющего напряжения, непосредственно ограничивают цепью 105 ограничения напряжения вышеуказанным образом, сопряжен с проблемами, заключающимися в необходимости заново корректировать разброс характеристик диода ZD регулирования напряжения, являющегося ограничивающим элементом схемы 105 ограничения напряжения, и разброс частоты колебаний fck в генераторе 103 регулирования напряжения относительно управляющего напряжения Vc, a также в необходимости ограничения частоты колебаний схемы ФАПЧ для отделения последней от рабочей частоты (необходимой частоты) схемы ФАПЧ с достаточным запасом.

Поэтому задача настоящего изобретения заключается в разработке схемы ФАПЧ, выполненной с возможностью ее легкого возвращения в нормальный режим работы, даже при аномальном режиме генерирования генератора управляющего напряжения и прерывания действия ФАПЧ.

Из патента Японии JP 10-107627 известно, что уровень напряжения сигнала управления, управляющего генератором 18, управляющего напряжения определяется равным или большим уровня напряжения, который может вызвать блокирование схемы ФАПЧ, при этом в случае определения состояния блокировки схемы ФАПЧ указанный уровень сигнала управления понижают для восстановления нормального режима автоподстройки частоты.

В указанной публикации первым средством определения является буферная схема 2, вторым средством определения является тример 24, а третьим - схема 26 объединения, раскрытая в п.1 формулы.

Из патента Японии JP 06-338786 известно, что в случае, когда делитель 7 частоты блокирован, напряжение на выходе транзисторов 2 и 3 возрастает до уровня либо значения, превышающего вышеуказанный уровень, при котором генераторная схема подключена к источнику энергии с возможностью замыкания на землю электрического заряда таким образом, что входное управляющее напряжение генератора управляющего напряжения снижается.

В этом смысле в обоих вышеуказанных источниках показано, что блокирование схемы ФАПЧ задается определением входного управляющего напряжения генератора управляющего напряжения, которое возрастает до предварительно заданного уровня, либо до значения, превышающего предварительно заданный уровень, в результате чего генерируемая частота генератора управляющего напряжения управляется на более низком уровне.

Недостатком технических решений по указанным патентам Японии является вероятность попадания шумов во входное напряжение управления с возникновением фазового дрожания, негативно отражающегося на точности определения состояния блокировки и управлении генерируемой частотой.

Настоящее изобретение также призвано устранить данный недостаток.

Раскрытие изобретения

Согласно данному изобретению, схема ФАПЧ, в которой последовательно контурно соединены компаратор, фильтр нижних частот синхронного детектора, генератор управляющего напряжения и делитель частоты, содержит средство обнаружения прекращения действия для обнаружения прекращения действия ФАПЧ и управляющее средство, которое при обнаружении прекращения действия указанным средством обнаружения прекращения действия управляет генератором управляющего напряжения таким образом, что снижается частота колебаний генератора управляющего напряжения. Таким образом, когда частота колебаний генератора управляющего напряжения превышает заранее определенное значение и схема ФАПЧ прекращает действовать, работу схемы можно быстро вернуть в нормальный режим работы за счет простого технического решения

Перечень фигур

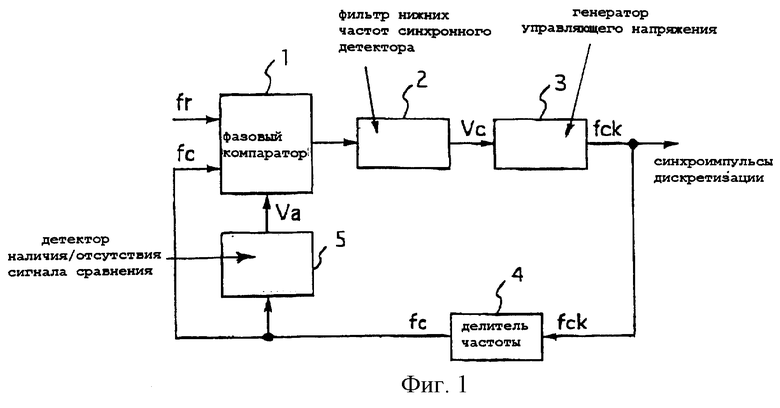

Фиг.1 - блок-схема схемы ФАПЧ согласно первому варианту осуществления изобретения.

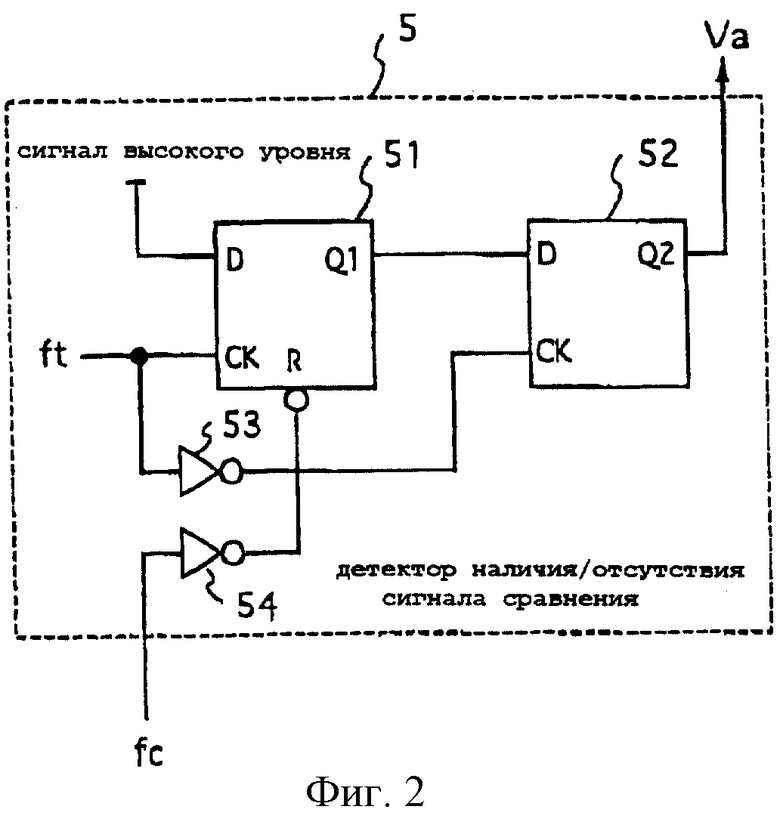

Фиг.2 - блок-схема детектора наличия/отсутствия сигнала сравнения.

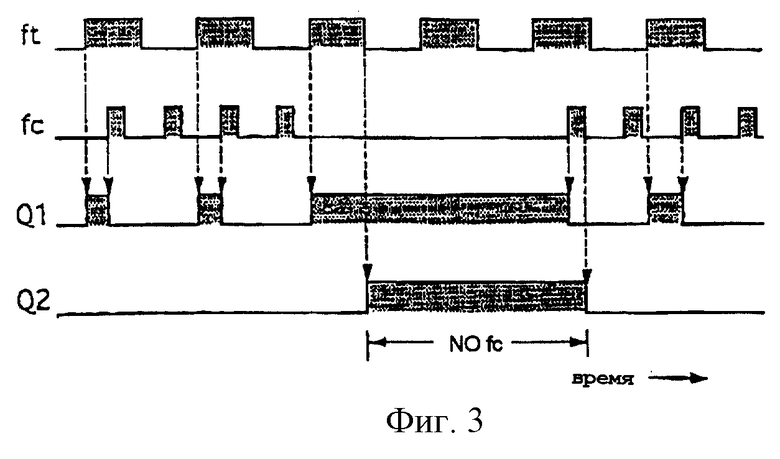

Фиг.3 - временная диаграмма детектора наличия/отсутствия сигнала сравнения.

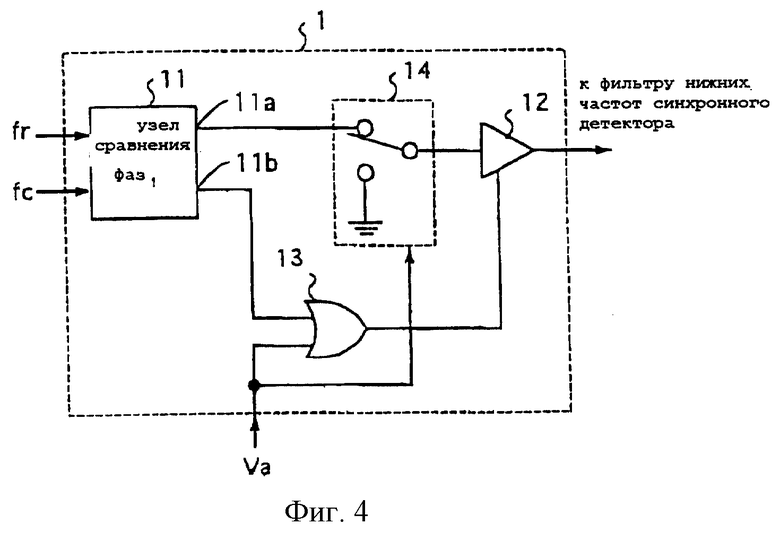

Фиг.4 - блок-схема фазового компаратора.

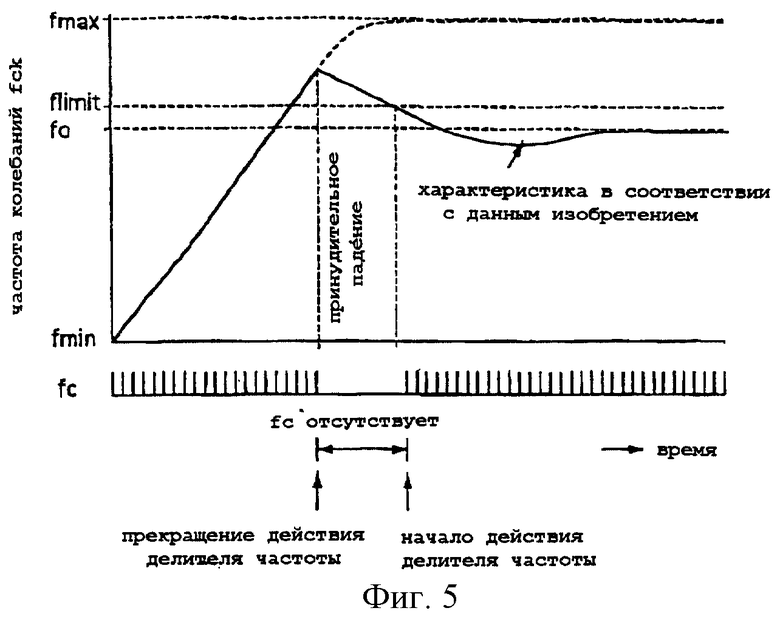

Фиг.5 - график характеристик по принудительному возвращению генератора управляющего напряжения в режим нормальной работы при возникновении аномальных колебаний.

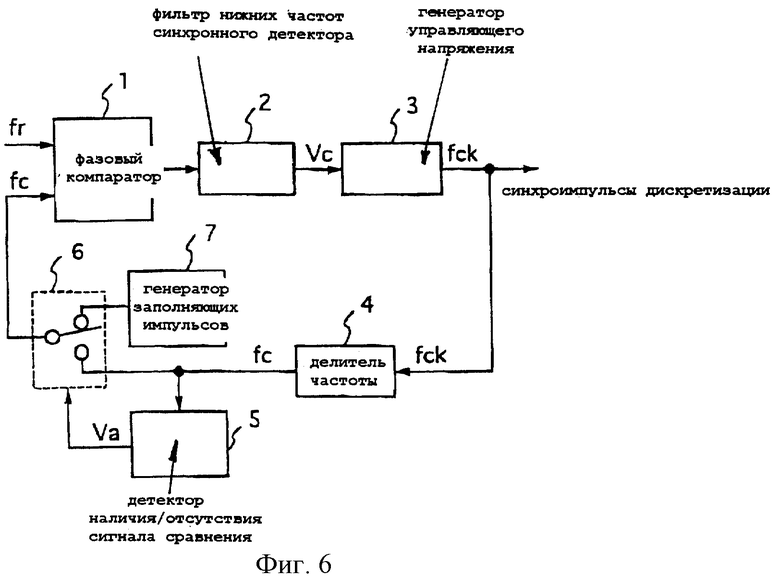

Фиг.6 - блок-схема ФАПЧ-схемы согласно второму варианту осуществления изобретения.

Фиг.7 - блок-схема ФАПЧ-схемы согласно известному уровню техники.

Фиг.8 - блок-схема схемы ограничения напряжения.

Фиг.9 - график характеристик частоты колебаний относительно управляющего напряжения генератора управляющего напряжения.

Лучший вариант осуществления изобретения

Фиг.1 изображает блок-схему ФАПЧ-схемы согласно варианту осуществления изобретения, содержащую фазовый компаратор 1, который сравнивает фазы опорного сигнала fr и сигнала сравнения fc, с получением на выходе сигнала результата сравнения; фильтр нижних частот 2 синхронного детектора, который сглаживает сигнал результата сравнения; генератор 3, управляемый напряжением, который формирует сигнал fck с частотой, пропорциональной вводимому управляющему напряжению Vc; делитель 4 частоты, который делит частоту входного сигнала на 1/N; и детектор 5 наличия/отсутствия сигнала сравнения, а именно средство обнаружения прекращения действия, которое обнаруживает наличие/отсутствие сигнала сравнения fc.

Таким образом, согласно данному варианту осуществления, детектор 5 наличия/отсутствия сигнала сравнения подключен к выходу делителя 4 частоты. При обнаружении отсутствия сигнала сравнения fc сигнал, снимаемый с фазового компаратора 1, регулирует частоту колебаний fck генератора 3, управляемого напряжением, до низких.

Фиг.2 является блок-схемой, иллюстрирующей внутреннюю структуру детектора 5 наличия/отсутствия сигнала сравнения. Позициями 51, 52 обозначены схемы DFF (D-триггера или триггера задержки). Позициями 53 и 54 обозначены инверторы. Сигнал высокого уровня подают на D-вывод схемы DFF 51; испытательный сигнал ft, формируемый независимо (и имеющий частоту, меньшую или равную % сигнала сравнения fc, и имеющий 50-процентный коэффициент заполнения), подают на СК-вывод схемы DFF 51. Сигнал сравнения fc подают на R-вывод (установки в исходное состояние) схемы DFF 51 через инвертор 54. Далее в схеме 52 DFF сигнал с вывода Q1 схемы 51 DFF подают на D-вывод схемы DFF 52; и испытательный сигнал ft инвертируют в инверторе 53 и подают на СК-вывод схемы DFF 52.

На фиг.3 приведена временная диаграмма работы детектора 5 наличия/отсутствия сигнала сравнения. При появлении испытательного сигнала ft вывод Q1 схемы DFF 51 распознает высокий уровень сигнала на D-выводе и становится выводом с высоким уровнем сигнала. При увеличении сигнала сравнения fc вывод Q1 схемы DFF 51 возвращается в исходное состояние и становится выводом с низким уровнем сигнала. При повышении электрического потенциала СК-вывода на выходной вывод схемы 52 DFF передаются данные с входного вывода D указанной схемы.

Поэтому, когда уровень сигнала сравнения fc последовательно изменяется с высокого на низкий, с низкого - на высокий и так далее, в заранее определенный период, даже если выходной вывод Q1 схемы DFF становится выводом с высоким уровнем сигнала при повышении испытательного сигнала, он возвращается в исходное состояние при повышении сигнала сравнения fc. Поэтому даже при последующем снижении уровня испытательного сигнала ft выходной вывод Q2 схемы 52 DFF не становится выводом с высоким уровнем сигнала.

Если сигнал сравнения fc отсутствует, то есть когда сигнал сравнения fc не изменяется до высокого уровня, то схема DFF 51 не возвращается в исходное состояние. Когда уровень испытательного сигнала ft падает, схема DFF 52 распознает высокий уровень сигнала на выходном выводе Q1 и передает его как сигнал высокого уровня на выходной вывод Q2 и затем продолжает эту операцию. Необходимо отметить, что когда сигнал сравнения fc начинает изменяться повторно, выходной вывод Q2 схемы DFF 52 возвращается на низкий уровень.

Фиг.4 является блок-схемой, которая иллюстрирует внутреннюю структуру фазового компаратора 1, которым управляет сигнал, обнаруживаемый в детекторе 5 наличия/отсутствия сигнала сравнения. Компаратор 11, выполняющий сравнение фаз и выполненный в виде вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ, либо аналогичного ему устройства; буфер 12 трех состояний; вентиль ИЛИ 13; переключающую схему 14. Буфер 12 трех состояний, вентиль 13 ИЛИ и переключающая схема 14 образуют управляющее средство. Когда фаза сигнала сравнения fc опережает фазу опорного сигнала fr, на выходном выводе 11а блока 11 сравнения фаз формируется сигнал с низким уровнем. Наоборот, когда фаза сигнала сравнения fc отстает от фазы опорного сигнала fr, на выходном выводе 11а блока 11 сравнения фаз формируется сигнал с высоким уровнем. В остальных случаях, когда фазы не сравнивают, уровень сигнала является неопределенным. При этом при наличии разности фаз между сигналом сравнения fc и опорным сигналом fr на управляющем выводе 11b блока 11 сравнения фаз формируется сигнал с высоким уровнем, и в остальных случаях на нем формируется сигнал с низким уровнем.

Вентиль ИЛИ 13 принимает логическую сумму управляющего сигнала, снимаемого с управляющего выходного вывода 11b узла 11 сравнения фаз и сигнала Va обнаружения, с детектора 5 наличия/отсутствия сигнала и передает ее на управляющий вывод буфера 12. Далее сигнал выходного вывода 11а блока 11 сравнения фаз подают на вход буфера 12 через переключающую схему 14. При этом переключающая схема 14 переключается на заземленный вывод (низкий уровень), когда сигнал Va обнаружения становится сигналом высокого уровня.

Поэтому в случае, когда сигнал Va обнаружения, снимаемый с детектора 5 наличия/отсутствия сигнала сравнения является сигналом, подтверждающим наличие сигнала; другими словами, в случае, когда сигнал обнаружения Va является сигналом низкого уровня, буфером 12 управляют в соответствии с сигналом с управляющего вывода 11b блока 11 сравнения фаз. То есть когда имеется сдвиг фазы между сигналом сравнения fc и опорным сигналом fr, управляющий вывод 11b является выводом с высоким уровнем сигнала. Поэтому буфер 12 оказывается включенным, в результате чего сигнал может проходить между входом и выходом, а сигнал с выходного вывода 11а блока 11 сравнения фаз пропускают через переключающую схему 14 и работа осуществляется в нормальном режиме. При отсутствии сдвига фаз (при захвате ФАПЧ) сигнал управляющего вывода 11b является сигналом низкого уровня, фильтр 2 нижних частот синхронного детектора имеет высокое выходное сопротивление. С использованием сигнала фильтра 2 нижних частот синхронного детектора, который установлен после фазового компаратора 1, генератор 3 управляющего напряжения формирует сигнал постоянной частоты.

С другой стороны, когда сигнал Va обнаружения с детектора 5 наличия/отсутствия сигнала сравнения является сигналом, подтверждающим отсутствие сигнала, другими словами, когда сигнал Va обнаружения является сигналом высокого уровня, то выходной сигнал переключающей схемы 14 является сигналом низкого уровня, и буфер 12 включается, в результате чего сигнал может проходить со входа на выход буфера. Поэтому сигнал низкого уровня, снимаемый с переключающей схемы 14, получается на выходе в неизменном виде. Соответственно сигнал низкого уровня подают на фильтр 2 нижних частот синхронного детектора, и управляющее напряжение Vc, подаваемое на генератор 4 управляющего напряжения, является сигналом низкого уровня, и генерируемая им частота является низкой.

Фиг.5 представляет диаграмму, иллюстрирующую действие генератора 3 управляющего напряжения, где fo - искомая частота частотного сигнала fck; fmax - верхняя предельная частота колебаний; fmin - нижняя предельная частота колебаний; и flimit - частота входного сигнала, являющаяся рабочим пределом делителя 4 частоты. Если частота колебаний fck превышает рабочую предельную частоту flimit, то сигнал сравнения fc пропадает. Поэтому, как указано выше, выходной сигнал фазового компаратора 1 регулируют на низком уровне сигнала, а частоту колебаний генератора 3 управляющего напряжения регулируют до низкой частоты. Таким образом, при снижении частоты колебаний fck ниже рабочего предельного значения flimit делитель частоты 4 возобновляет свою работу, схема ФАПЧ возвращается к первоначальному режиму работы, и частота колебаний fck устанавливается на искомое значение fo.

Таким образом, в соответствии с данным вариантом осуществления, даже если генератор 3 управляющего напряжения находится в режиме аномальных колебаний и работа делителя 4 частоты прекращается, этот момент фиксируется и производят регулировку генератора 3 управляющего напряжения, позволяющую снизить частоту его колебаний. В результате восстанавливается нормальный режим работы.

Фиг.6 представляет блок-схему, иллюстрирующую структуру схемы ФАПЧ в соответствии с еще одним вариантом осуществления настоящего изобретения. Согласно данному варианту, переключающая схема 6 подключена между делителем 4 частоты и фазовым компаратором 1. В обычном режиме переключающую схему 6 регулируют таким образом, что делитель 4 частоты и фазовый компаратор 1 подключены друг к другу с помощью переключающей схемы 6. При обнаружении детектором 5 наличия/отсутствия сигнала сравнения переключающую схему 6 регулируют путем подачи ложного импульса с генератора 7 ложных импульсов в качестве сигнала сравнения fc, который подают на фазовый компаратор 1. Переключающая схема 6 и генератор 7 ложных импульсов образуют управляющее средство.

При нормальной работе ложный импульс может быть сигналом с частотой более высокой, чем частота частотного сигнала, снимаемого с делителя 4 частоты. Таким образом, и в данном варианте осуществления, когда генератор 3 управляющего напряжения генерирует аномальные колебания и действие делителя 4 частоты прекращается, может быть немедленно восстановлен нормальный режим работы.

Необходимо отметить, что в описываемых выше вариантах осуществления выходной сигнал фазового компаратора 1 принудительно делают специальным сигналом (сигналом низкого уровня) с помощью сигнала Va обнаружения с детектора 5 наличия/отсутствия сигнала сравнения, либо специальный ложный импульс вводят в качестве сигнала сравнения в фазовый компаратор 1. Но описываемое изобретение не ограничивается приведенными вариантами осуществления. Например, управляющее напряжение Vc генератора 3 управляющего напряжения можно регулировать непосредственно сигналом Va обнаружения с детектора 5 наличия/отсутствия сигнала сравнения таким образом, что частоту колебаний генератора 3 управляющего напряжения регулируют до достижения определенной низкой частоты. При этом не требуется особой точности регулировки.

В приведенном выше описании режим прекращения действия схемы ФАПЧ определяется по наличию/отсутствию выходного сигнала делителя 4 частоты. Однако режим прекращения действия схемы ФАПЧ можно оценить, определив, является ли частота колебаний fck генератора 3 управляющего напряжения частотой заранее определенного значения, или превышает его. В этом случае сигнал частоты fck можно преобразовать в сигнал напряжения с помощью преобразователя частота-напряжение; и этот сигнал напряжения сравнивают с заранее определенным значением с помощью компаратора напряжения.

Промышленная применимость

В соответствии с вышеизложенным, настоящее изобретение обеспечивает преимущество, заключающееся в том, что при превышении частотой колебаний генератора управляющего напряжения заданного значения и при прекращении действия схемы ФАПЧ нормальный режим работы схемы может быть быстро восстановлен с использованием простой схемы. Данное изобретение может быть применено для формирования синхроимпульсов дискретизации широкого диапазона, которые используют при цифровой обработке аналоговых сигналов изображения и для аналогичных целей.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР СЕТКИ ЧАСТОТ НА БАЗЕ КОНТУРА ФАПЧ С КОМПЕНСАЦИЕЙ ПОМЕХ ДРОБНОСТИ | 2012 |

|

RU2491713C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Индикаторное устройство | 1990 |

|

SU1744472A2 |

| ИНФРАКРАСНЫЙ ТРЕХСПЕКТРАЛЬНЫЙ ИЗВЕЩАТЕЛЬ ПЛАМЕНИ | 2011 |

|

RU2443023C1 |

| Квазикогерентный демодулятор фазоманипулированных сигналов | 1990 |

|

SU1758898A1 |

| СВЧ СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2580068C1 |

| Индикаторное устройство | 1990 |

|

SU1744471A1 |

| КОГЕРЕНТНАЯ РАДИОЛИНИЯ | 2005 |

|

RU2286026C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Устройство для распознавания радиосигналов | 1987 |

|

SU1536508A2 |

Изобретение относится к устройствам фазовой подстройки частоты (ФАПЧ), в частности к схеме ФАПЧ, которая восстанавливает нормальный режим работы при прекращении действия ФАПЧ. Достигаемый технический результат - возвращение в нормальный режим работы при аномальном режиме генерирования генератора, управляемого напряжением. Схема фазовой подстройки частоты содержит фазовый компаратор, фильтр нижних частот, делитель частоты, средство обнаружения прекращения действия ФАПЧ для определения наличия или отсутствия сигнала сравнения на выходе делителя частоты или превышения значением частоты колебаний генератора, управляемого напряжением предварительно заданного уровня, при этом фазовый компаратор содержит блок сравнения фаз и управляющее средство. 1 н. и 2 з.п.ф-лы, 9 ил.

| Устройство для фазовой автоподстройки частоты | 1974 |

|

SU535715A1 |

| US 5939949 А, 17.08.1999 | |||

| US 5258725 А, 02.11.1993 | |||

| US 4942371, 17.07.1990 | |||

| Передача дискретных сообщений, под ред | |||

| ШУВАЛОВА В.П., Москва, Радио и связь, 1990, с.341-346. | |||

Авторы

Даты

2004-08-27—Публикация

2000-08-23—Подача