Изобретение относится к электронной технике, а именно к синтезаторам сетки частот (ССЧ) на базе контура импульсной фазовой автоподстройки частоты (ФАПЧ) с компенсацией помех дробности и может применяться при использовании схем основанных на амплитудно- или широтно-импульсной модуляции тока компенсации.

Синтезаторы сетки частот широко применяются в различных устройствах средств вычислительной техники, управления, радиоавтоматики и коммуникаций. Одними из наиболее важных параметров ССЧ являются частотный диапазон, частотное разрешение (минимальный шаг перестройки) и фазовый шум выходных сигналов синтезируемых частот, а также время перестройки между частотами.

В ССЧ на базе контура ФАПЧ осуществляется стабилизация частоты и фазы генератора, управляемого напряжением (ГУН). Умножение входной опорной частоты обеспечивается благодаря делению частоты ГУН в цепи обратной связи контура. Требование уменьшения значения шага сетки частот выходного сигнала влечет соответствующее уменьшение значения опорной частоты и увеличение значения коэффициента деления. Значение опорной частоты определяет скорость, с которой может подстраиваться контур ФАПЧ между управляющими импульсами. В результате увеличения инерционности контура ФАПЧ, ухудшаются качественные показатели регулирования в целом, что в общем случае приводит к увеличению длительности переходного процесса автоподстройки частоты и увеличению значения фазового шума выходного сигнала ССЧ. Это является основным недостатком ССЧ, использующих делитель с целочисленным коэффициентом деления.

Для устранения противоречия между между частотным разрешением и фазовым шумом разработаны методы, использующие в цепи обратной связи делители с дробно-переменным коэффициентом деления (ДДПКД), реализующие значение деления ниже десятичной точки. В результате обеспечивается работа контура ФАПЧ со значением опорной частоты намного превышающим значение шага сетки частот выходного сигнала. Такие синтезаторы получили название дробные-N ССЧ.

В дробном-N ССЧ происходит периодическое изменение коэффициента деления таким образом, что в среднем получается эффект деления на число содержащее дробную часть. В простейшем случае, за период управляющей последовательности Tm выполняется F делений со значением N+1 и М - F делений со значением N. Выходная частота ГУН Fvco рассчитывается по формуле

где Fref - значение опорной частоты, М - модуль дробности, равный количеству периодов частоты Fref в периодической управляющей последовательности Tm. Значение шага сетки частот выходного сигнала Fvco равно значению опорной частоты деленному на модуль дробности.

Результатом периодического изменения коэффициентов деления в ДДПКД являются периодические фазовые ошибки в контуре ФАПЧ, получившие название помех дробности. Помехи дробности приводят к отклонениям мгновенной фазы выходного сигнала ГУН от идеального положения во времени и, как следствие, к появлению в его спектре паразитных гармоник.

Таким образом, развитие методов компенсации эффекта помех дробности в контуре ФАПЧ является одним из основных направлений в технике проектирования дробных-N ССЧ.

Наиболее близким техническим решением к заявляемому изобретению является схема ССЧ на базе контура ФАПЧ с компенсацией помех дробности описанная в патенте США №6639475 В2 «PLL Circuity МПК H03L 7/00 [1]. Эта схема выбрана в качестве прототипа заявляемого изобретения и изображена на фиг.1.

Схема изобретения [1] имеет первый (Fref), второй (N) и третий (F) входы и выход Fvco. В состав схемы изобретения [1] входят:

1 - импульсный частотно-фазовый детектор (ИЧФД), сравнивающий фазу сигнала Fref опорной частоты и фазу сигнала Ffb частоты обратной связи и вырабатывающий сигналы Up и Dn в соответствии с фазовой разностью;

2 - источник тока накачки заряда (ИТНЗ), вырабатывающий выходной ток Io в соответствии с выходными сигналами ИЧФД;

3 - емкостной элемент, подключенный к выходу ИТНЗ для формирования сигнала управления Vc;

4 - элемент коммутации, подключенный первым выводом к выходу ИТНЗ и управляемый сигналом Sw так, что переводится в разомкнутое состояние, когда ИТНЗ вырабатывает выходной ток;

5 - фильтр контура управления (ФКУ), подключенный к второму выводу элемента коммутации (сигнал Vf) и вырабатывающий сигнал управления Vvco;

6 - генератор, управляемый напряжением (ГУН), вырабатывающий выходной сигнал Fvco с частотой в соответствии с выходным сигналом ФКУ;

7 - делитель с дробно-переменным коэффициентом деления (ДДПКД), осуществляющий деление выходной частоты ГУН на коэффициент, определяемый значением N и состоянием сигнала управления OVER, и вырабатывающий сигнал Ffb частоты обратной связи;

8 - схема управления значением коэффициента деления (УКД) в ДДПКД, накапливающая значение фазовой ошибки дробности Fc в пропорции к одному периоду выходной частоты ГУН, и вырабатывающая сигнал управления OVER для формирования дробности деления, заданной значением F;

9 - источник тока компенсации дробности (ИТКД), подключенный к второму выводу Vf элемента коммутации и вырабатывающий ток Ic в соответствии с значением накопленной фазовой ошибки Fc.

На фиг.2А представлена типовая структурная схема УКД дробного-N ССЧ, основанная на сумматоре (81), выходное значение Fc которого увеличивается на F по сигналу Ffb. При переполнении сумматор вырабатывает сигнал OVER.

Для формирования выходного тока компенсации Ic в схеме ИТКД используется амплитудно-импульсная модуляция (АИМ), широтно-импульсная модуляция (ШИМ) или их комбинация. Основным требованием является равенство площадей импульсов тока компенсации Ic и выходного тока Io схемы ИТНЗ.

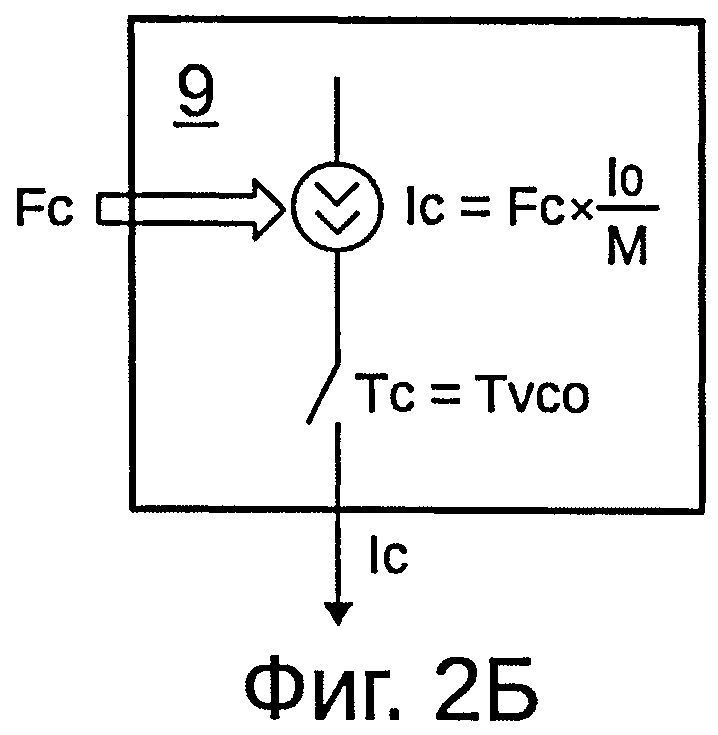

На фиг.2Б представлена типовая структурная схема ИТКД дробного-N ССЧ, основанная на АИМ тока компенсации. Длительность Тс импульса тока компенсации равна одному периоду Tvco выходной частоты ГУН. Амплитуда Ic импульса тока компенсации равна амплитуде Io выходного тока ИТНЗ деленной на модуль дробности М и умноженной на выходное значение Fc схемы УКД. Основным ограничением использования АИМ является точность установления амплитуды Ic тока компенсации при больших значениях модуля дробности.

На фиг.2В представлена типовая структурная схема ИТКД дробного-N ССЧ, основанная на ШИМ тока компенсации. Длительность Тс импульса тока компенсации равна длительности периода Tvco выходной частоты ГУН умноженной на выходное значение Fc схемы УКД. Амплитуда Ic импульса тока компенсации равна амплитуде Io выходного тока ИТНЗ деленной на модуль дробности М. Основным ограничением использования ШИМ является невозможность установки значения модуля дробности М больше значения целой части N коэффициента ДДПКД, а так же, как и при АИМ, точность установления амплитуды Ic тока компенсации при больших значениях модуля дробности.

Для решения ограничений, накладываемых на значение модуля дробности М, широко используется комбинированное АИМ и ШИМ управление при формировании тока компенсации.

На фиг.3 представлены диаграммы, поясняющие процесс компенсации помех дробности в контуре ФАПЧ дробного-N ССЧ изобретения [1] на примере АИМ тока компенсации при значении дробности F, равной 3/8.

Пусть контур ФАПЧ находится в установившемся режиме. Так как среднее значение коэффициента деления является не целым числом, внутри периодической управляющей последовательности Tm фазы сигналов Fref опорной частоты и Ffb частоты обратной связи не совпадают, что приводит к ШИМ выходного тока ИТНЗ I0. Величина модуляции пропорциональна фазовой ошибке, вызванной дробным делением. При каждом такте сравнения фаз в ИЧФД содержимое Fc сумматора схемы УКД увеличивается на дробное приращение F. Когда значение в сумматоре достигает значения модуля дробности, вырабатывается сигнал OVER переполнения сумматора, под управлением которого коэффициент деления в ДДПКД меняется с N на N+1. Значение Fc используется при формировании схемой ИТКД тока 1 с для компенсации тока I0, вызванного фазовой ошибкой дробности коэффициента деления в ДДПКД.

Сигнал Sw управляет элементом коммутации так, что когда выходной ток I0 схемы ИТНЗ находится в активном состоянии, элемент коммутации разомкнут.После замыкания элемента коммутации, начинается переходной процесс сложения зарядов вызванных выходными токами схем ИТПЗ и ИТКД по окончании которого потенциал напряжения сигнала Vf, поступающего на ФКУ, возвращается к первоначальному состоянию. Однако, отсутствие противоположного взаимодействия токов ИТНЗ и ИТКД на емкостном элементе когда токи одновременно активны приводит к переходному процессу взаимной компенсации вносимых ими зарядов после замыкания элемента коммутации, что вызывает остаточные пульсации сигнала Vf. Наличие остаточных пульсаций помех дробности в сигнале управления ГУН, является недостатком изобретения [1].

В случае использования ШИМ при формировании тока компенсации длительность переходного процесса взаимной компенсации увеличится из-за меньшей амплитуды тока Ic.

При последующей фильтрации сигнала Vf за счет уменьшения полосы пропускания ФКУ можно значительно уменьшить амплитуду остаточных пульсаций. Однако, по принципу действия контура ФАПЧ, меньшая полоса пропускания ФКУ увеличит прохождение в выходной сигнал ССЧ собственных низкочастотных шумов ГУН.

Техническим результатом настоящего изобретения является устранение остаточных пульсаций помех дробности в сигнале управления ГУН контура ФАПЧ дробного-N ССЧ при использовании схем компенсации, помех дробности, основанных на АИМ или ШИМ тока компенсации.

Технический результат достигается за счет того, что когда токи помех дробности или компенсации дробности, находясь в активном состоянии, изменяют потенциал напряжения емкостного элемента, элемент коммутации размыкает контур ФАПЧ. Замыкание контура происходит после окончания переходного процесса взаимной компенсации зарядов на емкостном элементе, вносимых названными токами. Для этого в схеме дробного-N ССЧ изобретения [1], имеющей первый (Fref), второй (N) и третий (F) входы, выход Fvco и включающей: ИЧФД (1), сравнивающий фазу сигнала опорной частоты Fref и фазу сигнала частоты обратной связи Ffb и вырабатывающий сигналы Up и Dn в соответствии с фазовой разностью; ИТНЗ (2), вырабатывающий выходной ток I0 в соответствии с выходными сигналами ИЧФД; емкостный элемент (3), подключенный к выходу ИТНЗ для формирования сигнала управления Vc; элемент коммутации (4), подключенный первым выводом к выходу ИТНЗ и управляемый сигналом Sw так, что переводится в разомкнутое состояние, когда ИТНЗ вырабатывает выходной ток; ФКУ (5), подключенный к второму выводу элемента коммутации (сигнал Vf) и вырабатывающий сигнал управления Vvco; ГУН (6), вырабатывающий выходной сигнал Fvco с частотой в соответствии с выходным сигналом ФКУ; ДДПКД (7), осуществляющий деление выходной частоты ГУН в соответствии с сигналом управления OVER и вырабатывающий сигнал частоты обратной связи; схему УКД (8), накапливающую значение фазовой ошибки дробности Fc в пропорции к одному периоду выходной частоты ГУН, и вырабатывающую сигнал управления OVER для формирования дробности, заданной значением F; ИТКД (9), вырабатывающий ток в соответствии со значением накопленной фазовой ошибки Fc, предложено выход ИТКД подключить к выходу ИТНЗ, при этом элементом коммутации управлять так, что на время перехода выхода ИТКД в активное состояние элемент коммутации переводится в разомкнутое состояние.

В результате к моменту окончания действия тока компенсации выходные токи ИТНЗ и ИТКД, складываясь на емкостном элементе, полностью компенсируют заряды, вносимые друг другом, и напряжение на емкостном элементе вернется к состоянию, которое было до размыкания элемента коммутации. Следовательно, вход ФКУ подключится обратно к емкостному элементу уже после окончания на нем переходного процесса компенсации помех дробности и, таким образом, пульсации напряжения в сигнале управления ГУН будут устранены. На время размыкания контура ФАПЧ, потенциал управляющего напряжения сигнала управления ГУН сохраняется на емкости конденсаторов ФКУ.

Заявляемое изобретение иллюстрируется следующими графическими материалами:

Фиг.1. Схема ССЧ на базе контура ФАПЧ с компенсацией помех дробности, представленная в изобретении [1], выбранного в качестве прототипа заявляемого изобретения.

Фиг.2А. Типовая структурная схема УКД дробного-N ССЧ.

Фиг.2Б. Типовая структурная схема ИТКД дробного-N ССЧ, основанная на АИМ тока компенсации.

Фиг.2В. Типовая структурная схема ИТКД дробного-N ССЧ, основанная на ШИМ тока компенсации.

Фиг.3. Диаграммы, поясняющие процесс компенсации помех дробности в контуре ФАПЧ дробного-N ССЧ изобретения [1] на примере АИМ тока компенсации при значении дробности F равной 3/8.

Фиг.4. Схема ССЧ на базе контура ФАПЧ с компенсацией помех дробности, заявляемая в данном изобретении.

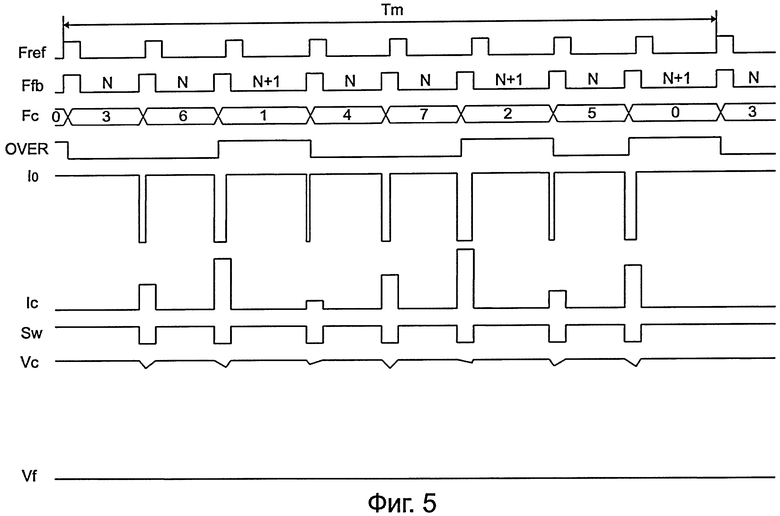

Фиг.5. Диаграммы, поясняющие процесс компенсации помех дробности в схеме контура ФАПЧ дробного-N ССЧ, заявляемой в данном изобретении, на примере АИМ тока компенсации при значении дробности F, равной 3/8.

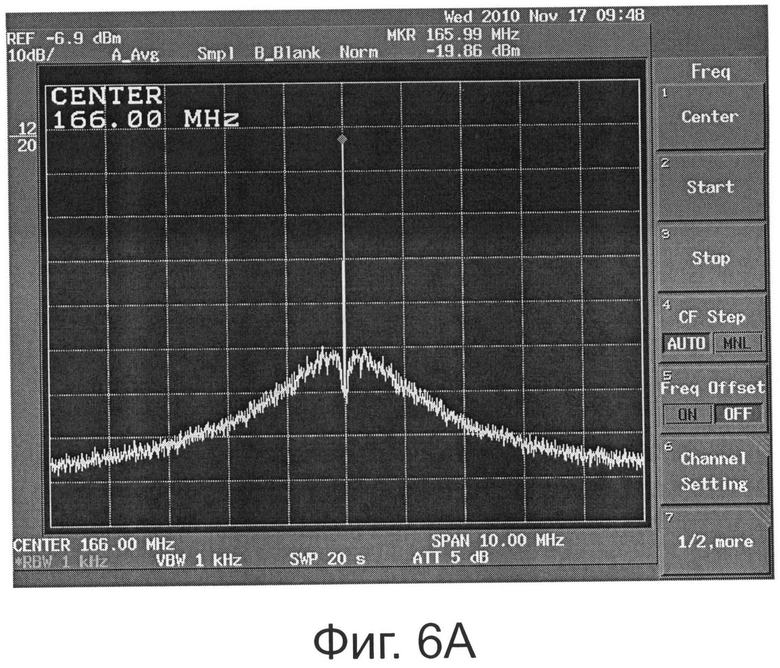

Фиг.6А. Спектрограмма выходного сигнала дробного-N ССЧ частотой 166 МГц при разрешении 1 МГц на деление.

Фиг.6Б. Спектрограмма выходного сигнала дробного-N ССЧ частотой 166 МГц при разрешении 50 кГц на деление.

Схема ССЧ на базе контура ФАПЧ с компенсацией помех дробности, заявляемая в данном изобретении, представлена на фиг.4. Схема имеет первый (Fref), второй (N) и третий (F) входы, выход Fvco и включает ИЧФД (1), имеющий первый вход Fref, второй вход Ffb, первый выход Up и второй выход Dn; ИТНЗ (2), имеющий первый вход Up, второй вход Dn и выход I0; емкостный элемент (3), имеющий вывод Vc; элемент коммутации (4), имеющий вход управления Sw и первый и второй выводы; ФКУ (5), имеющий вход Vf и выход Vvco; ГУН (6), имеющий вход Vvco и выход Fvco; ДДПКД (7), имеющий первый вход Fvco, второй вход N, третий вход OVER и выход Ffb; схему УКД (8), имеющую вход F, первый выход OVER и второй выход Fc; ИТКД (9), имеющий вход Fc и выход Ic.

На первый вход схемы ИЧФД подается сигнал опорной частоты с первого входа Fref устройства. Второй вход схемы ИЧФД подключен к выходу Ffb схемы ДДПКД. Выходы Up и Dn схемы ИЧФД соединены с соответствующими входами схемы ИТНЗ. Выходы схем ИТНЗ и ИТКД, вывод Vc емкостного элемента и первый вывод элемента коммутации соединены между собой. Второй вывод элемента коммутации соединен с входом схемы ФКУ, выход которой соединен с входом Vvco схемы ГУН. Выход схемы ГУН, первый вход схемы ДДПКД и выход Fvco устройства соединены между собой. На второй вход схемы ДДПКД подается значение целой части коэффициента деления с второго входа N устройства. Третий вход схемы ДДПКД подключен в первому выходу схемы УКД. На вход схемы УКД подается значение дробной части коэффициента деления с третьего входа F устройства. Вход схемы ИТКД подключен к второму выходу Fc схемы УКД.

Устройство работает следующим образом. Схема ИЧФД сравнивает фазу сигнала Fref опорной частоты и фазу сигнала Ffb частоты обратной связи и вырабатывает сигналы Up и Dn в соответствии с фазовой разностью. По этим сигналам схема ИТНЗ вырабатывает выходной ток I0, под действием которого, совместно с выходным током Ic схемы ИТКД, на емкостном элементе формируется потенциал напряжения сигнала Vc. Сигнал Sw управляет элементом коммутации так, что переводит его в разомкнутое состояние на время, когда выходные токи схем ИТНЗ или ИТКД находятся в активном состоянии, и в замкнутое состояние, когда выходы схем ИТНЗ и ИТКД выключены. На выходе схемы ФКУ формируется сигнал Vvco, являющийся управляющим для ГУН. Сигнал Fvco выходной частоты ГУН поступает на схему ДДПКД, осуществляющую деление на N или N+1 в зависимости от состояния сигнала управления OVER, и вырабатывающую сигнал Ffb частоты обратной связи. При каждом такте сравнения фаз в ИЧФД схема УКД накапливает значение фазовой ошибки Fc в пропорции к одному периоду выходной частоты ГУН и вырабатывает сигнал OVER для формирования дробности, заданной значением F. Схема ИТКД в соответствии со значением Fc накопленной фазовой ошибки вырабатывает ток Ic для компенсации импульсов тока I0 ИТНЗ, вызванных дробным делением в ДДПКД.

На фиг.5 представлены диаграммы, поясняющие процесс компенсации помех дробности в схеме контура ФАПЧ дробного-N ССЧ, заявляемой в данном изобретении, на примере АИМ тока компенсации при значении дробности F равной 3/8.

Пусть контур ФАПЧ находится в установившемся режиме. Так как среднее значение коэффициента деления является не целым числом, внутри периодической управляющей последовательности Tm фазы сигналов Fref опорной частоты и Ffb частоты обратной связи не совпадают, что приводит к ШИМ выходного тока ИТНЗ I0. Величина модуляции пропорциональна фазовой ошибке, вызванной дробным делением. Когда значение в сумматоре схемы УКД достигает значения модуля дробности, вырабатывается сигнал OVER переполнения сумматора, под управлением которого коэффициент деления в ДДПКД меняется с N на N+1. Значение Fc используется при формировании схемой ИТКД тока Ic для компенсации тока Io, вызванного фазовой ошибкой дробности коэффициента деления в ДДПКД.

На время активного состояния выходов ИТНЗ и ИТКД элемент коммутации переводится в разомкнутое состояние. При этом выходные токи ИТНЗ и ИТКД, складываясь на емкостном элементе (сигнал Vc), полностью компенсируют заряды вносимые друг другом так, что после окончания действия тока компенсации потенциал напряжения на емкостном элементе вернется к состоянию, которое было до размыкания элемента коммутации. Таким образом вход ФКУ подключается обратно к емкостному элементу уже после окончания на нем переходного процесса компенсации помех дробности, в результате чего пульсации напряжения сигнала Vf будут устранены. На время размыкания контура ФАПЧ, потенциал управляющего напряжения сигнала управления ГУН сохраняется на емкости конденсаторов ФКУ.

Для иллюстрации качества компенсации помех дробности в контуре ФАПЧ дробного-N ССЧ, основанного на заявляемом изобретении, на фиг.6А и фиг.6Б представлены спектрограммы выходного сигнала сложно-функционального блока (СФ-блока) синтезаторов сетки тактовых частот для интегрального устройства обработки информации, реализованного по КМОП-технологии 180 нм. Данный СФ-блок построен по двухуровневой схеме. Внешний кварцевый резонатор часов реального времени с частотой 32,768 кГц является опорным для ССЧ первого уровня. ССЧ первого уровня имеет целочисленный коэффициент деления в цепи обратной связи контура ФАПЧ и вырабатывает сигнал в диапазоне частот 16-30 МГц. Далее сигналы нескольких частот, одновременно требуемых для разных блоков устройства обработки информации синтезируются из выходного сигнала ССЧ первого уровня несколькими дробными-N ССЧ второго уровня, имеющими модуль дробности М равный восьми и использующими компенсацию помех дробности, заявляемую в данном изобретении.

Например, при синтезе сигнала частотой 166 МГц из опорной частоты 32,768 кГц, целочисленный ССЧ первого уровня программируется в соответствии с выражением:

Дробный-N ССЧ второго уровня программируется в соответствии с выражением

При этом нормированная погрешность установки требуемой частоты 166 МГц составляет менее 8,5×10-6.

На фиг.6А и фиг.6Б представлены спектрограммы выходного сигнала СФ-блока ССЧ частотой 166 МГц при разрешении 1 МГц и 50 кГц на деление соответственно. Спектральные характеристики синтезируемого сигнала подтверждают устранение остаточных пульсаций напряжения в сигнале управления ГУН контура ФАПЧ дробного-N ССЧ второго уровня.

С целью ускорения переходных процессов автоподстройки частоты может быть использован следующий алгоритм работы ИЧФД и управления элементом коммутации. Если схема ИЧФД обнаруживает фазовую разность более ± 2π радиан, то ИЧФД управляет схемой ИТНЗ так, что выходной ток I0 вырабатывается непрерывно. При этом элемент коммутации постоянно находится в замкнутом состоянии. Если фазовая разность, обнаруженная схемой ИЧФД, составляет менее ±2π радиан, то осуществляется управление, представленное на фиг.5.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2483434C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2013 |

|

RU2530248C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2602991C1 |

| Устройство эквивалентного умножения емкости конденсатора петлевого фильтра контура ФАПЧ | 2015 |

|

RU2612573C1 |

| Устройство эквивалентного умножения емкости конденсатора петлевого фильтра контура ФАПЧ | 2022 |

|

RU2783664C1 |

| СТРУКТУРА ФИЛЬТРА КОНТУРА УПРАВЛЕНИЯ ДЛЯ УСТРОЙСТВА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2010 |

|

RU2422985C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ НАПРЯЖЕНИЙ ДЛЯ ГЕНЕРАТОРА, УПРАВЛЯЕМОГО НАПРЯЖЕНИЕМ | 2017 |

|

RU2642405C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2024 |

|

RU2827940C1 |

Изобретение относится к электронной технике, а именно к синтезаторам сетки частот (ССЧ) на базе контура импульсной фазовой автоподстройки частоты (ФАПЧ) с компенсацией помех дробности, и может применяться при использовании схем, основанных на амплитудно- или широтно-импульсной модуляции тока компенсации. Техническим результатом изобретения является устранение остаточных пульсаций помех дробности в сигнале управления генератора, управляемого напряжением (ГУН). Синтезатор сетки частот содержит импульсный частотно-фазовый детектор, источник тока накачки заряда, емкостный элемент, элемент коммутации, фильтр контура управления, генератор, управляемый напряжением, делитель с дробно-переменным коэффициентом деления (ДДПКД), схему управления значением коэффициента деления в ДДПКД, источник тока компенсации дробности (ИТКД), выход которого подключен к выходу источника тока накачки заряда. 6 ил.

Синтезатор сетки частот, включающий импульсный частотно-фазовый детектор (ИЧФД), сравнивающий фазу сигнала опорной частоты и фазу сигнала частоты обратной связи и вырабатывающий первый и второй сигналы в соответствии с фазовой разностью; источник тока накачки заряда (ИТНЗ), вырабатывающий выходной ток в соответствии с первым и вторым выходными сигналами ИЧФД; емкостной элемент, подключенный к выходу ИТНЗ для формирования третьего сигнала управления; элемент коммутации, подключенный первым выводом к выходу ИТНЗ и управляемый так, что переводится в разомкнутое состояние, когда ИТНЗ вырабатывает выходной ток; фильтр контура управления, подключенный к второму выводу элемента коммутации и вырабатывающий четвертый сигнал управления, основанный на третьем сигнале управления; генератор, управляемый напряжением (ГУН), вырабатывающий выходной сигнал с частотой в соответствии с четвертым сигналом управления; делитель с дробно-переменным коэффициентом деления (ДДПКД), осуществляющий деление выходной частоты ГУН в соответствии с пятым сигналом управления и вырабатывающий сигнал частоты обратной связи; схему управления значением коэффициента деления в ДДПКД, накапливающую значение фазовой ошибки, вызванной дробным делением, и вырабатывающую пятый сигнал управления; источник тока компенсации дробности (ИТКД), вырабатывающий ток в соответствии со значением накопленной фазовой ошибки, отличающийся тем, что выход ИТКД подключен к выходу ИТНЗ, при этом элемент коммутации управляется так, что на время перехода выхода ИТКД в активное состояние элемент коммутации переводится в разомкнутое состояние.

| US 6639475 B2, 28.10.2003 | |||

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| СИНТЕЗАТОР ЧАСТОТ СВЧ С НИЗКИМ УРОВНЕМ ФАЗОВОГО ШУМА | 2009 |

|

RU2402868C1 |

| US 6483388 B2, 19.11.2002 | |||

| Многоходовой клапан | 1980 |

|

SU960480A1 |

Авторы

Даты

2013-08-27—Публикация

2012-10-01—Подача