Изобретение относится к электротехнике и может быть использовано в устройствах релейной защиты, например в качестве реле разности фаз напряжений сети и генератора.

Известно устройство, содержащее последовательно соединенные генератор тактовых импульсов, двоичный счетчик, дешифратор, формирователь импульсов и исполнительный элемент, выполненный в виде транзистора [1].

Недостатком устройства является относительно узкие функциональные возможности, не позволяющие использовать его в качестве реле разности фаз и реле скорости изменения фаз.

Наиболее близким по технической сущности к предлагаемому, является устройство, содержащее первый и второй выпрямительные блоки, выполненные в виде диодов, катод и анод которых являются, соответственно, клеммой напряжения генератора и клеммой напряжения сети, сумматор, первый и второй входы которого соединены, соответственно, с анодом первого и с катодом второго диодов, первый и второй операционные усилители, являющиеся, соответственно, повторителем и пороговым блоком, входы которых соединены с выходом сумматора, третий и четвертый диоды, аноды которых соединены с выходами первого и второго операционных усилителей, соответственно, умножитель, входы которых соединены с катодами третьего и четвертого диодов, первый и второй инверторы, входы которых соединены, соответственно, с катодами третьего и четвертого диодов, а также первый, второй и третий исполнительные элементы, соединенные, соответственно, с выходом умножителя и первого и второго инверторов [2].

Недостатком наиболее близкого технического решения является относительно узкие функциональные возможности, поскольку оно вырабатывает сигнал примерного равенства амплитуды напряжений сети и генератора, что указывает на временной интервал возможной подстройки фазы генератора к фазе сети, но не вырабатывает сигнала допустимого (или недопустимого) рассогласования фаз генератора и сети в интервале возможной подстройки.

Техническим результатом изобретения является расширение функциональных возможностей.

Этот технический результат достигается тем, что в устройство, содержащее первый и второй исполнительные элементы и первый пороговый блок, введены первый элемент И, первый и второй входы которого соединены, соответственно, с выходом первого порогового блока, вход которого является входом напряжения сети, и второго порогового блока, вход которого является входом напряжения генератора, первый и второй формирователи коротких импульсов, входы которых соединены с выходом первого порогового блока, первый, второй и третий элементы ИЛИ, первый, второй и третий фильтры-усреднители, второй элемент И, первый и второй счетчики импульсов, счетные входы которых соединены с выходами, соответственно, первого и второго элементов И, входы установки в ноль - соединены с выходами первого и второго элементов ИЛИ, соответственно, а выходы - соединены с информационными входами первого и второго фильтров-усреднителей, соответственно, последовательно соединенные делитель, первый и второй входы которого соединены с выходами, первого и второго фильтров-усреднителей, соответственно, и третий пороговый блок, выход которого соединен с входом первого исполнительного элемента, последовательно соединенные одновибратор, вход которого является входом запуска реле разности фаз, и генератор тактовых импульсов, выход которого соединен с третьим входом первого элемента И и со вторым входом второго элемента И, а также RS-триггер, R-вход которого соединен с выходом третьего элемента ИЛИ, S-вход - соединен с выходом первого формирователя коротких импульсов, с тактовыми входами первого и второго фильтров-усреднителей и с первыми входами первого и второго элементов ИЛИ, а выход - соединен со вторым входом второго элемента И, первый регистр памяти, информационный вход которого соединен с выходом делителя, второй регистр памяти, информационный вход которого соединен с выходом первого регистра памяти, тактовый вход соединен с тактовым входом первого регистра памяти и с выходом первого формирователя коротких импульсов, а вход установки в ноль второго регистра памяти соединен с входом установки в ноль первого регистра памяти и с выходом одновибратора, блок вычитания, первый и второй входы которого соединены, соответственно, с выходом первого регистра памяти и с выходом второго регистра памяти, а выход соединен с информационным входом третьего фильтра-усреднителя, тактовый вход которого соединен с выходом первого формирователя коротких импульсов, а вход установки в ноль соединен с выходом одновибратора, четвертый и пятый пороговые блоки, входы которых соединены с выходом третьего фильтра-усреднителя, а также четвертый элемент ИЛИ, первый и второй входы которого соединены с выходами, соответственно, четвертого и пятого пороговых блоков, а выход соединен с входом второго исполнительного элемента, при этом выход одновибратора соединен со вторыми входами первого и второго элементов ИЛИ, с первым входом третьего элемента ИЛИ и с входами установки в ноль первого и второго фильтров-усреднителей, а выход второго формирователя коротких импульсов соединен со вторым входом третьего элемента ИЛИ.

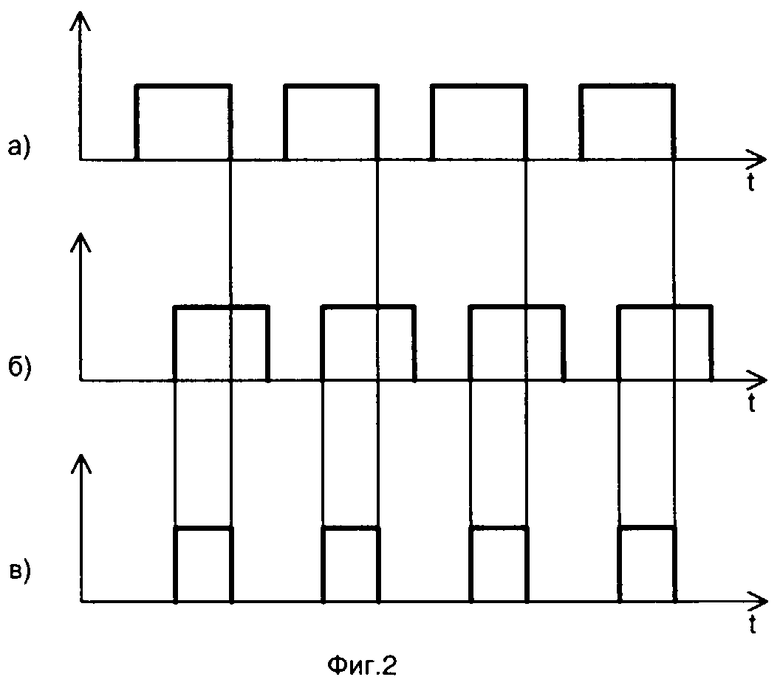

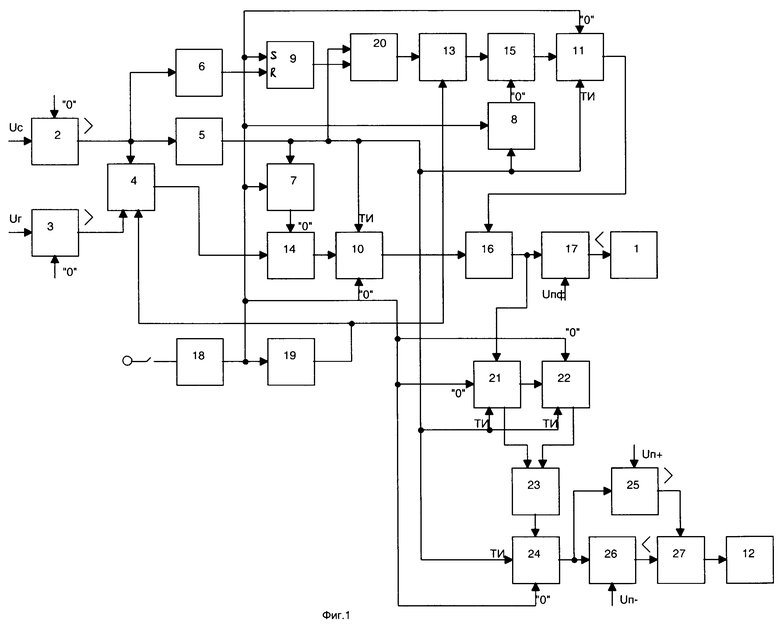

На фиг.1 представлена электрическая структурная схема реле разности фаз, на фиг.2 - временные диаграммы, поясняющие его работу.

Реле разности фаз (фиг.1) содержит исполнительный элемент 1, первый пороговый блок 2, второй пороговый блок 3, вход которого является входом напряжения генератора, первый элемент И 4, первый и второй входы которого соединены, соответственно, с выходом второго порогового блока 3 и с выходом первого порогового блока 2, вход которого является входом напряжения сети.

Реле разности фаз содержит также первый 5 и второй 6 формирователи коротких импульсов, входы которых соединены с выходом первого порогового блока 2, а также первый 7, второй 8 и третий 9 элементы ИЛИ, первый 10, второй 11 и третий 24 фильтры-усреднители, второй элемент И 13, первый 14 и второй 15 счетчики импульсов, счетные входы которых соединены с выходами, соответственно, первого 4 и второго 13 элементов И, входы установки в ноль -соединены с выходами первого 7 и второго 8 элементов ИЛИ, соответственно, а выходы - соединены с информационными входами первого 10 и второго 11 фильтров-усреднителей, соответственно.

Кроме того, реле разности фаз содержит последовательно соединенные делитель 16, первый и второй входы которого соединены с выходами, первого 10 и второго 11 фильтров-усреднителей, соответственно, и третий пороговый блок 17, выход которого соединен с входом исполнительного элемента 1, а также последовательно соединенные одновибратор 18, вход которого является входом запуска реле разности фаз, и генератор 19 тактовых импульсов, выход которого соединен с третьим входом первого элемента И 4 и со вторым входом второго элемента И 13, а также RS-триггер 20, R-вход которого соединен с выходом третьего элемента ИЛИ 9, S-вход - соединен с выходом первого формирователя 5 коротких импульсов, с тактовыми входами первого 10 и второго 11 фильтров-усреднителей и с первыми входами первого 7 и второго 8 элементов ИЛИ, а выход - соединен со вторым входом второго элемента И 13.

Реле разности фаз дополнительно содержит второй исполнительный элемент 12, первый регистр 21 памяти, информационный вход которого соединен с выходом делителя 16, второй регистр 22 памяти, информационный вход которого соединен с выходом первого регистра 21 памяти, тактовый вход - соединен с тактовым входом первого регистра 21 памяти и с выходом первого формирователя 5 коротких импульсов, а вход установки в ноль - соединен с входом установки в ноль первого регистра 21 сдвига и с выходом одновибратора 18, блок 23 вычитания, первый и второй входы которого соединены, соответственно, с выходом первого регистра 21 памяти и с выходом второго регистра 22 памяти, а выход - соединен с информационным входом третьего фильтра-усреднителя 24, тактовый вход которого соединен с выходом первого формирователя 5 коротких импульсов, а вход установки в ноль - соединен с выходом одновибратора 18, четвертый 25 и пятый 26 пороговые блоки, входы которых соединены с выходом третьего фильтра-усреднителя 24, а также четвертый элемент ИЛИ 27, первый и второй входы которого соединены с выходами “больше” и “меньше”, соответственно, четвертого 25 и пятого 26 пороговых блоков, а выход - соединен с входом второго исполнительного элемента 12, при этом выход одновибратора 18 соединен со вторыми входами первого 7 и второго 8 элементов ИЛИ, с первым входом третьего элемента ИЛИ 9 и с входами установки в ноль первого 10 и второго 11 фильтров-усреднителей, а выход второго формирователя 6 коротких импульсов соединен со вторым входом третьего элемента ИЛИ 9.

На фиг.2а представлены временные диаграммы сигналов на выходе первого портового блока 2; на фиг.2б - на выходе второго порогового блока 2; на фиг.2в - на выходе первого элемента И 4.

Первый 1 и второй 12 исполнительные элементы могут быть выполнены в виде обмоток реле, которые непосредственно или через соответствующие усилители соединены, соответственно, с выходом третьего порогового блока 17 и с выходом четвертого элемента ИЛИ 27. Первый 2 и второй 3 пороговые блоки могут быть выполнены в виде аналоговых компараторов с нулевым порогом, а третий 17, четвертый 25 и пятый 26 пороговые блоки - в виде цифровых компараторов. Первый 10, второй 11 и третий 24 фильтры-усреднители могут быть выполнены в виде стандартных цифровых фильтров, содержащих регистр сдвига, информационный и тактовый входы и вход установки в ноль которого являются, соответственно, информационным, тактовым входом и входом установки в ноль фильтра-усреднителя, выходы регистра сдвига соединены через соответствующие им умножители на весовые коэффициенты с сумматором, выход которого являются выходом фильтра-усреднителя. Первый 5 и второй 6 формирователи коротких импульсов формируют на своем выходе импульсы заданной длительности при перепаде их входных напряжений с уровня логического нуля на уровень логической единицы и с выхода логической единицы на уровень логического нуля, соответственно.

Остальные блоки устройства являются стандартными блоками электротехники. Цепи питания блоков, кроме цепи питания одновибратора 18, на фиг.1 опущены как несущественные.

Работает реле разности фаз следующим образом.

При включении устройства питание подается на все его элементы, в том числе, на вход запуска одновибратора 18, который вырабатывает импульс, поступающий на входы установки в ноль первого 10 и второго 11 фильтров-усреднителей, через, соответственно, первый 7 и второй 8 элементы ИЛИ - на входы установки в ноль первого 14 и второго 15 счетчиков импульсов, а также на вход запуска ГТИ 19 и на R-вход RS-триггера 20.

Сигналы напряжений внешнего генератора Uг и сети Uc поступают на входы второго 3 и первого 2 пороговых блоков, соответственно, которые формируют из них последовательности импульсов, представленные на фиг.2а и фиг.2б, соответственно. На выходе первого элемента И 4 сигнал логической единицы формируется в интервале совпадения этих импульсов (фиг.2в). В пределах интервалов совпадения первый счетчик 14 суммирует импульсы с выхода первого элемента И 4 и его содержимое за интервал периода изменения напряжения сети будет пропорционально интервалу совпадения импульсов с выходов первого 2 и второго 3 пороговых блоков, т.е. характеризовать степень согласования фаз напряжений сети и генератора.

По переднему фронту импульса (фиг.2а) первый формирователь 5 формирует короткий импульс, по которому содержимое первого счетчика 14 переписывается в первый фильтр-усреднитель 10, в котором формируется усредненное значение интервалов совпадения импульсов (фиг.2а и фиг.2б), характеризующее усредненное значение степени согласования фаз напряжений сети и генератора.

В начале работы реле разности фаз по сигналу одновибратора 18, который подается на вход третьего элемента ИЛИ 9, RS-триггер 20 устанавливается в нулевое состояние и переводится в единичное состояние по короткому импульсу с выхода первого формирователя 5 коротких импульсов, который также подается на тактовый вход второго фильтра-усреднителя 11 и через малую задержку во втором элементе ИЛИ 8 - на вход установки в ноль второго счетчика 15 импульсов. По импульсу с выхода второго формирователя 6 RS-триггер 20 переводится в нулевое состояние. Следовательно, содержимое второго счетчика 15 импульсов будет пропорционально длительности импульса фиг.2а и во втором фильтре-усреднителе 11 будет формироваться текущая усредненная оценка длительности половины периода напряжения. Сигнал с выхода первого фильтра-усреднителя 10 делится в делителе 16 на сигнал с выхода второго фильтра-усреднителя. На выходе делителя 16 формируется сигнал, пропорциональный относительной величине сдвига фазы напряжения генератора относительно напряжения сети. Если степень совпадения фаз не достаточно высокая, то на выходе третьего порогового блока 17 формируется уровень логической единицы, что приводит к срабатыванию первого исполнительного элемента 1.

Кроме того, сигналы с выхода делителя 16 поступают в первый регистр 21 памяти, а через интервал срабатывания первого формирователя 5 коротких импульсов передвигаются во второй регистр сдвига 22. Следовательно, на выходе блока 23 вычитания формируются оценки приращения (убывания) величины относительно сдвига фазы напряжений сети и генератора, которые усредняются в третьем фильтре-усреднителе 24. Эти усредненные оценки сравниваются в четвертом пороговом блоке 25 с верхним допустимым уровнем скорости изменения, с в пятом пороговом блоке 26 - с нижним допустимым уровнем скорости изменения. При выходе за допустимые пределы срабатывает второй исполнительный элемент 12.

Таким образом, благодаря введенным усовершенствованиям расширяются функциональные возможности устройства, поскольку обеспечивается реакция реле на степень согласования фаз напряжений сети и генератора и скорость ее изменения. При этом благодаря тому, что формируется относительная величина сдвига фаз, то реле буде некритично к абсолютным значениям частоты сети и генератора.

Источники информации

1. Электротехнический справочник, в 4-х томах, т.2. Электротехнические изделия и устройства. Под общей редакцией В.Г.Герасимова и др. - М.: Издательство МЭИ, 1998 г., с.390, рис. 35.10.

2. Андреев В.А. Релейная защита и автоматика систем электроснабжения. - М.: Высшая школа, 1991, с.355, рис. 12.16 (прототип).

3. Букреев и др. Микроэлектронные схемы цифровых устройств. - М.: Советское радио, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2237312C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2011 |

|

RU2484547C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2240620C1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2002 |

|

RU2213387C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2016 |

|

RU2639891C2 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2240621C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2016 |

|

RU2636750C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2241273C1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

| РЕЛЕ ЧАСТОТЫ | 2003 |

|

RU2239905C1 |

Изобретение относится к электротехнике и может быть использовано в устройствах релейной защиты, например в качестве реле разности фаз напряжений сети и генератора. Технический результат заключается в расширении функциональных возможностей. Для этого реле разности фаз содержит пять пороговых блоков, два элемента И, два счетчика импульсов, четыре элемента ИЛИ, RS-триггер, два исполнительных элемента, генератор тактовых импульсов, одновибратор, два формирователя коротких импульсов, три фильтра-усреднителя, делитель, блок вычитания, два регистра памяти, при этом вход первого порогового блока является входом напряжения сети, вход второго порогового блока является входом напряжения генератора, а вход одновибратора является входом запуска реле разности фаз. 2 ил.

Реле разности фаз, содержащее первый и второй исполнительные элементы и первый пороговый блок, отличающееся тем, что введены первый элемент И, первый и второй входы которого соединены, соответственно, с выходом первого порогового блока, вход которого является входом напряжения сети, и второго порогового блока, вход которого является входом напряжения генератора, первый и второй формирователи коротких импульсов, входы которых соединены с выходом первого порогового блока, первый, второй и третий элементы ИЛИ, первый, второй и третий фильтры-усреднители, второй элемент И, первый и второй счетчики импульсов, счетные входы которых соединены с выходами, соответственно, первого и второго элементов И, входы установки в ноль соединены с выходами первого и второго элементов ИЛИ, соответственно, а выходы соединены с информационными входами первого и второго фильтров-усреднителей, соответственно, последовательно соединенные делитель, первый и второй входы которого соединены с выходами первого и второго фильтров-усреднителей, соответственно, и третий пороговый блок, выход которого соединен с входом первого исполнительного элемента, последовательно соединенные одновибратор, вход которого является входом запуска реле разности фаз, и генератор тактовых импульсов, выход которого соединен с третьим входом первого элемента И и с входом второго элемента И, а также RS-триггер, R-вход которого соединен с выходом третьего элемента ИЛИ, S-вход соединен с выходом первого формирователя коротких импульсов, с тактовыми входами первого и второго фильтров-усреднителей и с первыми входами первого и второго элементов ИЛИ, а выход соединен со вторым входом второго элемента И, первый регистр памяти, информационный вход которого соединен с выходом делителя, второй регистр памяти, информационный вход которого соединен с выходом первого регистра памяти, тактовый вход соединен с тактовым входом первого регистра памяти и с выходом первого формирователя коротких импульсов, а вход установки в ноль второго регистра памяти соединен с входом установки в ноль первого регистра памяти и с выходом одновибратора, блок вычитания, первый и второй входы которого соединены, соответственно, с выходом первого регистра памяти и с выходом второго регистра памяти, а выход соединен с информационным входом третьего фильтра-усреднителя, тактовый вход которого соединен с выходом первого формирователя коротких импульсов, а вход установки в ноль соединен с выходом одновибратора, четвертый и пятый пороговые блоки, входы которых соединены с выходом третьего фильтра-усреднителя, а также четвертый элемент ИЛИ, первый и второй входы которого соединены с выходами, соответственно, четвертого и пятого пороговых блоков, а выход соединен с входом второго исполнительного элемента, при этом выход одновибратора соединен со вторыми входами первого и второго элементов ИЛИ, с первым входом третьего элемента ИЛИ и с входами установки в ноль первого и второго фильтров-усреднителей, а выход второго формирователя коротких импульсов соединен со вторым входом третьего элемента ИЛИ.

| АНДРЕЕВ В.А | |||

| Релейная защита и автоматика систем электроснабжения | |||

| - М.: Высшая школа, 1991, с.355 | |||

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1992 |

|

RU2027245C1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| US 3710189, 09.01.1973. | |||

Авторы

Даты

2004-11-27—Публикация

2003-06-03—Подача