Изобретение относится к области электросвязи и вычислительной техники, а конкретнее к области криптографических способов и устройств для защиты информации, передаваемой по телекоммуникационным сетям.

В совокупности признаков заявляемого способа используются следующие термины:

- операционный блок - электронная схема, выполняющая некоторое преобразование блоков двоичных данных, называемых двоичными векторами; операционный блок содержит информационный вход, на который подаются преобразуемые двоичные вектора Х=(x1, х2, ... , хn), и выход, на котором формируются преобразованные двоичные вектора Y=(y1, y2, ... , yn); преобразование, осуществляемое операционным блоком может быть выражено аналитически в виде Y=F(X);

- двоичный вектор - это некоторая последовательность нулевых и единичных битов, например (0101101011); двоичному вектору может быть сопоставлено численное значение, которое определяется однозначно структурой двоичного вектора, если считать, что позиция каждого бита соответствует двоичному разряду; двоичный вектор Х будем обозначать большими латинскими буквами, а биты, являющиеся его компонентами - малыми латинскими буквами, следующим образом Х=(x1, х2, ... , хn).

- операция конкатенации - операция объединения двоичных векторов, в результате которой формируется новый двоичный вектор, длина которого равна сумме длин двоичных векторов, над которыми осуществляется операция конкатенации; операцию конкатенации будем обозначать следующим образом: Z=(X, Y), где Х и Y - двоичные вектора, над которыми осуществляется операция конкатенации; например, при Х=(x1, х2, ... , хn) и Y=(y1, y2, ... , yk) для Z=(X, Y) имеем Z=(x1, x2, ... , xn, y1, y2, ... , yk);

- операнд - преобразуемый двоичный вектор;

- вес Хемминга - число единичных битов, содержащихся в двоичном векторе;

- управляемый операционный - блок операционный блок, содержащий дополнительный вход, называемый управляющим входом, на который подается управляющий двоичный вектор V=(ν 1,ν 2, ... , ν n), задающий конкретный вариант функции преобразования F; зависимость F от V обозначается индексом, а именно, в виде f(V); аналитическая запись преобразования выполняемого управляемым операционным блоком имеет вид Y=F(V)(X);

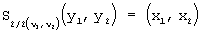

- управляемый элемент - это типовой электронный узел, снабженный t-разрядными информационным входом и выходом, w-разрядным управляющим входом, где t=2, 3 и w=1, 2, и используемый для построения управляемых операционных блоков; управляемый элемент представляет собой некоторый элементарный управляемый операционный блок и обозначается в виде St/w, t и w - число разрядов информационного и управляющего входов, соответственно;

- управляемая операция - это операция, осуществляемая с помощью управляемого операционного блока, в частности операция, выполняемая над одним операндом под управлением некоторого двоичного вектора, называемого управляющим двоичным вектором и заключающаяся в формировании выходного двоичного вектора в зависимости от значения операнда и значения управляющего двоичного вектора; в формулах управляемую операцию будем обозначать записью F(V), где V - управляющий двоичный вектор;

- модификация управляемой операции - операция, соответствующая преобразованию операнда при фиксированном значении управляющего двоичного вектора V=V0;

- обратная управляемая операция (по отношению к некоторой данной управляемой операции) - это управляемая операция, все модификации которой F

- схемотехнические ресурсы - число активных элементов (например, транзисторов или типовых логических модулей), которые могут быть использованы для реализации, например, для аппаратной реализации алгоритма шифрования;

- схемотехническая сложность реализации - схемотехнические ресурсы, используемые для реализации соответствующей электронной схемы, например управляемого операционного блока.

Известны управляемые сумматоры, представляющие собой управляемые операционные блоки, реализующие управляемую двухместную операцию [Гуц Н.Д., Молдовян А.А., Молдовян Н.А. Гибкие аппаратно-ориентированные шифры на базе управляемых сумматоров // Вопросы защиты информации. 2000. №1. С.8-15] и используемые для повышения стойкости шифрования. Недостатком управляемых сумматоров является то, что для их реализации требуются значительные схемотехнические ресурсы. Более экономичным вариантом управляемых операционных блоков являются блоки управляемых перестановок [Гуц Н.Д., Изотов Б.В., Молдовян Н.А. Управляемые перестановки с симметричной структурой в блочных шифрах // Вопросы защиты информации. 2000. №4. С.57-64], реализующие управляемую перестановку битов преобразуемого двоичного вектора и используемые при построении устройств, предназначенных для шифрования двоичной информации. Использование управляемых операций обеспечивает повышение стойкости шифрования данных при использовании незначительных схемотехнических ресурсов. Однако устройство аналог реализует частный вариант управляемой операции, которая сохраняет вес Хемминга операнда, что ограничивает повышение эффективности шифрующего преобразования за счет применения управляемой операции.

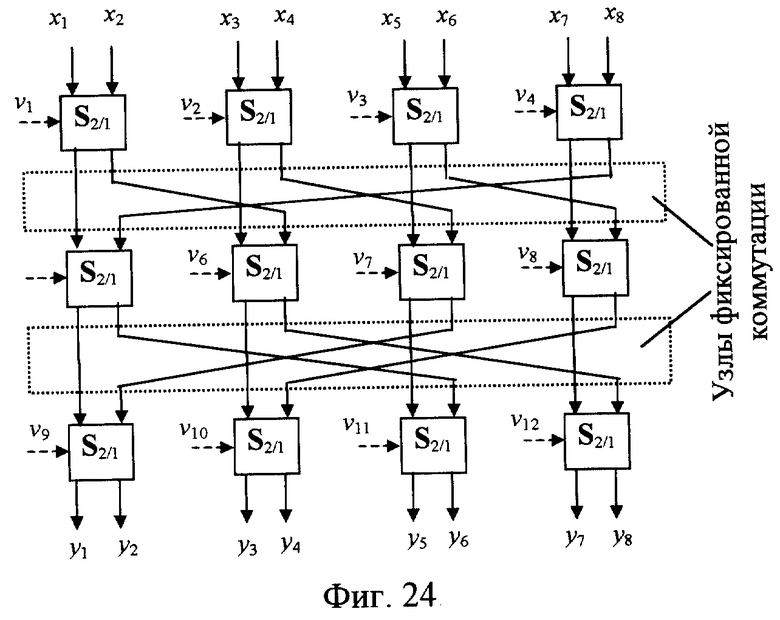

Наиболее близким по своей технической сущности к заявляемому управляемому операционному блоку является управляемый операционный блок, описанный в работе [Еремеев М.А., Молдовян Н.А. Синтез аппаратно-ориентированных управляемых подстановок над двоичными векторами большой длины//Вопросы защиты информации. 2001. №4. С.46-51] и построенный с использованием типовых управляемых элементов S2/1 (см. фиг.2а), содержащих двухразрядный информационный вход, двухразрядный выход и одноразрядный управляющий вход. На фиг.24 представлен частный вариант реализации управляемого операционного блока, построенного с использованием указанных управляемых элементов. В данном варианте управляемый операционный блок имеет 8-разрядный информационный вход, 8-разрядный выход и 12-разрядный управляющий вход. Проводники, передающие управляющие сигналы показаны пунктирной линией, а проводники, передающие информационные сигналы (т.е. биты преобразуемого двоичного вектора), - сплошной линией. Управляющие элементы образуют три активных каскада, каждый из которых состоит из четырех управляемых элементов. Входы верхнего (первого) активного каскада являются входами управляемого операционного блока. Выходы нижнего (последнего) активного каскада являются выходами управляемого операционного блока. Каждые два последовательных активных каскада между собой соединены посредством фиксированной коммутации соответствующих выходов предыдущего активного каскада с соответствующими входами последующего активного каскада. При изображении фиксированной коммутации на чертежах и фигурах фиксированная коммутация между соседними активными каскадами изображается непосредственно линиями, соответствующими соединительным проводникам, или в виде узла фиксированной коммутации, расположенного между соответствующими активными каскадами. Управляющие входы всех управляемых элементов составляют управляющий вход управляемого операционного блока. В общем случае устройство прототип представляет собой управляемый операционный блок, содержащий n-разрядный информационный вход, m-разрядный управляющий вход и s≥ 2 последовательных активных каскадов, состоящих из k=n/2 включенных управляемых элементов, причем совокупность информационных входов управляемых элементов i-го активного каскада, где i=1, 2, ... , s, образуют n-разрядный информационный вход i-го активного каскада и совокупность выходов управляемых элементов i-го активного каскада образуют n-разрядный выход i-того активного каскада. Кроме того, n-разрядный информационный вход первого активного каскада и n-разрядный выход s-го активного каскада являются, соответственно, n-разрядными информационным входом и выходом управляемого операционного блока. Причем совокупность управляющих входов всех активных каскадов является m-разрядным управляющим входом управляемого операционного блока, а каждый разряд n-разрядного выхода j-то активного каскада, где j=1, 2, ... , s-1, соединен с одним разрядом n-разрядного информационного входа (j+1)-го активного каскада.

Устройство прототип обеспечивает изменение веса Хемминга при преобразовании операнда, однако при аппаратной реализации с использованием широко распространенных программируемых логических матриц типа FPGA недостаточно эффективно используется потенциал, заложенный в данном типе программируемых устройств. Логическая матрица типа FPGA [Угрюмов Е.П. Цифровая схемотехника. - СПб, БХВ - Санкт-Петербург, 2000. - 518 с. (см. стр. 391-412)] представляет собой набор большого числа типовых логических модулей, основной частью каждого из которых являются две логические ячейки с четырехразрядным входом и одноразрядным выходом. Одна логическая ячейка позволяет реализовать произвольную булевую функцию от четырех переменных [Угрюмов Е.П. Цифровая схемотехника. - СПб, 2000. - С.402]. При реализации одного управляемого элемента S2/1, содержащего двухразрядный информационный вход, двухразрядный выход и одноразрядный управляющий вход, используется один типовой логический модуль. Это обусловлено тем, что преобразование, выполняемое управляемым элементом S2/1, задается двумя булевыми функциями от трех переменных, для реализации которых необходимо использовать две типовые логические ячейки, содержащиеся в одном типовом логическим модуле. Однако одна ячейка может реализовать произвольную булевую функцию от четырех переменных, т.е. один типовой логический модуль может выполнить существенно более сложное преобразование, чем преобразование, задаваемое управляемым элементом S2/1, а именно, преобразование, описываемое двумя булевыми функциями от четырех переменных. Таким образом, недостатком прототипа при аппаратной реализации с использованием логических программируемых логических матриц типа FPGA является относительно невысокая скорость обработки данных, обусловленная недостаточно эффективным использованием ресурсов типовых логических ячеек.

В основу изобретения положена задача разработать управляемый операционный блок, при реализации которого более эффективно используется потенциал логических ячеек типовых логических модулей программируемых логических матриц типа FPGA, благодаря чему при заданной криптостойкости снижается количество используемых логических ячеек, что ведет к повышению скорости обработки данных.

Решение поставленной задачи достигается тем, что в управляемом операционном блоке, снабженном n-разрядными информационным входом и выходом, где n≥ 4, m-разрядным управляющим входом, где m≥ 4, и содержащий s≥ 2 активных каскадов, i-й активный каскад, где i=1,2, ... , s, содержит k≥ 2 управляемых элементов, каждый из которых снабжен информационным и управляющим входами и выходом, совокупности информационных входов и выходов управляемых элементов i-го активного каскада и совокупность их управляющих входов являются, соответственно, n-разрядными информационными входом и выходом и управляющим входом i-го активного каскада, каждый разряд n-разрядного выхода j-го активного каскада, где j=1,2, ... ,s-1, подключен к одному из разрядов n-разрядного информационного входа (j+1)-го активного каскада, причем n-разрядный информационный вход первого активного каскада, n-разрядный выход s-го активного каскада и совокупность управляющих входов всех активных каскадов являются, соответственно, n-разрядным информационным входом, n-разрядным выходом и m-разрядным управляющим входом управляемого операционного блока, новым, согласно изобретению, является то, что, по крайней мере, один активный каскад состоит из управляемых элементов, каждый из которых снабжен t-разрядными информационными входом и выходом, где t=2,3, w-разрядным управляющим входом, где w=1,2, причем, по крайней мере, для одного управляемого элемента выполнено условие w+t=4, а каждый разряд управляющих входов управляемых элементов, содержащихся в активных каскадах, соединен с одним из разрядов m-разрядного управляющего входа управляемого операционного блока.

Благодаря такому решению, обеспечивается более полное использование потенциала программируемых логических матриц типа FPGA, обусловливаемое тем, что управляемый элемент с двухразрядным входом реализуется с использованием двух типовых логических ячеек программируемых логических матриц типа FPGA, каждая из которых реализует булевую функцию от четырех переменных. Последнее приводит к существенному повышению эффективности преобразования, осуществляемого с помощью управляемого элемента, и эффективности управляемого операционного блока, построенного на основе таких управляемых элементов. Это обеспечивает повышение эффективности управляемой операции как криптографического примитива, что позволяет уменьшить число раундов шифрования и тем самым обеспечивает снижение используемых схемотехнических ресурсов при аппаратной реализации на базе программируемых логических матриц типа FPGA и повышение скорости обработки данных.

Новым является также и то, по крайней мере, один из активных каскадов содержит g управляемых элементов, снабженных трехразрядными информационным входом и выходом и одноразрядным управляющим входом, где g является нечетным натуральным числом, удовлетворяющим условию 1≤ g&λτ; n/3, при нечетном n и четным натуральным числом, удовлетворяющим условию 1≤ g&λτ; n/3, при четном n&γτ; 6, и h управляемых элементов, снабженных двухразрядными информационным входом и выходом, причем h=(n-3g)/2.

Благодаря этому обеспечивается возможность построения управляемых операционных блоков с широким диапазоном соотношения размеров информационного и управляющего входов.

Новым является и то, что n является натуральным числом, кратным трем, и, по крайней мере, один из активных каскадов состоит из n/3 управляемых элементов, снабженных трехразрядными информационным входом и выходом и одноразрядным управляющим входом.

Благодаря этому обеспечивается однородность структуры управляемого операционного блока при числе разрядов информационного входа управляемого операционного блока, кратном трем.

Кроме того, новым является и то, что n является четным натуральным числом, и, по крайней мере, один из активных каскадов состоит из n/2 управляемых элементов, снабженных двухразрядными информационным входом и выходом и двухразрядным управляющим входом.

Также новым является то, что n является четным натуральным числом, и, по крайней мере, один из активных каскадов состоит из n/2 управляемых элементов, снабженных двухразрядными информационным входом и выходом и w-разрядным управляющим входом, причем, по крайней мере, один из управляемых элементов снабжен двухразрядным управляющим входом.

Последние два варианта заявляемого технического решения обеспечивают повышение числа различных потенциально возможных модификаций управляемой операции, что реализует один из механизмов повышения эффективности управляемой операции как криптографического примитива.

Заявляемое устройство поясняется чертежами, на которых показаны:

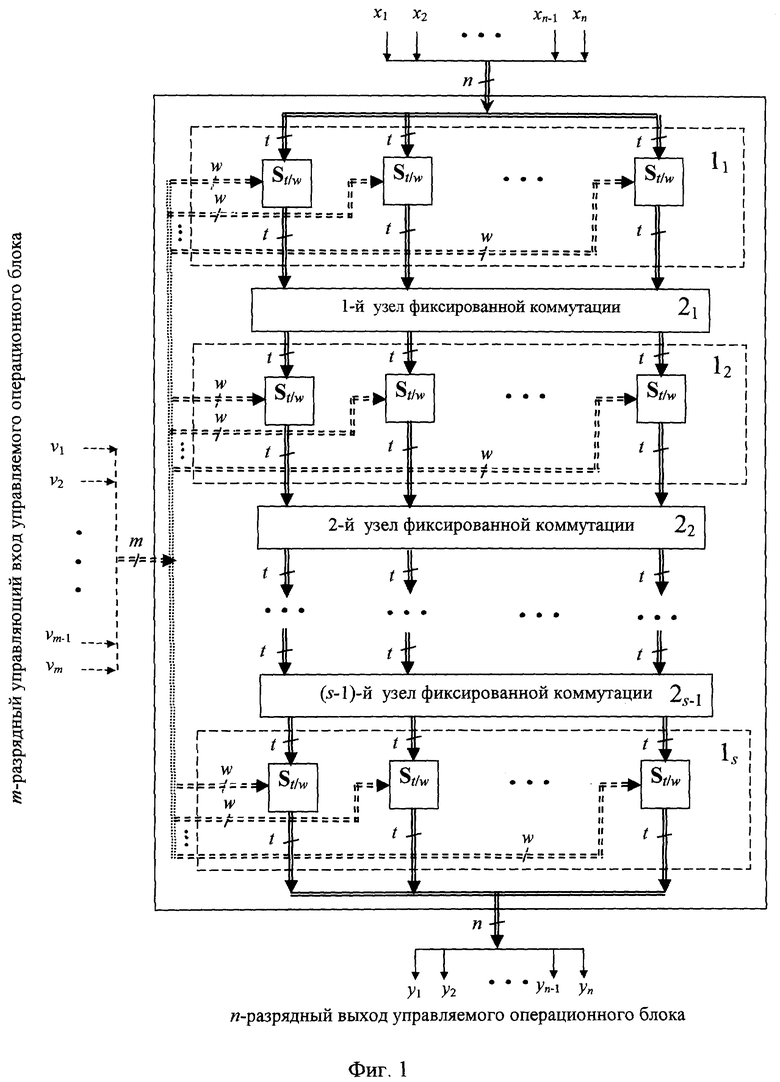

на фиг.1 - Общая схема заявленного управляемого операционного блока;

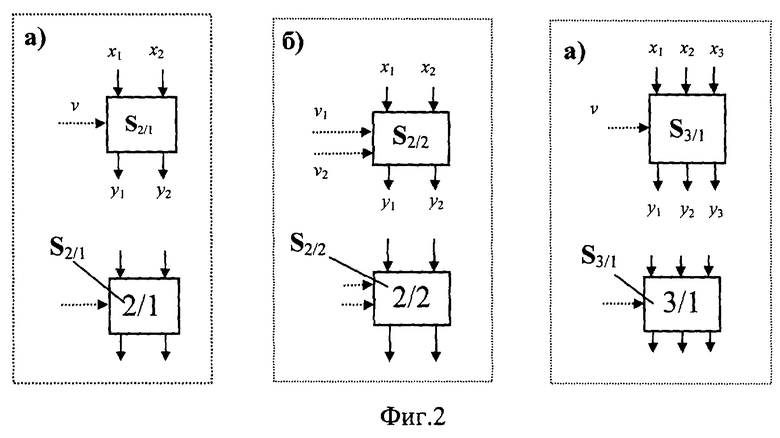

на фиг.2 - Типы управляемых элементов и их обозначения;

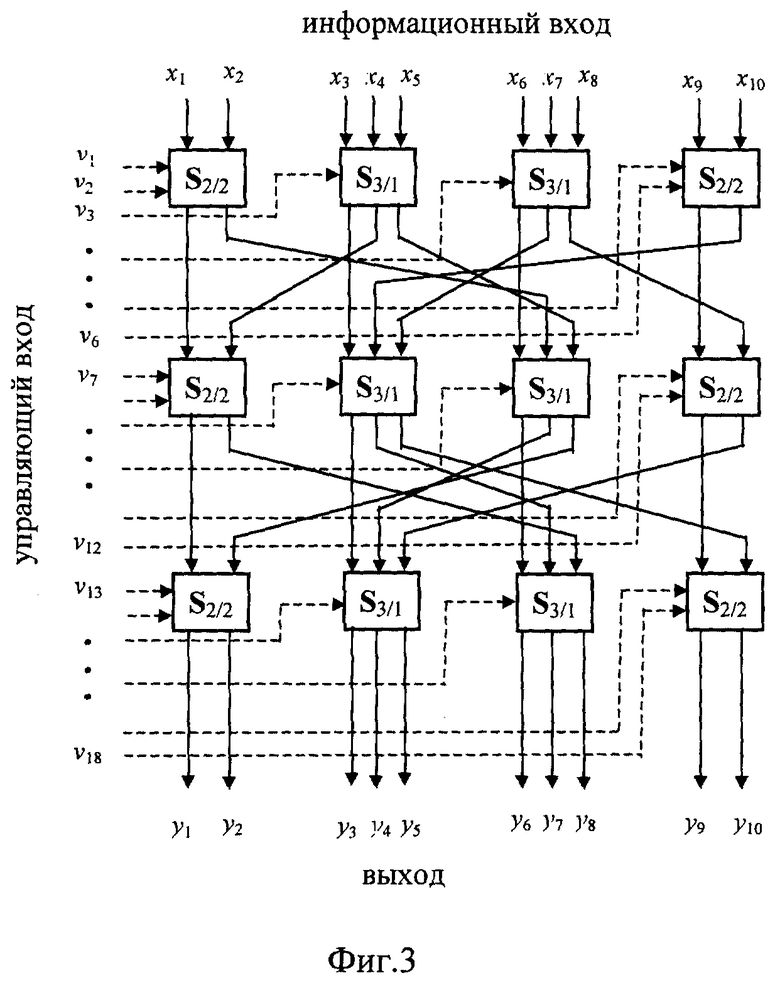

на фиг.3 - Вариант схемы управляемого операционного блока S10/18;

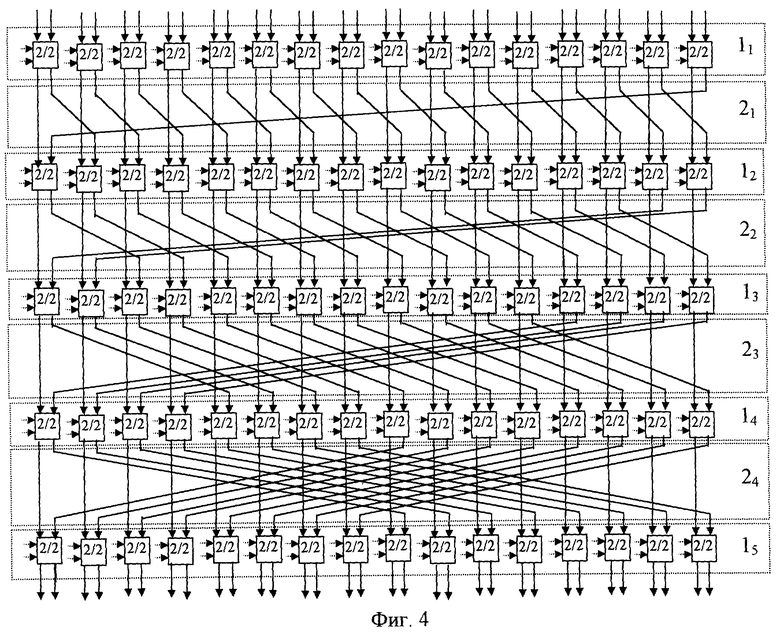

на фиг.4 - Вариант схемы управляемого операционного блока S32/160;

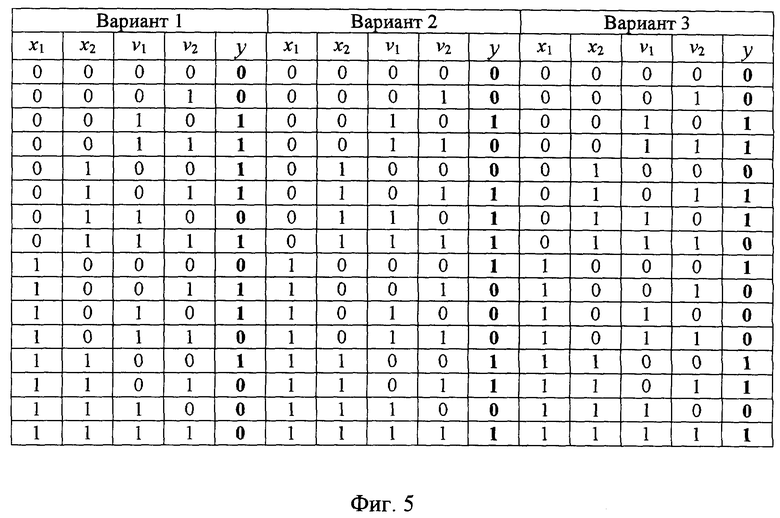

на фиг.5 - Таблицы истинности, задающие три варианта булевых функций от трех переменных;

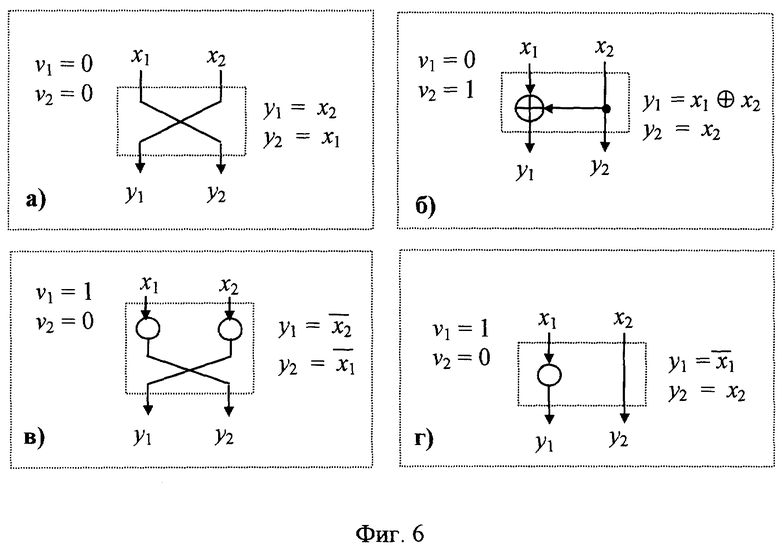

на фиг.6 - Варианты преобразований, осуществляемые управляемым элементом, описанным в примере 4, при четырех различных значениях управляющего вектора;

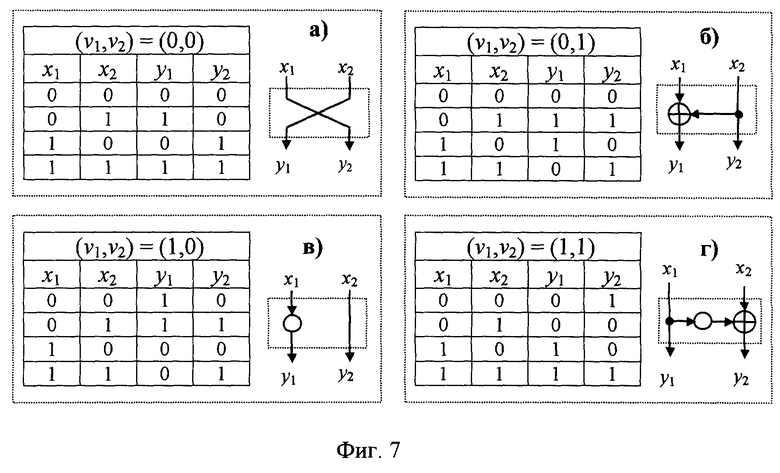

на фиг.7 - Варианты преобразований, осуществляемые управляемым элементом, описанным в примере 5;

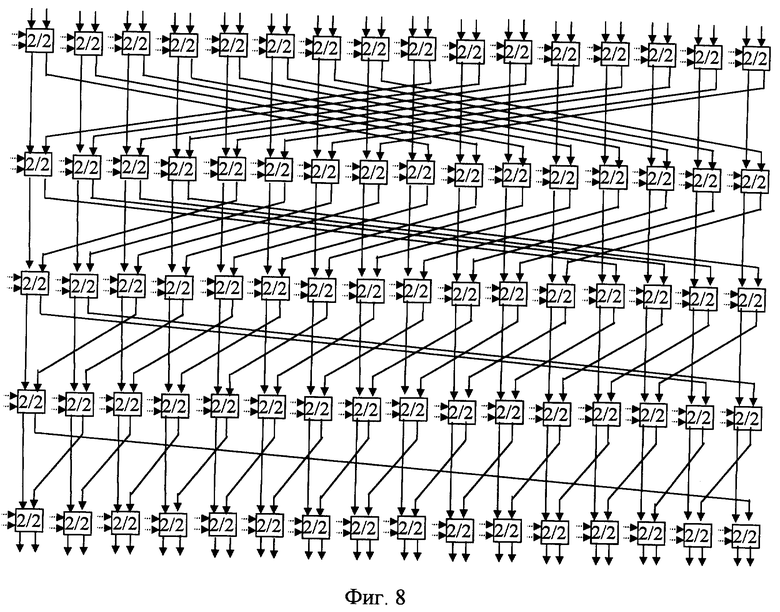

на фиг.8 - Схемы управляемого операционного блока S32/160;

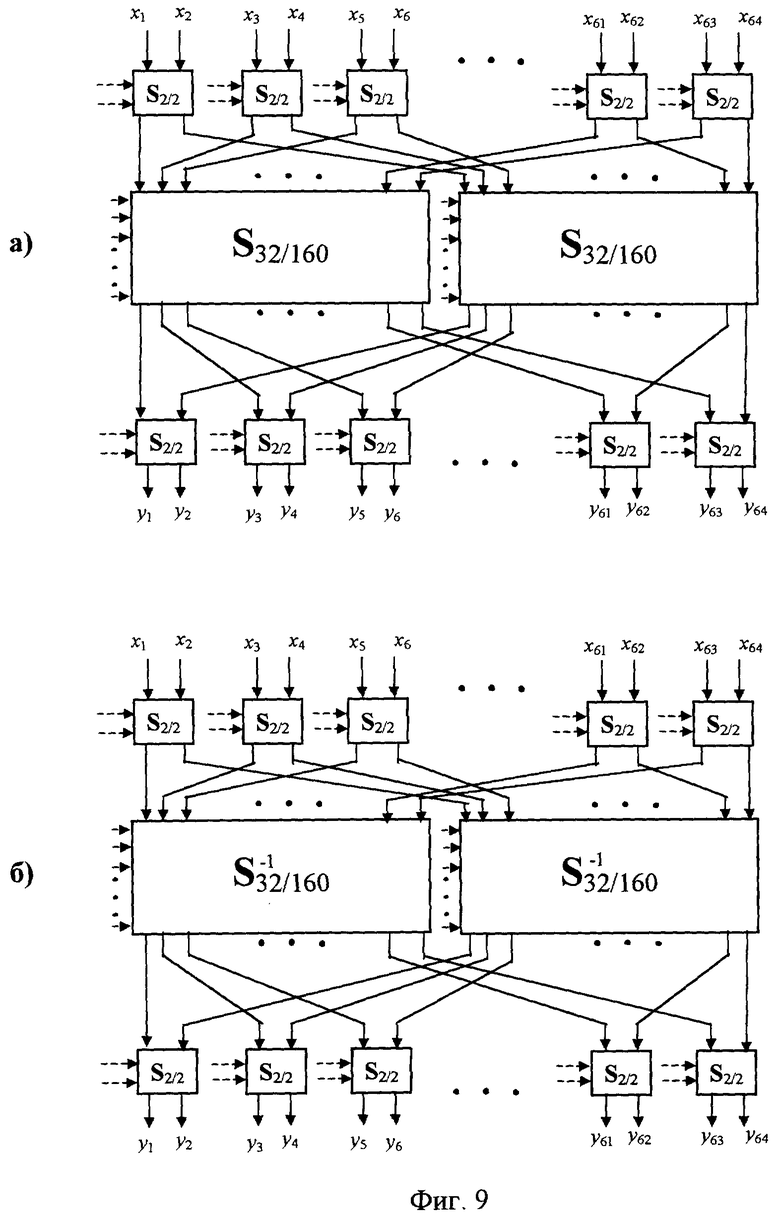

на фиг.9 - Вариант схемы управляемого операционного блока S64/448;

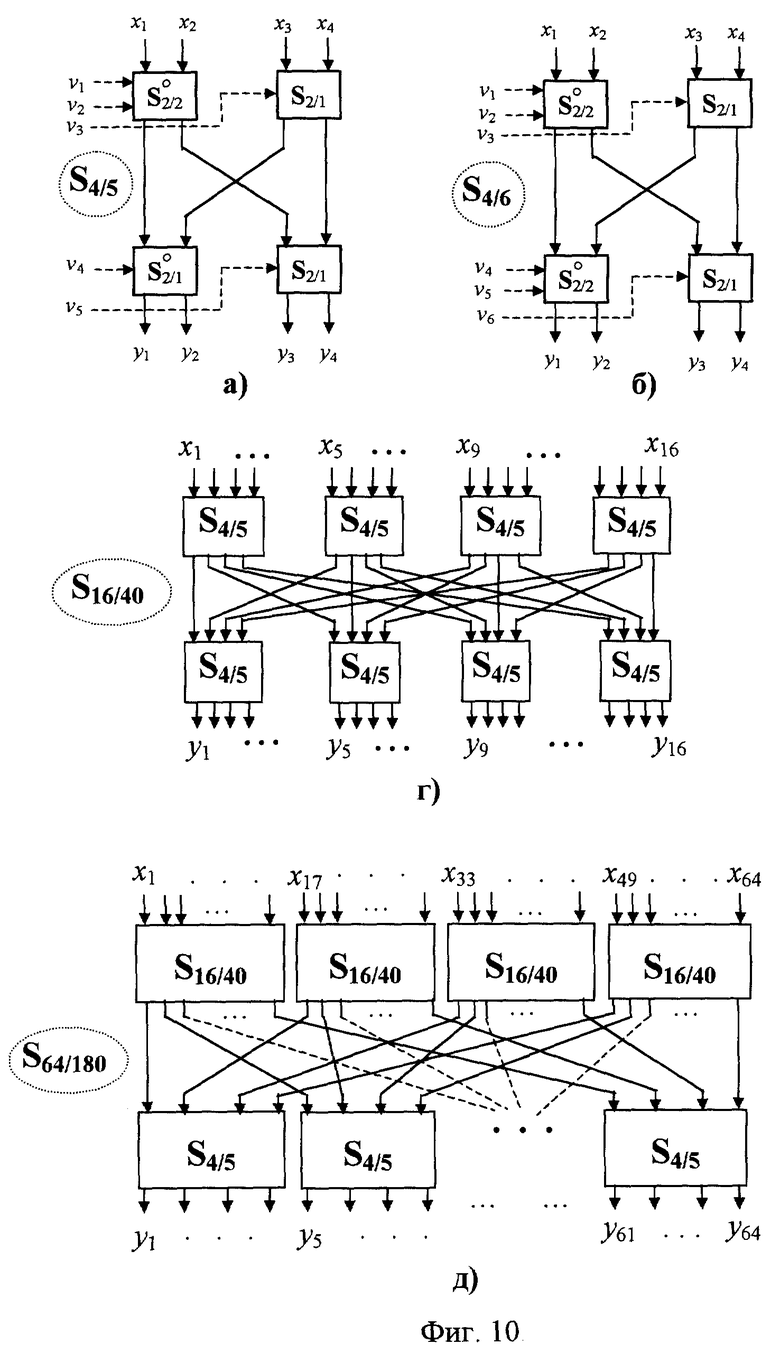

на фиг.10 - Вариант схемы управляемого операционного блока S64/180;

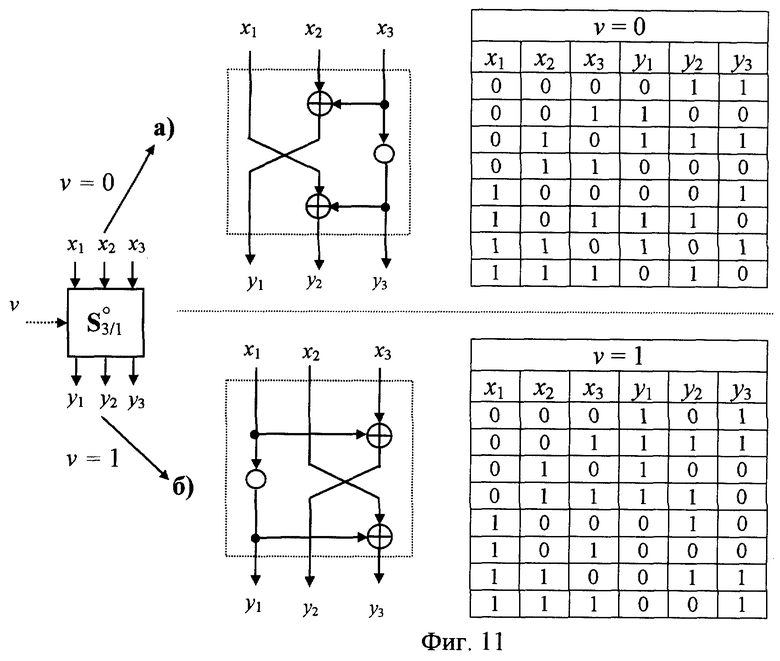

на фиг.11 - Вариант схемы управляемого элемента S3/1;

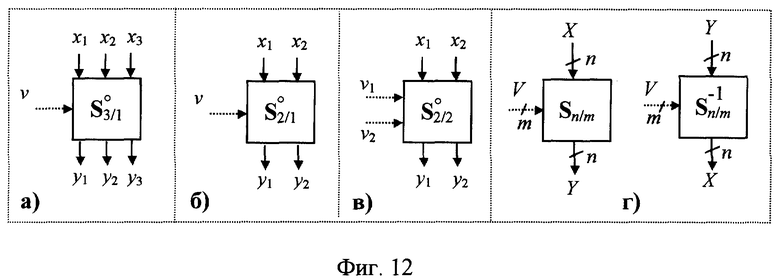

на фиг.12 - Обозначение управляемых элементов, являющихся инволюциями, и обозначение двух взаимно обратных управляемых операционных блоков;

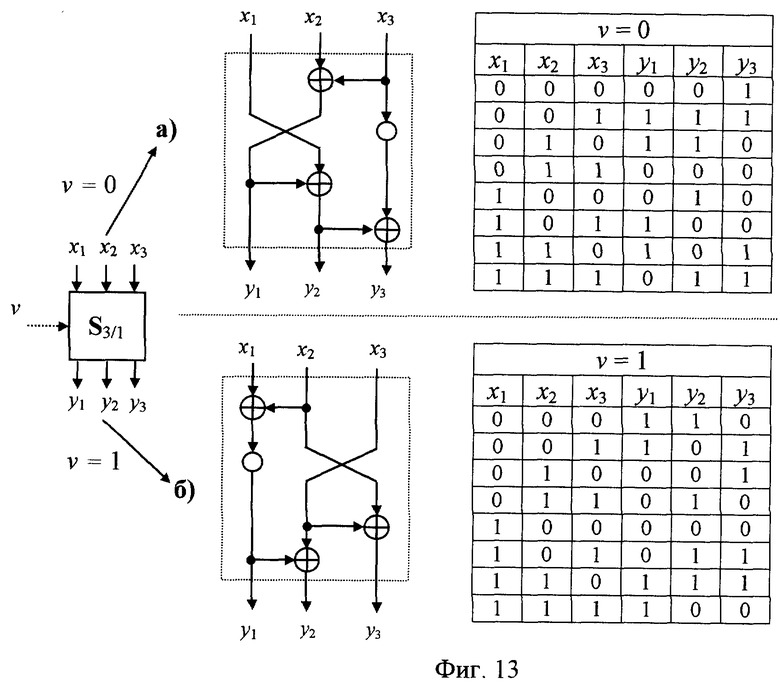

на фиг.13 - Вариант схемы управляемого элемента S3/1 общего типа;

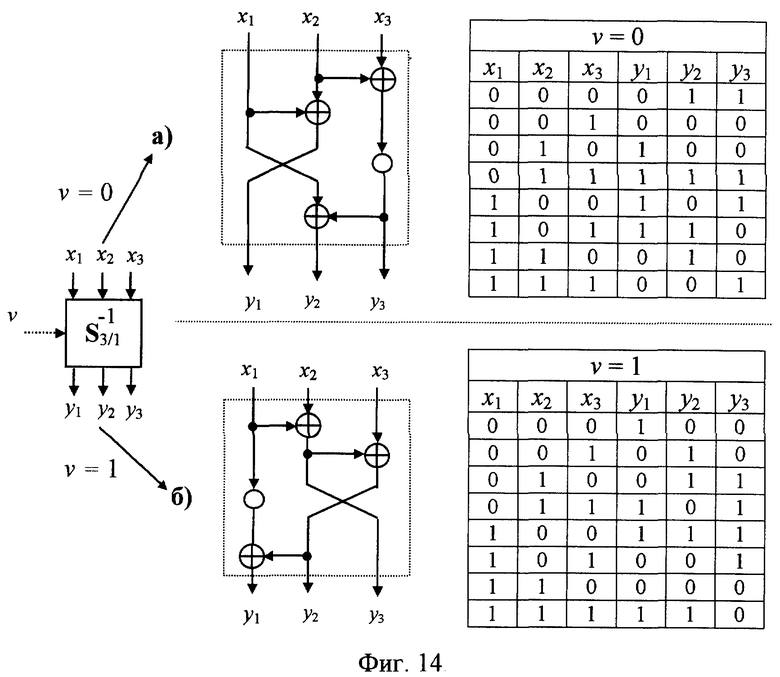

на фиг.14 - Вариант схемы управляемого элемента S

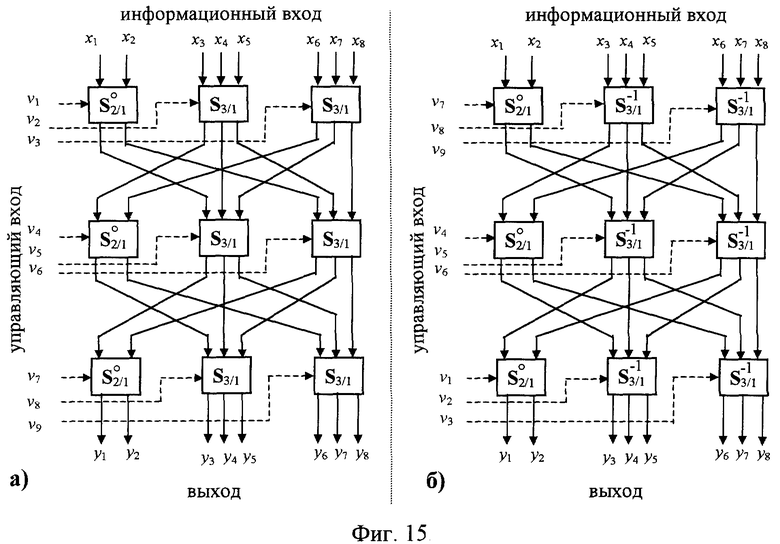

на фиг.15 - Вариант взаимно обратных управляемых операционных блоков S8/9 и S

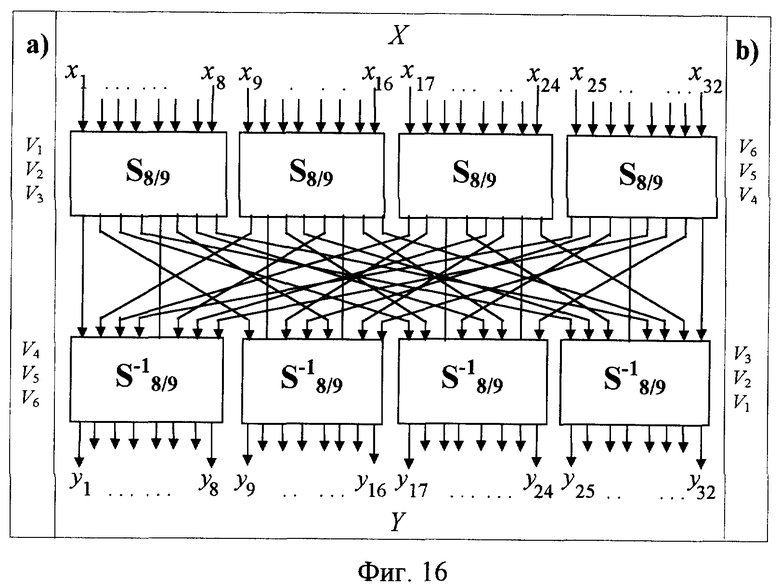

на фиг.16 - Вариант построения взаимно обратных управляемых операционных блоков S32/72 и S

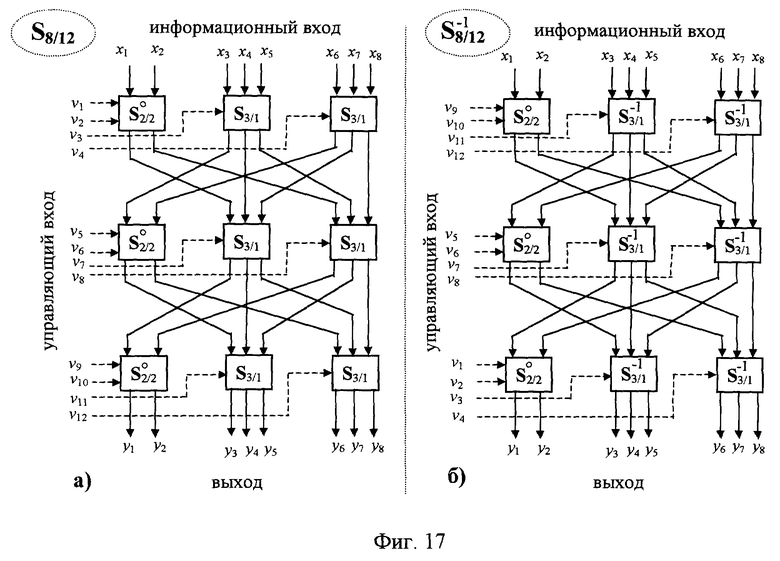

на фиг.17 - Вариант построения взаимно обратных управляемых операционных блоков S8/12 и S

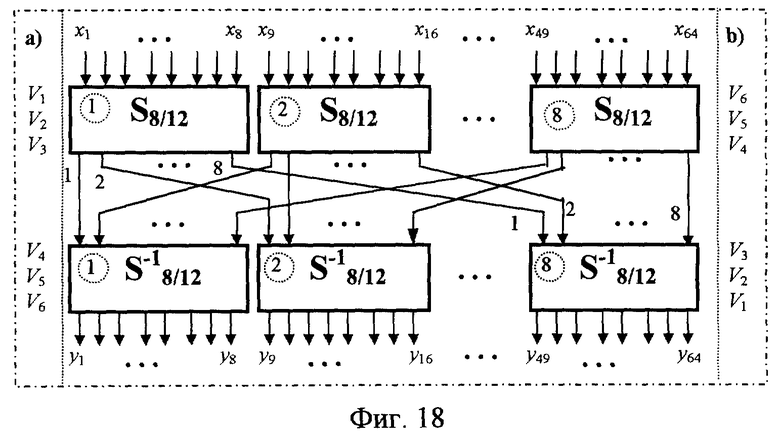

на фиг.18 - Вариант построения взаимно обратных управляемых операционных блоков S64/192 и S

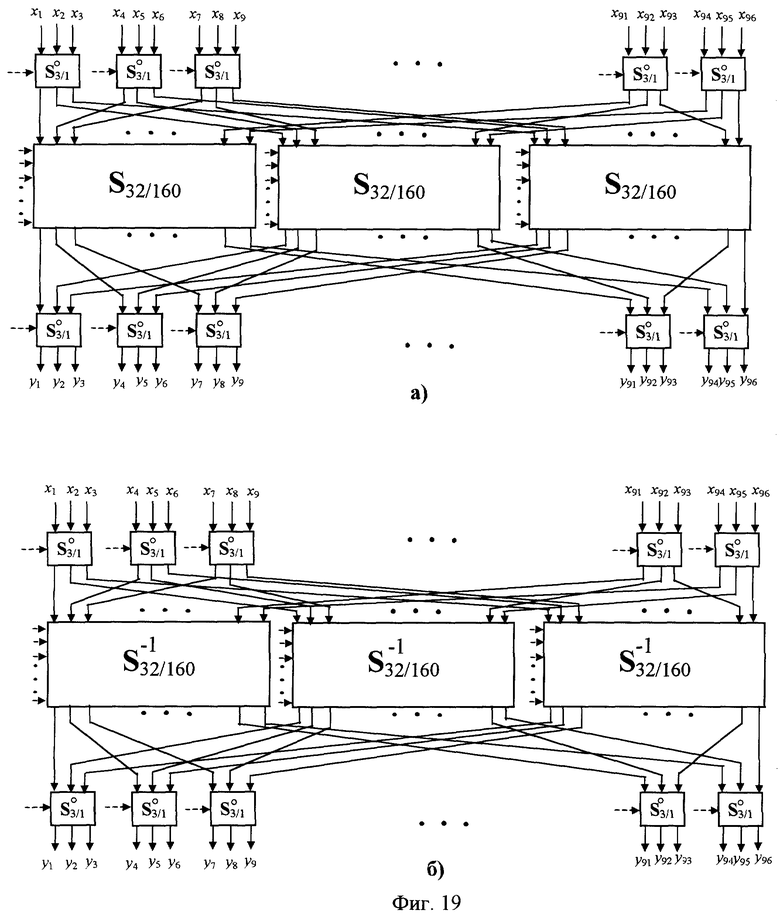

на фиг.19 - Вариант построения взаимно обратных управляемых операционных блоков S96/544 и S

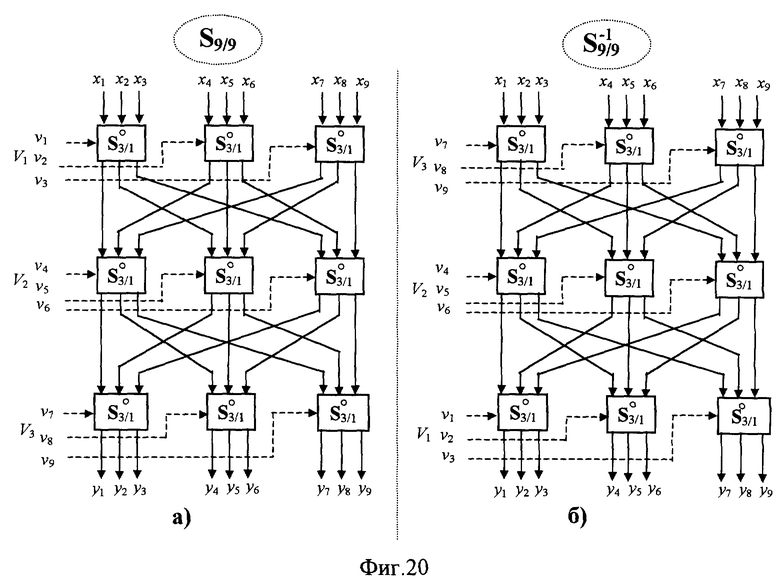

на фиг.20 - Вариант построения взаимно обратных управляемых операционных блоков S9/9 и S

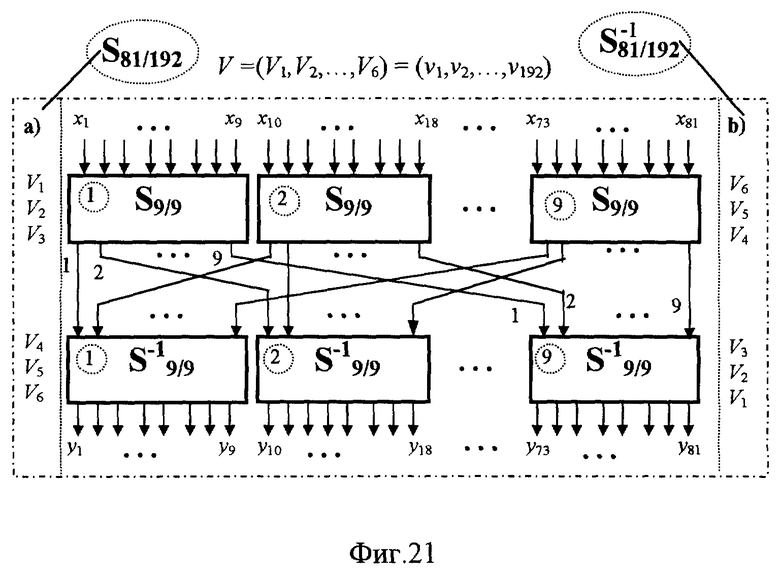

на фиг.21 - Вариант построения взаимно обратных управляемых операционных блоков S81/192 и S

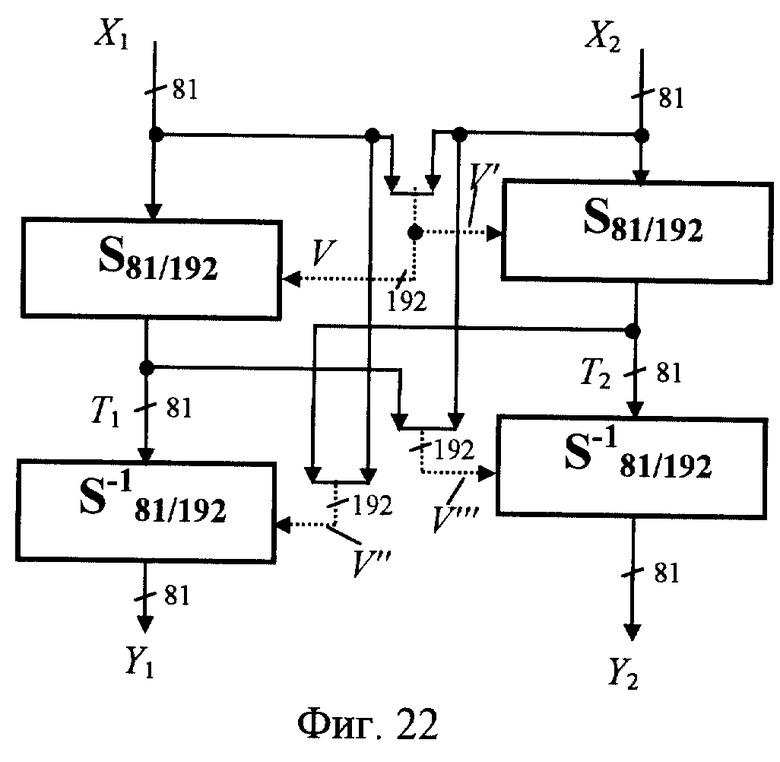

на фиг.22 - Вариант алгоритма одностороннего преобразования 192-битового блока данных;

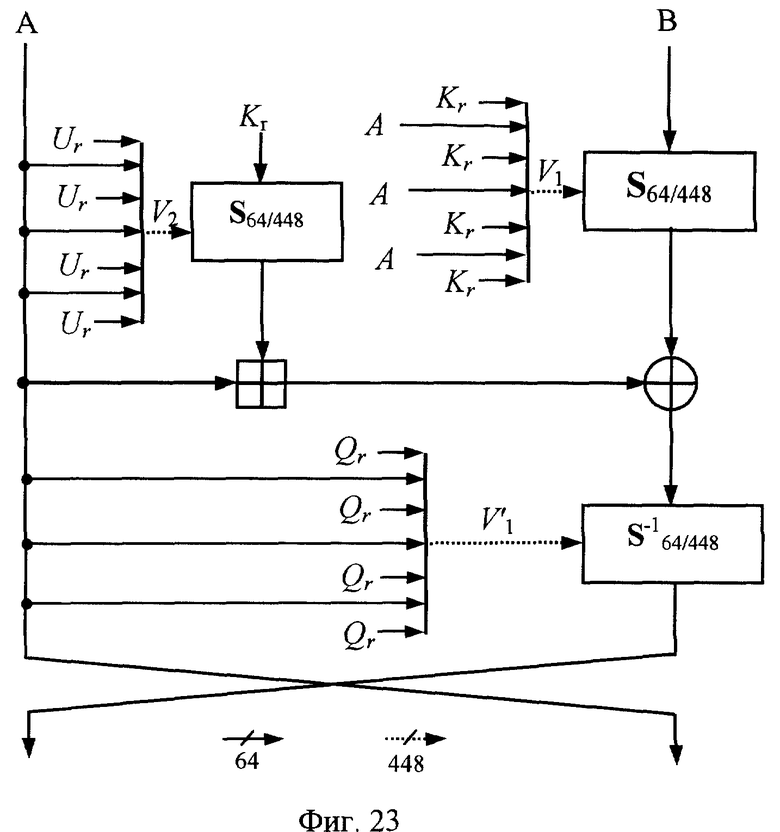

на фиг.23 - Вариант структуры одного раунда шифрования 128-битового алгоритма криптографического преобразования;

на фиг.24 - Прототип.

Обобщенная структура управляемого операционного блока, соответствующего заявляемому изобретению, представлена фиг.1, где х1, х2, ... , хn - биты преобразуемого двоичного вектора X, подаваемого на n-разрядный информационный вход управляемого операционного блока; у1, у2, ... , yn - биты выходного двоичного вектора Y, формируемого на n-разрядном выходе управляемого операционного блока; ν 1, ν 2, ... ν m - биты управляющего двоичного вектора V=(ν 1, ν 2, ... . ν m), подаваемого на m-разрядный управляющий вход управляемого операционного блока. В общем виде управляемый операционный блок представляет собой s последовательных активных каскадов 11, 12, ... , 1s, соединенных между собой с помощью узлов фиксированной коммутации 21, 22, ... , 2s-1, выполненных в виде разводки проводников, каждый из которых соединяет один из выходов одного их управляемых элементов предыдущего активного каскада с одним из информационных входов одного их управляемых элементов последующего активного каскада. В общем случае в каждом активном каскаде содержатся управляемые элементы трех типов S2/1, S2/2 и S3/1, которые показаны прямоугольниками с общим обозначением управляемого элемента St/w. При этом в разных активных каскадах данные управляемые элементы могут содержаться в различных сочетаниях. В зависимости от четности числа разрядов информационного входа n число содержащихся управляемых элементов типа S3/1 g является четным или нечетным, что обеспечивает соответствие суммарного числа разрядов входов всех управляемых элементов числу разрядов информационного входа активного каскада и управляемого операционного блока в целом. При нечетном n число g является нечетным, причем g удовлетворяет условию 1≤ g&λτ; n/3. При четном n&γτ; 6 число g является четным, причем g удовлетворяет условию 1≤ g<n/3. Если g≤ n/3, то активный каскад содержит h управляемых элементов типа S2/w, где w=1, 2, причем h=(n-3g)/2. В частном случае при произвольном четном значении n активный каскад может включать только управляемые элементы типа S2/2, число которых составляет n/2. В другом частном случае при произвольном значении n, кратном трем, активный каскад может включать только управляемые элементы типа S3/1, число которых составляет n/3. Возможны также частные случаи, соответствующие произвольному четному значению n, в которых активный каскад включает управляемые элементы типов S2/1 и S2/2, число общее число которых составляет n/2.

Совокупность всех информационных входов управляемых элементов первого каскада образуют n-разрядный информационный вход управляемого операционного блока, совокупность всех выходов управляемых элементов последнего активного каскада образуют n-разрядный выход управляемого операционного блока, а совокупность всех разрядов управляющих входов управляемых элементов всех активных каскадов образуют m-разрядный управляющий вход управляемого операционного блока.

На фиг.2б показан управляемый элемент, содержащий двухразрядный информационный вход, двухразрядный выход и двухразрядный управляющий вход, обозначаемый как S2/2. При этом на фигурах данный управляемый элемент обозначается прямоугольником, на котором приводится запись "S2/2" или "2/2". Повышение эффективности преобразования, осуществляемого с помощью управляемого элемента S2/2, реализуемого с помощью двух булевых функций от четырех переменных, обусловлено тем, что он реализует четыре различных модификации операции преобразования двухбитового входного двоичного вектора, тогда как управляемый элемент S2/1 реализует только две модификации подобной операции. Повышение эффективности случае связано с увеличением числа модификаций операций, реализуемых с помощью управляемого элемента.

На фиг.2в показан управляемый элемент, содержащий трехразрядный информационный вход, трехразрядный выход и одноразрядный управляющий вход, обозначаемый как S3/1, а на фигурах - прямоугольником с записью "S3/1" или "3/1". Повышение эффективности преобразования, осуществляемого с помощью управляемого элемента S3/1 реализуемого с помощью двух булевых функций от четырех переменных, обусловлено тем, что он реализует две модификации операции преобразования трехбитового входного двоичного вектора, тогда как управляемый элемент S2/1 реализует две модификации операции преобразования над двухбитовым входным двоичным вектором. Повышение эффективности в данном случае связано с увеличением размера преобразуемого входного двоичного вектора.

В общем случае управляемые элементы S2/2 реализуют 4 различных модификации управляемой операции, выполняемой над двухбитовым двоичным вектором (x1, x2), в зависимости от текущего значения двухбитового управляющего двоичного вектора (ν 1, ν 2) (см. фиг.2б). Каждый бит выходного двоичного вектора (y1, y2), получаемого в результате преобразования двоичного вектора (x1, x2) является булевой функцией от четырех переменных х1, x2, ν 1 и ν 2:, т.e. имеем y1=f1(x1, х2, ν 1, ν 2) и y2=f2(x1, x2, ν 1, ν 2). Всего существует Nf=216 различных булевых функций от четырех переменных. При реализации заявляемых управляемых операционных блоков в электронных устройствах, реализуемых с использованием логических матриц типа FPGA, произвольная булевая функция от четырех переменных может быть реализована с использованием одной логической ячейки. Поскольку имеются две логические ячейки в каждом типовом логическом модуле логической матрицы типа FPGA, то с помощью одного типового логического модуля могут быть реализованы две произвольные булевые функции от четырех переменных. Таким образом, используя один типовой логический модуль FPGA-матрицы, можно реализовать один управляемый элемент S2/2 произвольного типа. Число различных возможных управляемых элементов S2/2 составляет Ns=(Nf)2=232, из которых при построении управляемых операционных блоков для конкретных применений могут быть выбраны варианты управляемых элементов S2/2, обладающих нужными свойствами.

Варианты реализации управляемых элементов S2/1 с помощью двух булевых функций от трех переменных описаны в работе [Еремеев М.А., Молдовян Н.А. Синтез аппаратно-ориентированных управляемых подстановок над векторами большой длины // Вопросы защиты информации. 2001. №4. С.46-51].

В общем случае управляемые элементы S3/1 реализуют 2 различных модификации управляемой операции, выполняемой над трехбитовым двоичным вектором (х1, x2, х3), в зависимости от текущего значения управляющего бита v (см. фиг.2б). Каждый бит выходного двоичного вектора (y1, y2, y3) получаемого в результате преобразования двоичного вектора (х1, х2, х3) является булевой функцией от четырех переменных х1, х2, х3, и ν , т.е. имеем y1=f1(x1, x2, x3, ν ), у2=f2(x1, х2, x3, ν ) и y3=f3(х1, x2, x3, ν ). С использованием трех типовых логических модулей логической матрицы типа FPGA могут быть реализованы шесть произвольных булевых функций от четырех переменных. Таким образом, используя три типовых логических модуля FPGA-матрицы, можно реализовать два управляемых элемента S3/1 произвольного типа. При этом максимально используется потенциал логических ячеек. Число различных возможных управляемых элементов S3/1 составляет Ns=(Nf)3=248, из которых при построении управляемых операционных блоков для конкретных применений могут быть выбраны варианты управляемых элементов S3/1, обладающих свойствами, обеспечивающими высокую эффективность управляемых операционных блоков.

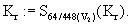

Управляемый операционный блок будем обозначать как Sn/m, где первый индекс обозначает разрядность информационного входа и выхода, а второй индекс, отделенный от первого разделителем “/” обозначает разрядность управляющего входа. На фиг.3 показан частный вариант построения управляемого операционного блока с 10-разрядным информационным входом, 10-разрядным выходом и 18-разрядным управляющим входом, построенный с использованием 6 управляемых элементов S2/2 и 6 управляемых элементов S3/1.

Для заданных значений n и m могут быть разработаны различные типы управляемых операционных блоков, отличающихся между собой набором используемых узлов фиксированной коммутации. В качестве узлов фиксированной коммутации управляемого операционного блока Sn/m могут быть взяты узлы фиксированной коммутации управляемых операционных блоков типа π n/m, построенных на основе управляемых элементов S2/1 и описанных в работе [Еремеев М.А., Молдовян Н.А. Синтез аппаратно-ориентированных управляемых подстановок над векторами большой длины//Вопросы защиты информации. 2001. №4. С.46-51], или узлы фиксированной коммутации, используемые в управляемых операционных блоках типа Рn/m, составленных с использованием рекурсивного механизма построения, описанного в работе [Гуц Н.Д., Изотов Б.В., Молдовян Н.А. Управляемые перестановки с симметричной структурой в блочных шифрах//Вопросы защиты информации. 2000. №4. С.57-64]. При заданном наборе узлов фиксированной коммутации различные управляемые операционные блоки строятся с использованием различных наборов управляемых элементов S2/1, S2/2 и S3/1. При этом каждый тип управляемых элементов может быть реализован в большом числе конкретных вариантов, используя булевые функции различного вида. В общем случае число различных модификаций управляемой операции, выполняемой операционным блоком Sn/m составляет 2m. Соотношение между n и m определяется числом активных каскадов в управляемом операционном блоке и соотношением управляемых элементов типа S2/z, где z=1, 2, и S3/1. Рассмотрим конкретные примеры построения управляемых операционных блоков Sn/m.

Пример 1. Управляемый операционный блок S10/18.

Данный пример показан на фиг.3в и соответствует построению управляемого операционного блока S10/18.

Пример 2. Управляемые операционные блоки типа S32/160.

Данный пример показан на фиг.4 и соответствует структурной схеме построения управляемого операционного блока S32/160, который состоит из пяти однотипных активных каскадов 11, 12, 13, 14, 15 и четырех узлов фиксированной коммутации 21, 22, 23, 24. Узлы фиксированной коммутации различаются между собой и выполнены таким образом, чтобы обеспечить влияние каждого входного бита x1, x2, ... , xn на каждый выходной бит y1, y2, ... , уn. Используя различные типы управляемых элементов S2/2, можно построить разные типы управляемых операционных блоков S32/160, сохраняя структурную схему, показанную на фиг.4. Ниже рассматриваются варианты булевых функций от четырех переменных и примеры построения управляемых элементов S2/2.

Пример 3. Варианты булевых функций типа у =f(x1, х2, ν 1, ν 2).

Данный пример показывает варианты булевых функций от четырех переменных y=f(x1, x2, ν 1, ν 2), которые могут быть использованы при построении управляемых элементов. Варианты таких функций, заданных с помощью таблиц истинности, показаны на фиг.5.

Пример 4. Построение управляемого элемента S2/2.

Данный пример показывает вариант построения управляемых элементов S2/2, в котором в качестве булевой функции y1=f1(x1, х2, ν 1, ν 2) используется первый вариант функции y=f(x1, х2, ν 1, ν 2) из примера 3, а в качестве булевой функции y2=f2(x1, х2, ν 1, ν 2) используется второй вариант функции y=f(x1, х2, ν 1, ν 2) из примера 3. Модификации управляемой операции, реализуемой управляемым элементом S2/2 при значениях управляющего двоичного вектора, равных (ν 1, ν 2)=(0, 0), (ν 1, ν 2)=(0, 1), (ν 1, ν 2)=(1, 0) и (ν 1, ν 2)=(1, 1), представлены в виде функциональной схемы и в виде аналитической записи на фигурах 6а, 6б, 6в и 6г, соответственно. На фиг.6в и 6г черта сверху над переменной в аналитической записи обозначает операцию логического отрицания, выполняемого над этой переменной. На фигурах операция логического отрицания обозначена знаком " ". Все четыре модификации управляемой операции, реализуемой управляемым элементом S2/2, являются инволюциями, т.е. задают преобразование, удовлетворяющее условию  , если

, если  , для каждого из четырех возможных значений двоичного вектора (ν 1, ν 2). При использовании других пар булевых функций могут быть построены управляемые элементы S2/2, которые не являются инволюциями, что при построении специальных типов управляемых операционных блоков предоставляет конструктивные преимущества, связанные с большим числом вариантов реализации управляемых элементов S2/2. При решении большого числа задач построения управляемых операционных блоков, ориентированных на применение в алгоритмах криптографического преобразования, достаточным является использование управляемых элементов S2/2, являющихся инволюциями, число конкретных вариантов которых является достаточно большим. Основным достоинством управляемых элементов, являющихся инволюциями, состоит в том, что с их использованием упрощается построение пар взаимно обратных управляемых операционных блоков.

, для каждого из четырех возможных значений двоичного вектора (ν 1, ν 2). При использовании других пар булевых функций могут быть построены управляемые элементы S2/2, которые не являются инволюциями, что при построении специальных типов управляемых операционных блоков предоставляет конструктивные преимущества, связанные с большим числом вариантов реализации управляемых элементов S2/2. При решении большого числа задач построения управляемых операционных блоков, ориентированных на применение в алгоритмах криптографического преобразования, достаточным является использование управляемых элементов S2/2, являющихся инволюциями, число конкретных вариантов которых является достаточно большим. Основным достоинством управляемых элементов, являющихся инволюциями, состоит в том, что с их использованием упрощается построение пар взаимно обратных управляемых операционных блоков.

Пример 5. Построение управляемого элемента S2/2.

Данный пример показывает вариант построения управляемого элемента S2/2, представленного четырьмя модификациями управляемой операции, которые описываются таблицами истинности и поясняются функциональными схемами на фиг.7. Модификации, реализуемые при значениях управляющего двоичного вектора (ν 1, ν 2)=(0, 0), (ν 1, ν 2)=(0, 1), (ν 1, ν 2)=(1, 0) и (ν 1, ν 2)=(1, 1) представлены на фиг.7а, 7б, 7в и 7г, соответственно.

Пример 6. Построение двух взаимно обратных управляемых операционных блоков S32/160 и S

Конкретный тип управляемого операционного блока S32/160 может быть получен на основе структурной схемы, показанной на фиг.4, в которой в качестве управляемых элементов S2/2 используются управляемые элементы, описанные в примере 4. Благодаря тому, что в блоке S32/160, соответствующем рассматриваемому примеру 6, используются управляемые элементы, осуществляющие преобразования, являющиеся инволюциями при любом значении управляющего двоичного вектора, можно легко построить управляемый операционный блок S

Пример 7. Построение управляемых операционных блоков S32/160 и S

Другой конкретный тип управляемого операционного блока S32/160, основанный на структурной схеме, показанной на фиг.4, может быть получен при использовании управляемых элементов S2/2, описанных в примере 5. Все модификации управляемой операции, задаваемой управляемым элементом примера 5, являются инволюциями, поэтому соответствующий обратный управляемый операционный блок S

Пример 8. Управляемые операционные блоки S64/448 и S

Управляемые операционные блоки с 64-битовым информационным входом S64/448 и S

Пример 9. Построение управляемых операционных блоков S4/5, S4/6, S16/40 и S64/180.

На фиг.10а и фиг.10б показано построение управляемых операционных блоков S4/6 и S4/5, в котором число активных каскадов равно двум, а набор включаемых управляемых элементов соответствует п.5 формулы изобретения. Данные операционные блоки сравнительно малого размера могут использоваться в качестве типовых узлов при построении управляемых операционных блоков произвольного размера. Пример использования блоков S4/5 для построения блоков S16/40 показан на фиг.10в. Блок S16/40 состоит из восьми блоков S4/5, расположенных в двух ярусах, каждый из которых состоит из четырех блоков S4/5. Блоки S4/5 нижнего яруса соединены с блоками верхнего яруса по принципу “каждый с каждым”. Пример использования блоков S4/5 и S16/40 для построения блоков S64/180 показан на фиг.10г, где верхний ярус представлен четырьмя блоками S16/40, а нижний - шестнадцатью блоками S4/5. Последние соединены с первыми по принципу “каждый с каждым”, который обеспечивает органическое единство блока S64/180 как единого целого.

Беря в качестве исходного узла блок S4/6 вместо блока S4/5, по аналогичным структурным схемам (см. фиг.10в и 10г) можно построить операционные блоки S16/48 и S64/228. Комбинируя различные сочетания управляемых элементов в составе активных каскадов управляемых операционных блоков, можно построить блоки Sn/m с произвольными соотношениями размера информационного и управляющего входов, что способствует выбору оптимизированных решений при построении устройств шифрования на основе заявляемого технического решения.

Пример 10. Построение управляемого элемента S3/1.

На фиг.11 показан вариант построения управляемого элемента S3/1, представленный таблицами истинности, описывающими зависимость выходных битов от входных при нулевом значении управляющего бита v (фиг.11а) и при единичном значении управляющего бита ν (фиг.11б). Данные две таблицы истинности полностью описывают три булевые функции y1=f1(x1, x2, x3, ν ), y2=f2(x1, х2, х3, ν ) и у3=f3(x1, х2, х3, ν ), с помощью которых три логических ячейки FPGA-матрицы реализуют данный вариант управляемого элемента S3/1. Схемы, описывающие преобразования, реализуемые данным вариантом управляемого элемента S3/1, при ν =0 (фиг.11а) и при ν =1 (фиг.11б), показывают, что управляемый элемент S3/1, соответствующий примеру 10, является инволюцией. В рассматриваемых далее схемах управляемые элементы, являющиеся инволюциями будем обозначать знаком "° ", используемым в качестве верхнего индекса: S° 3/1 (фиг.12а), S° 2/1 (фиг.11б), S° 2/2 (фиг.11в). Два взаимно обратных управляемых операционных блока, имеющих n-разрядный информационный вход и m-разрядный управляющий вход, где n 2 и m 1, будем обозначать как пару Sn/m и S

Пример 11. Построение взаимно обратных управляемых элементов S3/1 и S

На фиг.13 представлен вариант построения управляемого элемента S3/1, не являющегося инволюцией. Данный вариант описан функциональными схемами и таблицами истинности, соответствующими нулевому (фиг.13а) и единичному (фиг.13б) значению управляющего бита ν , аналогично примеру 10. Использование более общих вариантов управляемых элементов позволяет выбрать те из них, которые обладают более выраженными свойствами размножения ошибок, что для некоторых типов управляемых операционных блоков является предпочтительным, поскольку это позволяет снизить число раундов криптографического преобразования и тем самым снизить схемотехническую сложность реализации и повысить производительность алгоритмов криптографического преобразования, например, хэширования данных. При использовании подобных управляемых операционных блоков для шифрования данных необходимо реализовать соответствующие им обратные управляемые операционные блоки. Для реализации последних используются соответствующие обратные управляемые элементы S

Пример 12. Построение взаимно обратных управляемых операционных блоков S8/9 и S

Данный пример показан на фиг.15, где представлен управляемый операционный блок S8/9 (фиг.15а), построенный с использованием управляемых элементов S° 2/2 и S3/1, и блок S

Пример 13. Построение пары взаимно обратных управляемых операционных блоков S8/12 и S

Пример построения пары взаимно обратных блоков S8/12 и S

Пример 14. Построение пары взаимно обратных управляемых операционных блоков S96/544 и S

Пара взаимно обратных блоков S96/544 и S

Пример 15. Построение пары взаимно обратных управляемых операционных блоков S81/192 и S

Пара взаимно обратных блоков S81/192 и S

Другим вариантом реализации блоков S9/9 и S

Рассмотрим пример использования блоков Sn/m при построении алгоритма блочного одностороннего преобразования, который может быть использован в качестве составной части алгоритмов хэширования данных, и алгоритмов шифрования.

Пример 16. Использование управляемых операционных блоков S81/192 и S

Структура алгоритма одностороннего преобразования 192-битового блока данных представлена в виде схемы, показанной на фиг.22. Преобразуемый 192-битовый блок данных разбивается на два 81-битовых подблока Х1 и Х2, после чего каждый из них преобразуется с помощью управляемых операционных блоков S81/192 и S

Рассмотрим примеры использования блоков Sn/m при построении алгоритмов шифрования.

Пример 17. Использование управляемых операционных блоков S32/160 и S

В известном 12-раундовом шифре SPECTR-H64 [Н.Д.Гуц, Б.В.Изотов, А.А.Молдовян, Н.А.Молдовян. Скоростной алгоритм шифрования SPECTR-H64//Безопасность информационных технологий. 2000. №4. С.37-50], основанном на управляемых перестановках Р32/80 и Р

Для практического построения устройств шифрования наибольший интерес представляют управляемые операционные блоки Sn/m со значением n=32 и 64 и значением m=160 и 448, соответственно. В этих случаях управляющий двоичный вектор может быть сформирован в зависимости от одного из подблоков данных, например подблока А, и подключей К1, K2...Kl, где l&γτ; 4, используемых при выполнении процедур шифрования. Например, формирование управляющего двоичного вектора может быть осуществлено путем:

1) повторения подблока данных: V=(А, А, ... , А) и

2) объединения подключей и подблока данных: V=(К1, А, К2, ... , Kl, A).

Дополнительно управляющий двоичный вектор может быть подвергнут фиксированному преобразованию, например, над ним может быть осуществлена операция циклического сдвига бит в сторону старших или младших разрядов.

Рассмотрим пример построения 128-битового шифра на основе управляемых операционных блоков S64/448 и S

Пример 18. Использование управляемых операционных блоков S32/160 и S

Пример 18 поясняется на фиг.23. Шифрование 128-битового блока данных Х осуществляется следующим образом. Формируется секретный ключ, представленный в виде следующей совокупности 64-битовых раундовых подключей: K1, K2, ... , K6; Q1, Q2, ... , Q6 и U1, U2, ... , U6. Преобразуемый 128-битовый блок данных X разбивается на два 64-битовых подблока А и В и осуществляется преобразование подблоков А и B в соответствии со следующим алгоритмом.

1. Установить счетчик числа раундов шифрования r:=1.

2. Сформировать по подключу Кr и подблоку А 448-битовый управляющий двоичный вектор V1:= (Кr, А, Кr, А, Кr, А, Кr).

3. Сформировать по подключу Ur и подблоку А 448-битовый управляющий двоичный вектор V2:=(Ur, A, Ur, A, Ur, А, Ur).

4. Сформировать по подключу Qr и подблоку А 448-битовый управляющий двоичный вектор V1:=(Qr, A, Qr, A, Qr, A, Qr).

5. Преобразовать подблок В, выполнив над ним управляемую операцию, осуществляемую с помощью управляемого операционного блока S64/448, в зависимости от значения управляющего кода V1: В:=S64/448(v1)(B).

6. В зависимости от значения V2 преобразовать раундовый подключ Кr путем выполнения над ним управляемой операции, осуществляемую с помощью управляемого операционного блока S64/448, в зависимости от значения управляющего кода V2:

7. Сформировать двоичный вектор F: F:=A.

8. Преобразовать двоичный вектор F в соответствии с формулой: F:=(F+Kr) mod 264.

9. Преобразовать подблок B в соответствии с формулой: В:=В⊕ F, где знак "⊕ " обозначает операцию поразрядного суммирования по модулю 2.

10. Преобразовать подблок В, выполнив над ним управляемую операцию с помощью управляемого операционного блока S

11. Если r&λτ; 6, то прирастить r:=r+1, переставить подблоки А и В и перейти к шагу 2.

12. СТОП.

Блок криптограммы Y представляет собой конкатенацию преобразованных подблоков А и В: Y=(А, В). Расшифрование блока криптограммы осуществляется с помощью этого же алгоритма, за исключением того, что при выполнении шага 2 вместо подключа Кr используется подключ Q7-r, при выполнении шага 3 вместо подключа Ur используется подключ K7-r, а при выполнении шага 4 вместо подключа Qr используется подключ K7-r. Операция конкатенации на шагах 2, 3 и 4 выполняется практически без задержки, поскольку она реализуется с помощью простого соединения проводников, а шаги 5 и 6 выполняются параллельно, что обеспечивает высокую скорость шифрования 128-битовых блоков данных. При аппаратной реализации с использованием программируемых логических матриц типа FPGA данный алгоритм обеспечивает скорость шифрования более 2 Гбит/с при невысокой схемотехнической сложности реализации.

Приведенные примеры показывают, что заявляемый управляемый операционный блок технически реализуем и позволяет решить поставленную задачу.

Благодаря массовому выпуску программируемых логических матриц типа FPGA заявляемое техническое решение может быть широко использовано на практике при создании недорогих производительных криптографических устройств, перспективных для применения в скоростных телекоммуникационных системах и компьютерных сетях.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ ДАННЫХ | 2003 |

|

RU2309549C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЯЕМОГО ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ ДАННЫХ | 2003 |

|

RU2239291C1 |

| КРИПТОГРАФИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ДАННЫХ | 2003 |

|

RU2239955C1 |

| СПОСОБ БЛОЧНОГО КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2140713C1 |

| СПОСОБ БЛОЧНОГО ИТЕРАТИВНОГО ШИФРОВАНИЯ ЦИФРОВЫХ ДАННЫХ | 2000 |

|

RU2184423C2 |

| ИТЕРАТИВНЫЙ СПОСОБ БЛОЧНОГО ШИФРОВАНИЯ | 1999 |

|

RU2172075C1 |

| СПОСОБ ИТЕРАТИВНОГО ШИФРОВАНИЯ БЛОКОВ ДАННЫХ | 1999 |

|

RU2140714C1 |

| СПОСОБ ИТЕРАТИВНОГО ШИФРОВАНИЯ БЛОКОВ ДВОИЧНЫХ ДАННЫХ | 1999 |

|

RU2144268C1 |

| СПОСОБ ШИФРОВАНИЯ БЛОКОВ ДАННЫХ | 1997 |

|

RU2111620C1 |

| ИТЕРАТИВНЫЙ СПОСОБ БЛОЧНОГО ШИФРОВАНИЯ | 2001 |

|

RU2204212C2 |

Изобретение относится к области электросвязи и вычислительной техники, а конкретнее к области криптографических способов и устройств для защиты информации, передаваемой по телекоммуникационным сетям. Управляемый операционный блок преобразования двоичных данных содержит s≥2 активных каскадов, каждый из которых содержит к≥2 управляемых элементов, снабженных t-разрядными информационным входом и выходом и w-разрядным управляющим входом, где t=2,3 и w=1,2, причем, по крайней мере, для одного управляемого элемента выполнено условие w+t=4, а активные каскады состоят из управляемых элементов, снабженных двухразрядными управляющими входами, при этом активный каскад включает управляемые элементы, снабженные как трехразрядными, так и двухразрядными информационными входами и активный каскад включает управляемые элементы, снабженные как двухразрядными, так и одноразрядными информационными входами. Технический результат, достигаемый при реализации изобретения, состоит в повышении скорости обработки данных с использованием программируемых логических матриц типа FPGA. 4 з.п. ф-лы, 33 ил.

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ БЛОКОВ ДВОИЧНЫХ ДАННЫХ | 1998 |

|

RU2141729C1 |

| СПОСОБ БЛОЧНОГО КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2140713C1 |

| US 5966450 А, 12.10.1999 | |||

| Уровнемер | 1978 |

|

SU676876A2 |

| US 5442705 А, 15.08.1995 | |||

| DE 4016203 A1, 21.11.1991. | |||

Авторы

Даты

2004-11-27—Публикация

2002-10-14—Подача