Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых микросхем различного функционального назначения (операционных усилителей, непрерывных стабилизаторов напряжения, перемножителей сигналов и т.д.).

Известны широкополосные усилители (ШУ) на основе параллельно-балансных каскадов, которые стали основой построения современных аналоговых микросхем [1, 2]. Проблема улучшения их параметров (входного сопротивления, частотных свойств и др.) относится к числу основных проблем современной аналоговой микросхемотехники.

Ближайшим прототипом заявляемого устройства является каскодный дифференциальный усилитель, содержащий входной параллельно-балансный каскад, имеющий первый и второй входы, а также первый и второй противофазные токовые выходы, первый выходной транзистор, эмиттер которого подключен ко второму токовому выходу входного параллельно-балансного каскада, а база связана по переменному току с источником опорного напряжения [3].

Существенный недостаток известного ШУ состоит в том, что он имеет большие значения входной проводимости для переменного тока.

Основная цель предлагаемого изобретения состоит в уменьшении входной проводимости дифференциального усилителя в широком диапазоне частот - снижении двух ее основных составляющих, обусловленных емкостью коллекторного перехода входного транзистора и конечным значением коэффициента усиления по току базы входного транзистора.

Поставленная цель достигается тем, что в дифференциальном усилителе, содержащем входной параллельно-балансный каскад, имеющий первый и второй входы, а также первый и второй противофазные токовые выходы, первый выходной транзистор, эмиттер которого подключен ко второму токовому выходу входного параллельно-балансного каскада, вводятся новые связи база первого выходного транзистора связана по переменному току с первым входом входного параллельно-балансного каскада.

Предлагаемый дифференциальный усилитель (фиг.1) содержит входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, а также первый 4 и второй 5 противофазные токовые выходы, первый выходной транзистор 6, эмиттер которого подключен ко второму токовому выходу 5 входного параллельно-балансного каскада, а база - связана по переменному току с первым входом 2 входного параллельно-балансного каскада 1.

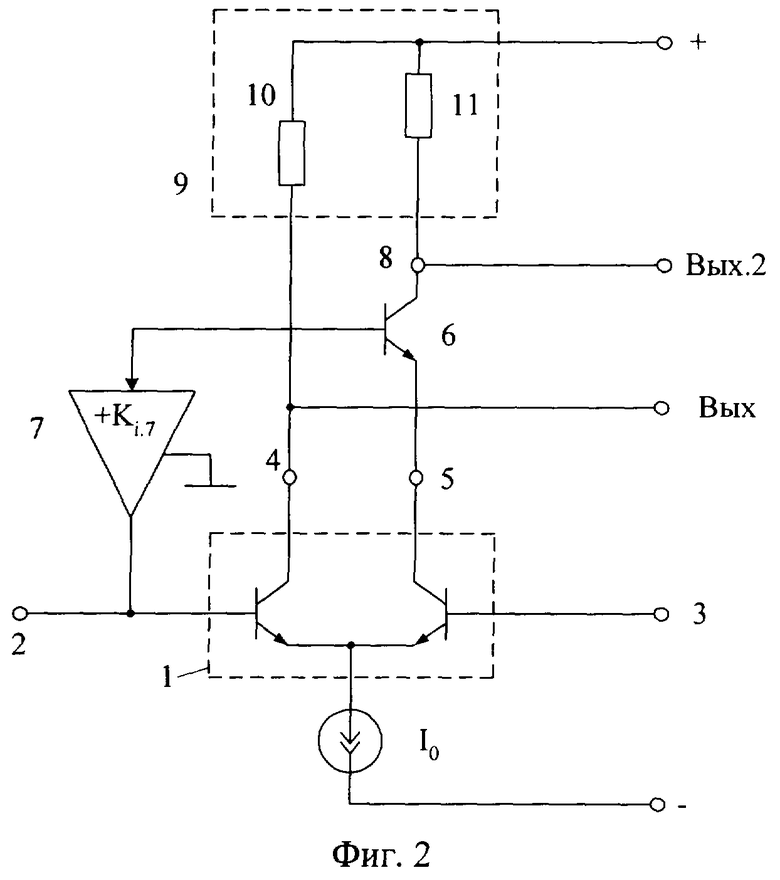

В устройстве фиг. 2, соответствующему п.2 формулы изобретения, база транзистора 6 связана со входом 2 через первую цепь смещения статического уровня 7, обеспечивающую близкий к единице коэффициент передачи по переменному току. В цепь коллектора 8 транзистора 6 и токового выхода 4 включена подсхема нагрузки 9, реализованная в частном случае, на основе резисторов 10 и 11.

Усилитель фиг.3, соответствующий п.3 и п.4 формулы изобретения, содержит также второй выходной транзистор 12, база которого через вторую цепь смещения статического уровня 13 связана со вторым входом 3 параллельно-балансного каскада 1. В данном устройстве подсхема нагрузки 9 включена в коллекторные цепи транзисторов 6 и 12.

В устройстве фиг.4, соответствующем п.5 формулы изобретения, входной параллельно-балансный каскад 1 содержит первый 14 и второй 15 входные транзисторы с объединенными эмиттерами, выходной транзистор 16, эмиттер которого подключен к коллектору транзистора 15 и источнику тока 17.

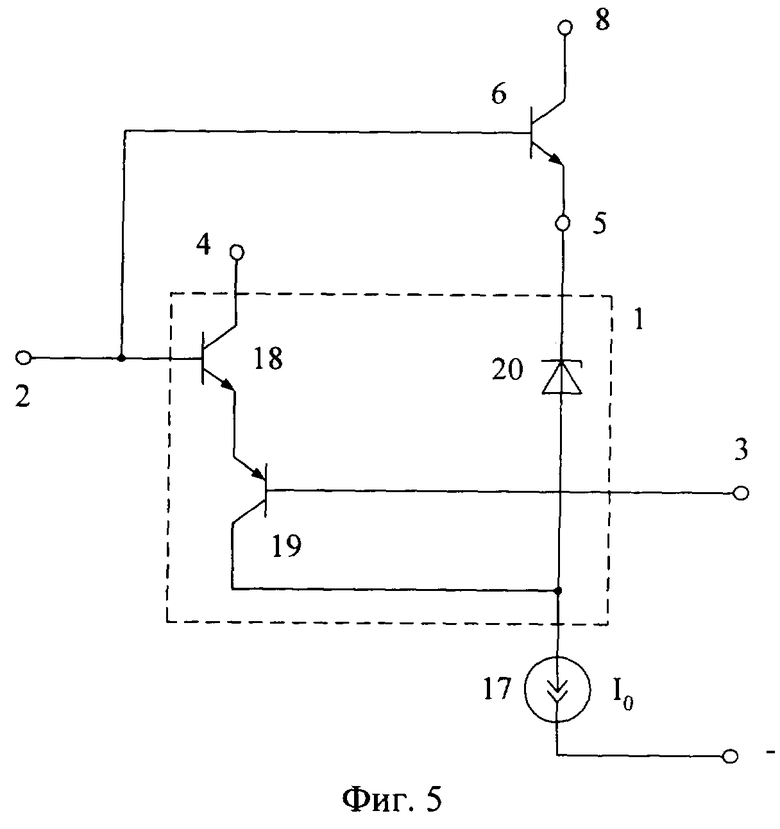

В устройстве фиг.5, соответствующем п.6 формулы изобретения, входной параллельно-балансный каскад 1 содержит первый 18 и второй 19 входные транзисторы с объединенными эмиттерами, коллектор второго 19 входного транзистора соединен с источником тока 17, а между вторым токовым выходом входного параллельно-балансного каскада 1 и коллектором второго входного транзистора включена первая вспомогательная цепь смещения статического уровня 20, выполненная, в частном случае, на р-n-переходе (стабилитроне).

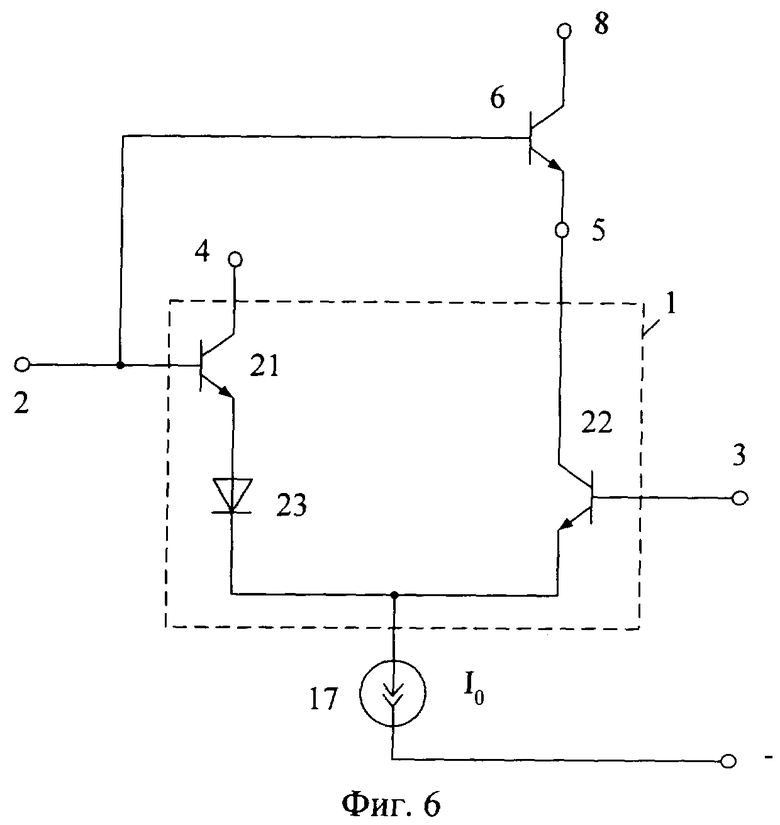

В устройстве фиг.6, соответствующем п.7 формулы изобретения, входной параллельно-балансный каскад 1 содержит первый 21 и второй 22 входные транзисторы, между эмиттерами которых включена вторая вспомогательная цепь смещения статического уровня на основе р-n-перехода 23.

В устройстве фиг.7, соответствующем п.8 формулы изобретения, входной параллельно-балансный каскад 1 содержит первый 24 и второй 25 входные транзисторы, эмиттеры которых соединены со входами первого 26 и второго 27 повторителей тока. Общие выводы повторителей тока 26 и 27 соединены с источником тока в общей эмиттерной цепи I0. Выходы первого 26 и второго 27 повторителей тока являются первым и вторым токовыми выходами входного параллельно-балансного каскада.

В устройствах фиг.8 и фиг.9, соответствующих п.9 формулы изобретения, первая 7 и вторая 13 цепи смещения статического уровня реализованы на основе двухполюсников 28 и 29, статический режим которых устанавливается вспомогательными источниками тока 30 и 31. В этой схеме заявляемый усилитель является выходным узлом более сложного дифференциального усилителя, включающего также транзисторы 32 и 33.

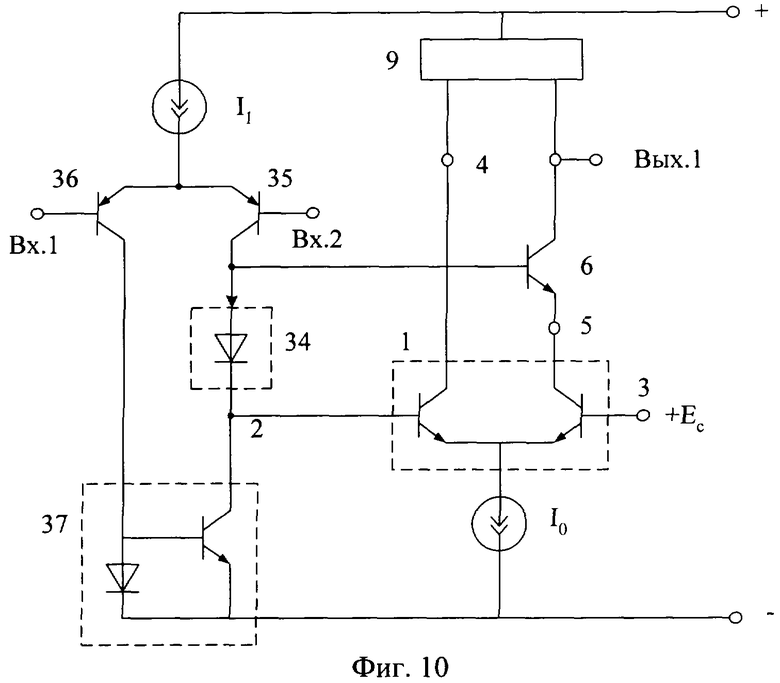

В усилителе фиг.10, соответствующем п. 10 формулы изобретения, в качестве первой цепи смещения статического уровня используется двухполюсник 34, статический режим которого устанавливается двумя управляемыми источниками тока на транзисторах 35, 36 и инвертирующем повторителе тока 37. В данном устройстве заявляемый усилитель используется как выходной узел более сложного многокаскадного усилителя.

В усилителе фиг.11, соответствующем п. 11 формулы изобретения, в качестве первой цепи согласования статического уровня используется транзисторный каскад 38, включенный по схеме с общей базой, входящий в структуру активной нагрузки 39 усилителя на транзисторах 40 и 41. В этой схеме заявляемый усилитель является выходным узлом более сложного устройства.

В усилителе фиг.12, соответствующем п. 12 формулы изобретения, в качестве первой 7 и второй 13 цепей смещения статического уровня используются транзисторные каскады 42 и 43, статический режим которых устанавливается двухполюсниками 44 и 45. На чертеже фиг. 12 заявляемое устройство является выходной частью более сложного усилителя, включающего транзисторы 46 и 47.

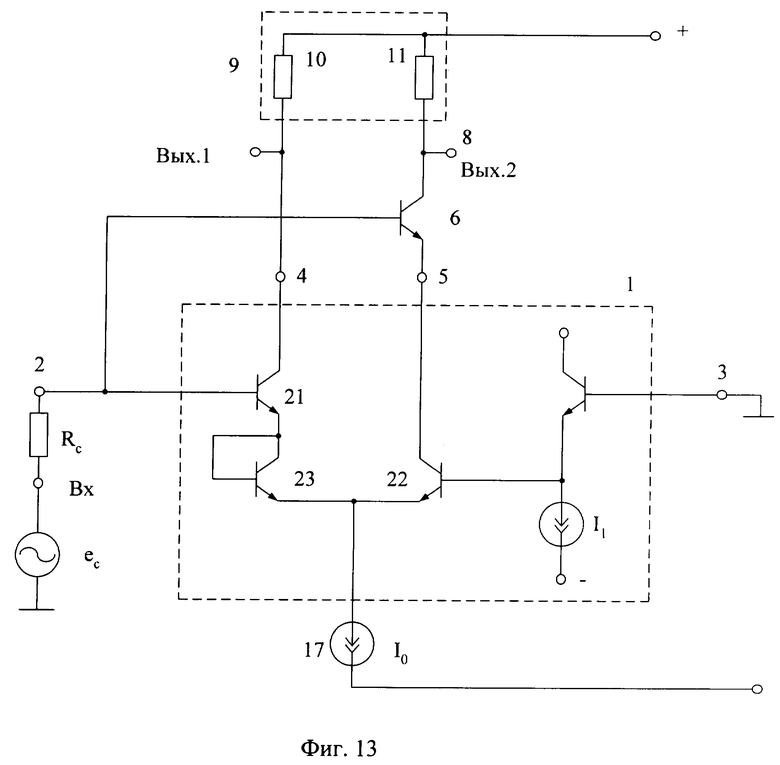

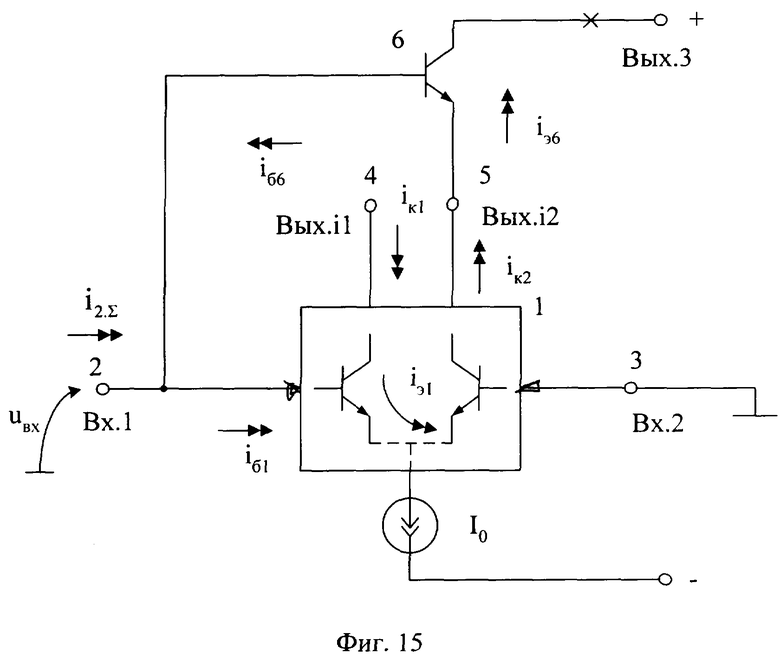

На чертеже фиг.13 приведена схема заявляемого усилителя, которая исследовалась с помощью компьютерной программы PSpice, а на чертеже фиг.14 показаны результаты ее компьютерного моделирования. На чертежах фиг.15 и фиг.16 приведены схемы, поясняющие работу заявляемого устройства.

Заявляемый усилитель (фиг.1, фиг.15) работает следующим образом.

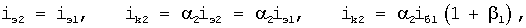

При подаче на вход 2 переменного напряжения uвх в цепи входа 2 входного параллельно-балансного каскада появляется приращение тока iб1:

где iэ1 - приращение тока эмиттера левого входного транзистора входного параллельно-балансного каскада 1;

β 1- коэффициент усиления по току базы левого входного транзистора входного параллельно-балансного каскада.

Учитывая, что в эмиттерную цепь каскада 1 включен источник не изменяющегося под действием сигнала тока I0, приращение тока эмиттера и, следовательно, тока коллектора правого входного транзистора каскада 1 будет равно току iэ1:

где α 2 - коэффициент усиления по току эмиттера правого входного транзистора каскада 1.

При этом токи в выходных узлах 4 и 5 будут иметь равную величину, но противоположные направления, а всё приращение тока iк2 передается в эмиттер транзистора 6:

Поэтому ток базы транзистора 6

Как следствие, в узле 2 произойдет вычитание двух близких по величине, но противоположных по направлению переменных токов iб1 и iб6:

Учитывая, что α 2≈1, а транзисторы в заявляемой схеме имеют близкие по величине коэффициенты усиления по току базы β 1≈β 6 получаем, что суммарный входной ток i2.∑ и, следовательно, входная проводимость заявляемого устройства близки к нулю. Это является существенным преимуществом усилителя фиг.1.

Кроме этого, в заявляемом устройстве обеспечивается компенсация емкостной составляющей входной проводимости, обусловленной “умножением” емкости коллекторного перехода левого транзистора каскада 1. Рассмотрим этот эффект на примере анализа схемы фиг. 16.

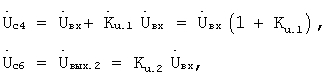

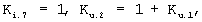

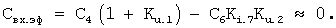

Комплекс переменных составляющих напряжений на емкостях С4 и С6:

где  - инвертирующий коэффициент усиления по напряжению со входа 2 к выходу Вых. 1;

- инвертирующий коэффициент усиления по напряжению со входа 2 к выходу Вых. 1;

- неинвертирующий коэффициент усиления по напряжению со входа 2 к выходу Вых.2.

- неинвертирующий коэффициент усиления по напряжению со входа 2 к выходу Вых.2.

Токи через емкости С4, С6 создают в узле 2 две составляющие, имеющие относительно выхода 2 противоположные направления:

Если С4=С6, то при выполнении в рабочем диапазоне частот условий

емкостная составляющая входной проводимости заявляемого усилителя будет близка к нулю:

Полученные выше аналитические оценки подтверждаются результатами (фиг. 14) компьютерного моделирования схемы фиг. 13 при следующих параметрах элементов и режимах по постоянному току: I0=500 мкА; R11=10 КОм; I1=150 мкА; R10=8,8÷ 10 К, Rc=10 КOм.

Все транзисторы соответствуют транзисторам ФГУП НПП “Пульсар” (г.Москва). Изменение сопротивления резистора R10 в пределах 8,8-10 КОм позволяло управлять величиной коэффициента усиления Кu.1 и, следовательно, эффектами компенсации.

Из графиков фиг. 14 следует, что за счет введения новых связей предлагаемый усилитель имеет более широкий частотный диапазон в сравнении с усилителем-прототипом. Во-первых, на низких частотах входное сопротивление (Rвx.k) в схеме фиг. 13 улучшается в 24 раза. Во-вторых, частотный диапазон коэффициента передачи по напряжению при сопротивлении источника сигнала Rc=10 КОм, расширяется более чем в 5 раз.

СПИСОК ЛИТЕРАТУРЫ

1. Алексеенко А.Г. Основы микросхемотехники. Элементы морфологии микроэлектронной аппаратуры / А.Г.Алексеенко. - Изд. 2-е, перераб. и доп. - М., “Сов. радио”, 1977. - 408с.

2. Проектирование и применение операционных усилителей /Под ред. Дж.Грэма, Дж.Тоби, Л.Хьюлсмана //Пер. с англ. В.И.Левина и И.М.Хейфеца под.ред. к.т.н. И.Н.Теплюка. - М.: Изд-во Мир, 1974.

3. Патент США №3531729, кл. 330-23.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393626C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2396699C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2255416C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2394360C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в различных микроэлектронных устройствах усиления и преобразования аналоговых сигналов. Технический результат заключается в снижении входной проводимости усилителя в широком диапазоне частот и, как следствие, повышении верхней граничной частоты. Устройство содержит входной параллельно-балансный каскад (1), имеющий первый и второй входы (2, 3), а также первый и второй противофазные токовые выходы (4, 5), первый выходной транзистор (6), эмиттер которого включен ко второму (5) токовому выходу входного параллельно-балансного каскада (1), при этом база первого выходного транзистора (6) связана по переменному току с первым (2) входом входного параллельно-балансного каскада (1). 11 з.п. ф-лы, 16 ил.

| US 3531729, 29.09.1970 | |||

| US 4755770, 05.07.1988 | |||

| US 5587687, 24.12.1996 | |||

| JP 10294624, 04.11.1998 | |||

| СПОСОБ ОГРАНИЧЕНИЯ ВЫХОДНОГО ТОКА | 1993 |

|

RU2101850C1 |

| Дифференциальный усилитель | 1977 |

|

SU764100A1 |

Авторы

Даты

2005-07-20—Публикация

2003-06-04—Подача