Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных и импульсных сигналов, в структуре аналоговых интерфейсов различного функционального назначения.

Известны операционные усилители (ОУ) на базе двух параллельно включенных параллельно-балансных каскадов, которые стали основой построения современных операционных усилителей, например, AD8631, НА2539, НА5190 и др. [1, 2, 4]. Однако они имеют недостаточно высокое быстродействие из-за нелинейных режимов работы при большом импульсном сигнале [5, 6]. Проблема повышения быстродействия ОУ данного класса, относящихся к числу наиболее широкополосных двухтактных структур, является одной из актуальных проблем современной аналоговой микросхемотехники.

Ближайшим прототипом заявляемого устройства является операционный усилитель [4], содержащий входной каскад, имеющий первый и второй противофазные токовые выходы, согласованные с шинами положительного источника питания, первый и второй противофазные токовые выходы, согласованные с шиной отрицательного источника питания, первый и второй р-n-р транзисторы с объединенными базами и выбранным на них напряжением смещения Ec1, эмиттеры которых соединены с соответствующими первым и вторым токовыми выходами входного каскада, согласованными с шиной положительного источника питания, первый и второй n-р-n транзисторы с объединенными базами и выбранным на них напряжением смещения Ес2, эмиттеры которых соединены с соответствующими первым и вторым противофазными токовыми выходами входного каскада, согласованными с шиной отрицательного источника питания, причем коллекторы вторых р-n-р и n-р-n транзисторов объединены и связаны с корректирующим конденсатором и выходным буферным усилителем.

Существенный недостаток известного ОУ состоит в том, что его архитектура не позволяет исключить нелинейные режимы и тем самым получить предельные значения максимальной скорости нарастания выходного напряжения (ϑ вых) для большого сигнала. Кроме этого, известное устройство характеризуется из-за несимметрии высокими значениями э.д.с. смещения нуля и малым коэффициентом ослабления входных синфазных сигналов.

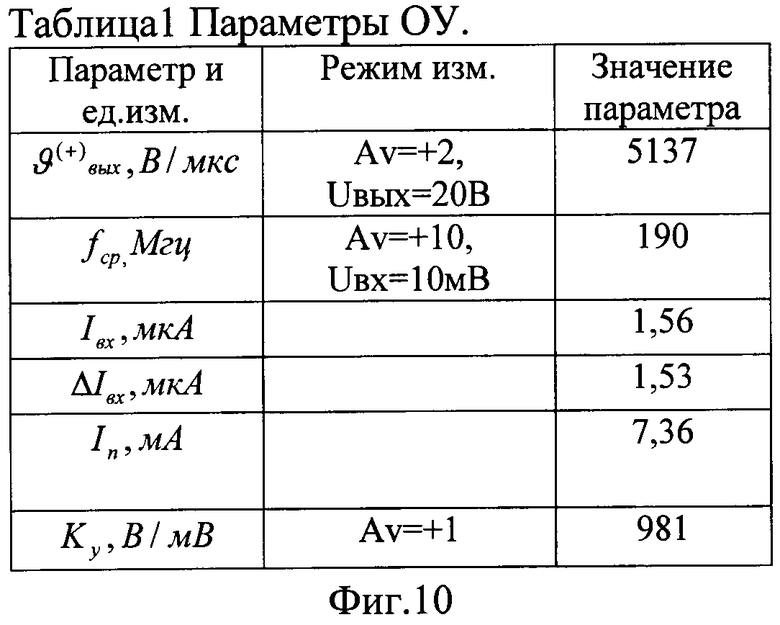

Основная цель предлагаемого изобретения состоит в повышении быстродействия - получении ϑ вых на уровне 4000-6000 В/мкс с использованием отечественных микронных технологий (с топологическими нормами ≥ 1,5÷ 2 мкм). Дополнительная цель - в уменьшении э.д.с. смещения нуля и повышении коэффициента ослабления входных синфазных сигналов.

Поставленная цель достигается тем, что в операционный усилитель, содержащий входной каскад, имеющий первый и второй противофазные токовые выходы, согласованные с шинами положительного источника питания, первый и второй противофазные токовые выходы, согласованные с шиной отрицательного источника питания, первый и второй р-n-р транзисторы с объединенными базами и выбранным на них напряжением смещения Ec1, эмиттеры которых соединены с соответствующими первым и вторым токовыми выходами входного каскада, согласованными с шиной положительного источника питания, первый и второй n-р-n транзисторы с объединенными базами и выбранным на них напряжением смещения Ес2, эмиттеры которых соединены с соответствующими первым и вторым противофазными токовыми выходами входного каскада, согласованными с шиной отрицательного источника питания, причем коллекторы вторых р-n-р и n-р-n транзисторов объединены и связаны с корректирующим конденсатором и выходным буферным усилителем, вводятся новые связи и элементы - входной каскад выполнен в виде дифференциальных усилителей, не имеющих ограничений выходного тока при изменении входного напряжения до нескольких вольт, между коллекторами первого и второго р-n-р транзисторов, а также коллекторами первого и второго n-p-n транзисторов введены соответственно первый и второй повторители тока, причем общий узел первого повторителя тока соединен с шиной положительного источника питания, а общий узел второго повторителя тока связан с шиной отрицательного источника питания.

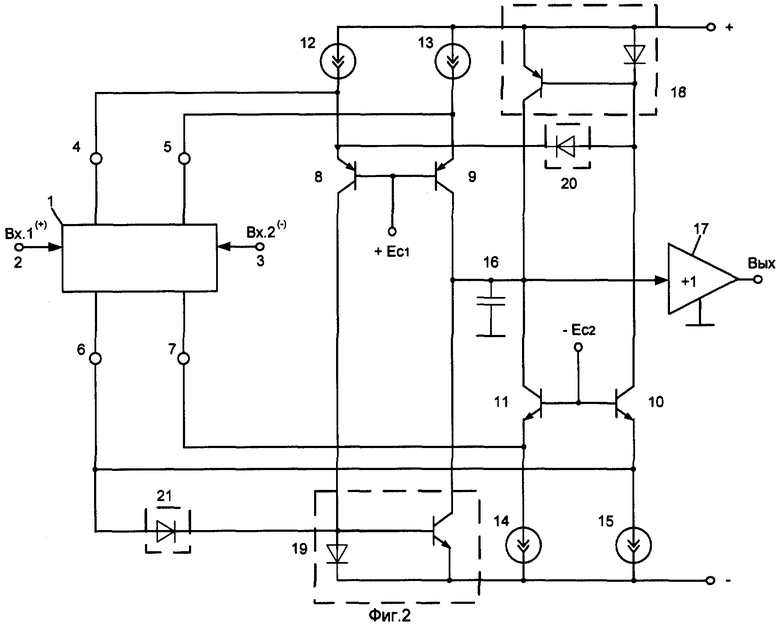

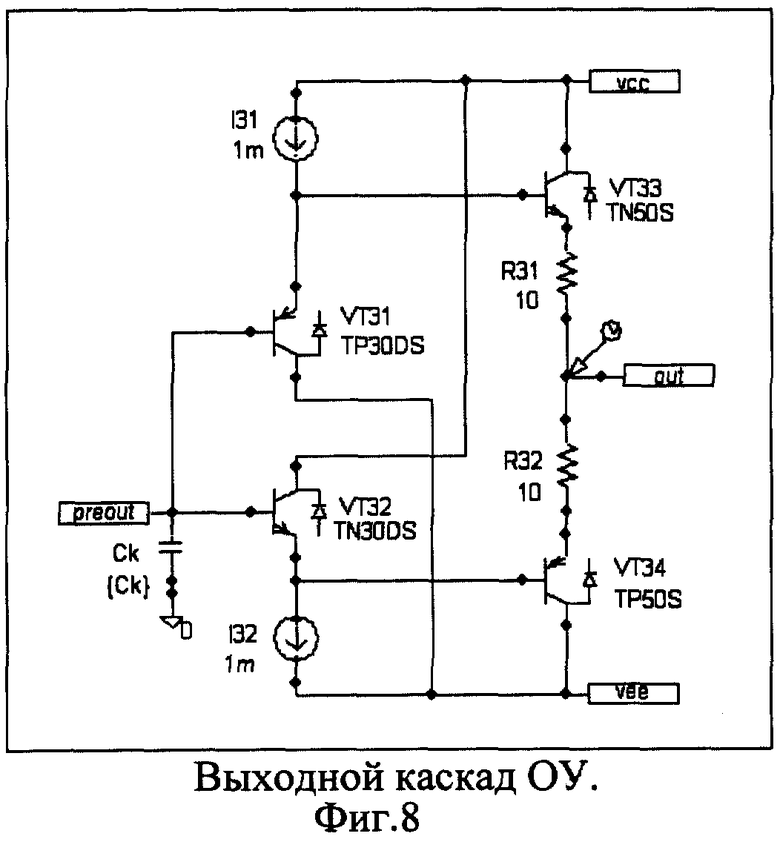

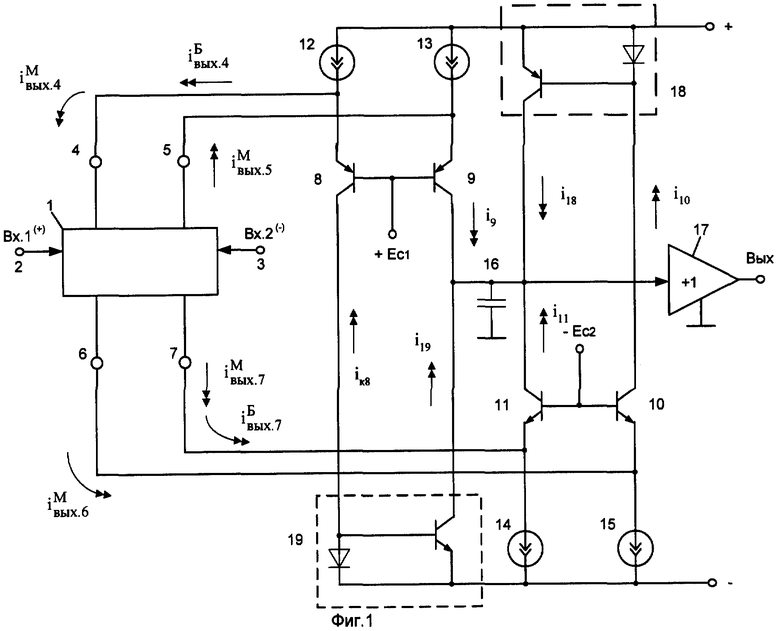

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.1. На фиг.2 изображена схема ОУ, в котором (п.2, п.3 формулы изобретения) вводятся дополнительные повторители тока с зоной нечувствительности 20 и 21, обеспечивающие передачу больших приращений выходных токов входного каскада, протекающих через узлы 4 и 6, в корректирующий конденсатор 16.

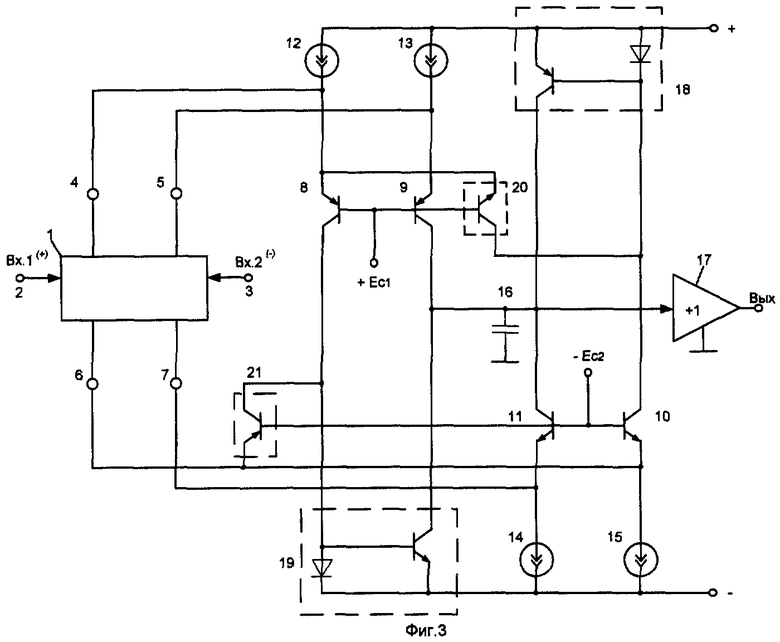

На фиг.3 показан частный случай реализации повторителей тока с зоной нечувствительности 20 и 21 - на основе n-р-n (20) и р-n-р (21) транзисторов, находящихся (при усилении малых сигналов) в отсечке.

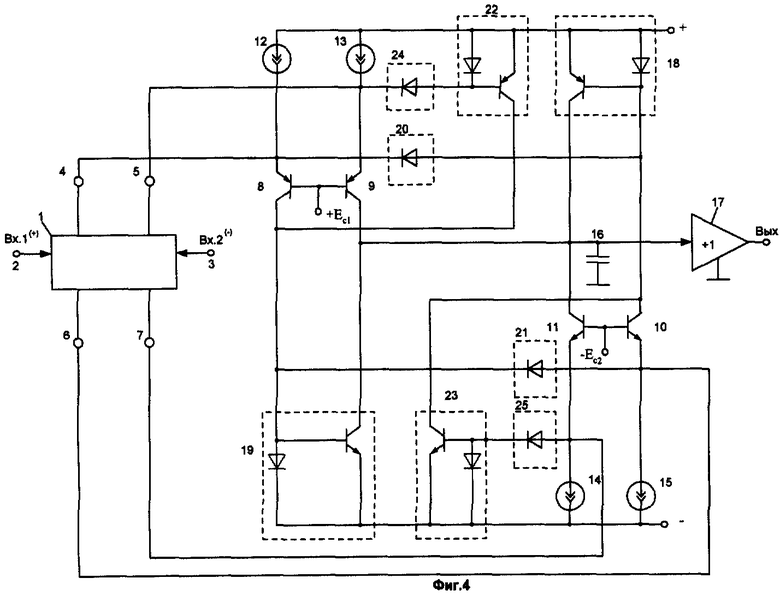

В схеме фиг.4 (п.6, п.7 формулы изобретения) введены новые элементы 22, 23, 24, 25, которые создают дополнительный нелинейный канал передачи большого сигнала от выходов 5 и 7 в корректирующий конденсатор 16. Эти связи направлены на устранение возникающей динамической ассиметрии в ОУ, которая может возникать из-за неодинакового быстродействия по выходам 4 и 5, а также 6 и 7.

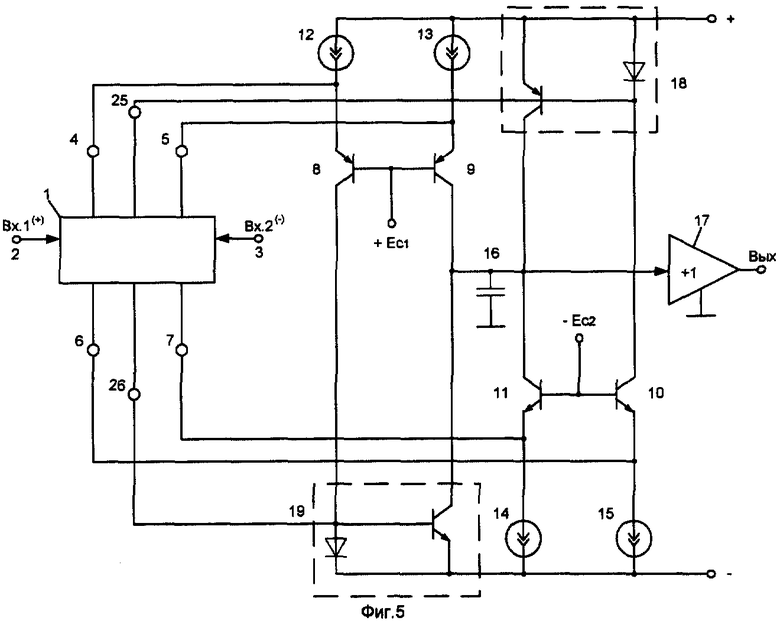

В схеме ОУ фиг.5 за счет использования во входном каскаде синфазных токовых выходов 25, 26, выходные токи которых пропорциональны только большому входному сигналу (uвх.2.3>>50 мВ), каналы передачи больших и малых сигналов совпадают только в первом 18 и втором 19 повторителях тока. Такая архитектура позволяет создавать сверхбыстродействующие ОУ, одинаково хорошо работающие как в режиме инвертора, так и в режиме повторителя импульсных сигналов.

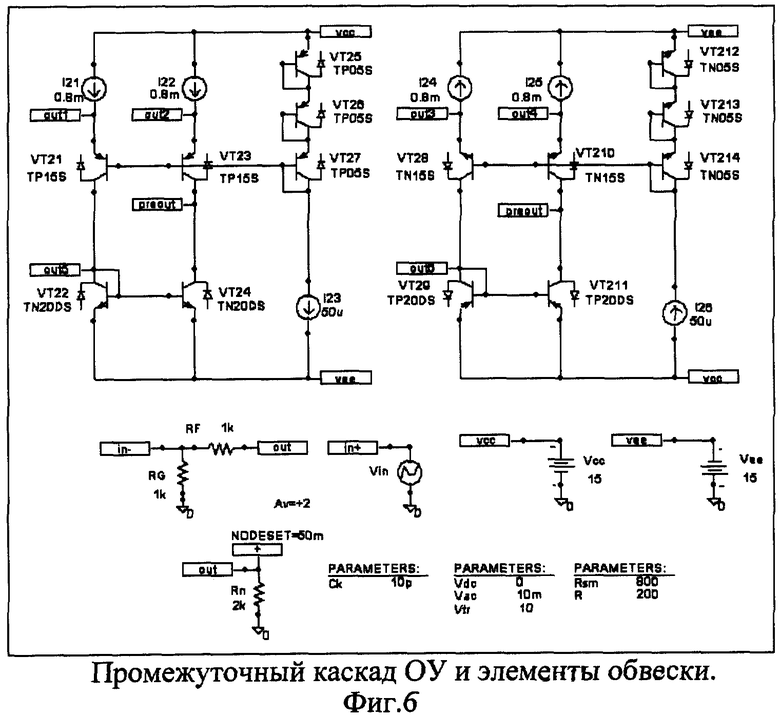

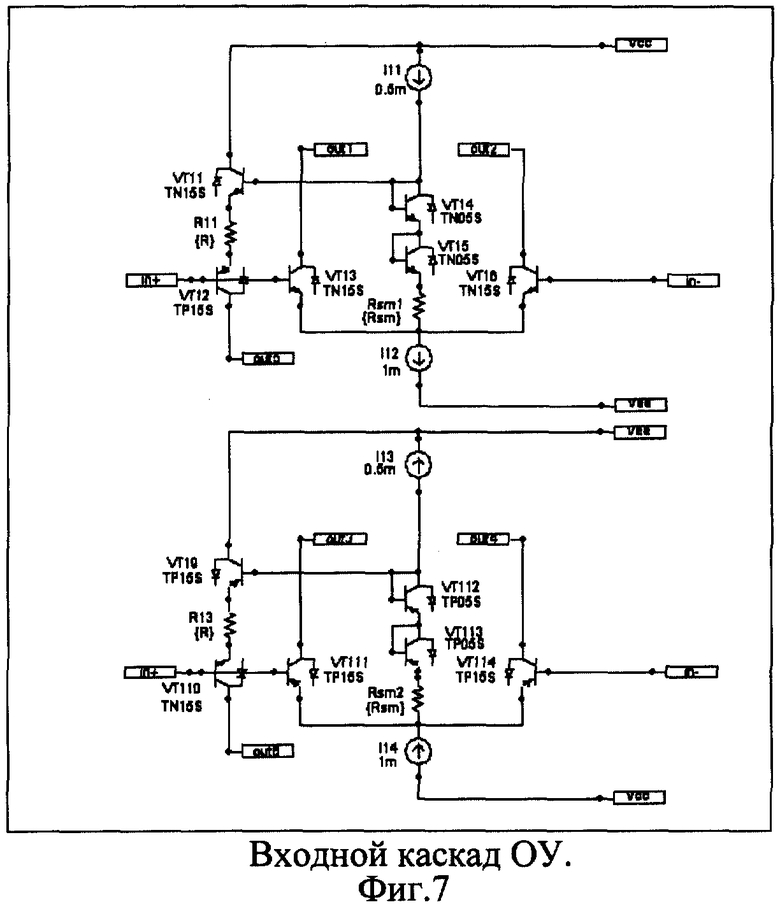

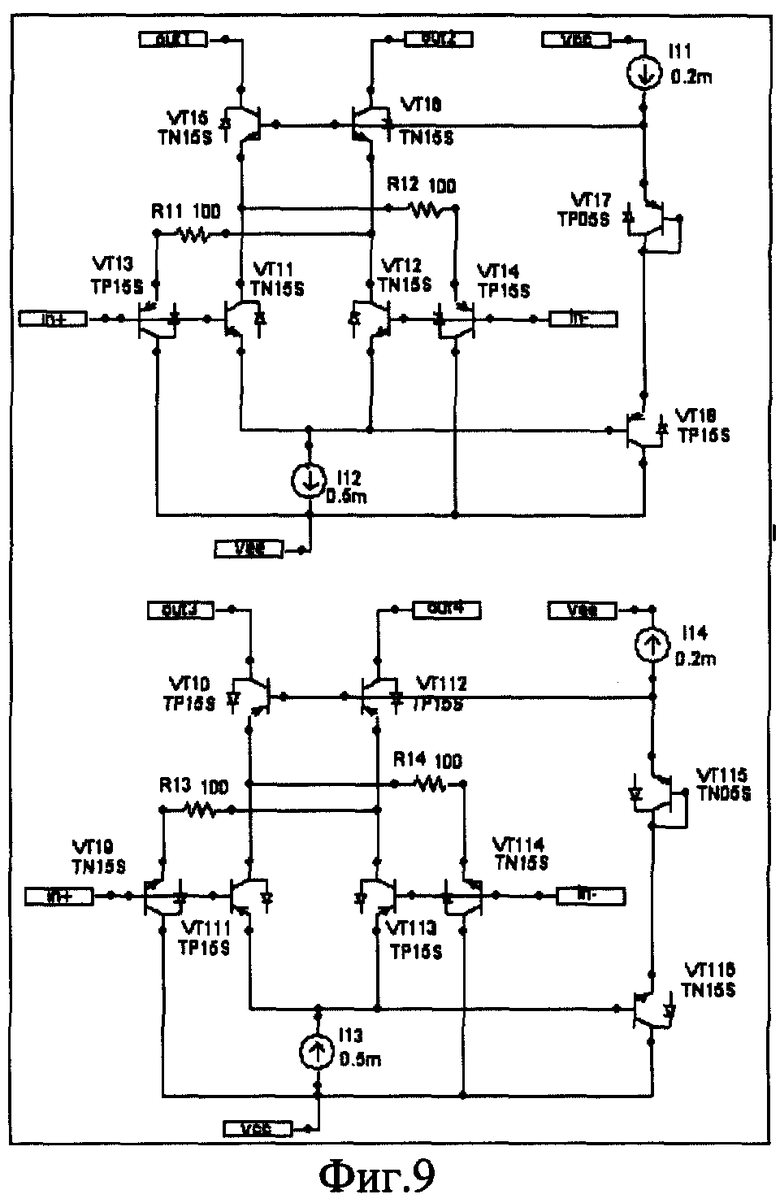

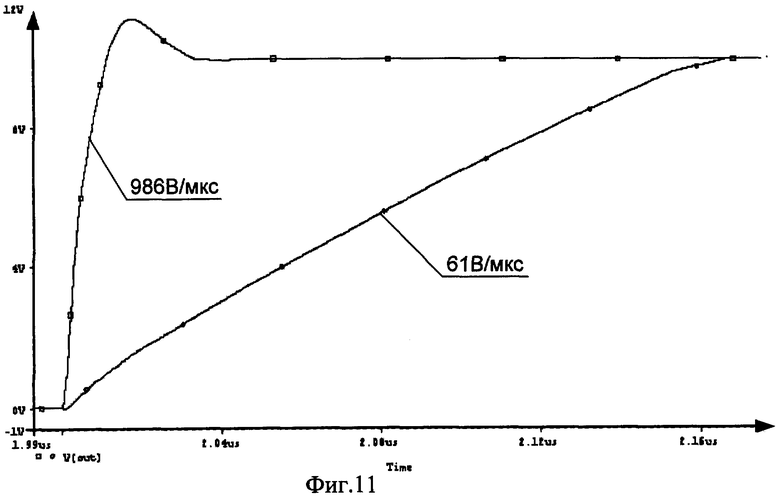

На фиг.6-фиг.8 и таблице 1 (фиг.10) изображены конкретные схемы функциональных узлов, которые использовались при построении ОУ фиг.5, и результаты их компьютерного моделирования в среде Pspice с использованием моделей интегральных транзисторов. На фиг.11 показана схема входного каскада 1, которая исследовалась в предлагаемом операционном усилителе.

Операционный усилитель фиг.1 содержит входной каскад 1, входами которого являются узлы 2 и 3, первый (4) и второй (5) противофазные токовые выходы входного каскада, согласованные с шинами положительного источника питания, а первый (6) и второй (7) противофазные токовые выходы входного каскада согласованы с шиной отрицательного источника питания, т.е. могут иметь потенциал, близкий к +Еп (-Еп). Выходы 4 и 5 соединены с эмиттерами первого 8 и второго 9 р-n-р транзисторов с объединенными базами и выбранным на них напряжением смещения Ec1, а выходы 6 и 7 связаны с эмиттерами первого (10) и второго (11) n-р-n транзисторов с объединенными базами и выбранным на них напряжением смещения Ес2. Статический режим транзисторов 8-11 устанавливается двухполюсниками 12, 13, 14, 15. Коллекторы вторых n-p-n (11) и p-n-р (9) транзисторов соединены друг с другом и связаны с корректирующим конденсатором 16 и выходным буферным усилителем 17. Между коллекторами первого 8 и второго 9 р-n-р транзисторов, а также между коллектором первого 10 и второго 11 n-p-n транзисторов включены первый 18 и второй 19 повторители тока, общие узлы которых соединены соответственно с шинами положительного и отрицательного источников питания. В качестве входного каскада 1 применяются дифференциальные усилители, не имеющие ограничения выходного тока при изменении входного напряжения до нескольких вольт [5, 6].

В устройстве фиг.2, соответствующем п.2 формулы изобретения, между эмиттером первого р-n-р транзистора 8 и входом первого повторителя тока 18 включен первый дополнительный повторитель тока 20 с зоной нечувствительности, а между эмиттером первого n-p-n транзистора 10 и входом второго повторителя тока 19 включен второй дополнительный повторитель тока 21 с зоной нечувствительности. В частном случае дополнительные повторители тока 20 и 21 выполнены в виде нескольких последовательно включенных р-n переходов (диодов).

В устройстве фиг.3, соответствующем п.4 и п.5 формулы изобретения, первый и второй дополнительные повторители тока с зоной нечувствительности 20 и 21 выполнены в виде нелинейных каскадов с общей базой на n-р-n (20) и р-n-р (21) транзисторах.

В устройстве фиг.4, соответствующем п.6 и п.7 формулы изобретения, введены первый 22 и второй 23 вспомогательные повторители тока, согласованные с соответствующими шинами питания, причем эмиттер второго р-n-р транзистора 9 соединен со входом первого вспомогательного повторителя тока 22 через третий повторитель тока с зоной нечувствительности 24, эмиттер второго n-р-n транзистора 11 соединен со входом второго 23 вспомогательного повторителя тока через четвертый повторитель тока с зоной нечувствительности 25, причем выход первого вспомогательного повторителя тока 22 соединен со входом второго повторителя тока 19, а выход второго вспомогательного повторителя тока 23 соединен со входом первого повторителя тока 18.

В устройстве фиг.5, соответствующем п.8 формулы изобретения, входной каскад 1, кроме малосигнальных выходов 4, 5 и 6, 7, имеет первый 25 и второй 26 синфазные выходы для большого сигнала, согласованные с шинами положительного (25) и отрицательного (26) источников питания и соединенные со входами первого 18 и второго 19 повторителя тока.

В качестве входного каскада 1, в соответствии с формулой изобретения, используются каскады, не имеющие ограничений выходного тока при изменении входного напряжения ОУ до нескольких вольт [5, 6].

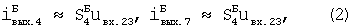

Рассмотрим работу устройства при положительном импульсе напряжения на входе Вх.1(-) ОУ (фиг.1, 2) в режиме повторителя со 100% обратной связью для трех наиболее характерных случаев: малый импульсный сигнал (импульсное напряжение между входами ОУ uвх2.3<Uгр≈50 мВ), большой импульсный сигнал (uвх.2.3≥Uгр·50 мВ, когда выходные токи в узлах 5 и 6 ограничиваются, а выходные токи узлов 4 и 7

продолжают изменяться пропорционально uвх.2.3, однако их значения не превышают статических уровней источников 12 и 14:

продолжают изменяться пропорционально uвх.2.3, однако их значения не превышают статических уровней источников 12 и 14:

большой импульсный сигнал, когда выходные токи узлов 4 и 7

большой импульсный сигнал, когда выходные токи узлов 4 и 7

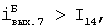

превышают статические уровни I12, I14:

превышают статические уровни I12, I14:

В статическом режиме, когда напряжение между узлами 2 и 3 близко к нулю, дополнительные повторители тока 20 и 21 (в частном случае диоды) закрыты. Такое состояние обеспечивается правильным выбором напряжений Eс1 и Ес2 на базах транзисторов.

Небольшие изменения выходных токов входного каскада  и

и

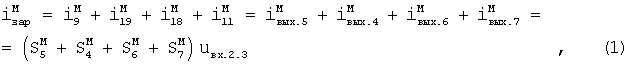

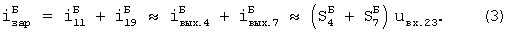

под действием входного сигнала ОУ (напряжение между узлами 2 и 3 uвх.2.3≤Uгр) передаются в эмиттерные цепи транзисторов: 8 и 9, 10 и 11, и далее на выход промежуточного каскада - к корректирующему конденсатору 16, где Uгp - входное напряжение uвx.2.3, при котором происходит ограничение выходных токов узлов 5 и 6. При этом осуществляется заряд (разряд) конденсатора 16 суммарным током, пропорциональным uвх.2.3 (фиг.1, токи со значком “М”):

под действием входного сигнала ОУ (напряжение между узлами 2 и 3 uвх.2.3≤Uгр) передаются в эмиттерные цепи транзисторов: 8 и 9, 10 и 11, и далее на выход промежуточного каскада - к корректирующему конденсатору 16, где Uгp - входное напряжение uвx.2.3, при котором происходит ограничение выходных токов узлов 5 и 6. При этом осуществляется заряд (разряд) конденсатора 16 суммарным током, пропорциональным uвх.2.3 (фиг.1, токи со значком “М”):

где  - крутизна преобразования малого входного напряжения uвх.2.3 в i-й выходной ток входного каскада.

- крутизна преобразования малого входного напряжения uвх.2.3 в i-й выходной ток входного каскада.

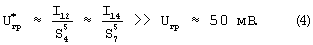

При малом сигнале (uвх.2.3<50 мВ) быстродействие ОУ получается наибольшим (зависящим как в любой линейной системе) от амплитуды выходного напряжения ОУ [5, 6]. Режим малых сигналов заканчивается при входном напряжении, превышающем 50 мВ (uвх.2.3>Uгp=50 мВ).

Во втором случае, когда uвх.2.3>Uгp=50 мВ, входной каскад, выполненный, например, по схеме фиг.7 или фиг.9, переходит в режим ограничения токов по выходам 5 и 6 (их абсолютные значения становятся близкими к нулю) и режим дальнейшего пропорционального (входному сигналу) приращения токов по выходам 4 и 7:

где  ,

,  - крутизны преобразования входного напряжения ОУ uвх.2.3 в соответствующий ток.

- крутизны преобразования входного напряжения ОУ uвх.2.3 в соответствующий ток.

Эти сравнительно большие (по сравнению со статическими токами выходов 4 и 7) приращения токов

передаются в выходную цепь и заряжают корректирующий конденсатор 16 суммарным током большого сигнала

передаются в выходную цепь и заряжают корректирующий конденсатор 16 суммарным током большого сигнала

За счет выбора параметров

входного каскада 1 обеспечивается такая же пропорциональность тока заряда

входного каскада 1 обеспечивается такая же пропорциональность тока заряда  что и на малом сигнале (1). Однако в этом режиме суммарный ток заряда корректирующего конденсатора 16

что и на малом сигнале (1). Однако в этом режиме суммарный ток заряда корректирующего конденсатора 16  достигает первого ограничения при

достигает первого ограничения при

что соответствует величине входного граничного напряжения подсхемы “входной каскад 1 - промежуточный каскад”:

что соответствует величине входного граничного напряжения подсхемы “входной каскад 1 - промежуточный каскад”:

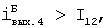

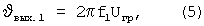

Повышенные значения  позволяют увеличить максимальную скорость нарастания выходного напряжения ОУ фиг.1 с величины ϑ вых.1 до величины ϑ вых.2>>ϑ вых.1:

позволяют увеличить максимальную скорость нарастания выходного напряжения ОУ фиг.1 с величины ϑ вых.1 до величины ϑ вых.2>>ϑ вых.1:

где f1 - частота единичного усиления по петле обратной связи ОУ;

Uгp - напряжение ограничения выходных токов iвых.5, iвых.6;

- напряжение ограничения выходных токов

- напряжение ограничения выходных токов  ,

,  .

.

При этом в схеме фиг.1 сохраняется симметрия токов заряда и разряда корректирующего конденсатора 16, что обеспечивает идентичность переходных процессов при различных полярностях импульсных входных сигналов.

Структура усилителя, каналы передачи сигналов существенно изменяются, когда выходные токи входного каскада

начинают превышать статические значения токов I12, (I14). Рассмотрим этот режим в схеме фиг.2.

начинают превышать статические значения токов I12, (I14). Рассмотрим этот режим в схеме фиг.2.

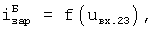

Если выходной ток ДК  становится больше, чем ток I12, то транзистор 8 запирается (потенциал эмиттера этого транзистора становится меньше, чем Ec1), открывается "диодный" повторитель тока 20, создавая новый путь прохождения большого сигнала - на вход повторителя тока 18, а затем на выход промежуточного каскада (в емкость 16). Таким образом, для этого уровня большого сигнала приращения тока

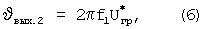

становится больше, чем ток I12, то транзистор 8 запирается (потенциал эмиттера этого транзистора становится меньше, чем Ec1), открывается "диодный" повторитель тока 20, создавая новый путь прохождения большого сигнала - на вход повторителя тока 18, а затем на выход промежуточного каскада (в емкость 16). Таким образом, для этого уровня большого сигнала приращения тока  передаются в емкость 16 по каналу с минимальной "электрической длиной", включающему элементы 20 и 18. Аналогично работает и канал передачи большого сигнала на элементах 21, 19 для другой полярности uвх.2.3. При выполнении данных условий быстродействие ОУ фиг.2 приближается к предельно возможному, характерному для линейного режима, а максимальная скорость нарастания выходного напряжения достигает значений

передаются в емкость 16 по каналу с минимальной "электрической длиной", включающему элементы 20 и 18. Аналогично работает и канал передачи большого сигнала на элементах 21, 19 для другой полярности uвх.2.3. При выполнении данных условий быстродействие ОУ фиг.2 приближается к предельно возможному, характерному для линейного режима, а максимальная скорость нарастания выходного напряжения достигает значений

где  - напряжение ограничения выходного тока

- напряжение ограничения выходного тока

входного каскада для большого сигнала.

входного каскада для большого сигнала.

В схеме фиг.3 снижаются ограничения на величину напряжения на базах транзисторов 8 и 9, так как при малых сигналах транзистор 20 закрыт. Однако, если потенциал эмиттера транзистора 8 становится меньше потенциала +Ec1, транзистор 20 входит в активный режим и передает на вход повторителя 18 разницу токов

Аналогично работает и ОУ фиг.4, в котором одновременно созданы каналы передачи "избыточных" токов со всех выходов 4-7 на выход промежуточного каскада.

Особенность схемы ОУ фиг.5 состоит в наличии у входного каскада (кроме малосигнальных выходов 4, 5, 6, 7) двух выходов 25 и 26 для большого сигнала. Пример построения таких входных каскадов дан на фиг.7. В этом случае "большой" сигнал может подаваться непосредственно на вход повторителей тока 18 и 19.

Таким образом, в зависимости от вариантов построения входного каскада 1, возможно изменение состава функциональных узлов ОУ и связей между ними, что нашло отражение в многозвенной формуле изобретения.

Результаты компьютерного моделирования в среде Pspice фиг.1-фиг.5 показывают, что заявляемое устройство имеет высокие значения максимальной скорости нарастания выходного напряжения ϑ вых≥4000 В/мкс и по совокупности обобщенных показателей качества превосходит лучшие зарубежные аналоги.

Источники информации

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Рис.6.11.

2. Двухтактный операционный усилитель. Патент РФ №2193273 Н 03 f 3/45.

3. Дифференциальный усилитель. Патент США №4649352, кл. 330-261.

4. Operational amplifier circuit. Патент США №4463319, кл. 330-261.

5. Операционные усилители с непосредственной связью каскадов / В.И.Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М.Соколов. - Л., 1979.

6. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. – 216 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2015 |

|

RU2621289C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374756C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ "НАПРЯЖЕНИЕ-ТОК" С ШИРОКИМ ДИАПАЗОНОМ ЛИНЕЙНОЙ РАБОТЫ | 2017 |

|

RU2658818C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2006 |

|

RU2321157C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2283533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

Изобретение относится к радиотехнике и связи для использования в качестве устройства усиления широкополосных, в частности, импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения. Технический результат заключается в повышении быстродействия и получении скорости нарастания на уровне 4000-6000 В/мкс с возможностью использования микронных технологий с топологическими нормами от 1,5-2 мкм. Операционный усилитель содержит входной каскад (1), выполненный в виде дифференциальных усилителей, не имеющих ограничений выходного тока при изменении входного напряжения до нескольких вольт, р-n-р транзисторы (Т) (8, 9), n-р-n Т (10, 11). Эмиттеры Т (8, 9, 10, 11) соединены с соответствующими противофазными токовыми выходами каскада (1), коллекторы Т (9, 11) объединены и связаны с корректирующим конденсатором (16) и выходным буферным усилителем (17). Между коллекторами Т (8, 9) и коллекторами Т(10, 11) введены повторители тока (ПТ) (19,18). 7 з.п. ф-лы, 11 ил.

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| СОВМЕЩЕННАЯ АНТЕННАЯ СИСТЕМА | 1991 |

|

RU2039399C1 |

| US 4387309, 07.06.1983 | |||

| US 4649352, 10.03.1987 | |||

| Застежка-молния | 1981 |

|

SU1071205A3 |

| US 6356153 A, 12.03.2002. | |||

Авторы

Даты

2005-06-27—Публикация

2003-10-06—Подача