Изобретение относится к области радиосвязи и может быть использовано при разработке широкополосных радиостанций и систем передачи данных с повышенной скрытностью и помехоустойчивостью.

Известно устройство для передачи и приема модулированных по фазе и частоте сигналов [АС №684750, 7 МПК Н 04 В 7/165, 1979 г.; Н 04 J 1/20, заявка Японии №49-25043, ПМК Н 04 В, 1974 г.], которые содержат на передающей стороне - синхронизатор, выходы которого через соответствующие коммутаторы подключены к входам фазового частотного модулятора, и выходной согласующий блок, при этом на вторые входы коммутаторов поданы информационные сигналы, на приемной стороне - линейный согласующий блок, выход которого подключен к входу блока задержки и к входам полосовых фильтров, выходы которых через соответствующие амплитудные детекторы подключены к входам детектора максимального сигнала, выходы которого через интеграторы соединены с входами триггера, а также частотный модулятор и блок формирования опорного сигнала, выход которого подключен к первому входу фазового детектора, причем выход соответствующего интегратора соединен с входом частотного модулятора.

Недостатком данных устройств является низкая помехоустойчивость. Известно устройство для передачи и приема модулированных по фазе и частоте сигналов [АС №684750, 7МПК Н 04 В 7/165, 1979 г.], содержащее на передающей стороне - последовательно соединенные синхронизатор, первый коммутатор, фазовый модулятор, смеситель, ко второму входу которого подключен выход частотного модулятора, состоящего из двух ключей, выходы которых являются выходом частотного модулятора, первые входы которых через второй коммутатор подключены ко второму выходу синхронизатора, причем вторые входы ключей частотного модулятора через соответствующие выходы синтезатора частот подключены ко второму входу фазового модулятора, а также содержит выходной согласующий блок, выход которого является выходом передающей стороны, на приемной стороне - линейный согласующий блок, вход которого является входом приемной стороны, последовательно соединенные блок задержки, смеситель, ко второму входу которого подключен выход частотного модулятора, состоящего из двух ключей, выходы которых являются выходом частотного модулятора, усилитель промежуточной частоты и фазовый детектор, выход которого является первым выходом приемной стороны, причем выход усилителя промежуточной частоты подключен к блоку формирования опорного сигнала, первый выход которого через синтезатор частот соединен с первыми входами ключей частотного модулятора, а второй выход соединен со вторым входом фазового детектора, а также содержит два полосовых фильтра, входы которых подключены к входу блока задержки, а выходы через соответствующие амплитудные детекторы соединены с соответствующими входами детектора максимального сигнала, выходы которого через соответствующие интеграторы подключены ко вторым входам ключей частотного модулятора и соответствующим входам триггера, выход которого является вторым выходом приемной стороны.

Недостатком этого устройства является то, что для передачи логических «1» и «0» двоичной информации необходимо иметь две полосы частотного спектра и низкая помехоустойчивость.

Низкая помехоустойчивость устройства объясняется тем, что в условиях прицельных помех на приемной стороне с выхода интеграторов на входы ключей частотного модулятора триггера возможно одновременное поступление двух логических «1» или «0», что приведет к нарушению алгоритма работы как частотного модулятора, так и триггера, а это в свою очередь вызовет нарушение условий приема фазомодулированного (ФМ) сигнала и, как следствие, снизит качество воспроизведения информации.

Из известных устройств наиболее близким по технической сущности и достигаемому эффекту является устройство для передачи и приема модулированных по фазе и частоте сигналов [Пат. RU 2228576, 7 МПК Н 04 В 7/00, 10.05.2004], содержащее на передающей стороне - последовательно соединенные синхронизатор, первый коммутатор, фазовый модулятор, первый смеситель, ко второму входу которого подключен выход частотного модулятора, состоящего из двух ключей, выходы которых являются выходом частотного модулятора, первый полосовой фильтр, второй смеситель и выходной согласующий блок, выход которого является выходом передающей стороны, причем второй вход второго смесителя через последовательно соединенные первый линейный частотно-модулированный гетеродин, первый блок «ИЛИ», первый делитель частоты и первый блок «И» подключен ко второму входу второго ключа и через первый синтезатор частот - ко вторым входам фазового модулятора и первого ключа, первый вход которого соединен с первым входом второго ключа и выходом второго коммутатора, первый вход которого подключен ко второму выходу синхронизатора, а второй вход - через последовательно соединенные второй блок «ИЛИ» и второй блок «И» подключен ко второму входу передающей стороны, являющемуся информационным входом устройства, при этом первый вход второго блока «И» соединен со вторым входом первого блока «И», первым выходом блока управления и первым входом третьего блока «И», второй вход которого подключен к третьему входу передающей стороны, являющемуся информационным входом устройства, а выход через третий блок «ИЛИ» соединен со вторым входом первого коммутатора, причем второй вход третьего блока «ИЛИ» через последовательно соединенные блок «И-НЕ», второй выход которого подключен ко второму входу второго блока «ИЛИ», и первый согласованный фильтр соединен со вторым входом первого блока «ИЛИ» и первым входом блока управления, второй вход которого подключен к первому входу передающей стороны, являющемуся входом управляющего сигнала устройства, а второй выход блока управления соединен со вторыми входами блока «И-НЕ» и четвертого блока «И», первый вход которого через второй делитель частоты подключен ко второму выходу синтезатора частот, первому входу первого линейного частотно-модулированного гетеродина и выходу первого опорного генератора, а выход четвертого блока «И» через генератор кодов соединен с первым согласованным фильтром, на приемной стороне - последовательно соединенные линейный согласующий блок, вход которого является входом приемной стороны, третий смеситель, второй полосовой фильтр, блок задержки, четвертый смеситель, ко второму входу которого подключен выход частотного модулятора, состоящего из двух ключей, выходы которых являются выходом частотного модулятора, и усилитель промежуточной частоты, выход которого подключен к первому входу фазового детектора и через блок формирования опорного сигнала соединен со вторым входом фазового детектора, выход которого является выходом приемной стороны, причем первый выход блока формирования опорного сигнала через второй синтезатор частот подключен к первым входам третьего и четвертого ключей, а также содержит два полосовых фильтра, входы которых подключены к входу блока задержки, а выходы через соответствующие амплитудные детекторы соединены с соответствующими входами детектора максимального сигнала, выходы которого через соответствующие интеграторы подключены ко вторым входам ключей частотного модулятора и соответствующим входам третьего триггера, выход которого через последовательно соединенные седьмой блок «И», второй согласованный фильтр, второй триггер, шестой блок «И», выход которого подключен ко второму входу второго триггера, первый триггер, формирователь импульсов, четвертый блок «ИЛИ» и второй линейный частотно-модулированный гетеродин подключен ко второму входу третьего смесителя, причем второй вход второго линейного частотно-модулированного гетеродина соединен со вторым входом шестого блока «И» и выходом второго опорного генератора, выход которого через последовательно соединенные пятый блок «И» и третий делитель частоты подключен ко второму входу четвертого блока «ИЛИ», а соответствующие выходы первого триггера соединены с соответствующими входами пятого и седьмого блоков «И».

В известном устройстве для передачи информационных сигналов (логических «1» и «0» двоичной информации), а также повышения помехоустойчивости в условиях преднамеренных помех применяется модуляция центральных частот ФМ-ЧМ сигналов по линейному закону. Общая ширина спектра излучаемого информационного сигнала состоит из суммы удвоенного значения девиации частоты линейного частотно-модулированного сигнала и ширины спектра фазоманипулированного сигнала. Значение второго слагаемого зависит от длительности информационного сигнала (логических «1»и «0»).

Таким образом, недостатком прототипа является завышенная занимаемая полоса частотного спектра.

Техническим результатом изобретения является уменьшение занимаемой полосы частотного спектра и сохранение высокой помехоустойчивости в условиях преднамеренных помех за счет модуляции центральных частот передаваемых линейных частотно-модулированных (ЛЧМ) радиоимпульсов по информационному закону без смены знака скорости перестройки частоты и длительности модуляции, а также применения на приемной стороне согласованной фильтрации с весовой обработкой и управляемой временной селекции сжатых по времени видеоимпульсов для выделения информационного сигнала (логических «1» и «0»).

Указанный результат достигается за счет того, что в известное Устройство для передачи и приема модулированных по фазе и частоте сигналов, содержащее на передающей стороне - последовательно соединенные первый полосовой фильтр, смеситель и выходной согласующий блок, выход которого является выходом передающей стороны, а также синхронизатор, первый синтезатор частот, линейный частотно-модулированный гетеродин, первый и второй коммутаторы, на приемной стороне - последовательно соединенные линейный согласующий блок, вход которого является входом приемной стороны, второй смеситель и второй полосовой фильтр, усилитель промежуточной частоты, последовательно соединенные блок «И» и делитель частоты, а также блок «ИЛИ», второй синтезатор частот, амплитудный детектор, интегратор и два триггера, при этом выход первого триггера является выходом приемной стороны, на передающей стороне первый вход линейного частотно-модулированного гетеродина соединен с выходом синхронизатора и первым входом второго коммутатора, второй вход линейного частотно-модулированного гетеродина подключен к входу синхронизатора и второму выходу первого синтезатора частот, первый выход которого соединен со вторым входом смесителя, третий вход линейного частотно-модулированного гетеродина соединен с выходом первого коммутатора, первый вход которого подключен к первому входу передающей стороны, являющемуся информационным входом устройства, причем второй вход первого коммутатора соединен с выходом второго коммутатора, а четвертый вход линейного частотно-модулированного гетеродина подключен ко второму входу передающей стороны, являющемуся управляющим входом устройства, первый выход линейного частотно-модулированного гетеродина соединен с входом первого полосового фильтра, а второй выход линейного частотно-модулированного гетеродина подключен ко второму входу второго коммутатора, при этом синхронизатор выполнен в виде последовательно соединенных формирователя импульсов, вход которого подключен к входу синхронизатора и инвертора, выход которого соединен с выходом синхронизатора, на приемной стороне введены дисперсионный фильтр сжатия, ключ, мультиплексор и блок формирования селектирующих, управляющих импульсов и выделения информационных сигналов, при этом выход второго полосового фильтра через дисперсионный фильтр сжатия подключен к информационному входу ключа, выход которого через последовательно соединенные усилитель промежуточной частоты и амплитудный детектор подключен к интегратору, выход которого соединен с первыми входами блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов и мультиплексора, выход которого подключен к первому входу второго триггера, первый и второй выходы которого соединены соответственно с первым входом блока «ИЛИ» и вторым (управляющим) входом ключа, причем второй вход блока «ИЛИ» подключен к первому выходу блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов, второй вход которого соединен со вторым входом второго триггера и выходом делителя частоты, второй вход которого подключен к четвертому выходу блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов, второй и третий выходы которого соединены соответственно со вторым и третьим входами мультиплексора, а первый и второй входы первого триггера подключены соответственно к пятому и шестому выходам блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов, третий вход которого соединен со вторым выходом второго синтезатора частот и первым входом блока «И», второй вход которого подключен к выходу блока »ИЛИ», а первый выход второго синтезатора частот соединен со вторым входом второго смесителя.

Предлагаемое техническое решение является новым, поскольку из общедоступных сведений не известно устройство для передачи и приема модулированных по фазе и частоте сигналов, обеспечивающее уменьшение занимаемой полосы частотного спектра и сохранение высокой помехоустойчивости в условиях преднамеренных помех за счет модуляции центральных частот передаваемых линейных частотно-модулированных (ЛЧМ) радиоимпульсов по информационному закону без смены знака скорости перестройки частоты и длительности модуляции, а также применения на приемной стороне согласованной фильтрации с весовой обработкой и управляемой временной селекции сжатых по времени видеоимпульсов для выделения информационного сигнала (логических «1» и «0»).

В предлагаемом устройстве для уменьшения занимаемой полосы частотного спектра передаваемых информационных сигналов (логических «1» и «0» двоичной информации) предлагается использовать модуляцию центральной частоты излучаемых ЛЧМ радиоимпульсов по информационному закону.

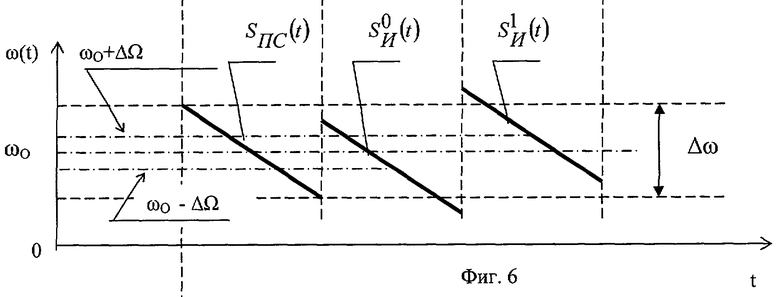

Предположим, что при передаче логической «1» центральная частота ЛЧМ радиоимпульса увеличивается на ΩM, а при передаче логического «0» - уменьшается на ΩM.

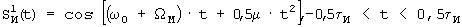

Тогда, формируемый передающей стороной информационный сигнал принимает вид

при передаче логической «1», или (1)

при передаче логического «0»,

где ω0=2πF0 - центральная угловая частота информационного ЛЧМ сигнала;

- скорость перестройки частоты;

- скорость перестройки частоты;

Δω=2π·ΔF - девиация частоты;

τИ - длительность информационного ЛЧМ сигнала;

ΩМ=2πFM - величина частотного сдвига.

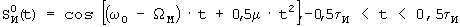

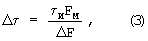

Величину отстройки начальной частоты информационного ЛЧМ сигнала выберем из условия (связь с амплитудой)

где ΔωДФС - полоса пропускания дисперсионного фильтра сжатия.

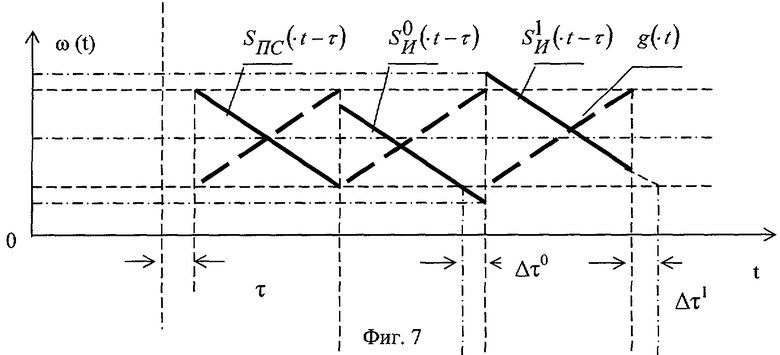

При приеме информационных ЛЧМ радиоимпульсов (1) на выходе дисперсионного фильтра появляются сжатые по времени сигналы, имеющие временные сдвиги относительно автокорреляционной функции [Ч.Кук, М. Бернфельд. Радиолокационные сигналы. Теория и применение. Перевод с английского под редакцией B.C.Кельзона. М., «Сов. радио», 1971, фиг.6.2, стр.151].

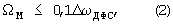

Величину временного сдвига сжатого сигнала можно найти из выражения

Так, например, для девиации частоты ΔF=1,0·МГц, τИ=32,0·мкс и частотном сдвиге FM=50,0 кГц, расчетный временной сдвиг сжатого сигнала, найденный из выражения (3), составит 1,6 мкс.

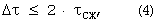

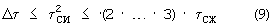

Величина временного сдвига сжатого по времени информационного сигнала, найденная из (3), должна удовлетворять следующему условию

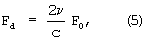

Однако, в реальных условиях информационный ЛЧМ сигнал, поступающий на вход приемной стороны, не всегда является точной копией излученного сигнала. Наиболее общая форма искажений наблюдается в том случае, если приемная сторона размещается на подвижном объекте, скорость перемещения которого имеет радиальную составляющую скорости по отношению к передающей стороне. Это может привести к появлению дополнительного сдвига центральной частоты информационного сигнала в ту или иную сторону на величину доплеровского приращения частоты Fd.

Для устройства связи, работающего на прием, например, в ультракоротковолновом (УКВ) диапазоне длин волн и установленного на самолете, величину доплеровского приращения частоты найдем из выражения

где v - радиальная скорость;

с - скорость света.

Так, для радиальной скорости v=200 м/с, например, самолет выполняет полет в направлении передающей стороны, находящейся на пункте управления воздушным движением, центральной частоты передаваемого информационного сигнала F0=220,0 МГц и скорости света с=3·108 м/с, доплеровское приращение частоты Fd составит 293 Гц. Величина приращения временного сдвига сигнала, сжатого по времени, вызванного доплеровским приращением частоты, найденная из (3), не превышает 10 нс, которым можно пренебречь при проведении дальнейших расчетов.

Выделение информационного сигнала (логических «1» и «0») в предлагаемом устройстве осуществляется с помощью селектирующих импульсов (стробов). С этой целью на вход приемной стороны поступает синхронизирующий ЛЧМ радиоимпульс (пилот-сигнал) для наведения стробов на информационные сигналы.

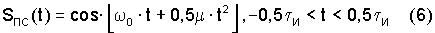

Параметры пилот-сигнала согласованы с импульсной характеристикой дисперсионного фильтра сжатия

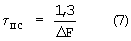

Длительность сжатого пилот-сигнала τПС при измерении на уровне 4 дБ ниже пиковой амплитуды близка к расчетной [Ч.Кук, М. Бернфельд. Радиолокационные сигналы. Теория и применение. Перевод с английского под редакцией B.C.Кельзона. М., «Сов. радио»]

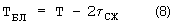

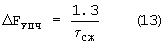

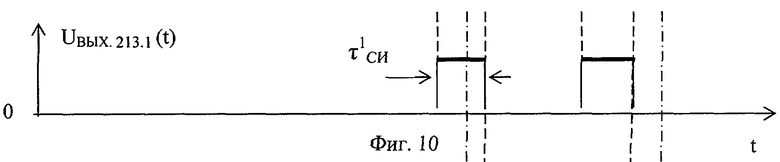

начало формирования первого строба  задерживается относительно пилот-сигнала на длительность бланка ТБЛ (см. фиг.9 и 10)

задерживается относительно пилот-сигнала на длительность бланка ТБЛ (см. фиг.9 и 10)

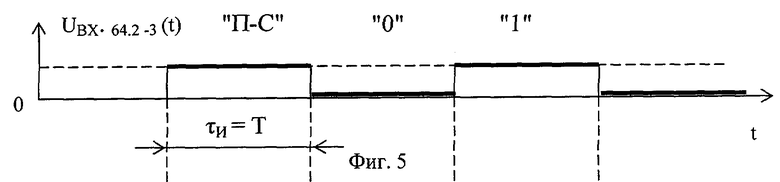

где Т - период повторения пилот-сигнала (фиг.5).

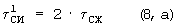

Длительность первого строба выберем из условия

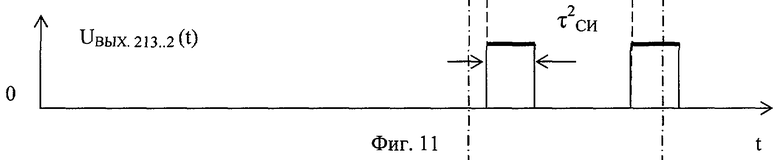

Начало формирования второго строба  привязано к заднему фронту первого строба (см. фиг.11).

привязано к заднему фронту первого строба (см. фиг.11).

Длительность второго строба выберем из условия

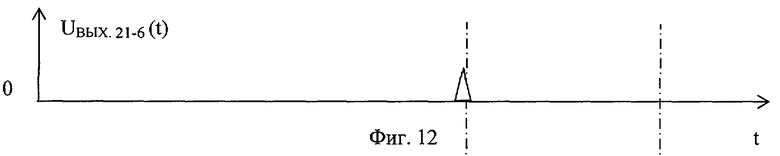

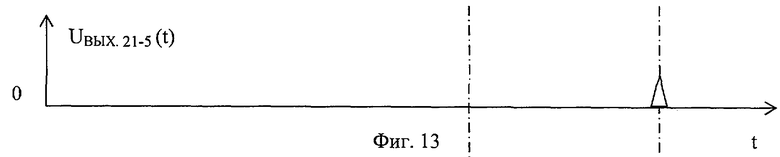

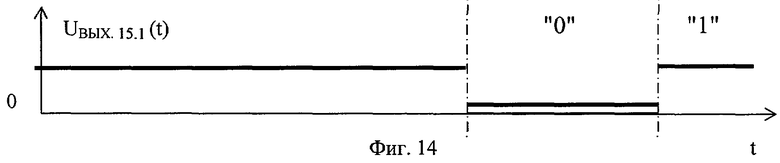

Первый строб предназначен для выделения сигнала логического «0» и (см. фиг.12), а второй - логической «1» (см. фиг.13).

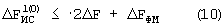

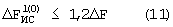

Общая ширина занимаемой полосы частотного спектра прототипа выбрана из условия маскировки энергетических спектров информационных сигналов и не должна превышать удвоенного значения ширины спектра передаваемого информационного сигнала

где ΔFФМ=ΔF - ширина спектра фазоманипулированного сигнала.

Занимаемая полоса частотного спектра (девиация частоты) информационного ЛЧМ сигнала (1) на выходе передающей стороны предлагаемого устройства с учетом (2) не должна превышать

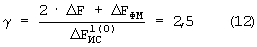

Из отношения полос частотного спектра, необходимых для функционирования прототипа (10) и предлагаемого устройства (11), найдем качественную оценку γ предлагаемого устройства

Так, например, для девиации частоты ΔF=1,0 МГц, уменьшение занимаемой полосы частотного спектра γ=2,5.

Таким образом, в предлагаемом устройстве, за счет введения новых связей и блоков, обеспечивается уменьшение занимаемой полосы частотного спектра в 2,5 раза.

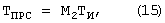

На фиг.1 приведена структурная схема передающей и приемной сторон предлагаемого устройства.

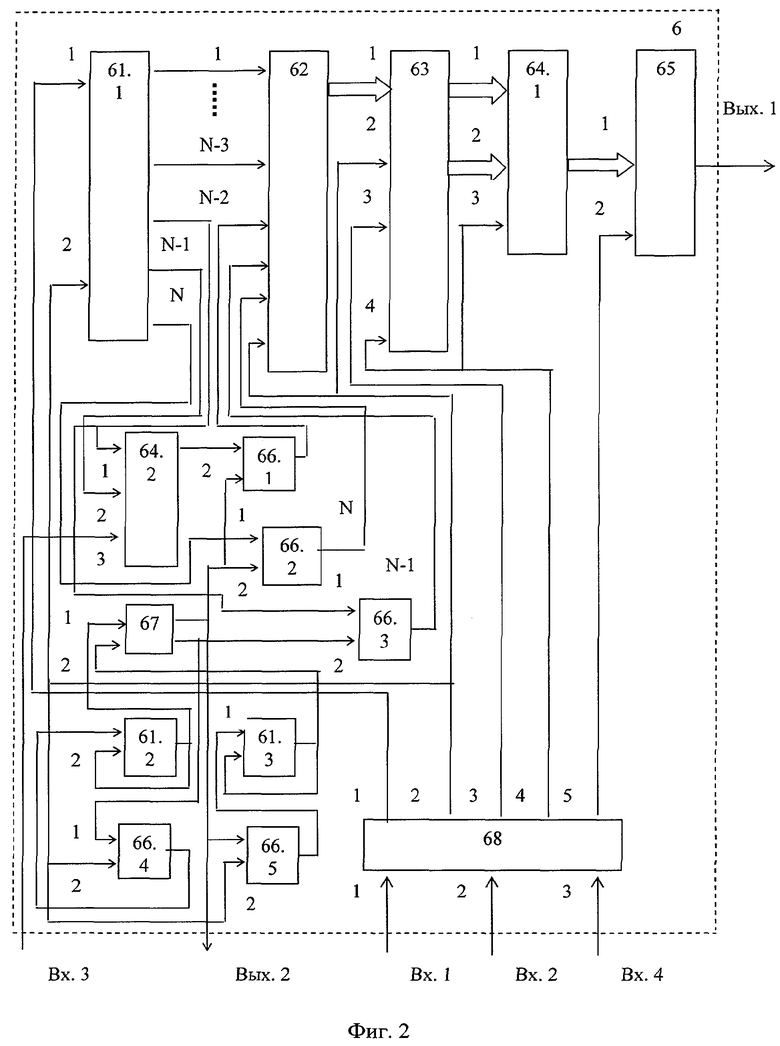

На фиг.2 приведена структурная схема линейного частотно-модулированного гетеродина.

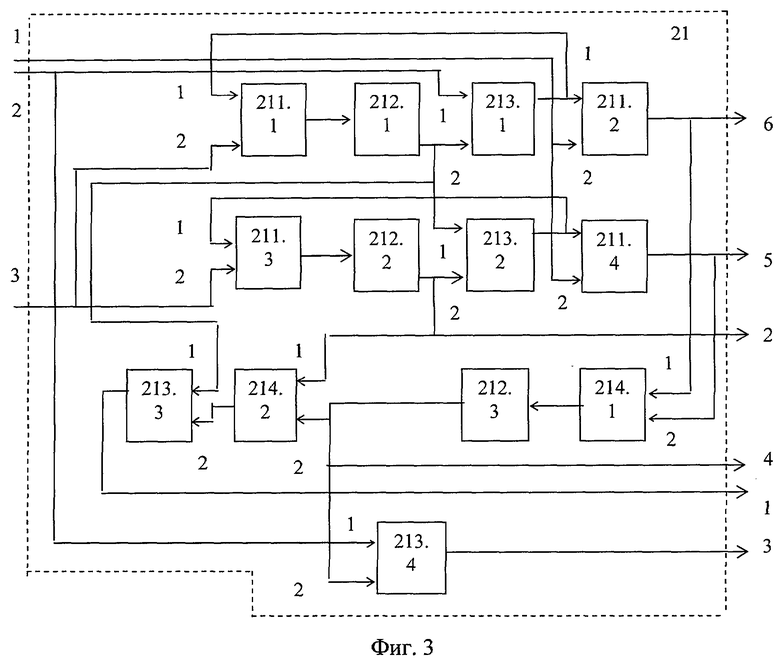

На фиг.3 приведена структурная схема блока формирования селектирующих, управляющих импульсов и выделение информационных сигналов.

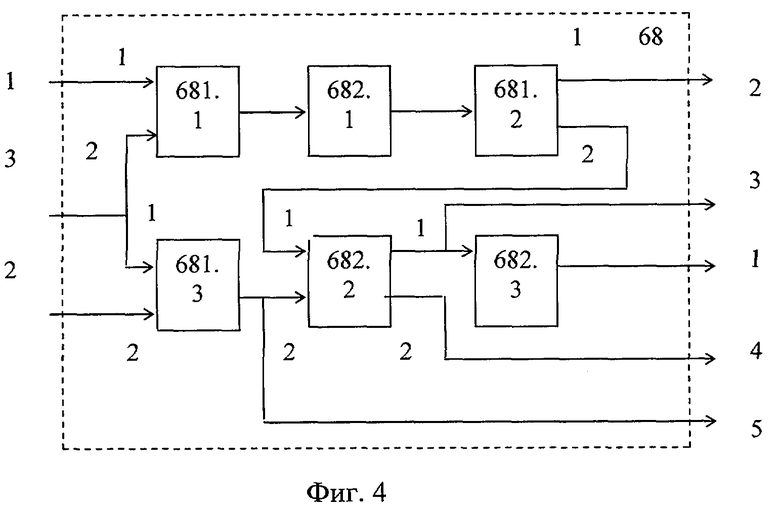

На фиг.4 приведена структурная схема блока управления.

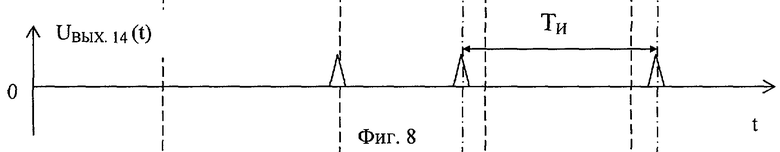

На фиг.5-14 приведены эпюры, поясняющие работу передающей и приемной сторон предлагаемого устройства.

Устройство содержит на передающей стороне (фиг.1) - первый полосовой фильтр 1.1, первый смеситель 2.1, выходной согласующий блок 3, синхронизатор 4, первый синтезатор 5.1 частот, линейный частотно-модулированный гетеродин 6, первый и второй коммутаторы 7.1 и 7.2, при этом синхронизатор 4 состоит из формирователя 16 импульсов и инвертора 17, на приемной стороне - второй полосовой фильтр 1.2, второй смеситель 2.2, второй синтезатор 5.2 частот, усилитель 9 промежуточной частоты, блок 10 «И», делитель 11 частоты, блок 12 «ИЛИ», амплитудный детектор 13, интегратор 14, первый и второй триггеры 15.1 и 15.2, дисперсионный фильтр 18 сжатия, ключ 19, мультиплексор 20 и блок 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов.

Причем, на передающей стороне - первый коммутатор 7.1, вход которого соединен с первым (информационным) входом передающей стороны, а выход подключен к третьему входу линейного частотно-модулированного гетеродина 6, первый выход которого через последовательно соединенные первый полосовой фильтр 1.1 и первый смеситель 2.1 подключен к выходному согласующему блоку 3, выход которого является выходом передающей стороны, причем второй вход первого смесителя 2.1 соединен с первым выходом синтезатора 5.1 частот, второй выход которого подключен ко второму входу линейного частотно-модулированного гетеродина 6 и синхронизатору 4, состоящему из последовательно соединенных формирователя 16 импульсов, вход которого подключен к входу синхронизатора 4 и инвертора 17, выход которого соединен с выходом синхронизатора 4, выход которого подключен к первому входу линейного частотно-модулированного гетеродина 6 и через второй коммутатор 7.2 соединен со вторым входом первого коммутатора 7.1, при этом второй вход второго коммутатора 7.2 подключен ко второму выходу линейного частотно-модулированного гетеродина 6, четвертый вход которого соединен со вторым (управляющим) входом передающей стороны, на приемной стороне - линейный согласующий блок 8, вход которого соединен с входом приемной стороны, а выход линейного согласующего блока 8 через последовательно соединенные второй смеситель 2.2, второй полосовой фильтр 1.2, дисперсионный фильтр 18 сжатия, ключ 19, усилитель 9 промежуточной частоты, амплитудный детектор 13, интегратор 14 подключен к первому входу блока 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов, пятый и шестой выходы которого соединены соответственно с первым и вторым входами первого триггера 15.1, выход которого является выходом приемной стороны, причем выход интегратора 14 через последовательно соединенные мультиплексор 20, второй триггер 15.2, второй (инверсный) выход которого подключен ко второму входу ключа 19, и блок 12 «ИЛИ» подключен ко второму входу блока 10 «И», первый вход которого соединен со вторым выходом второго синтезатора 5.2 частот, первый выход которого подключен ко второму входу второго смесителя 2.2, а выход блока 10 «И» соединен с первым входом делителя 11 частоты, выход которого соединен со вторыми входами второго триггера 15.2 и блока 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов, третий вход которого подключен ко второму выходу второго синтезатора 5.2 частот, причем первый, второй и третий выходы блока 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов соединены соответственно со вторым входом блока 12 «ИЛИ», вторым и третьим входами мультиплексора 20, а четвертый выход блока 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов подключен ко второму входу делителя 11 частоты.

Линейный частотно-модулированный гетеродин 6 выполнен согласно схеме, приведенной на фиг.2, на котором обозначено:

61.1, 61.2, 61.3 - первый, второй и третий счетчики адреса, синхронизирующих информационных сигналов;

62 - регистр;

63 - постоянное запоминающее устройство (ПЗУ);

64.1, 64.2 - первый и второй мультиплексоры;

65 - цифроаналоговый преобразователь (ЦАП);

66.1, 66.2, 66.3, 66.4 и 66.5 - первый, второй, третий, четвертый и пятый блоки «И»;

67 - триггер;

68 - блок управления.

Входы блока 68 управления соединены соответственно с первым, вторым и четвертым входами линейного частотно-модулированного гетеродина 6, третий вход которого подключен к третьему входу второго мультиплексора 64.2, причем первый выход блока 68 управления соединен с первым входом первого счетчика 61.1 адреса, цифровые выходы которого от 1 до N-3 разрядов подключены к соответствующим информационным входам регистра 62, цифровой выход которого из N разрядов соединен с постоянным запоминающим устройством 63, первый и второй выходы которого через первый мультиплексор 64.1 подключены к первому входу цифроаналогового преобразователя 65, выход которого соединен с первым выходом линейного частотно-модулированного гетеродина 6, причем цифровой выход N-2 первого счетчика 61.1 адреса подключен к первым входам второго мультиплексора 64.2 и третьего блока 66.3 «И», цифровой выход N-1 первого счетчика 61.1 адреса соединен со вторым входом второго мультиплексора 64.2, выход которого через первый блок 66.1 «И» подключен к информационному входу N-2 регистра 62, N-1 вход которого соединен с выходом третьего блока 66.3 «И», второй вход которого подключен ко второму выходу триггера 67, первый выход которого соединен со вторыми входами первого и второго блоков 66.1 и 66.2 «И», первый вход которого подключен к цифровому выходу N первого счетчика 61.1 адреса, а выход второго блока 66.2 «И» соединен с информационным входом N регистра 62, второй (управляющий) вход которого подключен соответственно ко вторым входам первого счетчика 61.1 адреса, постоянного запоминающего устройства 63 и второму выходу блока управления 68, третий выход которого соединен с третьим входом постоянного запоминающего устройства 63, четвертый вход которого подключен к третьему входу первого мультиплексора 64.1 и четвертому выходу блока 68 управления, пятый выход которого соединен со вторым входом цифроаналогового преобразователя 65, причем соответствующие входы триггера 67 подключены соответственно к выходам и вторым входам второго и третьего счетчиков 61.2 и 61.3 синхронизирующих и информационных сигналов, первые входы которых соединены соответственно с выходами четвертого и пятого блоков 66.4 и 66.5 «И», первый вход которого подключен ко второму выходу линейного частотно-модулированного гетеродина 6 и первому выходу триггера 67, второй выход которого соединен также с первым входом четвертого блока 66.4 «И», причем вторые входы четвертого и пятого блоков 66.4 и 66.5 «И» подключены ко второму выходу блока 68 управления.

Блок 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов выполнен согласно схеме, приведенной на фиг. 3, на которой обозначено:

211.1, 211.2, 211.3 и 211.4 - первый, второй, третий и четвертый блоки «И»;

212.1, 212.2 и 212.3 - первый, второй и третий делители частоты;

213.1, 213.2, 213.3 и 213.4 - первый, второй, третий и четвертый триггеры;

214.1 и 214.2 - первый и второй блоки «ИЛИ».

Блок 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов содержит последовательно соединенные первый блок 211.1 «И», первый делитель 212.1 частоты и первый триггер 213.1, первый вход которого соединен со вторым входом блока 21, а выход подключен к первым входам первого и второго блоков 211.1 и 211.2 «И», выход которого является шестым выходом блока 21, причем второй вход первого блока 211.1 «И» соединен с третьим входом блока 21 и вторым входом третьего блока 211.3 «И», выход которого через последовательно соединенные второй делитель 212.2 частоты и второй триггер 213.2 подключен к первым входам третьего и четвертого блоков 211.3 и 211.4 «И», выход которого является пятым выходом блока 21, причем второй вход четвертого блока 211.4 «И» соединен со вторым входом второго блока 212.2 «И» и первым входом блока 21, а выходы второго и четвертого блоков 211.2 и 211.4 «И» подключены соответственно к первому и второму входам первого блока 214.1 «ИЛИ», выход которого через третий делитель 212.3 частоты соединен с четвертым выходом блока 21 и через четвертый триггер 213.4 подключен к третьему выходу блока 21, причем первый вход четвертого триггера 213.4 соединен со вторым входом блока 21, кроме того, выход третьего делителя 212.3 частоты через последовательно соединенные второй блок 214.2 «ИЛИ» и третий триггер 213.3 подключен к первому выходу блока 21, при этом первый вход второго блока 214.2 «ИЛИ» соединен с выходом второго делителя 212.2 частоты и вторым выходом блока 21, а первый вход третьего триггера 213.3 подключен к выходу первого делителя 212.1 частоты и первому входу второго триггера 213.2.

Блок 68 управления выполнен согласно схеме, приведенной на фиг.4, на которой обозначено:

681.1, 681.2 и 681.3 - первый, второй и третий блоки «И»;

682.1, 682.2 и 682.3 - первый, второй и третий триггеры.

Блок 68 управления содержит последовательно соединенные первый блок 681.1 «И», первый вход которого подключен к первому входу блока 68, первый триггер 682.1 и второй блок 681.2 «И», первый выход которого подключен ко второму выходу блока 68, причем второй вход первого блока 681.1 «И» подключен к третьему входу блока 68 и первому входу третьего блока 681.3 «И», второй вход которого соединен со вторым входом блока 68, а выход - подключен к пятому входу блока 68 и через последовательно соединенные второй и третий триггеры 682.2 и 682.3 подключен к первому выходу блока 68, причем второй выход второго блока 681.2 «И» соединен с первым входом второго триггера 682.2, выходы которого подключены также к третьему и четвертому выходам блока 68.

Первый и второй полосовые фильтры 1.1 и 1.2 могут быть реализованы, например, по схеме фильтра сосредоточенной селекции [Свистов В.М, Радиолокационные сигналы и их обработка. М.: «Сов. Радио», 1977. - 448 с., ил., стр.130, фиг.3.13].

Первый и второй смесители 2.1 и 2.2 представляют собой, например, диодный преобразователь частоты, выполненный, например, по балансной схеме [М.С.Шумилин, В.Б.Козырев, В.А.Власов. Проектирование транзисторных каскадов передатчиков. Учебное пособие для техникумов. - М.: Радио и связь, 1987. - 320 с.: ил., стр.178, фиг.2.77].

Первый и второй синтезаторы 5.1 и 5.2 частот состоят, например, из опорного гетеродина, выполненного, например, на микросхеме серии КР1533ЛН2 по схеме (В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко. Микросхемы и их применение: Справ. Пособие. - 3-е изд., перераб. и доп. - М.: Радио и связь, 1989 г., 240 с., стр.210, фиг.7.10, д], выход которой через второй выход первого (второго) синтезатора 5.1 (5.2) соединен со вторым входом ЛЧМ гетеродина 6 и синхронизатором 4 (первым входом блока 10 «И» и третьим входом блока 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов), а также подключен к фазовому детектору, входящему в состав схемы ФАПЧ с умножением в N раз [Гальперин М.В. Практическая схемотехника в промышленной автоматике. - М.: 1987. - 320 с.: ил., см. стр.183, рис 4.18, б], где N - коэффициент умножения опорного сигнала при формировании напряжения гетеродина для передающей (приемной) сторон соответственно, а выход ФАПЧ является первым выходом первого (второго) синтезатора 5.1 (5.2) частот.

Дисперсионный фильтр 18 сжатия представляет собой, например, ультразвуковое устройство типа дифракционная решетка [Ч.КУК, М.БЕРНФЕЛЬД. Радиолокационные сигналы. Теория и применение. Перевод с английского под редакцией B.C.КЕЛЬЗОНА. М., «Сов. радио», 1971, фиг.13.23, стр.498].

Ключ 19 может быть реализован, например, на микросхеме серии 286КТ2 [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.193, 222].

Блоки 10, 66.1...66.4, 66.5, 212.1...212.4, 681.1...681.3 «И», коммутаторы 7.1 (7.2) и инвертор 17, а также блоки 12, 214.1 и 214.2 «ИЛИ» могут быть реализованы, например, на микросхемах серии 1533ЛИ1, 1533ЛН1 и 1533ЛЛ1 [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.12, 13, 17 и 74, 75].

Делители частоты 11, 212.1, 212.2 и 212,3, формирователь импульсов 16, счетчики адреса 61.1, синхронизирующих и информационных сигналов 61.2 и 61.3 могут быть выполнены, например, на микросхемах серии КС193ИЕ7А и КР1533ИЕ7 [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.26, 80], соответственно.

Триггеры 15.1, 15.2, 67, 211.1 ... 211.6 и 682.1 ... 682.3 могут быть реализованы, например, на микросхемах серии 1533 ТМ2 [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.35, 86].

Мультиплексоры 20, 64.1 и 64.2 могут быть выполнены, например, на микросхемах серии КР1533КП11А [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.44, 88].

Регистр 62 представляет собой регистр на триггерах D-типа, выполненный, например, на микросхеме серии КР1533ИР23 [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.33, 85].

Постоянное запоминающее устройство (ПЗУ) 63 представляет собой однократно программируемое постоянное запоминающее устройство выполненное, например, на двух микросхемах серии КР556РТ17 [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.111, 124].

Цифроаналоговый преобразователь (ЦАП) 65 представляет собой, например, быстродействующий десятиразрядный ЦАП, выполненный, например, на микросхеме серии КР11118ПА2А [Перельман Б.Л., Шевелев В.И. Отечественные микросхемы и зарубежные аналоги. Справочник, «НТЦ Микротех», 2000 г. - 375 с.: ил., стр.70, 102].

Устройство работает следующим образом.

На передающей стороне (см. фиг.1) в исходном состоянии первый синтезатор 5.1 частот формирует напряжение гетеродина с постоянной частотой для преобразования выходного сигнала ЛЧМ гетеродина 6 на частоту излучения, а также опорный сигнал тактовой частоты fТ для синхронизатора 4 и ЛЧМ гетеродина 6. С выхода синхронизатора 4 на первые входы второго коммутатора 7.2 и ЛЧМ гетеродина 6 поступает непрерывная последовательность испульсов положительной полярности с длительностью, равной длительности ЛЧМ сигнала.

Триггер 67 (фиг.2) находится в следующем состоянии.

Сигнал логического «0» с первого (прямого) выхода триггера 67 поступает:

на вторые входы первого и второго блоков 66.1 и 66.2 «И» для отключения N-2 и N цифровых выходов первого счетчика 61.1 адреса от N-2 и N информационных входов регистра;

на первый вход пятого блока 66.5 «И» для запрета прохождения последовательности синхронизирующих импульсов на первый вход третьего счетчика 61.3 для формирования длительности передаваемого сообщения;

через второй выход ЛЧМ гетеродина 6 на второй вход второго коммутатора 7.2 для запрета прохождения импульсов положительной полярности на управляющий вход первого коммутатора 7.1.

Сигнал логической «1» со второго (инверсного) выхода триггера 67 поступает:

на второй вход третьего блока 66.3 «И» для подключения N-2 выхода первого счетчика 61.1 адреса к N-1 информационному входу регистра 62;

на первый вход четвертого блока 66.4 «И» и разрешает прохождение последовательности синхронизирующих импульсов на первый вход второго счетчика 61.2 для формирования пилот-сигнала.

Сигнал логического «0», поступающий с управляющего входа передающей стороны на четвертый вход ЛЧМ гетеродина 6, запрещает прохождение последовательности импульсов положительной полярности и опорного сигнала тактовой частоты fТ на входы первого и второго триггеров 682.1 и 682.2 (фиг.4).

ЛЧМ гетеродин 6 находится в режиме ожидания. Передающая сторона готова к передаче информационных сигналов.

На приемной стороне (фиг.1) в исходном состоянии второй синтезатор 5.2 частот формирует напряжение гетеродина с постоянной частотой для преобразования принимаемых информационных ЛЧМ сигналов на промежуточную частоту и опорный сигнал тактовой частоты fТ. Опорный сигнал поступает на третий вход блока 21 формирования селектирующих, управляющих импульсов и выделения информационных сигналов (в дальнейшем блока 21) для формирования первого и второго селектирующих импульсов (фиг.3), а также на первый вход блока 10 «И» для формирования импульсов запуска первого селектирующего импульса.

Сигнал логической «1» со второго (инверсного) выхода второго триггера 15.2 поступает на второй вход ключа 19 для разрешения прохождения сжатых информационных сигналов на вход усилителя 9 промежуточной частоты.

Сигнал логического «0» с первого (прямого) выхода второго триггера 15.2, через блок 12 «ИЛИ», поступает на второй вход блока 10 «И» для запрета прохождения опорного сигнала на первый вход делителя 11 частоты.

Сигнал логического «0» с первых (прямых) выходов первого и второго триггеров 213.1 и 213.2 (фиг.3) поступают соответственно на первые входы первого, второго, третьего и четвертого блоков 211.1, 211.2 и 211.3, 211.4 «И» для запрета прохождения как опорного сигнала тактовой частоты fТ на входы первого и второго делителей 212.1 и 212.2 частоты, так и сжатых информационных видеосигналов на 6 и 5 выходы блока 21.

На других выходах блока 21 (фиг.1) формируются сигналы логического «0», которые не изменяют состояния блока 12 «ИЛИ», мультиплексора 20 и делителя 11 частоты. Выход интегратора 14 через первый вход мультиплексора 20 подключен к первому входу второго триггера 15.2.

Приемная сторона готова к приему и обработке информационных сигналов.

Включение передающей стороны на излучение осуществляется по сигналу логической «1», поступающему с первого (управляющего) входа передающей стороны на четвертый вход ЛЧМ гетеродина 6. Сигнал логической «1» с четвертого входа ЛЧМ гетеродина 6 поступает на третий вход блока 68 управления (фиг.4) и разрешает прохождение последовательности импульсов положительной полярности (с первого входа) и опорного сигнала (со второго входа) через первый и третий блоки 681.1 и 681.3 «И» на входы первого и второго триггеров 682.1 и 682.2 блока 68 для формирования:

сигналов синхронизации, определяющих длительность ЛЧМ радиоимпульса на первом выходе ЛЧМ гетеродина 6;

тактовых импульсов с частотой повторения fП1=fТ.

Импульсы положительной полярности с выхода первого триггера 682.1 поступают на второй блок 681.2 «И». На первом выходе второго блока 681.2 «И» формируется сигнал синхронизации с периодом повторения, равным длительности ЛЧМ сигнала. Сигнал синхронизации через второй выход блока 68 поступает на вторые входы первого счетчика 61.1 адреса, четвертого и пятого блоков 66.4 и 66.5 «И», регистра 62 и ПЗУ 63 (фиг.2).

С выхода третьего блока 681.3 «И» опорный сигнал с тактовой частотой fТ поступает на второй вход второго триггера 682.2 и через пятый выход блока 68 на второй вход ЦАП 65.

Сигнал синхронизации со второго выхода второго блока 681.2 «И» поступает на первый вход второго триггера 682.2.

Второй триггер 682.2 (фиг.2) формирует последовательность прямых и инверсных тактовых импульсов с частотой повторения fП2=0,5 fТ, необходимых для обеспечения цифрового синтеза ЛЧМ сигнала с заданной скоростью перестройки частоты, которая поступает:

с первого выхода второго триггера 682.2 на вход третьего триггера 682.3 и через третий выход блока 68 на третий вход ПЗУ 63;

со второго выхода второго триггера 682.2, через четвертый выход блока 68, на четвертый вход ПЗУ 63 и третий вход первого мультиплексора 64.1.

Третий триггер 682.3 формирует последовательность тактовых импульсов с частотой повторения fП3=0,25 fТ, которая через первый выход блока 68 поступает на первый вход первого счетчика 61.1 адреса.

С выхода четвертого блока 66.4 «И» сигнал синхронизации, с периодом повторения, равным длительности ЛЧМ сигнала, поступает на первый вход второго счетчика 61.2. Второй счетчик 61.2 предназначен для формирования длительности пилот-сигнала (6). В состав пилот-сигнал могут входить от одного до нескольких десятков ЛЧМ радиоимпульсов. Их число зависит от номера абонента. Для удобства рассмотрим случай, когда длительность пилот-сигнала равна длительности одного ЛЧМ радиоимпульса (М=1, где М - коэффициент деления второго счетчика 61.2). Тогда на выходе второго счетчика 61.2 через время, равное длительности одного ЛЧМ радиоимпульса, формируется импульс переноса, который изменяет состояние триггера 67 на противоположный и обнуляет содержимое второго счетчика 61.2.

Сигнал логического «0» со второго выхода триггера 67 поступает:

на первый вход четвертого блока 66.4 «И» для запрещения прохождения последовательности синхронизирующих импульсов на первый вход второго счетчика 61.2;

на второй вход третьего блока 66.3 «И» для отключения N-2 выходы первого счетчика 61.1 адреса от N-1 информационного входа регистра 62.

Сигнал логической «1» с первого выхода триггера 67 поступает:

на первые входы первого, второго и четвертого блоков 66.1, 66.2 и 66.4 «И» для подключения N-2, N-1 и N цифровых выходов первого счетчика 61.1 адреса к N-2, N-1 и N информационным входам регистра 62;

через второй выход ЛЧМ гетеродина 6, на второй вход второго коммутатора 7.2, для разрешения прохождения импульсов положительной полярности на управляющий вход первого коммутатора 7.1 для считывания информационного сигнала со второго (информационного) входа передающей стороны (фиг.5).

Информационный сигнал в виде логических «1» и «0» двоичной информации поступает на третий (управляющий) вход второго мультиплексора 64.2 (фиг.2) для модуляции центральной частоты синтезированного ЛЧМ сигнала (см. выражение (1) и (фиг.6), где сплошной линией показан закон перестройки частоты внутри радиоимпульса). Длительность логической «1» («0») равна длительности ЛЧМ радиоимпульса.

Первый счетчик 61.1 адреса начинает вычисление текущих значений адресов кодов амплитуд отсчетов синтезируемого ЛЧМ сигнала. Вычисленные значения кода адреса записываются в регистр 62 и используются для адресации ПЗУ 63. В ПЗУ 63 записаны значения синусоидальных отсчетов Ku(Δt). Разрядность входных слов ПЗУ 63 в общем случае меньше или равна разрядности первого счетчика 61.1 адреса кода амплитуды, Ku(Δt) с выхода ПЗУ 63 поступает на соответствующие входы первого мультиплексора 64.1.

В зависимости от полярности управляющего напряжения на третьем входе первого мультиплексора 64.1 первый или второй выходы ПЗУ 63 подключаются на первый вход ЦАП 65. С помощью ЦАП 65 осуществляется переход к аналоговым значениям ЛЧМ сигнала.

Пилот-сигнал (6) и информационные ЛЧМ сигналы (1) с выхода ЛЧМ гетеродина 6 поступают на вход первого полосового фильтра 1.1. Амплитудно-частотная характеристика первого полосового фильтра 1.1 согласована с шириной спектра информационного ЛЧМ сигнала (11). С выхода первого полосового фильтра 1.1 ЛЧМ сигналы (6) и (1) поступают на первый вход первого смесителя 2.1 для преобразования на частоту излучения. С выхода первого смесителя 2.1 информационные ЛЧМ сигналы через выходной согласующий блок 3 поступают на выход передающей стороны.

На приемной стороне пилот-сигнал со временем запаздывания τ через линейно-согласующий блок 8 поступает на первый вход второго смесителя 2.2. Преобразованный на промежуточную частоту пилот-сигнал поступает на вход второго полосового фильтра 1.2. Второй полосовой фильтр 1.2 аналогичен первому полосовому фильтру 1.1.

ЛЧМ сигнал после прохождения второго полосового фильтра 1.2 поступает на вход дисперсионного фильтра 18 сжатия (фиг.7). Дисперсионная характеристика фильтра 18 сжатия показана на фиг.7 штриховой линией. На выходе дисперсионного фильтра 18 формируется радиоимпульс с длительностью (7).

Сжатый радиоимпульс с выхода дисперсионного фильтра 18 через открытый ключ 19 поступает на вход усилителя 9 промежуточной частоты.

Полоса пропускания ΔFУПЧ усилителя 9 определяется из выражения

С выхода усилителя 9 промежуточной частоты сжатый радиоимпульс пилот-сигнала поступает на вход амплитудного детектора 13.

Видеосигнал с выхода амплитудного детектора 13 (фиг.8, момент времени t1) через последовательно соединенные интегратор 14 и мультиплексор 20 поступает на первый вход второго триггера 15.2 и 20 поступает на первый вход второго триггера 15.2 и изменяет его состояние на противоположное.

Второй триггер 15.2 формирует сигнал логического «0» (бланк), который со второго выхода поступает на второй вход ключа 19 и запрещает прохождение сигналов (шумов) на интервале времени между сжатыми радиоимпульсами на вход усилителя 9 промежуточной частоты.

Сигнал логической «1» с первого выхода второго триггера 15.2 через блок 12 «ИЛИ» (фиг.9, момент времени t1) поступает на второй вход блока 10 «И» и разрешает прохождение опорного сигнала на вход делителя 11 частоты. Через время, равное длительности бланка (8), на выходе делителя 11 частоты появится импульс переноса, который поступает:

на второй вход второго триггера 15.2 для изменения его состояния на исходное;

на второй вход блока 21 сигналов для запуска первых селектирующего (фиг.10, момент времени t1+ТБЛ) и управляющего импульсов.

В блоке 21 (фиг.3) первый и четвертый триггеры 213.1 и 213.4 изменяют свое состояние на противоположное.

На выходе первого триггера 213.1 формируется первый селектирующий импульс с длительностью τ1 СИ (фиг.10), который поступает на первые входы первого и второго блоков 211.1 и 211.2 «И», и разрешает прохождение:

опорного сигнала на вход первого делителя 212.1 частоты;

информационного импульса (логического «0») на шестой выход блока 21 (фиг.12).

На выходе четвертого триггера 213.4 формируется первый управляющий импульс, который поступает на третий вход мультиплексора 20 для подключения третьего выхода блока 21 к первому выходу второго триггера 15.2.

Через время, равное длительности первого селектирующего импульса (τ1 СИ), на выходе первого делителя 212.1 частоты появится импульс переноса, который поступает:

на второй вход первого триггера 213.1 для завершения формирования первого селектирующего импульса;

на первый вход второго триггера 213.2 для формирования второго селектирующего импульса;

на первый вход третьего триггера 213.3 для формирования второго управляющего импульса.

На выходе второго триггера 213.2 формируется второй селектирующий импульс с длительностью τ2 СИ (фиг.11), который поступает на первые входы третьего и четвертого блоков 211.3 и 211.4 «И» для разрешения прохождения:

опорного сигнала на вход второго делителя 212.2 частоты;

информационного импульса (логической «1») на пятый выход блока 21 (фиг.13).

Через время, равное длительности второго селектирующего импульса (τ2 СИ), на выходе второго делителя 212.2 частоты появится импульс переноса, который поступает:

на второй вход второго триггера 213.2 для завершения формирования второго селектирующего импульса;

на второй выход блока 21 для изменения состояния второго триггера 12.2 на противоположное;

на первый вход второго блока 214.2 «ИЛИ».

Импульс переноса с выхода второго блока 214.2 «ИЛИ» поступает на второй вход третьего триггера 213.3 для завершения формирования второго управляющего импульса.

Информационные импульсы с пятого и шестого выходов блока 21 (фиг.13 и 12) раздельно во времени поступают на соответствующие входы первого триггера 15.1.

На выходе первого триггера 15.1 формируется информационный сигнал (фиг.14), который поступает на выход приемной стороны.

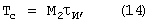

На передающей стороне через время, равное длительности передаваемого сообщения ТС,

где М2 - коэффициент деления третьего счетчика 61.3, формируется импульс переноса, который изменяет состояние триггера 67 на исходное и обнуляет содержимое третьего счетчика 61.3.

На втором выходе триггера 67 появляется сигнал логической «1», который поступает на вход четвертого блока 66.4 «И» и разрешает формирование второго пилот-сигнала. Такой режим работы передающей стороны выбирается из условия обеспечения устойчивого приема информационных сигналов на приемной стороне.

На приемной стороне третий делитель 212.3 частоты осуществляет подсчет принятых информационных знаков (видеоимпульсов на выходах второго и четвертого блоков 211.2 и 211.4 «И»).

Через время, равное длительности принятого сообщения ТПРС,

где ТИ - период повторения видеоимпульсов на выходе первого блока 214.1 «ИЛИ»;

М2 - коэффициент деления, на выходе третьего делителя 212.3 частоты появится видеоимпульс, который поступит:

на четвертый выход блока 21 для обнуления делителя 11 частоты;

на вторые входы четвертого триггера 213.4 и второго блока 214.2 «ИЛИ» для завершения формирования первого и второго управляющих импульсов.

Коэффициенты деления третьего счетчика 61.3 информационных сигналов и третьего делителя 212.3 частоты одинаковы и выбираются из условия обеспечения временной синхронизации. Изменение временной задержки информационных сигналов может быть вызвано как относительным отклонением частоты первого и второго синтезаторов 5.1 и 5.2 частот, так и изменением расстояния между передающей и приемной сторонами.

Приемная часть переходит в режим внешней синхронизации (режим приема второго пилот-сигнала и возможного изменения временного положения первого и второго селектирующих импульсов).

Таким образом, введение в состав устройства для передачи и приема модулированных по фазе и частоте широкополосных сигналов новых блоков и связей обеспечивает уменьшение занимаемой полосы частотного спектра в 2,5 раза, а также сохраняется высокая помехоустойчивость устройства в условиях преднамеренных помех, за счет модуляции центральных частот передаваемых линейных частотно-модулированных радиоимпульсов по информационному закону без смены знака скорости перестройки частоты и длительности модуляции, а также применения на приемной стороне согласованной фильтрации с весовой обработкой информационных ЛЧМ сигналов и управляемой временной селекции сжатых по времени видеоимпульсов для восстановления информационного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ ШИРОКОПОЛОСНЫХ СИГНАЛОВ ДЛЯ ПОДВИЖНЫХ ОБЪЕКТОВ, ОБОРУДОВАННЫХ БЛОКИРАТОРАМИ РАДИОЛИНИЙ УПРАВЛЕНИЯ ВЗРЫВОМ | 2007 |

|

RU2336634C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2005 |

|

RU2288539C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2002 |

|

RU2228576C2 |

| РАДИОЛОКАТОР С ЛИНЕЙНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ ЗОНДИРУЮЩЕГО СИГНАЛА | 1993 |

|

RU2060514C1 |

| СТАНЦИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛИНИЯМ УПРАВЛЕНИЯ ВЗРЫВНЫМИ УСТРОЙСТВАМИ | 2005 |

|

RU2292059C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Анализатор спектра сигналов | 1990 |

|

SU1753616A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ С ЗОНДИРОВАНИЕМ ПРОСТРАНСТВА ФАЗОМАНИПУЛИРОВАННЫМИ СИГНАЛАМИ С ПЕРЕСТРОЙКОЙ ДЛИТЕЛЬНОСТИ ПАРЦИАЛЬНЫХ РАДИОИМПУЛЬСОВ ПО ЛИНЕЙНОМУ ЗАКОНУ | 2009 |

|

RU2405169C2 |

| НЕЛИНЕЙНЫЙ РАДАР ДЛЯ ДИСТАНЦИОННОГО МОНИТОРИНГА ПРОДУКТОПРОВОДОВ | 2007 |

|

RU2343499C1 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКАЯ МОНОИМПУЛЬСНАЯ РЛС | 2011 |

|

RU2497146C2 |

Изобретение относится к области радиосвязи и может быть использовано при разработке широкополосных радиостанций и систем передачи данных с повышенной скрытностью и помехоустойчивостью. Технический результат - уменьшение занимаемой полосы частотного спектра в 2,5 раза и обеспечение высокой помехоустойчивости от преднамеренных помех. В устройстве для уменьшения занимаемой полосы частотного спектра используются модуляции центральных частот, передаваемых линейных частотно-модулированных радиоимпульсов по информационному закону, для чего на приемной стороне введены дисперсионный фильтр сжатия, ключ, мультиплексор и блок формирования селектирующих, управляющих импульсов и выделения информационных сигналов. Кроме того, обеспечена согласованная фильтрация с весовой обработкой информационных ЛЧМ сигналов и временная селекция сжатых по времени видеоимпульсов для восстановления информационного сигнала. 14 ил.

Устройство для передачи и приема модулированных по фазе и частоте сигналов, содержащее на передающей стороне последовательно соединенные первый полосовой фильтр, смеситель и выходной согласующий блок, выход которого является выходом передающей стороны, а также синхронизатор, первый синтезатор частот, линейный частотно-модулированный гетеродин, первый и второй коммутаторы, на приемной стороне - последовательно соединенные линейный согласующий блок, вход которого является входом приемной стороны, второй смеситель и второй полосовой фильтр, усилитель промежуточной частоты, последовательно соединенные блок И и делитель частоты, а также блок ИЛИ, второй синтезатор частот, амплитудный детектор, интегратор и два триггера, при этом выход первого триггера является выходом приемной стороны, отличающееся тем, что на передающей стороне первый вход линейного частотно-модулированного гетеродина соединен с выходом синхронизатора и первым входом второго коммутатора, второй вход линейного частотно-модулированного гетеродина подключен к входу синхронизатора и второму выходу первого синтезатора частот, первый выход которого соединен со вторым входом смесителя, третий вход линейного частотно-модулированного гетеродина соединен с выходом первого коммутатора, первый вход которого подключен к первому входу передающей стороны, являющемуся информационным входом устройства, причем второй вход первого коммутатора соединен с выходом второго коммутатора, а четвертый вход линейного частотно-модулированного гетеродина подключен ко второму входу передающей стороны, являющемуся управляющим входом устройства, первый выход линейного частотно-модулированного гетеродина соединен с входом первого полосового фильтра, а второй выход линейного частотно-модулированного гетеродина подключен ко второму входу второго коммутатора, при этом синхронизатор выполнен в виде последовательно соединенных формирователя импульсов, вход которого подключен к входу синхронизатора и инвертора, выход которого соединен с выходом синхронизатора, на приемной стороне введены дисперсионный фильтр сжатия, ключ, мультиплексор и блок формирования селектирующих, управляющих импульсов и выделения информационных сигналов, при этом выход второго полосового фильтра через дисперсионный фильтр сжатия подключен к информационному входу ключа, выход которого через последовательно соединенные усилитель промежуточной частоты и амплитудный детектор подключен к интегратору, выход которого соединен с первыми входами блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов и мультиплексора, выход которого подключен к первому входу второго триггера, первый и второй выходы которого соединены соответственно с первым входом блока ИЛИ и вторым (управляющим) входом ключа, причем второй вход блока ИЛИ подключен к первому выходу блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов, второй вход которого соединен со вторым входом второго триггера и выходом делителя частоты, второй вход которого подключен к четвертому выходу блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов, второй и третий выходы которого соединены соответственно со вторым и третьим входами мультиплексора, а первый и второй входы первого триггера подключены соответственно к пятому и шестому выходам блока формирования селектирующих, управляющих импульсов и выделения информационных сигналов, третий вход которого соединен со вторым выходом второго синтезатора частот и первым входом блока И, второй вход которого подключен к выходу блока ИЛИ, а первый выход второго синтезатора частот соединен со вторым входом второго смесителя.

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2002 |

|

RU2228576C2 |

| Устройство для передачи и приема модулированных по фазе и частоте сигналов | 1977 |

|

SU684750A1 |

| Устройство для приема сигналов с комбинированной частотной и фазовой манипуляцией | 1986 |

|

SU1363523A1 |

| US 5374903, А, 20.12.1994 | |||

| US 4546328, А, 08.10.1985. | |||

Авторы

Даты

2005-10-20—Публикация

2004-06-09—Подача