Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к технологии оптической передачи данных, в частности к способу и схеме синхронного приема данных, передаваемых по оптической системе передачи данных от абонента на центральный узел в высокоскоростном пакетном режиме.

Уровень техники

Для решения проблемы синхронизации при передаче данных от абонента на центральный узел в случае использования пассивной оптической сети с асинхронным режимом передачи (АРП (АТМ) (А-ПОС (A-PON)), при использовании технологии высокоскоростного множественного доступа с временным разделением каналов (МДВР (TDMA)), необходимо использовать специальную технологию и способ. Например, работа каждой ячейки, из которой осуществляют доступ к терминалу оптической линии (ТОЛ (OLT)) в асинхронном режиме передачи (АРП), должна быть приблизительно синхронизирована с ее диапазоном, но даже в этом случае существует некоторый, не равный целому числу бит интервал между ячейками, работающими в АРП. В этом случае для совмещения данных необходимо использовать синхронизацию битов и одновременно осуществлять синхронизацию байтов данных и ячеек. В настоящем изобретении эту проблему называют проблемой приема для высокоскоростной синхронизации битов. В качестве другого примера можно отметить, что поскольку данные, передаваемые из ячеек, работающих в АРП, от абонента на центральный узел, поступают через различные удаленные терминалы, и их передача производится в пакетном режиме, необходимо обеспечить индивидуальную синхронизацию для каждой ячейки.

Во время указанного выше синхронного приема для обеспечения максимальной устойчивости по времени тактовую частоту выборки на конце приема ТОЛ устанавливают по середине наблюдаемой структуры входных данных. При этом обычно используют способ индивидуальной установки, основанный на схеме фазовой синхронизации (СФС (PLL)). При использовании такой технологии вначале с помощью фазового детектора определяют фазы передних и задних фронтов импульсов последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, и тактовую частоту выборки для генерирования "восходящего" и "нисходящего" импульсов; затем эти два импульса передают в "насос загрузки", и затем выходное напряжение насоса загрузки используют для изменения частоты генератора, управляемого напряжением (ГУН (VCO)), для получения тактовой частоты с соответствующей фазой.

Недостаток технологии СФС состоит в следующем. Во-первых, при использовании технологии СФС необходимо длительное время для разъединения, чтобы обеспечить стабильную синхронизацию по фазе, что не совместимо с характеристиками высокоскоростной передачи данных, передаваемых в пакетном режиме от абонента на центральный узел в системе А-ПОС. Во-вторых, трудно построить схему детектирования фазы для обеспечения детектирования фазы данных, передаваемых от абонента на центральный узел, в режиме высокоскоростной пакетной передачи, и тактовой частоты выборки. В-третьих, трудно получить небольшое значение статической погрешности фазы и динамической ошибки определения фазы между тактовой частотой выборки и последовательно поступающими данными, передаваемыми в высокоскоростном пакетном режиме от абонента на центральный узел; например, это касается времени задержки, времени синхронной задержки и нелинейных характеристик фазового детектора, так как в нем для обеспечения стабильности требуется обеспечить малую полосу пропускания петли обратной связи, но в этом случае схема не позволяет отслеживать высокочастотные шумы.

Другой способ позиционирования, который используют более часто, состоит в использовании выборки с избыточностью, когда тактовая частота имеет четыре фазы для данных, передаваемых по каналу от абонента на центральный узел, в режиме высокоскоростной последовательной пакетной передачи. На дальнем конце в передаваемую головную часть данных, передаваемых в режиме высокоскоростной последовательной пакетной передачи от абонента на центральный узел, ячейки, работающей в АРП, добавляют специальный заголовок (преамбулу); при этом на конце автоматического коммутатора каналов, если при использовании некоторой тактовой частоты получают выборку правильного кода заголовка, считается, что фаза тактовой частоты удовлетворяет требованиям по фазе, и эту тактовую частоту выбирают в качестве синхронной тактовой частоты, и затем выполняют выборку битовых данных, преобразование данных в байтовую форму и реверсирование ячейки, и т.д.

Недостаток этого способа состоит в следующем. Во-первых, выбранная тактовая частота не всегда устанавливается в середине наблюдаемой структуры данных, так что допуски по времени могут быть очень незначительными. Во-вторых, при высокой скорости передачи данных трудно удовлетворить требования, предъявляемые к системе. В-третьих, трудно обеспечить точное отслеживание фазового шума системы.

Сущность изобретения

Настоящее изобретение направлено на способ и схему синхронного приема высокоскоростных данных, передаваемых от абонента на центральный узел, предназначенные для решения проблем, указанных выше, с использованием простого устройства и выполнения.

Цель настоящего изобретения достигается с использованием следующего технического решения: способ синхронного приема при высокоскоростной передаче данных от абонента на центральный узел в системе оптической передачи данных, при котором используют многофазную тактовую частоту с различными фазами для синхронного приема высокоскоростных битов, при этом способ содержит:

А. использование тактовой частоты с Х различными фазами для обеспечения выборки с избыточностью высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, для получения данных, передаваемых по Х каналам, адаптацию данных, передаваемых по Х каналам, к локальной тактовой частоте, где Х представляет собой целое положительное число;

В. детектирование кодов заголовков данных, передаваемых по Х каналам, адаптированных к локальной тактовой частоте, определение корректно принятых данных;

С. выбор корректных данных, выборка которых была проведена с использованием тактовой частоты, установленной в середине наблюдаемой структуры корректных данных, выполнение последовательно-параллельного преобразования, а также синхронизацию байтов и ячейки для выбранных корректных данных.

Указанные тактовые частоты с Х различными фазами представляют собой тактовые частоты с 8 или 16 различными фазами, и разность фаз для каждых двух последующих тактовых частот равна 1/Х периода тактовой частоты.

Этап А дополнительно содержит: генерирование с помощью генератора тактовой частоты Х тактовых частот с равной разностью фаз; выполнение с помощью Х схем выборки, соответствующих указанной Х-фазной тактовой частоте, выборки с избыточностью высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, и получение данных, передаваемых по Х каналам; выполнение с помощью Х адаптирующих каскадов, соответствующих Х схемам выборки, адаптации указанных данных, передаваемых по Х каналам, к локальной тактовой частоте; выполнение сдвига и синхронизации указанных адаптированных данных, передаваемых по Х каналам, с помощью Х каскадов сдвига, соответствующих Х адаптирующим каскадам.

Каждая из указанных Х схем выборки включает трехкаскадные регистры, соединенные последовательно, которые производят сдвиг данных с указанной Х-фазной тактовой частотой, для устранения нестабильности принимаемого сигнала.

Адаптацию данных, передаваемых по Х каналам, к указанной локальной тактовой частоте выполняют с помощью соответствующих Х адаптирующих каскадов; адаптацию выполняют следующим образом: выходные данные регистра, управляемого с помощью тактовой частоты, передают в качестве входных данных в регистр, управляемый другой тактовой частотой и, в конце концов, передают в регистр, управляемый указанной локальной тактовой частотой.

Сдвиг указанных адаптированных данных, выполняемый с помощью указанных каскадов сдвига, по указанной локальной тактовой частоте, выполняют с помощью последовательно соединенных регистров, содержащих 8+1 каскадов.

Этап В дополнительно содержит: сравнение указанных адаптированных данных с кодами заголовков и определение данных с кодом заголовка, детектированным в качестве корректных данных; выполнение детектирования полярности и измерение переднего фронта и заднего фронта указанных корректных данных для замены данных, передаваемых по этому каналу.

Во время выполнения сравнения адаптированных данных, содержащих коды заголовков, в случае, когда все биты адаптированных данных идентичны коду заголовка, или только один из битов не идентичен коду заголовка, принимают решение, что код заголовка был детектирован, и данные с этим кодом заголовка представляют собой корректные данные.

Указанное детектирование полярности дополнительно включает: сравнение бит за битом корректных данных, содержащих указанный код заголовка, для установки исходных векторов индексов hit1-hit8, и в случае, когда биты различаются, соответствующий индекс (hit) устанавливают равным "0", а когда они идентичны, соответствующий индекс устанавливают равным "1"; выполнение операции исключающее ИЛИ для двух последовательных индексов и помещение результата в флаг - Flag; при этом биты младшей значащей "1" и старшей значащей "1" представляют, соответственно, передний фронт и задний фронт указанных корректных данных.

Этап С дополнительно включает: определение указанного положения "а" бита младшей значащей " 1" и положения "b" бита старшей значащей "1" в указанном флаге с помощью логической схемы выбора и выбор корректных данных, выборка которых была проведена на тактовой частоте с номером (а+b)/2 фазы, для выполнения последовательно-параллельного преобразования и синхронизации ячейки.

Этот этап дополнительно включает деление указанной локальной тактовой частоты для получения тактовой частоты восстановления, используемой для последовательно-параллельного преобразования, причем указанную тактовую частоту восстановления также передают через указанную схему синхронного приема вместе с синхронизированными передаваемыми данными байта и ячейки.

Цель настоящего изобретения также может быть достигнута благодаря использованию схемы: она отличается тем, что схема синхронного приема при высокоскоростной передаче данных от абонента на центральный узел в системе оптической передачи данных, включающей:

блок схемы генерирования тактовой частоты, предназначенный для получения X-фазной тактовой частоты, блок схемы выборки, предназначенный для высокоскоростной последовательной передачи данных в пакетном режиме от абонента на центральный узел по Х каналам, блок схемы детектирования кодов заголовков, предназначенный для детектирования кодов заголовков данных, передаваемых по Х каналам, блок логической схемы выбора и блок синхронизации байта и ячейки, который состоит из блока схемы выбора данных, передаваемых по Х каналам, блока схемы выбора синхронного сигнала и блока схемы последовательно-параллельного преобразования;

указанная Х-фазная тактовая частота с различными фазами, генерируемая с помощью указанного блока генерирования тактовой частоты, поступает в указанный блок схемы выборки данных, передаваемых по Х каналам, соответственно;

и указанный блок схемы выборки соединен с указанным блоком схемы детектирования кода заголовка данных, передаваемых по Х каналам, и указанным блоком схемы выбора данных, передаваемых по Х каналам, указанного блока синхронизации байта и ячейки, соответственно;

указанный блок схемы детектирования кода заголовка соединен с указанным блоком логической схемы выбора и с указанным блоком выбора синхронного сигнала, указанного блока синхронизации байта и ячейки, соответственно;

указанный блок логической схемы выбора соединен с указанным блоком схемы выбора синхронного сигнала и блоком схемы выбора данных, передаваемых по Х каналам, указанного блока синхронизации байта и ячейки, соответственно;

указанный блок схемы выбора синхронного сигнала и указанный блок схемы выбора данных, передаваемых по Х каналам, указанного блока синхронизации байта и ячейки соединены с указанным блоком последовательно-параллельного преобразования, соответственно;

указанная локальная тактовая частота поступает в указанный блок схемы выборки и в указанный блок детектирования кода заголовка данных, передаваемых по Х каналам, соответственно.

Устройство также содержит схему деления указанной локальной тактовой частоты, которая непосредственно генерирует тактовую частоту восстановления, используемую для последовательно-параллельного преобразования, и указанная тактовая частота восстановления поступает на выход указанной схемы синхронного приема вместе с данными синхронизированного байта и данными ячейки.

Каждый указанный выше канал схемы выборки состоит из последовательно включенных каскадов выборки, которые используются для устранения подстабильных состояний адаптирующего каскада, который выполняет адаптацию указанных данных выборки с указанной локальной тактовой частотой, и каскада сдвига, который осуществляет синхронизацию данных.

Указанный блок логических схем выбора включает соединенные генератор временной последовательности, регистр первого флага, регистр второго флага, первую схему декодирования, вторую схему декодирования, первый регистр, второй регистр, сумматор и селектор;

указанный последовательный генератор соединен с первым регистром флага, вторым регистром флага, первым регистром, вторым регистром и указанным селектором, соответственно;

указанный первый регистр флага, первая схема декодирования и первый регистр соединены последовательно и затем соединены с одним из входов указанного сумматора;

указанный второй регистр флага, вторая схема декодирования и второй регистр соединены последовательно и затем подключены к другому входу указанного сумматора;

выход указанного сумматора соединен с указанным селектором; и в первый регистр флага, второй регистр флага, первый регистр и второй регистр поступает локальная тактовая частота.

Указанный блок генерирования тактовой частоты с Х фазами выполнен по схеме фазовой синхронизации (СФС) или по схеме цифровой синхронизации (СЦС (DLL)).

Способ и схема синхронного приема, в соответствии с настоящим изобретением, при высокоскоростной передаче данных от абонента на центральный узел в системе оптической передачи данных предложены для решения недостатков существующего технического решения, и представляют собой способ и схему приема с высокоскоростной битовой синхронизацией. Способ содержит следующие этапы: вначале выполняют выборку с избыточностью высокоскоростных данных, передаваемых в пакетном режиме от абонента на центральный узел, с помощью многофазной тактовой частоты (содержащей, например, 8-16 фаз) и адаптацию данных, для которых была проведена выборка с избыточностью, к локальной тактовой частоте, затем производят детектирование кода заголовка (например, в виде кода Бэйкера (baker code)), на основании результата детектирования затем выбирают данные, выборка которых была проведена с использованием тактовой частоты, установленной в середине наблюдаемой структуры данных, в качестве корректных данных для выполнения последовательно-параллельного преобразования, синхронизации байта и ячейки.

Способ и схема синхронного приема, в соответствии с настоящим изобретением, при высокоскоростной передаче данных от абонента на центральный узел в системе оптической передачи данных, представляют собой способ и схему приема с высокоскоростной битовой синхронизацией. В этом способе используют многофазную тактовую частоту для выполнения выборки с избыточностью данных и адаптации данных, для которых была проведена выборка, к локальной тактовой частоте. В способе используют схему детектирования полярности для упрощения последующих схем, и используют логическую схему выбора для выбора данных, выборка которых была проведена с использованием тактовой частоты, установленной в середине наблюдаемой структуры. В способе используют добавление кода Бэйкера в качестве кода заголовка для высокоскоростной последовательной пакетной передачи данных от абонента на центральный узел. Настоящее изобретение направлено на выбор данных, а не на выбор тактовой частоты, и в нем используют высокую тактовую частоту с делением частоты для использования ее в качестве тактовой частоты байтов.

Сравнение со способом выборки по четырехфазной тактовой частоте для выполнения выборки с избыточностью при пакетной передаче данных от абонента на центральный узел, способ и схема в соответствии с настоящим изобретением, имеют следующие преимущества: использование большего количества различных фаз тактовой частоты позволяет обеспечить выборку с избыточностью, так, что обеспечивается большая степень детализации выборки, и это позволяет эффективно отслеживать фазовую ошибку системы; это позволяет надежно и точно выбирать тактовую частоту в середине наблюдаемой структуры принимаемых данных, так что в схеме обеспечивается максимальный допуск по времени; в схеме используют режим магистральной передачи данных без обратной связи, благодаря чему расчетная скорость передачи данных в схеме может быть существенно увеличена при удовлетворении условий битовой синхронизации при высокоскоростной передаче данных; схема выполняет обработку после синхронизации принятых данных с локальной тактовой частотой, так что схема может быть выполнена более просто, и в ней отсутствует неустойчивость фазы, в ней не требуется использовать регистры FIFO (регистры для организации очереди типа "первым пришел - первым обслуживается"), в ней легко осуществляется последовательное синхронное управление; схема позволяет непосредственно генерировать высокоскоростную тактовую частоту с делением частоты, так, что в ней отсутствуют шумы переключения тактовой частоты.

Краткое описание чертежей

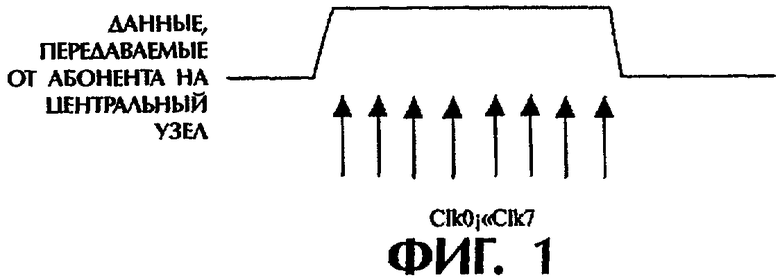

На фигуре 1 представлен принцип проведения выборки данных, передаваемых от абонента на центральный узел при использовании восьмифазной тактовой частоты.

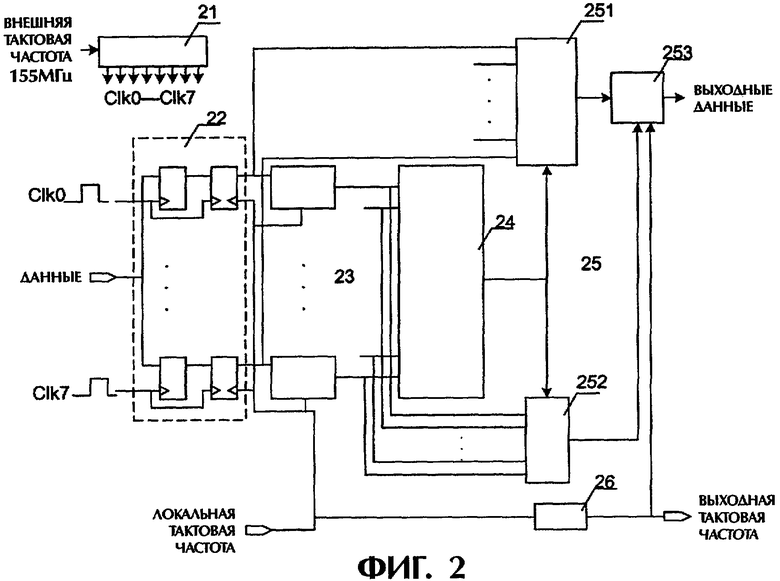

На фигуре 2 показана схема приема при использовании восьмифазной тактовой частоты для обеспечения высокоскоростной битовой синхронизации.

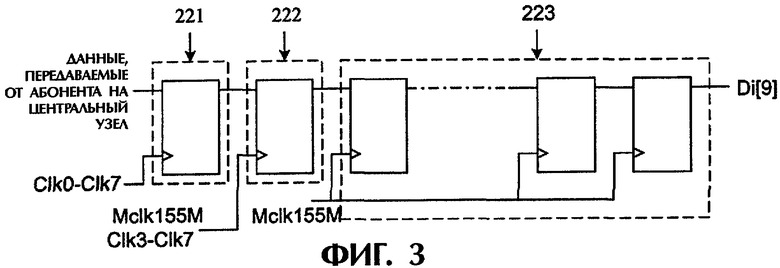

На фигуре 3 показана схема одной фазы схемы выборки блока выборки данных, передаваемых от абонента на центральный узел, по фиг.2.

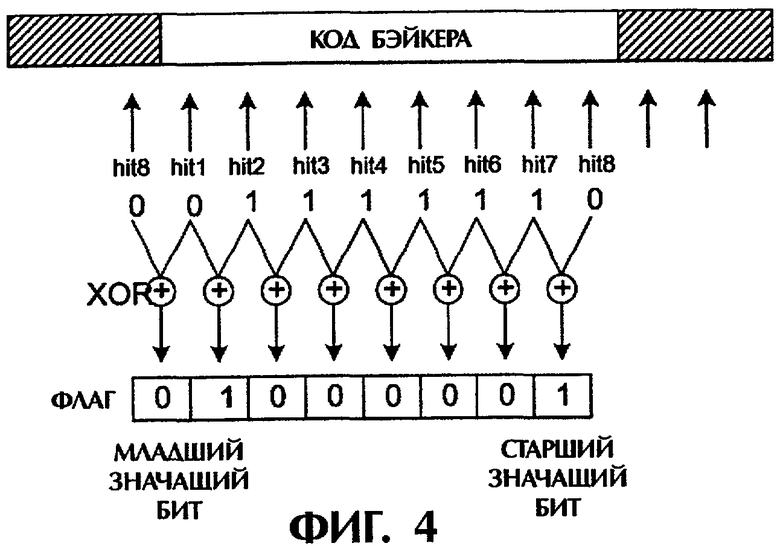

На фигуре 4 представлена схема детектирования полярности для блока схемы детектирования кода заголовка (кода Бэйкера) по фиг.2.

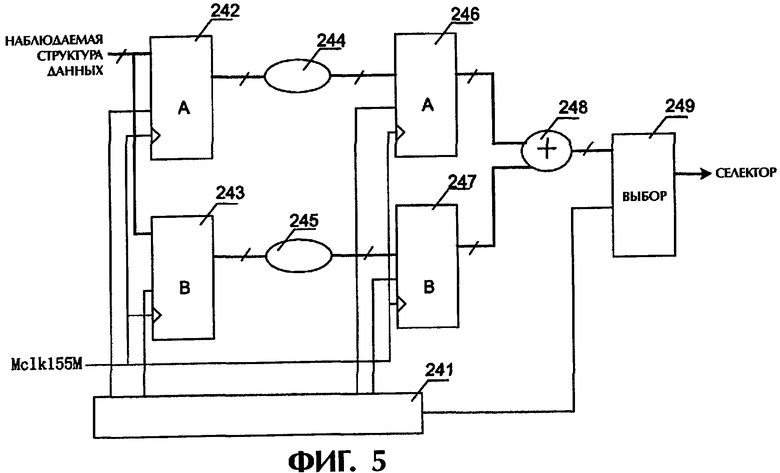

На фигуре 5 изображена схема логической схемы выбора.

Осуществление изобретения

Настоящее изобретение будет более подробно описано ниже со ссылкой на чертежи, на которых

на фигуре 1 представлен принцип выполнения выборки при высокоскоростной последовательной пакетной передаче данных от абонента на центральный узел при использовании восьмифазных тактовых частот, имеющих различные фазы. С использованием восьмифазных тактовых частот (Clk0-Clk7) с различными фазами выполняют выборку с избыточностью высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел; если при использовании всех восьмифазных тактовых частот Clk0-Clk7 были получены корректные данные выборки, в качестве принятых данных обычно используют данные, выборка которых была проведена с помощью тактовых частот Clk3 или Clk4, которые находятся в середине наблюдаемой структуры высокоскоростных последовательных данных, передаваемых в пакетном режиме, от абонента на центральный узел.

На фигуре 2 представлен основной принцип работы способа и принципиальная структура схемы. Она включает: блок 21 генерирования многофазной (восьмифазной) тактовой частоты, блок 22 схемы выборки высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, блок 23 схемы детектирования кода Бэйкера (одного из кодов заголовка), блок 24 логической схемы выбора и блок 25 синхронизации байта ячейки, которые соединены с блоком 251 схемы выбора многоканальных (с восьмиканальных данных), блок 252 схемы выбора синхронного сигнала, и последовательно-параллельный преобразователь 253. Кроме того, схема содержит схему 26 деления тактовой частоты, коэффициент деления которой зависит от количества параллельных битов последовательно-параллельного преобразователя 253.

Блок 21 схемы генерирования многофазной тактовой частоты генерирует тактовые частоты, количество которых равно требуемому количеству фаз, и частота которых равна скорости передачи битов данных, передаваемых от абонента на центральный узел, и которые имеют равные разности фаз. Например, при скорости передачи высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, равной 155 Мбит/с, и при внешней тактовой частоте, равной 155 МГц, генерируются восьмифазные тактовые частоты с частотой 155 МГц, и с равной разностью фаз, при этом период тактовой частоты равен 6,4 нс, и разность фаз между каждыми двумя последовательными тактовыми частотами составляет 1/8 внешнего периода тактовой частоты, то есть, 0,8 нс. Схема 21 многофазной тактовой частоты может быть построена с использованием обычного принципа фазовой синхронизации (СФС) или цифровой синхронизации (СЦС). Восемь тактовых частот Clk0-Clk7 поступают на схему 22 выборки высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента, на центральный узел.

Блок 22 схемы выборки высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, состоит из с восьмиканальной схемы выборки, в которой восьмифазная тактовая частота Clk0-Clk7 используется для выполнения выборки с избыточностью высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, для получения последовательных данных, передаваемых по восьми каналам, затем полученные данные адаптируют к локальной тактовой частоте, равной 155 МГц, с помощью преобразователя для последующей обработки.

На фигуре 3 показан один канал (одна фаза) схемы 22 выборки, которая содержит три каскада, показанные тремя блоками, представленными пунктирными линиями.

Первый каскад представляет собой каскад 221 выборки, который выполняет выборку с избыточностью в режиме сдвига высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, одной из восьми фазных тактовых частот Clk0-Clk7, и получает данные, соответствующие используемой тактовой частоте. Первый каскад может быть выполнен в виде трех последовательно соединенных каскадов регистров, что необходимо для устранения подстабильного состояния и нестабильности принимаемого сигнала.

Второй каскад представляет собой адаптирующий каскад 222, который используют для адаптации выбранных данных с избыточностью по отношению к основной тактовой частоте или к указанной локальной тактовой частоте (Mclk155 МГц) через частоты Clk3, Clk4, Clk5, Clk6 и Clk7 или непосредственно.

Адаптацию к основной тактовой частоте выполняют с использованием следующих взаимозависимостей, в которых выходные данные регистра, управляемые с помощью тактовой частоты, находящейся слева от стрелки →, передают на вход данных регистра, управляемого тактовой частотой, находящейся справа от стрелки.

Clk0→Clk4→Mclk155M→Mclk155M;

Clk1→Clk5→Mclk155M→Mclk155M;

Clk2→Clk6→Clk3→Mclk155M;

Clk3→Clk7→Clk4→Mclk155M;

Clk4→Mclk155M→Mclk155M;

Clk5→Mclk155M→Mclk155M;

Clk6→Clk3→Mclk155M;

Clk7→Clk4→Mclk155M.

Из вышеприведенных взаимозависимостей можно видеть, что данные, синхронизированные с использованием восьмифазной тактовой частоты, в конце концов, получаются адаптированными к основной тактовой частоте или к локальной тактовой частоте (Mclk155 МГц).

Третий каскад представляет собой каскад 223 сдвига, который используется для синхронизации выходных данных адаптирующих каскадов 222. Выходные данные каждого канала были адаптированы к основной тактовой частоте, соответственно, и каждая из них с различной фазой тактовой частоты. Каскад 223 сдвига и регистр сдвига состоят из девяти включенных последовательно каскадных регистров. Восемь каскадов 223 сдвига передают 8 младших значащих битов последовательных данных в блок 23 схемы детектирования кода заголовка (кода Бэйкера), соответственно, и затем передают старший значащий бит (MSB) в блок 251 схемы выбора данных, соответственно, для выбора данных, как показано на фиг.2.

Схема 23 детектирования кода заголовка (кода Бэйкера) также включает восемь схем детектирования кода Бэйкера, которые выполняют, соответственно, детектирование кода заголовка для 8 младших значащих битов последовательных данных, поступающих на выход восьми каскадов 223 сдвига, для определения наличия корректных данных в восьми каналах. Каждая схема детектирования кода Бэйкера состоит из схем сравнения кодов Бэйкера и схемы детектирования полярности.

На фигуре 4 представлен принцип работы схемы детектирования кода Бэйкера. Схема сравнения кода Бэйкера выполняет сравнение поступающих данных с кодом Бэйкера "11100101". На фиг.4 стрелки под не заштрихованной областью показывают результат процедуры сравнения; когда бит данных идентичен соответствующему биту кода Бэйкера, индекс исходного вектора устанавливают в "1", в противном случае в "0". Как показано на фиг.4, индексы hit1 и hit8 равны "0", и все индексы hit2-hit7 равны "1" (шесть "1"). В ходе сравнения, когда все биты равны, или только один бит не равен коду Бэйкера, определяется, что код Бэйкера был детектирован. Сравнение продолжается непрерывно по индексам hit8, hit1, hit2...hit7, hit8... и так далее.

Схему детектирования полярности используют для детектирования переднего фронта и заднего фронта высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, и результат, который используют для замены данных выборки, передают в последующие схемы для дальнейшей обработки; таким образом, уменьшается объем вычислений, и упрощается дальнейшая обработка; поэтому вся схема позволяет выполнять обработку данных, передаваемых по восьми каналам, при тактовой частоте 155 МГц. В устройстве используют восемь логических элементов исключающее ИЛИ, которые выполняют логическую операцию исключающее ИЛИ для двух последовательных результатов сравнения кода Бэйкера. На фиг.4 - результат сравнения "01000001" последовательно записывают в восьмибитовый флаг, который в данном примере содержит "0" в младшем значащем бите и "1" в старшем значащем бите.

Как показано на фиг.4, данные флага содержат только два бита, равных "1", которые заменяют шесть битов, равных "1", исходного вектора индексов, и это упрощает последующие схемы.

Логическая схема 24 выбора выполняет обработку наблюдаемой структуры данных размером 8×8 битов, поступающих со схемы 23 детектирования кода Бэйкера, для определения какая из фазных тактовых частот восьмифазных тактовых частот расположена в середине наблюдаемой структуры данных.

Как показано на фиг.5, логическая схема 24 выбора содержит генератор 241 временной последовательности, флаг А (первый флаг) 242, состоящий из логических схем регистра, флаг В (второй флаг) 243, состоящий из логических схем регистра, логическую схему А 244 декодирования (первая логическая схема декодирования), логическую схему В 245 декодирования В (вторая схема декодирования), регистр А (первый регистр) 246, регистр В (второй регистр) 247, сумматор 248 (+), и селектор (SEL) 249, состоящий из логических схем регистра. Блок 24 логической схемы выбора определяет положение "а" первой "1" в флаге и положение "b" второй "1" в флаге для вычисления номера (а+b)/2 фазы частоты, которая расположена в середине наблюдаемой структуры корректных данных, с помощью сумматора 248 и селектора 249. Как показано на фиг.4, положение "а" первой "1" в флаге равно 2, и положение "b" второй "1" равно 8, так что (2+8)/2=5, и частота Clk5 будет расположена в середине наблюдаемой структуры корректных данных.

Логическая схема выбора, в основном, предназначена для решения проблемы, возникающей, в случае большого значения разности фаз тактовой частоты, когда код Бэйкера пересекает границу основного периода тактовой частоты. При разработке схемы необходимо учитывать, что скорость декодирования влияет на синхронизацию последовательных байтов.

Блок 25 синхронизации байта и ячейки состоит из схемы 261 выбора данных, схемы 252 выбора синхронного сигнала и последовательно-параллельного преобразователя 253. Блок 25 синхронизации байта и ячейки используют для выбора, синхронизации и последовательно-параллельного преобразования данных, передаваемых по восьми каналам, для выполнения синхронизации байта и ячейки. Под управлением логической схемы 24 выбора схема 251 выбора данных производит выбор одного из старших значащих битов (MSB) передаваемых данных, соответственно, с помощью восьми каскадов 223 сдвига схемы 22 выборки данных. Под управлением логической схемы 24 выбора, схема 252 выбора синхронного сигнала выбирает данные, передаваемые по одному из восьми каналам, с помощью схемы 23 выбора кода Бэйкера и синхронно подает их на выход. Под управлением схемы 26 деления тактовой частоты и схемы 251 выбора данных, последовательно-параллельный преобразователь 253 преобразует восьмибитовые последовательные данные одного из каналов, поступающих с выхода схемы 252 выбора синхронного сигнала, в параллельные данные для выполнения синхронизации ячейки; одновременно с этим схема 26 деления тактовой частоты подает на выход тактовую частоту байта. Схема 26 деления тактовой частоты генерирует тактовую частоту восстановления принимаемых данных с использованием локальной тактовой частоты и подает ее на выход вместе с синхронизированными данными байта и ячейки. Более подробное описание схемы воплощения устройства не приведено в настоящем описании, поскольку оно хорошо известно в данной области техники.

Способ и схема, в соответствии с настоящим изобретением, прошли проверку работы на практике. Было доказано, что их можно надежно использовать при скорости передачи данных до 155 Мбит/с; при этом динамический диапазон составляет приблизительно 30 дБ, и частота возникновения ошибки меньше, чем 1×10-12, что удовлетворяет требованиям стандарта G.983.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕРФЕЙС ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2369033C2 |

| ИНТЕРФЕЙС С ВЫСОКОЙ СКОРОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2371872C2 |

| ИНТЕРФЕЙС ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧИ ДАННЫХ С УЛУЧШЕННЫМ УПРАВЛЕНИЕМ СОЕДИНЕНИЕМ | 2004 |

|

RU2341906C2 |

| УСТРОЙСТВО И СПОСОБ ДЛЯ РЕАЛИЗАЦИИ ИНТЕРФЕЙСА С ВЫСОКОЙ СКОРОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2337497C2 |

| УСТРОЙСТВО И СПОСОБ ИНТЕРФЕЙСА С ВЫСОКОЙ СКОРОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2355121C2 |

| ИНТЕРФЕЙС С ВЫСОКОЙ СКОРОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2331160C2 |

| УСТРОЙСТВО И СПОСОБ РЕАЛИЗАЦИИ ИНТЕРФЕЙСА ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2353066C2 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ, УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ, УСТРОЙСТВО ЗАПИСИ ДАННЫХ И СПОСОБ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2276812C2 |

| УСТРОЙСТВО ДЕТЕКТИРОВАНИЯ КАНАЛОВ ВИДЕОКОНФЕРЕНЦСВЯЗИ В СИСТЕМАХ ПЕРЕДАЧИ С ВРЕМЕННЫМ УПЛОТНЕНИЕМ | 2013 |

|

RU2539967C1 |

| СПОСОБ И СИСТЕМА ДЛЯ ПРЕДОСТАВЛЕНИЯ ВЫСОКОСКОРОСТНОГО ОБСЛУЖИВАНИЯ ПРИ ПОМОЩИ МНОГОАБОНЕНТСКОЙ СЕТИ ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2357373C2 |

Изобретение относится к области оптической связи. Технический результат заключается в точном отслеживании фазового шума и в более точном установлении тактовой частоты. Сущность изобретения заключается в том, что способ включает этапы генерирования тактовых частот с Х различными фазами, передачи в пакетном режиме от абонента на центральный узел высокоскоростных данных, получения данных, переданных по Х каналам, адаптированных к локальной тактовой частоте, детектирования кодов заголовков упомянутых данных, определения принятых корректных данных, выбора корректных данных, прошедших выборку с использованием тактовой частоты, установленной в середине наблюдаемой структуры и выполнения последовательно-параллельного преобразования, синхронизации бита и ячейки. 2 н. и 14 з.п. ф-лы, 5 ил.

А. соответственно, проведение выборки с избыточностью высокоскоростных последовательных данных, передаваемых в пакетном режиме от абонента на центральный узел, с использованием Х-фазной тактовой частоты для получения данных, передаваемых по Х каналам, и адаптацию данных, передаваемых по Х каналам, к локальной тактовой частоте, где Х представляет собой целое положительное число;

В. детектирование кодов заголовков данных, передаваемых по Х каналам, адаптированных к указанной локальной тактовой частоте, для определения корректных данных;

С. выбор корректных данных, выборка которых была проведена с использованием тактовой частоты, установленной в середине наблюдаемой структуры указанных корректных данных, выполнение последовательно-параллельного преобразования, синхронизацию байта и ячейки для выбранных корректных данных;

причем этап В содержит соответствующее сравнение данных, передаваемых по Х каналам, адаптированных к локальной тактовой частоте, с кодами заголовков и определение адаптированных данных с кодом заголовка, детектированным в качестве корректных данных, проверку переднего фронта и заднего фронта корректных данных, и

этап С содержит определение позиций переднего фронта и заднего фронта и выбор корректных данных, отобранных на тактовой частоте на середине определенных позиций, для последовательно-параллельного преобразования, синхронизации байта и ячейки.

Х-фазная тактовая частота с различными фазами, генерируемая с помощью блока схемы генерирования тактовой частоты, поступает в блок схемы выборки данных, передаваемых по Х каналам, соответственно;

выходы указанного блока схемы выборки данных, передаваемых по Х каналам, соответственно соединены со входами блока схемы детектирования кода заголовка данных, передаваемых по Х каналам, и со входами указанного блока схемы выбора данных указанного блока синхронизации байта и ячейки, соответственно;

выходы указанного блока схемы детектирования кода заголовка данных, передаваемых по Х каналам, соединены со входами указанного блока логической схемы выбора и со входами указанного блока схемы выбора синхронного сигнала указанного блока синхронизации байта и ячейки, соответственно;

выход указанного блока логической схемы выбора соединен с управляющим выводом указанного блока схемы выбора синхронного сигнала и управляющим выводом блока схемы выбора данных указанного блока синхронизации байта и ячейки, соответственно;

выход указанного блока схемы выбора синхронного сигнала соединен со входом указанного блока последовательно-параллельного преобразования, выход указанного блока схемы выбора данных указанного блока синхронизации байта и ячейки соединен с управляющим выводом указанного блока схемы последовательно-параллельного преобразования;

локальная тактовая частота поступает в указанный блок схемы выборки данных, поступающих по Х каналам, и в указанный блок схемы детектирования кода заголовка данных, поступающих по Х каналам, соответственно.

указанный генератор временной последовательности соединен с первым регистром флага, вторым регистром флага, первым регистром, вторым регистром и указанным селектором, соответственно;

указанный первый регистр флага, первая схема декодирования и первый регистр соединены последовательно и затем соединены с одним из входов указанного сумматора; причем указанный второй регистр флага, вторая схема декодирования и второй регистр соединены последовательно и затем подключены к другому входу указанного сумматора;

выход указанного сумматора соединен с указанным селектором, и локальная тактовая частота поступает на первый регистр флага, второй регистр флага, первый регистр и второй регистр.

| СИСТЕМА АСИНХРОННОЙ ВРЕМЕННОЙ ОПТИЧЕСКОЙ СВЯЗИ | 1990 |

|

RU2101867C1 |

| WO 9926364 А1, 27.05.1999 | |||

| WO 9528777 А1, 17.07.1997 | |||

| Устройство для центрирования деталей | 1979 |

|

SU872049A1 |

Авторы

Даты

2006-02-27—Публикация

2002-03-27—Подача