Изобретение относится к квантовой радиотехнике и оптической связи и может быть использовано в волоконно-оптических системах связи в качестве приема дискретной информации и синхронизации.

Известное устройство, описанное в статье Roland Wilson and John Richter "Generation and Performance of Quadraphase Welti Codes for Radar and Synchronization of Coherent and Differentially Coherent PSK" // IEEE Transactions on Communications, 1979, September, - v.COM-27, - №9, - p.1296-1301, fig.4, состоит из генератора опорных колебаний, фазовращателя на  , первого и второго перемножителей, первого и второго полосовых фильтров, вычитателя, порогового устройства, решающего блока и k - идентичных каскадов (где N=2k - число элементов в четверично-кодированной последовательности; k≥2 целое число), каждый из которых включает в себя знакозадающий блок, линию задержки на время 2k-lτ (где τ -длительность одного элемента принимаемой четверично-кодированной последовательности) и ячейку суммирования-вычитания, и осуществляет обработку сложных сигналов с относительной фазовой манипуляцией кодами Велти.

, первого и второго перемножителей, первого и второго полосовых фильтров, вычитателя, порогового устройства, решающего блока и k - идентичных каскадов (где N=2k - число элементов в четверично-кодированной последовательности; k≥2 целое число), каждый из которых включает в себя знакозадающий блок, линию задержки на время 2k-lτ (где τ -длительность одного элемента принимаемой четверично-кодированной последовательности) и ячейку суммирования-вычитания, и осуществляет обработку сложных сигналов с относительной фазовой манипуляцией кодами Велти.

Недостатком такого устройства является отсутствие возможности применения относительной фазовой манипуляции (ОФМ), так как при обработке четверично-кодированной последовательности с ОФМ при временных сдвигах элементов четверично-кодированной последовательности нарушаются взаимно корреляционные свойства, а также невозможности его применения для обработки оптического сигнала в волоконно-оптических системах связи, что ограничивает область применения данного устройства для приема четверично-кодированных последовательностей.

Известное устройство, описанное в статье В.В.Крылова, И.В.Стеклова "Формирование и обработка сложных сигналов с квадратурной манипуляцией кодами Велти" // Радиотехника, 1994 г., - №10, - с.61-65, рис.2, состоит из оптимального фильтра одиночного сигнала, первого и второго перемножителя и k - идентичных каскадов, каждый из которых включает в себя линию задержки на время 2k-lτ и ячейку суммирования-вычитания, и осуществляет обработку сложных сигналов с квадратурной манипуляцией кодами Велти.

Недостатком такого устройства является отсутствие возможности когерентной свертки четверично-кодированной последовательности, а также невозможность его применения для обработки оптического сигнала в волоконно-оптических системах связи, что ограничивает область применения данного устройства для приема четверично-кодированных последовательностей.

Наиболее близким по технической сущности и выполняемым функциям к заявленному устройству аналогу (прототипу), является устройство для приема четверично-кодированных последовательностей (см. авт.св. №1721837 СССР, МПК7 Н 04 L 27/26, заявл. 08.01.90, опубл. 23.03.92. Бюл. №11). Известное устройство содержит демодулятор, многоотводную линию задержки, коммутатор, k-1 блоков задержки, k-1 преобразователей импульсной последовательности, знакозадающий блок, вычитатель и решающий блок, каждый из блоков задержки содержит вычитатель, элемент задержки и переключатель, а каждый из преобразователей импульсной последовательности содержит знакозадающий блок и сумматор.

Устройство для приема четверично-кодированных последовательностей содержит последовательно соединенные многоотводную линию задержки, коммутатор, k-1 блоков задержки, вычитатель и решающий блок. При этом k - выходов многоотводной линии задержки подключены к соответствующим k - входам коммутатора. Кроме того, устройство также содержит последовательно соединенные k-1 преобразователей импульсной последовательности и знакозадающий блок, выход которого подключен к второму информационному входу вычитателя. Второй информационный выход и второй информационный вход каждого блока задержки соответственно являются вторым информационным входом и первым информационным выходом соответствующего преобразователя импульсной последовательности. Причем каждый блок задержки выполнен в виде последовательно соединенных вычитателя, элемента задержки и переключателя. Причем первый информационный вход вычитателя соответственно является первым информационным входом и вторым информационным выходом блока задержки. Второй информационный вход вычитателя является вторым информационным входом блока задержки. Второй информационный выход элемента задержки подключен к второму информационному входу переключателя, выход которого является первым информационньм выходом блока задержки. Установочные входы коммутатора и блоков задержки, которые являются установочными входами переключателей, являются вторыми установочными входами устройства. Каждый преобразователь импульсной последовательности выполнен в виде последовательно соединенных знакозадающего блока и сумматора. Вход знакозадающего блока является первым информационным входом преобразователя импульсной последовательности. Выход знакозадающего блока соответственно является первым информационным входом сумматора и первым информационным выходом преобразователя импульсной последовательности. Второй информационный вход и выход сумматора соответственно являются вторым информационным входом и вторым информационным выходом преобразователя импульсной последовательности. Установочные входы преобразователей импульсной последовательности, которые являются установочными входами знакозадающих блоков, а также установочный вход знакозадающего блока являются первыми установочными входами устройства. Вход демодулятора является входом устройства, а первый и второй информационные выходы демодулятора соответственно подключены к входу многоотводной линии задержки и к первому информационному входу первого преобразователя импульсной последовательности. При этом выход решающего блока является выходом устройства.

Устройство для приема четверично-кодированной последовательности - прототип осуществляет обработку сложных сигналов с четверичной фазовой манипуляцией (ФМ-4), где нечетные и четные элементы четверично-кодированной последовательности передаются с различными значениями начальной фазы, то есть значение начальной фазы элементов четверично-кодированной последовательности определяет его принадлежность к номеру дополнительной последовательности.

Недостатком такого устройства является отсутствие возможности когерентной свертки четверично-кодированной последовательности, а также невозможности его применения для обработки оптического сигнала в волоконно-оптических системах связи, что ограничивает область применения данного устройства для приема четверично-кодированных последовательностей.

Задачей изобретения является разработка устройства для приема четверично-кодированных последовательностей, обеспечивающего достижение технического результата, заключающегося в расширении области применения за счет когерентной свертки на оптическом уровне сложного сигнала. При этом повышается помехоустойчивость цифрового оптического сигнала или увеличивается длина регенерационного участка волоконно-оптической линии передачи в волоконно-оптических системах связи при приеме дискретной информации и синхронизации.

Для достижения технического результата в известном устройстве для приема четверично-кодированных последовательностей, содержащее последовательно соединенные многоотводную линию задержки, коммутатор и k-1 блоков задержки (при этом k - выходов многоотводной линии задержки подключены к соответствующим k - входам коммутатора), а также последовательно соединенные k-1 преобразователей импульсной последовательности и знакозадающий блок. Второй информационный выход и второй информационный вход каждого блока задержки соответственно являются вторым информационным входом и первым информационным выходом соответствующего преобразователя импульсной последовательности. Причем каждый блок задержки выполнен в виде последовательно соединенных элемента задержки и переключателя, при этом второй информационный выход элемента задержки подключен к второму информационному входу переключателя, выход которого является первым информационным выходом блока задержки. При этом установочные входы каждого блока задержки, которые являются установочными входами переключателей, а также установочный вход коммутатора являются первыми установочными входами устройства. Каждый преобразователь импульсной последовательности содержит знакозадающий блок и сумматор, при этом каждый знакозадающий блок содержит переключатель, а второй информационный вход и выход сумматора соответственно являются вторым информационным входом и вторым информационным выходом преобразователя импульсной последовательности. При этом установочные входы каждого преобразователя импульсной последовательности, которые являются установочными входами знакозадающих блоков, а также установочный вход знакозадающего блока являются вторыми установочными входами устройства. Кроме того, устройство содержит решающий блок, выход которого является выходом устройства. Дополнительно введены разветвитель и блок обработки оптического сигнала, причем вход разветвителя является входом устройства, а первый и второй информационные выходы разветвителя соответственно подключены к входу многоотводной линии задержки и к первому информационному входу первого преобразователя импульсной последовательности, первый информационный вход которого является входом знакозадающего блока. Причем в каждый блок задержки дополнительно введены последовательно соединенные направленный ответвитель и сумматор. При этом вход и второй информационный выход направленного ответвителя соответственно являются первым информационным входом и вторым информационным выходом блока задержки. Второй информационный вход сумматора является вторым информационным входом блока задержки. Причем выход сумматора подключен к входу элемента задержки. В каждый преобразователь импульсной последовательности дополнительно введен направленный ответвитель, вход и второй информационные выходы которого соответственно подключены к выходу знакозадающего блока и к первому информационному входу сумматора. При этом первый информационный выход направленного ответвителя является первым информационным выходом преобразователя импульсной последовательности. Первый информационный выход k-1-го блока задержки и выход знакозадающего блока соответственно подключены к первому и второму информационным входам блока обработки оптического сигнала, выход которого подключен к входу решающего блока.

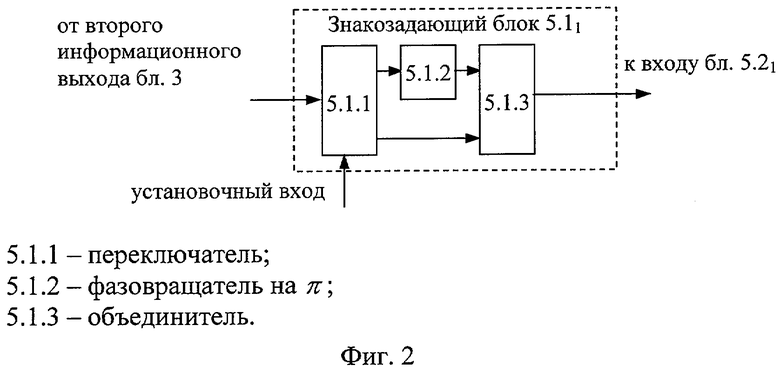

В знакозадающий блок дополнительно введены фазовращатель на π и объединитель. Причем первый и второй информационные выходы переключателя соответственно подключены к входу фазовращателя на π и к второму информационному входу объединителя, первый информационный вход которого подключен к выходу фазовращателя на π. При этом информационный и установочный входы переключателя соответственно являются информационным и установочными входами знакозадающего блока. Выход объединителя является информационным выходом знакозадающего блока.

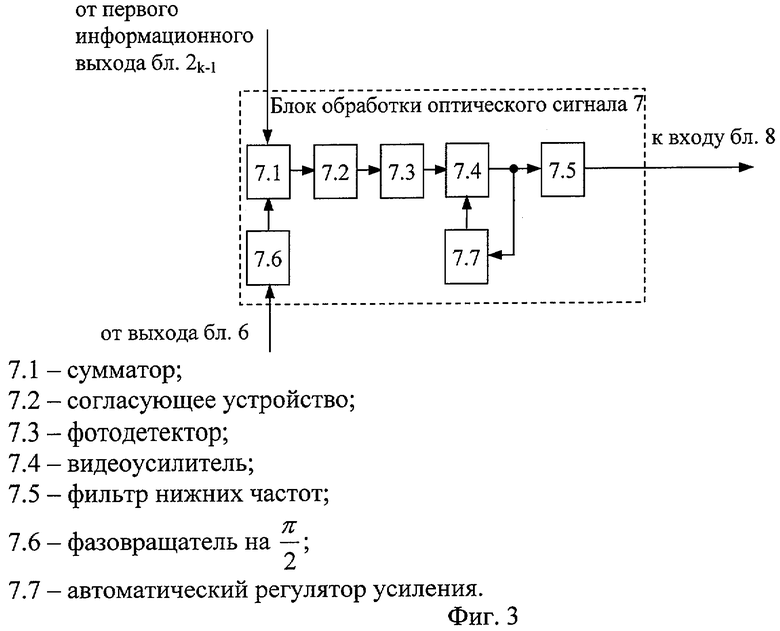

Блок обработки оптического сигнала состоит из сумматора, согласующего устройства, фотодетектора, видеоусилителя, фильтра нижних частот, фазовращателя на  и автоматического регулятора усиления. Причем в блоке обработки оптического сигнала последовательно соединены фазовращатель на

и автоматического регулятора усиления. Причем в блоке обработки оптического сигнала последовательно соединены фазовращатель на  , сумматор, согласующее устройство, фотодетектор, видеусилитель и фильтр нижних частот, выход которого является выходом блока обработки оптического сигнала. Выход видеусилителя подключен к входу автоматического регулятора усиления, выход которого подключен к управляющему входу видеоусилителя. Первый информационный вход сумматора и вход фазовращателя на

, сумматор, согласующее устройство, фотодетектор, видеусилитель и фильтр нижних частот, выход которого является выходом блока обработки оптического сигнала. Выход видеусилителя подключен к входу автоматического регулятора усиления, выход которого подключен к управляющему входу видеоусилителя. Первый информационный вход сумматора и вход фазовращателя на  соответственно являются первым и вторым информационными входами блока обработки оптического сигнала.

соответственно являются первым и вторым информационными входами блока обработки оптического сигнала.

Благодаря новой совокупности существенных признаков за счет введения разветвителя, направленных ответвителей и блока обработки оптического сигнала обеспечивается возможность использования когерентной свертки на оптическом уровне четверично-кодированных последовательностей. Этим достигается возможность расширения области применения заявленного устройства, в частности, повышения помехоустойчивости цифрового оптического сигнал или увеличения длины регенерационного участка волоконно-оптической линии передачи в волоконно-оптических системах связи при приеме дискретной информации и синхронизации.

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, и выявление источников, содержащих сведения об аналогах заявленного изобретения, позволили установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Выбор из перечня выявленных аналогов прототипа, как наиболее близкого по совокупности существенных признаков аналога, позволил выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявленное изобретение соответствует критерию "новизна".

Для проверки соответствия заявленного изобретение критерию "изобретательский уровень" заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, определенного заявителем. Не выявлено влияние преобразований, предусматриваемых существенными признаками заявленного изобретения, на достижение технического результата. В частности, заявленным изобретением не предусматриваются следующие преобразования: дополнение известного средства какой-либо известной частью, присоединяемой к нему по известным правилам, для достижения технического результата, в отношении которого установлено влияние именно таких дополнений; замену какой-либо части известного средства другой известной частью для достижения технического результата, в отношении которого установлено влияние именно такой замены; исключение какой-либо части средства с одновременным исключением обусловленной ее наличием функции и достижением при этом обычного для такого исключения результата; увеличение однотипных элементов для усиления технического результата, обусловленного наличием в средстве именно таких элементов; выполнение известного средства или его части из известного материала для достижения технического результата, обусловленного известными свойствами материала; создание средства, состоящего из известных частей, выбор которых и связь между которыми осуществлены на основании известных правил, рекомендаций, и достигаемый при этом технический результат обусловлен только известными свойствами частей этого объекта и связей между ними; изменение количественных признаков или взаимосвязи признаков, если известен факт влияния каждого из них на технический результат и новые значения признаков или их взаимосвязь могли быть получены из известных зависимостей.

Следовательно, заявленное изобретение соответствует критерию "изобретательский уровень".

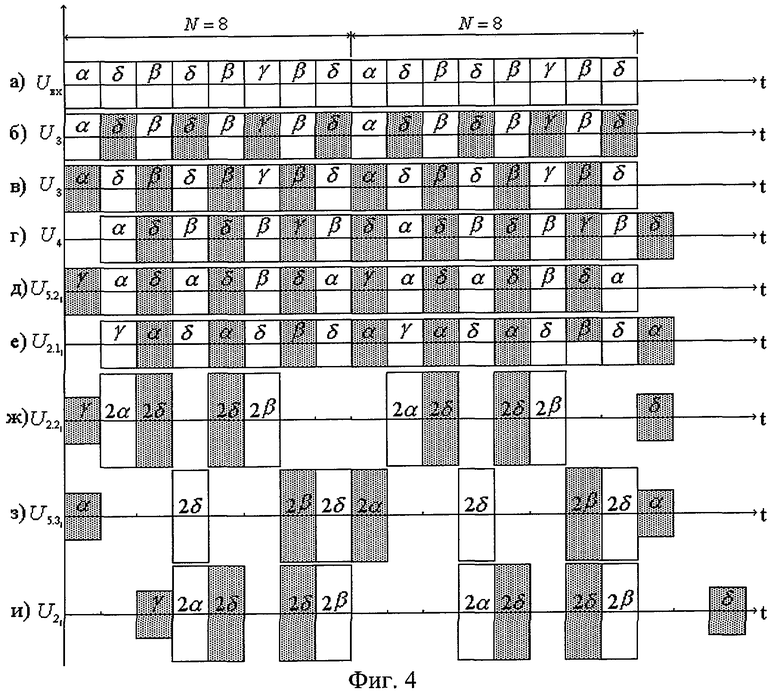

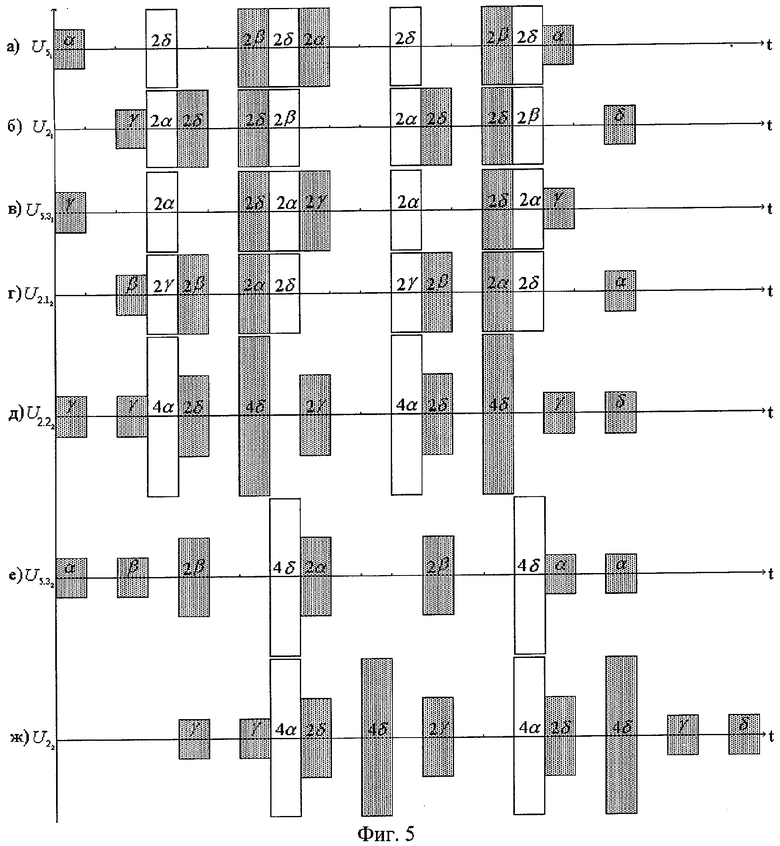

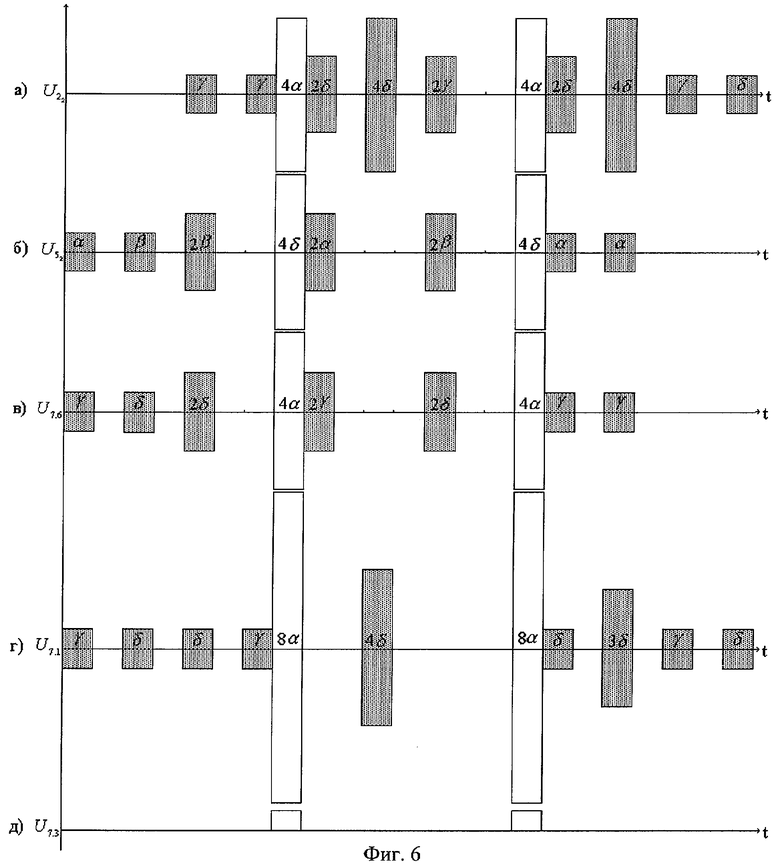

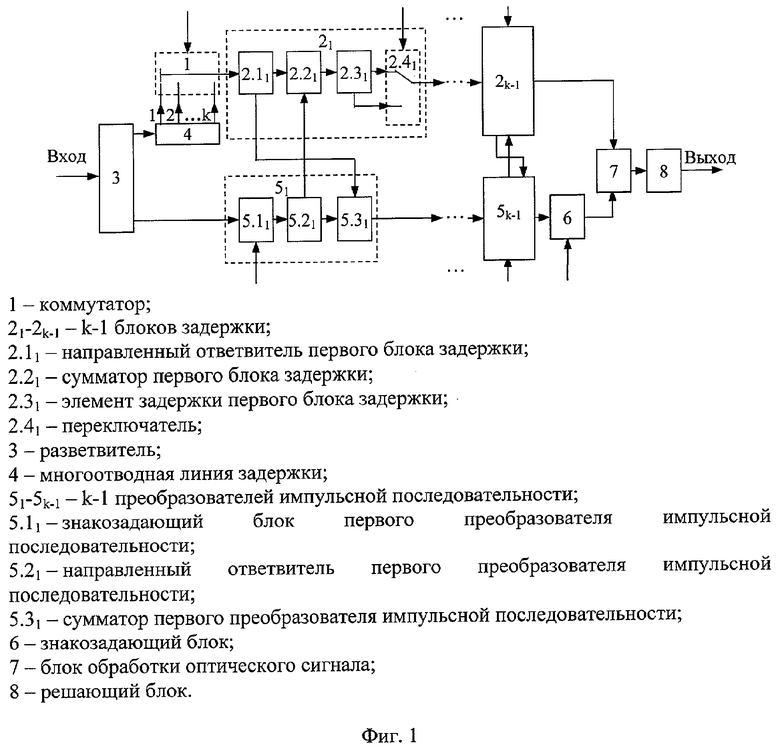

Изобретение поясняется графическими материалами, на которых изображено: фиг.1 - структурная схема устройства для приема четверично-кодированных последовательностей; фиг.2 - структурная схема знакозадающего блока; фиг.3 - структурная схема блока обработки оптического сигнала; фиг.4 - эпюры, поясняющие принцип свертки дополнительных последовательностей в первом блоке задержки и в первом преобразователе импульсной последовательности; фиг.5 - эпюры, поясняющие принцип свертки дополнительных последовательностей в k-1-ом блоке задержки и k-1-ом преобразователе импульсной последовательности; фиг.6 - эпюры, поясняющие принцип свертки дополнительных последовательностей в блоке обработки оптического сигнала.

Сведения, подтверждающие возможность осуществления изобретения с получением вышеуказанного технического результата, заключаются в следующем.

Устройство для приема четверично-кодированных последовательностей, представленное на фиг.1, содержащее последовательно соединенные многоотводную линию задержки 4, коммутатор 1, k-1 блоков задержки 21-2k-1, блок обработки оптического сигнала 7 и решающий блок 8, при этом k - выходов многоотводной линии задержки 4, подключены к соответствующим k - входам коммутатора 1. Также последовательно соединенные k-1 преобразователей импульсной последовательности 51-5k-1 и знакозадающий блок 6, выход которого подключен к второму информационному входу блока обработки оптического сигнала 7. Второй информационный выход и второй информационный вход каждого блока задержки 21-2k-1 соответственно являются вторым информационным входом и первым информационным выходом соответствующего преобразователя импульсной последовательности 51-5k-1. Причем каждый блок задержки 21-2k-1 выполнен в виде последовательно соединенных направленного ответвителя 2.11, сумматора 2.21 элемента задержки 2.31 и переключателя 2.41. Вход и второй выход направленного ответвителя 2.11 соответственно являются первым информационным входом и вторым информационным выходом блока задержки 21, второй информационный вход сумматора 2.21 является вторым информационным входом блока задержки 21, второй информационный выход элемента задержки 2.31 подключен к второму информационному входу переключателя 2.41, выход которого является первым информационным выходом блока задержки 21. При этом установочные входы каждого блока задержки 21, которые являются установочными входами переключателей 2.41, а также установочный вход коммутатора 1 являются первыми установочными входами устройства. Каждый преобразователь импульсной последовательности 51-5k-1 выполнен в виде последовательно соединенных знакозадающего блока 5.11, направленного ответвителя 5.21 и сумматора 5.31, вход знакозадающего блока 5.11 является первым информационным входом преобразователя импульсной последовательности 51, первый информационный выход направленного ответвителя 5.21 является первым информационным выходом преобразователя импульсной последовательности 51, второй информационный вход и выход сумматора 5.31 соответственно являются вторым информационным входом и вторым информационными выходами преобразователя импульсной последовательности 51. При этом установочные входы каждого преобразователя импульсной последовательности 51-5k-1, которые являются установочными входами знакозадающих блоков 5.11, а также установочный вход знакозадающего блока 6 являются вторыми установочными входами устройства. Вход разветвителя 3 является входом устройства, первый и второй информационные выходы разветвителя 3 соответственно подключены к входу многоотводной линии задержки 4 и к первому информационному входу первого преобразователя импульсной последовательности 51, первый информационный вход которого является входом знакозадающего блока 5.11, выход решающего блока 8 является выходом устройства.

Коммутатор 1 предназначен для подключения в соответствии с номером j функции Радемахера (где j=0,1,..., k) k-го выхода многоотводной линии задержки 4 к первому информационному входу первого блока задержки 21. Он может быть реализован, как описано в книге P.P.Убайдуллаев "Волоконно-оптические сети" (М.: Эко-Трендз, 2000, с.60-61, рис.3.19 а), а также в книге Н.Н.Слепова "Современные технологии цифровых оптоволоконных сетей связи" (М.: Радио и связь, 2000, с.326, рис.10-12).

Блоки задержки 21-2k-1, каждый из которых состоит из направленного ответвителя 2.11, сумматора 2.21, элемента задержки 2.31 и переключателя 2.41, предназначены для свертки первой дополнительной последовательности и задержки ее на выходе на время в соответствии с номером j функции Радемахера.

Направленные ответвители 2.11-2.1k-1 в блоках задержки 2i-2k-i и направленные ответвители 5.21-5.2k-1 в преобразователях импульсной последовательности 51-5k-1 идентичны и предназначены для разделения оптического сигнала на прямой и отраженный оптический сигнал, отличающиеся на  с половинной мощностью оптического сигнала в каждой ветви направленного ответвителя. Они могут быть реализованы, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.194-209, рис.6.10 б, г).

с половинной мощностью оптического сигнала в каждой ветви направленного ответвителя. Они могут быть реализованы, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.194-209, рис.6.10 б, г).

Сумматоры 2.21-2.2k-1 в блоках задержки 21-2K-1, сумматоры 5.31-5.3k-1 в преобразователях импульсной последовательности 51-5k-1 и сумматор 7.1 в блоке обработки оптического сигнала 7 идентичны и предназначены для объединения первой и второй дополнительных последовательностей. Они могут быть реализованы, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.194-209, рис.6.10 а, в).

Элементы задержки 2.31-2.3k-1 предназначены для задержки первой дополнительной последовательности на первом и втором информационных выходах соответственно на 2h-1τ и 2hτ (где h=1,2,...,k-1 - номер элемента задержки 2.3k-1 блока задержки 2k-1). Они могут быть реализованы, как описано в книге Л.Е.Варакин "Системы связи с шумоподобными сигналами" (М.: Радио и связь, 1985, с.352-361, рис.21.11).

Переключатели 2.41-2.4k-1 предназначены для подключения в соответствии с номером j функции Радемахера первого или второго информационных выходов элементов задержки 2.31-2.3k-1 к второму информационному выходу блока задержки 21-2k-1. Они могут быть реализованы, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.209-221, рис.6.23).

Разветвитель 3 предназначен для деления четверично-кодированной последовательности на две дополнительные последовательности с половинной мощностью в каждой ветви. Он может быть реализован, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.194-209, рис.6.10 а, в).

Многоотводная линия задержки 4 предназначена для задержки первой дополнительной последовательности на l-ом отводе многоотводной линии задержки на 2ι-1τ (где l=1,2,..., k - номер отвода многоотводной линии задержки). Она может быть реализована, как описано в книге Л.Е.Варакин "Системы связи с шумоподобными сигналами" (М.: Радио и связь, 1985, с.352-361, рис.21.11).

Преобразователи импульсной последовательности 51-5k-1, каждый из которых состоит из знакозадающего блока 5.11, направленного ответвителя 5.21 и сумматора 5.31 предназначены в соответствии с номером j функции Радемахера для инвертирования (неинвертирования), а также свертки второй дополнительной последовательности.

Знакозадающие блоки 5.11-5.1k-1 в преобразователях импульсной последовательности 51-5k-1 и знакозадающий блок 6 идентичны и предназначены для инвертирования (неинвертирования) в соответствии с номером j функции Радемахера второй дополнительной последовательности. Вариант знакозадающего блока 5.11 представлен на фиг.2 и состоит из переключателя 5.1.1, фазовращателя на π 5.1.2 и объединителя 5.1.3. Первый и второй информационные выходы переключателя 5.1.1 соответственно подключены к входу фазовращателя на π 5.1.2 и к второму информационному входу объединителя 5.1.3, первый информационный вход которого подключен к выходу фазовращателя на π 5.1.2. При этом информационный и установочный входы переключателя 5.1.1 соответственно являются информационным и установочным входами знакозадающего блока 5.1. Выход объединителя 5.1.3 является информационным выходом знакозадающего блока 5.1.

Переключатель 5.1.1 предназначен для подключения своего входа к своему первому или второму информационному выходу в соответствии с номером j функции Радемахера. Он может быть реализован, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.209-221, рис.6.23).

Фазовращатель на π 5.1.2 предназначен для поворота фазы оптического сигнала на π. Он выполнен в виде двух последовательно соединенных электрооптических модуляторов на основе эффекта Поккельса и может быть реализован, как описано в книге Н.Н.Слепов "Современные технологии цифровых оптоволоконных сетей связи" (М.: Радио и связь, 2000, с.348-349, рис.10-36).

Объединитель 5.1.3 предназначен для объединения оптических сигналов. Он может быть реализован, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.194-209, рис.6.10 а, в).

Блок обработки оптического сигнала 7, схема которого представлена на фиг.3, предназначен для окончательной свертки четверично-кодированной последовательности на оптическом уровне, а также обработки оптического сигнала и состоит из сумматора 7.1, согласующего устройства 7.2, фотодетектора 7.3, видеоусилителя 7.4, фильтра нижних частот 7.5, фазовращателя на  и автоматического регулятора усиления 7.7. Причем в блоке обработки оптического сигнала 7 последовательно соединены фазовращатель на

и автоматического регулятора усиления 7.7. Причем в блоке обработки оптического сигнала 7 последовательно соединены фазовращатель на  сумматор 7.1, согласующее устройство 7.2, фотодетектор 7.3, видеусилитель 7.4 и фильтр нижних частот 7.5, выход которого является выходом блока обработки оптического сигнала 7. Выход видеусилителя 7.4 подключен к входу автоматического регулятора усиления 7.7, выход которого подключен к управляющему входу видеоусилителя 7.4. Первый информационный вход сумматора 7.1 и вход фазовращателя на

сумматор 7.1, согласующее устройство 7.2, фотодетектор 7.3, видеусилитель 7.4 и фильтр нижних частот 7.5, выход которого является выходом блока обработки оптического сигнала 7. Выход видеусилителя 7.4 подключен к входу автоматического регулятора усиления 7.7, выход которого подключен к управляющему входу видеоусилителя 7.4. Первый информационный вход сумматора 7.1 и вход фазовращателя на  на - 7.6 соответственно являются первым и вторым информационными входами блока обработки оптического сигнала 7.

на - 7.6 соответственно являются первым и вторым информационными входами блока обработки оптического сигнала 7.

Согласующее устройство 7.2 предназначено для вывода оптического излучения из волоконного световода волоконно-оптического кабеля и сопряжения его с фотодетектором 7.3. Оно может быть реализовано, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.193, рис.6.9).

Фотодетектор 7.3 предназначен для преобразования входного оптического сигнала в электрический цифровой сигнал. Он может быть реализован, как описано в книге А.Б.Иванов "Волоконная оптика: компоненты, системы передачи, измерения" (М.: Сайрус Системе, 1999, с.149-154, рис.2.20).

Видеоусилитель 7.4 предназначен для усиления цифрового сигнала до уровня, необходимого для дальнейшей обработки. Он может быть реализован, как описано в книге Л.Н.Астраханцев и др. "Военные системы многоканальной электросвязи" под ред. А.Т.Лебедева (Л.: ВАС, 1979, с.263-265, рис.18.22, рис.18.23).

Фильтр нижних частот 7.5 предназначен для выделения полезного сигнала и эффективного подавления всех побочных комбинационных колебаний на входе решающего блока 8. Он может быть реализован, как описано в книге А.Ф.Белецкий "Основы теории линейных электрических цепей" (М.: Связь, 1967, с.591-596, рис.21.36, рис.21.37).

Фазовращатель на  предназначен для поворота фазы второй дополнительной последовательности на

предназначен для поворота фазы второй дополнительной последовательности на  Он выполнен в виде электрооптического модулятора на основе эффекта Поккельса и может быть реализован, как описано в книге Н.Н.Слепов "Современные технологии цифровых оптоволоконных сетей связи" (М.: Радио и связь, 2000, с.348-349, рис.10-36).

Он выполнен в виде электрооптического модулятора на основе эффекта Поккельса и может быть реализован, как описано в книге Н.Н.Слепов "Современные технологии цифровых оптоволоконных сетей связи" (М.: Радио и связь, 2000, с.348-349, рис.10-36).

Автоматический регулятор усиления 7.7 предназначен для формирования управляющего напряжения для изменения коэффициента усиления видеоусилителя 7.4 при слабом уровне входного цифрового сигнала, обеспечивая линейность всего тракта приема цифрового сигнала. Он может быть реализован, как описано в книге Л.Н.Астраханцев и др. "Военные системы многоканальной электросвязи" под ред. А.Т.Лебедева (Л.: ВАС, 1979, с.302-308, рис.20.4).

Решающий блок 8 предназначен для принятия решения по идентификации и регистрации единичного элемента цифрового сигнала. Он может быть реализован, как описано в книге М.М.Бутусов и др. "Волоконно-оптические системы передачи" под ред. В.Н.Гомзина (М.: Радио и связь, 1992, с.34-36, рис.1.11).

Устройство для приема четверично-кодированных последовательностей, представленное на фиг.1, работает следующим образом.

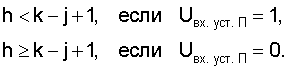

По первым установочным входам устройства (фиг.1) до приема четверично-кодированной последовательности с периодом N=2k (где N - число элементов в четверично-кодированной последовательности) производится коммутация многоотводной линии задержки 4 и элементов задержки 2.31-2.3k-1 в соответствии с номером j функции Радемахера, соответствующего принимаемой четверично-кодированной последовательности, по следующему правилу:

а) номер отвода многоотводной линии задержки 4, который с помощью коммутатора 1 коммутируется на первый информационный вход блока задержки 21, который является входом направленного ответвителя 2.11, определяется выражением l=k-j+1 (где l=1,2,..., k; l - номер отвода многоотводной линии задержки).

б) в зависимости от номера j функции Радемахера формируются установочные напряжения Uвх.уст.П, поступающие на установочные входы переключателей 2.41-2.4k-1 блоков задержки 21-2k-1.

Номера блоков задержки 21-2k-1, в которых переключатели 2.41-2.4k-1 подключают вторые информационные выходы элементов задержки 2.31-2.3k-1 к своим выходам, которые являются вторыми информационными выходами блоков задержки 21-2k-1, определяются по следующему правилу:

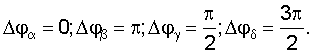

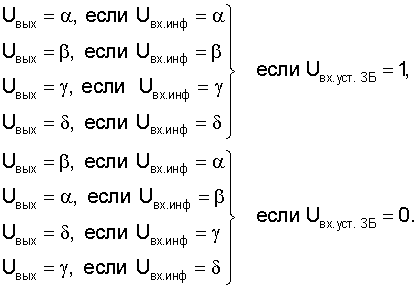

По вторым установочным входам устройства (фиг.1) до приема четверично-кодированной последовательности с периодом N=2k знакозадающие блоки 5.11-5.1k-1 преобразователей импульсной последовательности 51-5k-1 и знакозадающий блок 6 включаются в режим инвертирования или неинвертирования поступающей на их входы четверично-кодированной последовательности в соответствии с номером E-кода (где i=0,1,...,N-1, i-номер E-кода), соответствующего принимаемой четверично-кодированной последовательности, по следующему правилу:

а) при номере Е-кода i=7 (для k=3) в двоичном исчислении номер Е-кода соответствует кодовой комбинации 111, следовательно, установочные напряжения Uвх.уст. 3Б поступающие на установочные входы знакозадающих блоков 5.11-5.1k-1 и 6 будут соответствовать Uвх.уст. 3Б=1.

В качестве примера на эпюрах фиг.4а показано цикловое поступление на вход разветвителя 3 оптического сигнала в виде двух четверично-кодированных последовательностей (Е-кода) αδβδβγβδ с алфавитом α, β, γ, δ при числе элементов N=8, где α=-β, γ=-δ, причем элементы α и β ортогональны γ и δ. Это может быть, например, фазоманипулированная последовательность, в которой начальные фазы элементов принимают значения

В разветвителе 3 четверично-кодированная последовательность (фиг.4а) делится на две дополнительные последовательности с половинной мощностью в каждой ветви разветвителя 3. На первом и втором информационных выходах разветвителя 3 соответственно формируются первая и вторая дополнительные последовательности. При этом в первой дополнительной последовательности нечетные элементы четверично-кодированной последовательности α, β являются активными, а четные элементы четверично-кодированной последовательности γ, δ являются пассивными. Во второй дополнительной последовательности четные элементы четверично-кодированной последовательности γ, δ являются активными, а нечетные элементы четверично-кодированной последовательности α, β являются пассивными. Частота чередования активных элементов одной и другой дополнительных последовательностей определяется номером j функции Радемахера. Например, при j=k активные элементы одной последовательности чередуются с активными элементами другой последовательности через один, а при j=1 сначала следуют все активные элементы первой последовательности, а затем - все активные элементы второй последовательности. Эпюры первой и второй дополнительных последовательностей при j=k=3 представлены на фиг.4б, в соответственно, при этом неактивные элементы первой и второй дополнительных последовательностей на эпюрах выделены в виде темных квадратов.

Первая дополнительная последовательность (фиг.4б) поступает на вход многоотводной линии задержки 4, в которой задержка первой дополнительной последовательности (фиг.4б) в ее l-м отводе равна 2l-1τ. Коммутатор 1 обеспечивает в соответствии с номером j=3 функции Радемахера подключение первого выхода l=1 многоотводной линии задержки 4 к первому информационному входу блока задержки 21, который является входом направленного ответвителя 2.11. Следовательно, первая дополнительная последовательность (фиг.4б) в многоотводной линии задержки 4 задерживается на τ. Эпюра задержанной первой дополнительной последовательности представлена на фиг.4г. Этим обеспечивается совмещение по времени активных и пассивных элементов первой (задержанной на τ) и второй дополнительных последовательностей (фиг.4в, г), при этом первая и вторая дополнительные последовательности (фиг.4в, г) имеют по 2k-1 активных элементов. Вторая дополнительная последовательность (фиг.4в) поступает на первый информационный вход преобразователя импульсной последовательности 51, который является информационным входом знакозадающего блока 5.11.

Знакозадающий блок 5.11, представлен на фиг.2 (аналогичным образом реализованы все остальные знакозадающие блоки 5.1k-1 и 6). Знакозадающий блок 5.11 работает следующим образом. Вторая дополнительная последовательность (фиг.4в) поступает на информационный вход переключателя 5.1.1, где при поступлении установочного напряжения Uвх.уст.3Б=0 на установочный вход переключателя 5.1.1 вторая дополнительная последовательность (фиг.4в) с первого информационного выхода переключателя 5.1.1 через фазовращатель на π 5.1.2 поступает на первый информационный вход объединителя 5.1.3. На выходе знакозадающего блока 5.11 формируется инвертированная четверично-кодированная последовательность. При поступлении установочного напряжения Uвх.уст.3Б=1 на установочный вход переключателя 5.1.1 вторая дополнительная последовательность (фиг.4в) с первого информационного выхода переключателя 5.1.1 поступает на второй информационный вход объединителя 5.1.3. На выходе объединителя 5.1.3, выход которого является выходом знакозадающего блока 5.11, формируется неинвертированная четверично-кодированная последовательность (фиг.4в), которая соответствует дополнительной последовательности, поступающей на информационный вход оптического переключателя 5.1.1. Следовательно, знакозадающие блоки 5.11-5.1k-1 (блок 6) работают по следующему правилу:

Таким образом, под действием установочного напряжения Uвх.уст.3Б=0 на установочные входы знакозадающих блоков 5.11-5.1k-1 и 6 на их выходах формируется инвертированная вторая дополнительная последовательность, а под действием установочного напряжения Uвх.уст.3Б=1 на установочные входы знакозадающих блоков 5.11-5.1k-1 и 6 на их выходах формируется неинвертированная вторая дополнительная последовательность, которая соответствует дополнительной последовательности, поступающей на информационные входы знакозадающих блоков 5.11-5.1k-1 и 6. Для примера выбран такой Е-код у которого по вторым установочным входам устройства все знакозадающие блоки 5.11-5.1k-1 и 6 включены в режим неинвертирования по фазе, поступающего на их информационный вход второй дополнительной последовательности.

С выхода знакозадающего блока 5.11 вторая дополнительная последовательность (фиг.4в) поступает на вход направленного ответвителя 5.21. В направленном ответвителе 5.21 с полупрозрачным зеркалом вторая дополнительная последовательность (фиг.4в) разделяется на две ветви (с половинной мощностью второй дополнительной последовательности в каждой ветви направленного ответвителя 5.21). На первом и втором информационных выходах направленного ответвителя 5.21 соответственно формируются отраженная и прямая вторые дополнительные последовательности. С второго информационного выхода направленного ответвителя 5.21 вторая дополнительная последовательность (фиг.4 в), без фазовых изменений (прямая), поступает на первый информационный вход сумматора 5.31, а с первого информационного выхода направленного ответвителя 5.21, который является первым информационным выходом преобразователя импульсной последовательности 51, отраженная вторая дополнительная последовательность, отличающаяся на  поступает на второй информационный вход блока задержки 21, который является вторым информационным входом сумматора 2.21. Эпюра отраженной второй дополнительной последовательности представлена на фиг.4д.

поступает на второй информационный вход блока задержки 21, который является вторым информационным входом сумматора 2.21. Эпюра отраженной второй дополнительной последовательности представлена на фиг.4д.

С выхода коммутатора 1 задержанная на τ первая дополнительная последовательность (фиг.4г) поступает на первый информационный вход блока задержки 21, который является информационным входом направленного ответвителя 2.11. В направленном ответвителе 2.11 с полупрозрачным зеркалом задержанная первая дополнительная последовательность (фиг.4г) разделяется на две ветви (с половинной мощностью первой дополнительной последовательности в каждой ветви направленного ответвителя 2.11). На первом и втором информационных выходах направленного ответвителя 2.11 соответственно формируются прямая и отраженная первые дополнительные последовательности. С первого информационного выхода направленного ответвителя 2.11 первая задержанная дополнительная последовательность (фиг.4г), без фазовых изменений (прямая), поступает на первый информационный вход сумматора 2.21, а с второго информационного выхода направленного ответвителя 2.11, который является вторым информационным выходом блока задержки 21, отраженная первая задержанная дополнительная последовательность, отличающаяся на  поступает на второй информационный вход преобразователя импульсной последовательности 51, который является вторым информационным входом сумматора 5.31. Эпюра отраженной задержанной первой дополнительной последовательности представлена на фиг.4 е.

поступает на второй информационный вход преобразователя импульсной последовательности 51, который является вторым информационным входом сумматора 5.31. Эпюра отраженной задержанной первой дополнительной последовательности представлена на фиг.4 е.

При этом дополнительные последовательности в силу механизма их образования характерны тем, что половина их активных элементов одинакова по фазе, а другая половина активных элементов - противоположна по фазе. Следовательно, в сумматорах 2.21 и 5.31 происходит суммирование по фазе 2k-2 активных элементов дополнительных последовательностей с одинаковой фазой (в сумматоре 2.21 суммируются последовательности, представленные на фиг.4г и фиг.4д, а в сумматоре 5.31 суммируются последовательности, представленные на фиг.4в и фиг.4е). В результате на выходах сумматоров 2.21 и 5.31 образуются новые дополнительные последовательности, но они содержат по 2k-2 активных элемента с амплитудами в два раза большими, чем у элементов принимаемой четверично-кодированной последовательности. Эпюры вновь сформированных первой и второй дополнительных последовательностей представлены на фиг.4ж, з соответственно.

С выхода сумматора 5.31 вторая дополнительная последовательность (фиг.4з) поступает на второй информационный выход преобразователя импульсной последовательности 51. С выхода сумматора 2.21 первая дополнительная последовательность (фиг.4ж) поступает на вход элемента задержки 2.31. На первом информационном выходе первая дополнительная последовательность (фиг.4ж) задерживается на 2h-1τ, а на втором информационном выходе элемента задержки 2.31 первая дополнительная последовательность (фиг.4ж) задерживается на 2hτ.

При поступлении на установочные входы переключателей 2.41-2.4k-1 установочного напряжения Uвх.уст.П=1 они подключают к своим выходам (которые являются первыми информационными выходами блоков задержки 21-2k-1) первые информационные выходы соответствующих элементов задержки 2.31-2.3k-1, что обеспечивает задержку первой дополнительной последовательности на 2h-1τ, а при поступлении на установочные входы переключателей 2.41-2.4k-1 установочного напряжения Uвх.уст.П=0 они подключают к своим выходам вторые информационные выходы соответствующих элементов задержки 2.31-2.3k-1, что обеспечивает задержку первой дополнительной последовательности на 2hτ. Для примера выбран Е-код (при k=j=3), при котором по первым установочным входам устройства все переключатели 2.41-2.4k-1 обеспечивают подключение второго информационного выхода элементов задержки 2.31-2.3k-1 к вторым информационным выходам блоков задержки 21-2k-i, что обеспечивает задержку первой дополнительной последовательности на 2hτ в блоках задержки 21-2k-1. Следовательно, первая дополнительная последовательность (фиг.4ж) в блоке задержки 21 задерживается на втором информационном выходе элемента задержки 2.31 на 2 τ и с помощью переключателя 2.41 подключается к первому информационному выходу блока задержки 21. Эпюра задержанной первой дополнительной последовательности в элементе задержки 2.31 на первом информационном выходе блока задержки 21 представлена на фиг.4и.

Таким образом, блок задержки 21 обеспечивает при помощи элементов задержки 2.31 и переключателя 2.41 совмещение активных элементов новых сформированных дополнительных последовательностей (фиг.4з, и).

На первом и втором информационных выходах направленного ответвителя 2.12 вновь формируются прямая (фиг.4 и или фиг.5б) и отраженная (фиг.5г) первая дополнительная последовательность, а на первом и втором информационных выходах направленного ответвителя 5.22 вновь формируются отраженная (фиг.5в) и прямая (фиг.4з или фиг.5а) вторая дополнительная последовательность. В сумматорах 2.22 и 5.32 суммируются соответствующие прямые (фиг.4з, и или фиг.5а, б) и отраженные (фиг.5в, г) дополнительные последовательности, а на их выходах образуются новые дополнительные последовательности, содержащие по 2k-3 активных элемента с амплитудами в 4 раза большими, чем у элементов принимаемой четверично-кодированной последовательности, и так далее. Эпюры вновь сформированных первой и второй дополнительных последовательностей представлены на фиг.5д, е соответственно.

При этом первая дополнительная последовательность (фиг.5д) в блоке задержки 22 задерживается на втором информационном выходе элемента задержки 2.32 на 4τ и с помощью переключателя 2.42 подключается к первому информационному выходу блока задержки 22. Эпюра задержанной первой дополнительной последовательности в элементе задержки 2.32 на первом информационном выходе блока задержки 22 представлена на фиг.5ж.

Первая дополнительная последовательность (фиг.5ж) с первого информационного выхода блока задержки 22 поступает на первый информационный вход блока обработки оптического сигнала 7, а вторая дополнительная последовательность (фиг.5е) с второго информационного выхода преобразователя импульсной последовательности 52, поступает на информационный вход знакозадающего блока 6. Под действием установочного напряжения Uвх.уст.ЗБ=1 на установочный вход знакозадающего блока 6 на его выходе формируется неинвертированная вторая дополнительная последовательность (фиг.5е), которая соответствует дополнительной последовательности, поступающей на информационный вход знакозадающего блока 6. С выхода знакозадающего блока 6 вторая дополнительная последовательность (фиг.5е) поступает на второй информационный вход блока обработки оптического сигнала 7.

Блок обработки оптического сигнала 7 представлен на фиг.3. Блок обработки оптического сигнала 7 работает следующим образом. Первая дополнительная последовательность (фиг.5ж или фиг.6а) поступает на первый информационный вход сумматора 7.1, а вторая дополнительная последовательность (фиг.5е или фиг.6б) поступает на фазовращатель на  В фазовращателе на

В фазовращателе на  вторая дополнительная последовательность (фиг.6б) поворачивается

вторая дополнительная последовательность (фиг.6б) поворачивается  Эпюра повернутой на

Эпюра повернутой на  второй дополнительной последовательности представлена на фиг.6в. С выхода фазовращателя на

второй дополнительной последовательности представлена на фиг.6в. С выхода фазовращателя на  вторая дополнительная последовательность (фиг.6в) поступает на второй информационный вход сумматора 7.1, где происходит сложение по фазе первой (фиг.6а) и второй (фиг.6в) дополнительных последовательностей с амплитудой 2k-1. Эпюра свернутой четверично-кодированной последовательности представлена на фиг.6г.

вторая дополнительная последовательность (фиг.6в) поступает на второй информационный вход сумматора 7.1, где происходит сложение по фазе первой (фиг.6а) и второй (фиг.6в) дополнительных последовательностей с амплитудой 2k-1. Эпюра свернутой четверично-кодированной последовательности представлена на фиг.6г.

На выходе сумматора 7.1 на протяжении времени 2k-1 τ после начала поступления на вход устройства четверично-кодированной последовательности полезный сигнал с фазой Δϕα будет отсутствовать, но по истечении этого времени появится импульс длительностью τ с амплитудой в 2k раз больше амплитуды элемента четверично-кодированной последовательности и фазой Δϕα.

Таким образом, в процессе приема четверично-кодированной последовательности формируется сигнал (фиг.6г) с амплитудой, пропорциональной автокорреляционной функции (АКФ) этой последовательности при условии, что по вторым установочным входам устройства знакозадающие блоки 5.11-5.1k-1 и 6 включены в соответствии с номером Е-кода, соответствующего принимаемой четверично-кодированной последовательности, а по первым установочным входам устройства произошла коммутация многоотводной линии задержки 4 и элементов задержки 2.31-2.3k-1 в соответствии с номером j функции Радемахера, соответствующего принимаемой четверично-кодированной последовательности. В результате происходит когерентная свертка на оптическом уровне четверично-кодированной последовательности с увеличением амплитуды оптического сигнала на входе фотодетектора в N раз с фазой Δϕα

Следовательно, свернутую четверично-кодированную последовательность на входе фото детектора 7.3 можно представить следующим выражением:

U7.1=NUccos(2πƒн+Δϕα),

где ƒн - частота несущего сигнала; Uc - амплитуда четверично-кодированной последовательности.

Свертка четверично-кодированной последовательности (кодов Велти или E-кодов) характеризуется тем, что апериодическая АКФ имеет импульсный вид (не имеет боковых выбросов) Uα=000000080000000 при N=8 и Uс=1.

В предлагаемом устройстве приема четверично-кодированной последовательности относительно просто решена задача когерентной свертки оптического сигнала, поскольку колебания принимаются от одного и того же источника. Любые изменения в световой линии от передатчика до приемника оказываются одинаковыми для всех элементов четверично-кодированной последовательности.

АКФ четверично-кодированной последовательности (фиг.6г) поступает на вход согласующего устройства 7.2, которое выводит оптическое излучение из волоконного световода волоконно-оптического кабеля и сопрягает его с фотодетектором 7.3. С согласующего устройства 7.2 АКФ четверично-кодированной последовательности (фиг.6г) поступает на вход фотодетектора 7.3. Таким образом, на выходе фотодетектора 7.3 формируются цифровые сигналы, представленные на эпюрах фиг.6д.

Вследствие того, что элементы четверично-кодированной последовательности α и β ортогональны γ и δ, то на выходе фотодетектора 7.3 отклики на "чужие" сигналы равны нулю, то есть на выходе фотодетектора 7.3 Uβ=0, Uγ=0 и Uδ=0.

Сформированный (фиг.6г) цифровой сигнал с выхода фотодетектора 7.3 поступает на вход видеусилителя 7.4 для первичного усиления цифрового сигнала. С выхода видеусилителя 7.4 цифровой сигнал одновременно поступает на вход автоматического регулятора усиления 7.7 и фильтра нижних частот 7.5. В автоматическом регуляторе усиления 7.7 формируется управляющее напряжение, которое поступает на управляющий вход видеусилителя 7.4 для автоматического управления коэффициентом усиления видеоусилителя 7.4 при слабом уровне входного цифрового сигнала, этим обеспечивая линейность всего тракта приема цифрового сигнала. В фильтре нижних частот 7.5 происходит выделение полезного цифрового сигнала и эффективное подавление побочных комбинационных составляющих цифрового сигнала. С выхода фильтра нижних частот 7.5 цифровой сигнал поступает на вход решающего блока 8.

Решающий блок 8 восстанавливает исходную форму и амплитуду сигнала, а также его временное расположение на тактовом интервале. При этом решение в решающем блоке 8 принимается с нулевым пороговым значением, то есть по закону напряжения на выходе фильтра нижних частот.

Таким образом, предлагаемое устройство для приема четверично-кодированных последовательностей обеспечивает расширение области применения благодаря повышению помехоустойчивости цифрового оптического сигнала или увеличения длины регенерационного участка волоконно-оптической линии передачи за счет когерентной свертки на оптическом уровне сложного сигнала для волоконно-оптических систем связи в качестве приема дискретной информации и синхронизации.

Вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного устройства следующей совокупности условий:

- средство, воплощающее заявленное устройство при его осуществлении, предназначено для использования в волоконно-оптических системах связи в качестве приема дискретной информации и синхронизации;

- для заявленного устройства в том виде, как оно охарактеризовано в формуле изобретения, подтверждена возможность его осуществления с помощью описанных в заявке или известных до даты приоритета средств и методов;

- средство, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Таким образом, заявленное изобретение соответствует критерию "промышленная применяемость".

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема четвертично-кодированных последовательностей | 1990 |

|

SU1721837A1 |

| ЛИНИЯ ПЕРЕДАЧИ ВЫСОКОСКОРОСТНОГО ЦИФРОВОГО ОПТИЧЕСКОГО СИГНАЛА | 2003 |

|

RU2247473C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2020 |

|

RU2740001C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2001 |

|

RU2188516C1 |

| ЛИНИЯ ПЕРЕДАЧИ ЦИФРОВОГО ОПТИЧЕСКОГО СИГНАЛА | 2005 |

|

RU2286647C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2006 |

|

RU2320084C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2004 |

|

RU2268550C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2006 |

|

RU2315428C9 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДИАГРАММ НАПРАВЛЕННОСТИ АНТЕННЫ В ДАЛЬНЕЙ ЗОНЕ | 1992 |

|

RU2082985C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2005 |

|

RU2305368C2 |

Изобретение относится к радиотехнике и может быть использовано в волоконно-оптических системах связи. Технический результат заключается в повышении помехоустойчивости или увеличения длины регенерационного участка волоконно-оптической линии передачи. Сущность изобретения заключается в том, что устройство содержит коммутатор, k-1 блоков задержки, разветвитель, многоотводную линию задержки, k-1 преобразователей импульсной последовательности, знакозадающий блок, блок обработки оптического сигнала и решающий блок. 2 з.п. ф-лы, 6 ил.

| Устройство для приема четвертично-кодированных последовательностей | 1990 |

|

SU1721837A1 |

| Устройство для формирования многопозиционно-кодированных последовательностей | 1986 |

|

SU1336249A1 |

| SU 1177910 A, 07.09.1985 | |||

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КОРРЕСПОНДЕНТОВ | 1991 |

|

RU2012143C1 |

| JP 54104216, 16.08.1979. | |||

Авторы

Даты

2006-04-10—Публикация

2004-08-09—Подача