(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА ЧЕТВЕРИЧНО-КОДИРОВАННЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2004 |

|

RU2273961C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2020 |

|

RU2740001C1 |

| УСТРОЙСТВО СВЯЗИ | 1997 |

|

RU2116700C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2004 |

|

RU2268550C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2001 |

|

RU2188516C1 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Устройство для преобразования по функциям Уолша | 1986 |

|

SU1383393A1 |

| Устройство для формирования ортогональных последовательностей | 1977 |

|

SU661733A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2006 |

|

RU2320084C1 |

Изобретение относится к радиотехнике и может найти применение в системах передачи информации, синхронизации и радиолокации. Целью изобретения является увеличение числа принимаемых последовательностей. Устройство содержит коммутатор, блоки задержки, демодулятор, многоотводную линию задержки, вычислитель, решающий блок, преобразователи им- пульсной последовательности и знакозадающий блок. На выходе решающего блока в процессе приема четвертичной последовательности формируется напряжение, пропорциональное автокорреляционной функции этой последовательности при условии, что по первым установочным входам знакозадающие блоки включены по номеру соответствующего D-кода, а по вторым установочным входам линия задержки и элементы задержки включены по номеру соответствующей функции Радемахера. 4 ил.

Изобретение относится к радиотехнике и может найти применение в системах передачи информации, синхронизации и радиолокации.

Целью изобретения является увеличение числа принимаемых последовательностей.

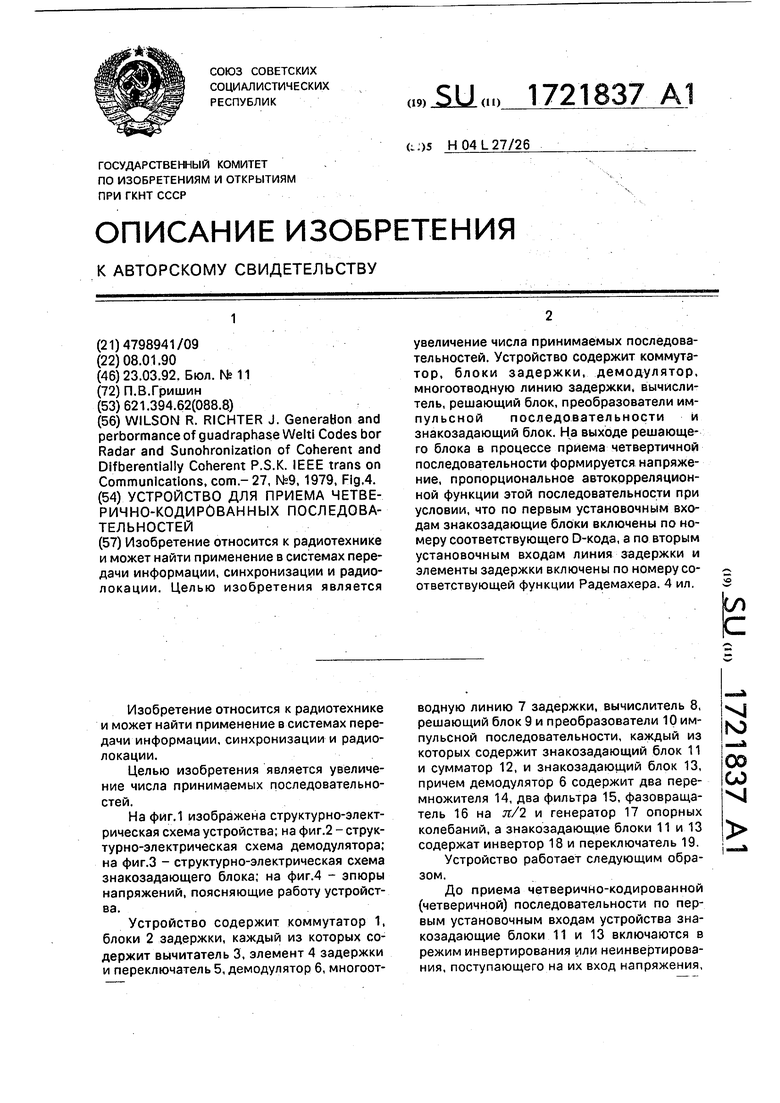

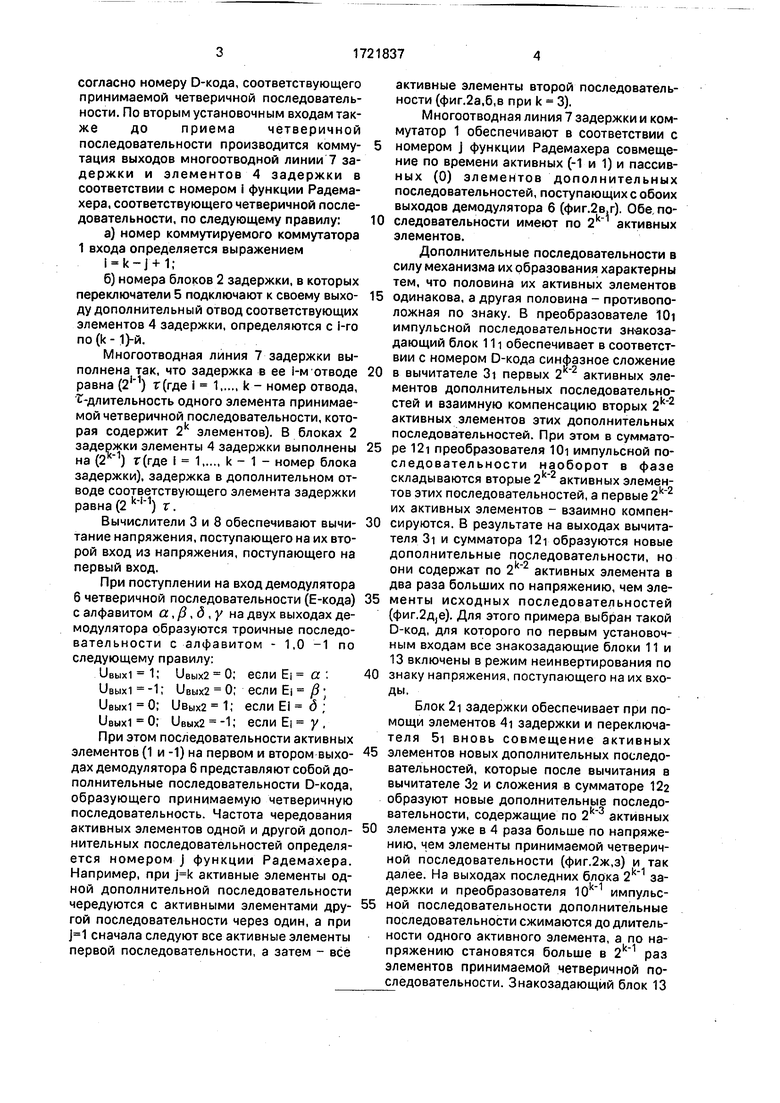

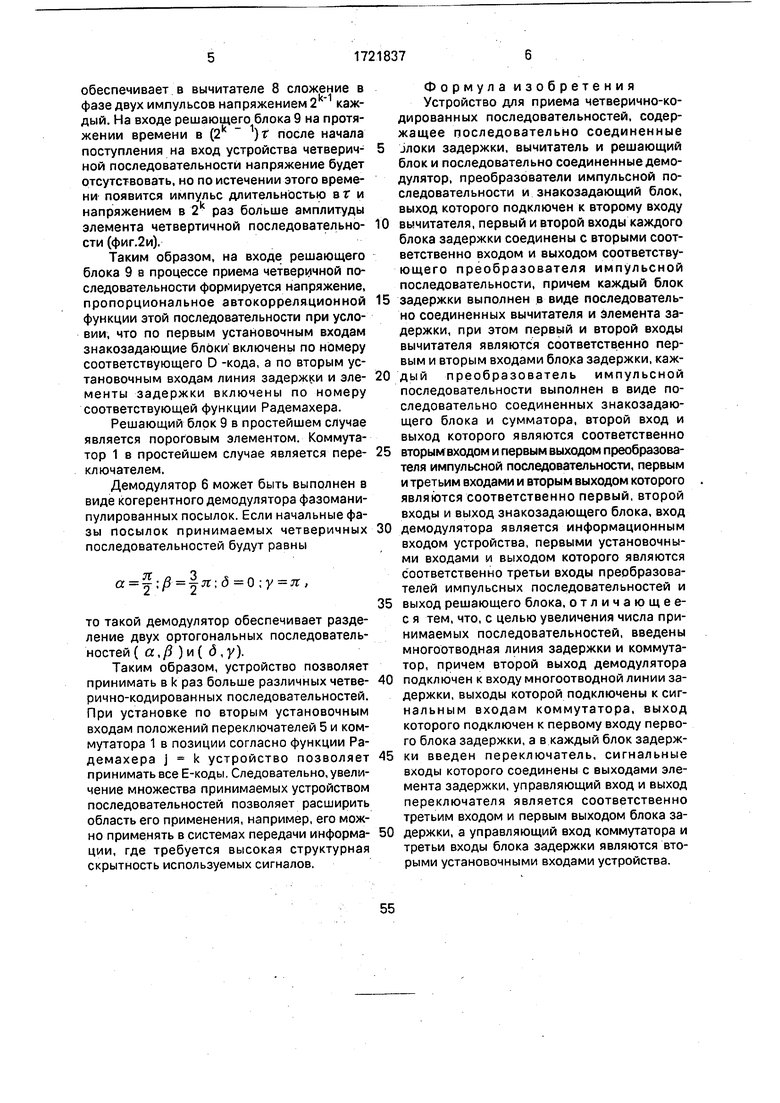

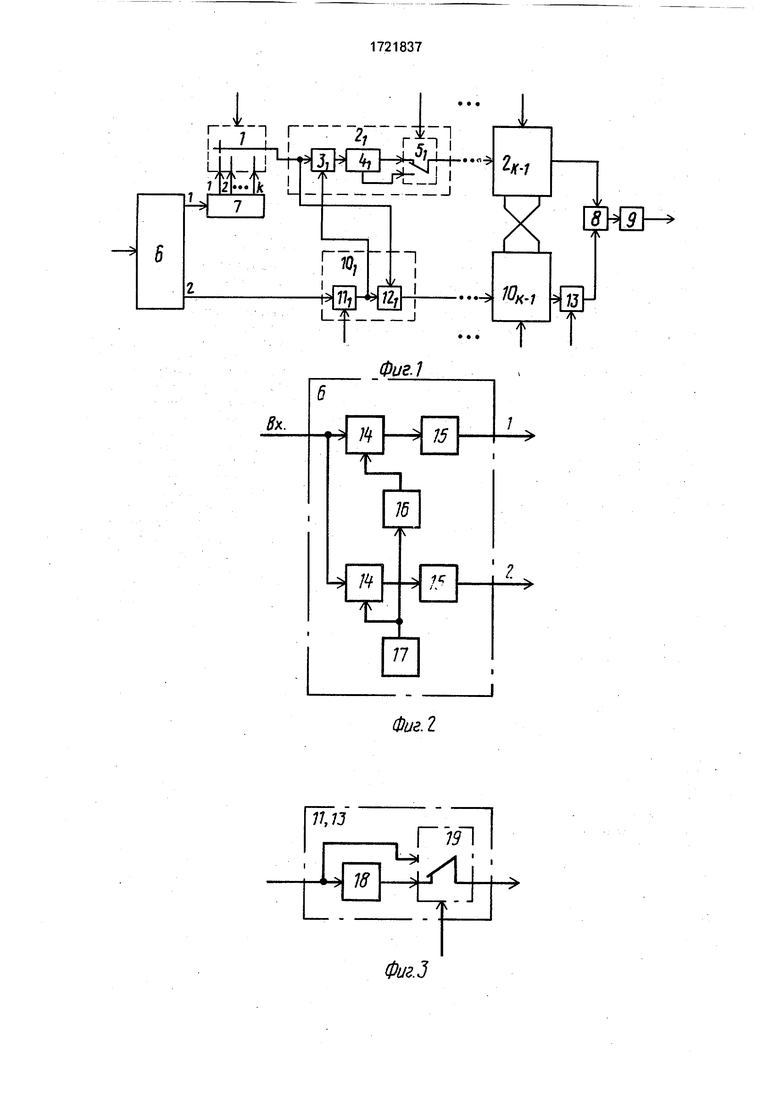

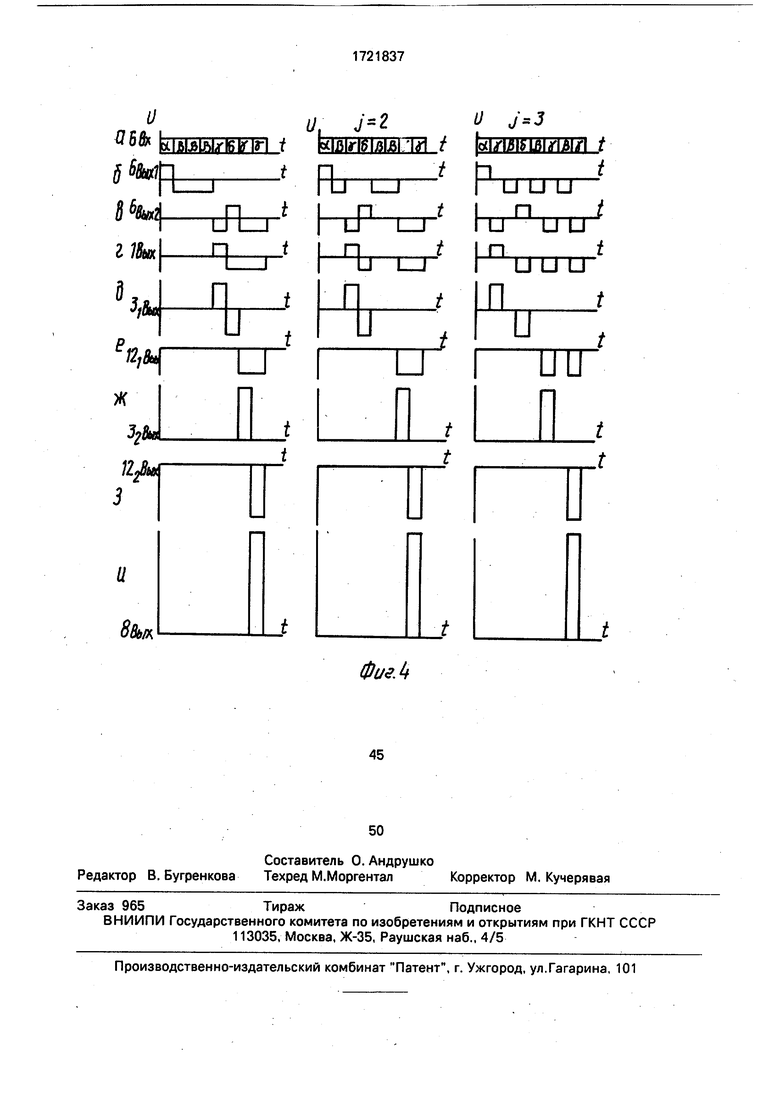

На фиг.1 изображена структурно-электрическая схема устройства; на фиг.2 - структурно-электрическая схема демодулятора; на фиг.З - структурно-электрическая схема знакозадающего блока; на фиг.4 - эпюры напряжений, поясняющие работу устройства.

Устройство содержит коммутатор 1, блоки 2 задержки, каждый из которых содержит вычитатель 3, элемент 4 задержки и переключатель 5, демодулятор 6, многоотводную линию 7 задержки, вычислитель 8, решающий блок 9 и преобразователи 10 импульсной последовательности, каждый из которых содержит знакозадающий блок 11 и сумматор 12, и знакозадающий блок 13, причем демодулятор 6 содержит два перемножителя 14, два фильтра 15, фазовращатель 16 на тг/2 и генератор 17 опорных колебаний, а знакозадающие блоки 11 и 13 содержат инвертор 18 и переключатель 19.

Устройство работает следующим образом.

До приема четверично-кодированной (четверичной) последовательности по первым установочным входам устройства знакозадающие блоки 11 и 13 включаются в режим инвертирования или неинвертирования, поступающего на их вход напряжения,

VI

ГО

00 СА VI

согласно номеру D-кода, соответствующего принимаемой четверичной последовательности. По вторым установочным входам также до приема четверичной последовательности производится коммутация выходов многоотводной линии 7 задержки и элементов 4 задержки в соответствии с номером i функции Радема- хера, соответствующего четверичной последовательности, по следующему правилу:

а)номер коммутируемого коммутатора 1 входа определяется выражением

i k-j + 1;

б)номера блоков 2 задержки, в которых переключатели 5 подключают к своему выходу дополнительный отвод соответствующих элементов 4 задержки, определяются с i-ro по (k - 1)-й.

Многоотводная линия 7 задержки выполнена так, что задержка в ее i-м отводе

равна (2м) Т (где i 1k - номер отвода,

-длительность одного элемента принимаемой четверичной последовательности,которая содержит 2 элементов). В блоках 2 задержки элементы 4 задержки выполнены на () г (где i 1,..., k - 1 - номер блока задержки), задержка в дополнительном отводе соответствующего элемента задержки равна (2 ) т.

Вычислители 3 и 8 обеспечивают вычитание напряжения, поступающего на их второй вход из напряжения, поступающего на первый вход.

При поступлении на вход демодулятора 6 четверичной последовательности (Е-кода) с алфавитом а, /3, д , у на двух выходах демодулятора образуются троичные последовательности с алфавитом - 1,0 -1 по следующему правилу:

ивых1 1; 1)Вых2 0; если Е а :

иВых1 -1; ивых2 0; если EJ /3;

11вых1 0; Квых2 1; если Ei 6 ;

ивых1 0; ивых2 -1; если у.

При этом последовательности активных элементов (1 и -1) на первом и втором выходах демодулятора 6 представляют собой дополнительные последовательности D-кода, образующего принимаемую четверичную последовательность. Частота чередования активных элементов одной и другой дополнительных последовательностей определяется номером j функции Радемахера. Например, при активные элементы одной дополнительной последовательности чередуются с активными элементами другой последовательности через один, а при сначала следуют все активные элементы первой последовательности, а затем - все

активные элементы второй последовательности (фиг.2а,б,в при k 3).

Многоотводная линия 7 задержки и коммутатор 1 обеспечивают в соответствии с

номером j функции Радемахера совмещение по времени активных (-1 и 1) и пассивных (0) элементов дополнительных последовательностей, поступающих с обоих выходов демодулятора 6 (фиг.2в.г). Обе,по0 следовательности имеют по 2 активных элементов.

Дополнительные последовательности в силу механизма их образования характерны тем, что половина их активных элементов

5 одинакова, а другая половина - противоположная по знаку. В преобразователе 10i импульсной последовательности знакоза- дающий блок 11i обеспечивает в соответствии с номером D-кода синфазное сложение

0 в вычитателе 3i первых активных элементов дополнительных последовательностей и взаимную компенсацию вторых активных элементов этих дополнительных последовательностей. При этом в суммато5 ре 12i преобразователя 10i импульсной последовательности наоборот в фазе складываются вторые активных элементов этих последовательностей, а первые их активных элементов - взаимно компен0 сируются. В результате на выходах вычита- теля 3i и сумматора 12i образуются новые дополнительные последовательности, но они содержат по активных элемента в два раза больших по напряжению, чем эле5 менты исходных последовательностей (фиг.2д)е). Для этого примера выбран такой D-код, для которого по первым установочным входам все знакозадающие блоки 11 и 13 включены в режим неинвертирования по

0 знаку напряжения, поступающего на их входы.

Блок 2ч задержки обеспечивает при помощи элементов 4i задержки и переключателя 5i вновь совмещение активных

5 элементов новых дополнительных последовательностей, которые после вычитания в вычитателе 32 и сложения в сумматоре 122 образуют новые дополнительные последовательности, содержащие по активных

0 элемента уже в 4 раза больше по напряжению, чем элементы принимаемой четверичной последовательности (фиг.2ж,з) и так далее. На выходах последних блока задержки и преобразователя импульс5 ной последовательности дополнительные последовательности сжимаются до длительности одного активного элемента, а по напряжению становятся больше в раз элементов принимаемой четверичной последовательности. Знакозадающйй блок 13

обеспечивает в вычитателе 8 сложение в фазе двух импульсов напряжением каждый. На входе решающего блока 9 на протяжении времени в (2k )г после начала поступления на вход устройства четверичной последовательности напряжение будет отсутствовать, но по истечении этого времени появится импульс длительностью в Г и напряжением в 2k раз больше амплитуды элемента четвертичной последовательности (фиг.2и).

Таким образом, на входе решающего блока 9 в процессе приема четверичной последовательности формируется напряжение, пропорциональное автокорреляционной функции этой последовательности при условии, что по первым установочным входам знакозадающие блоки включены по номеру соответствующего D -кода, а по вторым установочным входам линия задержки и элементы задержки включены по номеру соответствующей функции Радемахера.

Решающий блок 9 в простейшем случае является пороговым элементом. Коммутатор 1 в простейшем случае является переключателем.

Демодулятор 6 может быть выполнен в виде когерентного демодулятора фазомани- пулированных посылок. Если начальные фазы посылок принимаемых четверичных последовательностей будут равны

а Ј;Д ,

то такой демодулятор обеспечивает разделение двух ортогональных последовательностей ( a,fi )и( (5,у).

Таким образом, устройство позволяет принимать в к раз больше различных четве- рично-кодированных последовательностей. При установке по вторым установочным входам положений переключателей 5 и коммутатора 1 в позиции согласно функции Радемахера j k устройство позволяет принимать все Е-коды. Следовательно, увеличение множества принимаемых устройством последовательностей позволяет расширить область его применения, например, его можно применять в системах передачи информации, где требуется высокая структурная скрытность используемых сигналов.

Формула изобретения Устройство для приема четверично-ко- дированных последовательностей, содержащее последовательно соединенные

локи задержки, вычитатель и решающий блок и последовательно соединенные демодулятор, преобразователи импульсной последовательности и знакозадающий блок, выход которого подключен к второму входу

вычитателя, первый и второй входы каждого блока задержки соединены с вторыми соответственно входом и выходом соответствующего преобразователя импульсной последовательности, причем каждый блок

задержки выполнен в виде последовательно соединенных вычитателя и элемента задержки, при этом первый и второй входы вычитателя являются соответственно первым и вторым входами блока задержки, каждый преобразователь импульсной последовательности выполнен в виде последовательно соединенных знакозадаю- щего блока и сумматора, второй вход и выход которого являются соответственно

вторым входом и первым выходом преобразователя импульсной последовательности, первым и третьим входами и вторым выходом которого являются соответственно первый, второй входы и выход знакозадающего блока, вход

демодулятора является информационным входом устройства, первыми установочными входами и выходом которого являются соответственно третьи входы преобразователей импульсных последовательностей и

выход решающего блока, отличающее- с я тем, что, с целью увеличения числа принимаемых последовательностей, введены многоотводная линия задержки и коммутатор, причем второй выход демодулятора

подключен к входу многоотводной линии задержки, выходы которой подключены к сиг- нальным входам коммутатора, выход которого подключен к первому входу первого блока задержки, а в каждый блок задержки введен переключатель, сигнальные входы которого соединены с выходами элемента задержки, управляющий вход и выход переключателя является соответственно третьим входом и первым выходом блока задержки, а управляющий вход коммутатора и третьи входы блока задержки являются вторыми установочными входами устройства.

Фиг.З

Аи.

j

и y-j

ФиеЛ

| WILSON R | |||

| RICHTER J | |||

| Generation and perbormanceof guadraphase Welti Codes bor Radar and Synchronization of Coherent and Difberentially Coherent P.S.K | |||

| IEEE trans on Communications, com.-27, №9, 1979, FigA |

Авторы

Даты

1992-03-23—Публикация

1990-01-08—Подача