Изобретение относится к интегральной микроэлектронике и может быть использовано в системах обработки оптической информации.

Фотосигналы с многоэлементных датчиков, в частности, для инфракрасных фотоприемных устройств (ИК ФПУ), особенно в среднем и дальнем ИК диапазоне, характеризуются низкой контрастностью изображения, высоким уровнем "геометрического" шума. Поэтому неотъемлемой частью современных многоэлементных ИК ФПУ третьего поколения является реализация функционально полных систем, включающих в себя предпроцессорную обработку информации с многоэлементных датчиков в цифровой форме (L.J.Kozlowski, К.Vural at all. Progress toward high-performance infrared imaging systems-on-a chip. Proceeding of SPIE, vol.4130 (2000), p.245-253).

Известно многоканальное устройство считывания (а.с. СССР №1702829, МПК: 6 Н 01 L 29/768), выполненное на полупроводниковой подложке, содержащее многовыходной коммутатор, линейку N усилителей, общую шину считывания, шину записи, блок предпроцессорной обработки сигналов с сигнальным входом и компенсирующим выходом.

Недостаток известного устройства заключается в ограничении динамического диапазона, быстродействия, ограничение функциональных возможностей предпроцессорной обработки сигналов. Недостаток обусловлен тем, что информационный сигнал и корректирующее напряжение передается в аналоговой форме и привязано к данному конкретному устройству считывания, а также предпроцессорной обработкой сигнала в аналоговой форме, последовательным преобразованием аналогового сигнала в цифровой.

Ближайшим техническим решением к заявляемому является многоканальное устройство считывания (И.И.Ли, М.В.Попов. Многовходовый процессор с адаптивными устройствами предпроцессорной обработки сигналов для многоэлементных датчиков. Автометрия, №6, 1997 г., стр.20-25), выполненное на полупроводниковой подложке, содержащее N входных узлов, многовыходной коммутатор, общую шину считывания, шину записи, блок предпроцессорной обработки сигналов, содержащий компаратор, арифметико-логическое устройство, блок памяти, причем из двух входов компаратора, один предназначен для подачи на него сигнала в цифровом коде и соединен с общей шиной считывания, а другой вход компаратора предназначен для подачи опорного сигнала, выход компаратора соединен с входом арифметико-логического устройства, выход которого соединен с входом блока памяти, а выход блока памяти связан с шиной записи, каждый входной узел выполнен в виде усилителя, имеющего вход, выход и управляющий вход, двух МДП-транзисторов, при этом затвор первого МДП-транзистора соединен с выходом соответствующей ячейки многовыходного коммутатора, а сток - с общей шиной считывания, затвор второго МДП-транзистора соединен с выходом следующей ячейки многовыходного коммутатора, а сток - с шиной записи. Исток первого МДП-транзистора соединен с выходом усилителя, а исток второго МДП-транзистора соединен с управляющим входом усилителя. Усилитель выполнен на основе блока ввода с прямой инжекцией на приборах с зарядовой связью и соединенных с ним трех МДП-транзисторов. Блок предпроцессорной обработки сигналов кроме вышеуказанных элементов содержит цифроаналоговый преобразователь (ЦАП), через который выход блока памяти связан с шиной записи, при этом выход блока памяти дополнительно связан с арифметико-логическим устройством. Один из входов компаратора, служащий для подачи сигнала в цифровом коде, соединен с общей шиной считывания через последовательно связанные аналого-цифровой преобразователь (АЦП), узел двойной коррелированной выборки и предусилитель.

Данное известное устройство работает следующим образом. Вход усилителя подключают к датчикам. Многовыходной коммутатор обеспечивает последовательное подключение выходов усилителя через первый МДП-транзистор на общую шину считывания. Сигнал в аналоговой форме поступает на вход АЦП, с выхода АЦП - на компаратор. На второй вход компаратора поступает опорный код. В зависимости от соотношения информационного сигнала и опорного кода на выходе компаратора будут сформированы коды: +1 при Uсиг<Uоп; -1 при Uсиг>Uоп; 0 при Uсиг=Uоп. При коде +1 информация в i-той ячейке блока памяти (ОЗУ) увеличивается на дискрету младшего разряда ОЗУ, а при коде -1 - уменьшается. В следующем такте при считывании информационного сигнала с i+1 ячейки усилителя (входного узла) откорректированное значение напряжения i-той ячейки усилителя, через шину записи и вторые МДП-транзисторы поступает в аналоговой форме на управляющий вход i-того усилителя, который хранит его в аналоговом виде до следующего цикла считывания (коррекции). При постоянном сигнале максимально через 2n циклов считывания, где n - разрядность ОЗУ потенциалы на всех управляющих входах входных узлов будут сформированы таким образом, что выходные сигналы на общей шине считывания с точностью до младшего разряда АЦП будут равны опорному вне зависимости от вольтамперных характеристик присоединенных датчиков к входам усилителей и неоднородности передаточных характеристик усилителей. При этом в качестве датчиков могут быть, в частности, ИК фотоприемники.

Недостаток ближайшего технического решения заключается в ограничении динамического диапазона, быстродействия и функциональных возможностей. Ограничение динамического диапазона обусловлено тем, что информационный сигнал и корректирующее напряжение передается в аналоговой форме. Ограничение быстродействия связано с ограничением скорости передачи сигналов вследствие необходимости последовательного преобразования аналогового сигнала в цифровую форму. Ограничение функциональных возможностей обусловлено предпроцессорной обработкой сигналов в аналоговой форме.

Техническим результатом изобретения является расширение динамического диапазона, повышение быстродействия и расширение функциональных возможностей.

Технический результат достигается тем, что в многоканальном устройстве считывания, выполненном на полупроводниковой подложке, содержащем N входных узлов, многовыходной коммутатор, общую шину считывания, шину записи, блок предпроцессорной обработки сигналов, содержащий компаратор, арифметико-логическое устройство, блок памяти, причем из двух входов компаратора, один предназначен для подачи на него сигнала в цифровом коде и соединен с общей шиной считывания, а другой вход компаратора предназначен для подачи опорного сигнала, выход компаратора соединен с входом арифметико-логического устройства, выход которого соединен с входом блока памяти, а выход блока памяти связан с шиной записи, каждый входной узел выполнен в виде усилителя, имеющего вход, выход и управляющий вход, двух МДП-транзисторов, при этом затвор первого МДП-транзистора соединен с выходом соответствующей ячейки многовыходного коммутатора, а сток - с общей шиной считывания, затвор второго МДП-транзистора соединен с выходом следующей ячейки многовыходного коммутатора, а сток - с шиной записи, каждый входной узел дополнительно снабжен аналогово-цифровым преобразователем, имеющим разрядность К, цифроаналоговым преобразователем, имеющим разрядность L, исток первого МДП-транзистора соединен с выходом аналого-цифрового преобразователя, вход которого соединен с выходом усилителя, исток второго МДП-транзистора соединен с входом цифроаналогового преобразователя, выход которого соединен с управляющим входом усилителя, общая шина считывания выполнена из количества шин, равного разрядности аналого-цифрового преобразователя и количеству первых МДП-транзисторов, соединенных затворами с соответствующим выходом многовыходного коммутатора, стоками с соответствующими шинами общих шин считывания, истоками с соответствующими входами аналого-цифровых преобразователей, которое равно К, шина записи выполнена из количества шин, равного разрядности цифроаналогового преобразователя и количеству вторых МДП-транзисторов, соединенных стоками с соответствующими шинами, образующими шину записи, затворами - с выходом следующей ячейки многовыходного коммутатора, истоками - с соответствующими входами цифроаналогового преобразователя, которое равно L.

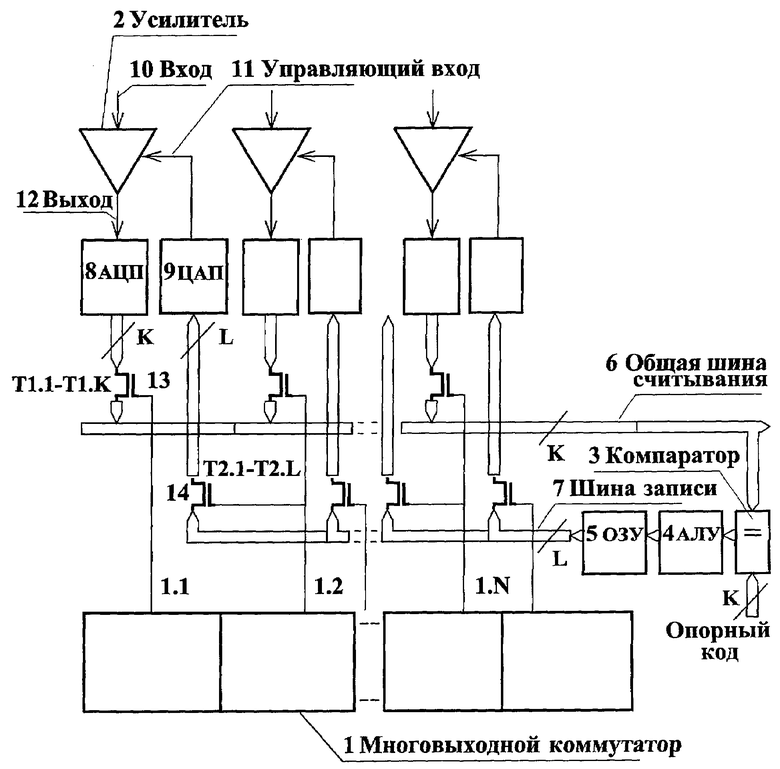

Сущность изобретения поясняется нижеследующим описанием и прилагаемым чертежом, на котором приведена принципиальная схема предлагаемого устройства считывания для двухмерных датчиков с адаптивной обработкой сигналов в цифровой форме, где 1 - многовыходной коммутатор, 2 - усилитель, 3 - компаратор, 4 - арифметико-логическое устройство (АЛУ), 5 - блок памяти (ОЗУ), 6 - общая шина считывания, 7 - шина записи, 8 - аналогово-цифровой преобразователь (АЦП), 9 - цифроаналоговый преобразователь (ЦАП), 10 - вход усилителя, 11 - управляющий вход усилителя, 12 - выход усилителя, 13 - первый МДП-транзистор, 14 - второй МДП-транзистор.

Предлагаемое многоканальное устройство считывания, также как и прототип, обеспечивает предпроцессорную обработку сигналов с многоэлементных датчиков в реальном масштабе времени, заключающуюся в вычитании индивидуально для каждого канала аддитивных компонент сигналов, которые для многоэлементных датчиков, как правило, являются неинформационными компонентами. При считывании информации с ИК фотоприемников в диапазоне длин волн 5-14 мкм неинформационные компоненты сигналов, обусловленные фоновым излучением, составляют от 80% до 90% от полного сигнала. Конструктивное решение предлагаемого устройства дает возможность отслеживать низкочастотные изменения характеристик датчиков, передаточных характеристик усилителей и т.д., таким образом, реализуя функцию фильтра высоких частот, причем с возможностью индивидуальной для каждого канала многоэлементного датчика адаптивной регулировки характеристик такого фильтра.

Дополнительная комплектация каждого входного узла АЦП и ЦАП (см. чертеж) решает задачу расширения динамического диапазона и чувствительности многоэлементных датчиков. Известно, что при создании систем цифровой обработки сигналов с многоэлементных датчиков наиболее проблемным в реализации узлом является аналого-цифровой преобразователь, которым и определяется динамический диапазон. Именно этот узел ограничивает разрядность цифровых систем обработки сигналов и, следовательно, динамический диапазон и чувствительность многоэлементных датчиков на их основе. Для многоэлементных ИК ФПУ, работающих в дальнем ИК диапазоне, необходим цифровой измерительный канал с числом разрядов не менее 16. До настоящего времени, даже при использовании самых современных кремниевых технологий для многоканальных устройств, при жестких ограничениях на занимаемую одной ячейкой устройства считывания площадь и потребляемую мощность не удается реализовать АЦП с разрядностью более 10 и получить требуемый динамический диапазон и чувствительность многоэлементных ИК ФПУ третьего поколения с сигналом на выходе в цифровой форме. В предлагаемом техническом решении данная задача решается тем, что полный динамический диапазон устройства определяется суммарной разрядностью АЦП и ЦАП. Как известно ЦАП значительно проще в реализации, чем АЦП.

Расширение динамического диапазона, как и повышение быстродействия, обусловлено тем, что конструктивное решение предлагаемого устройства в отличие от прототипа позволяет перейти от последовательного преобразования аналогового сигнала в цифровую форму к параллельному и передавать информационный сигнал и корректирующее напряжении не в аналоговой форме, а в цифровой. В результате скорость передачи сигналов по общей шине считывания и шине записи значительно увеличивается, повышается быстродействие многоканального устройства считывания. Это также расширяет функциональные возможности и область применения многоканального устройства считывания, поскольку они способствуют быстродействию различных ИК ФПУ на его основе.

Наконец, конструктивное решение предлагаемого устройства позволяет проводить предпроцессорную обработку сигналов в цифровой форме в отличие от известного технического решения. В результате имеет место существенное расширение функциональных возможностей различных ИК ФПУ, выполненных на основе предлагаемого многоканального устройства считывания. Например, введение по шине записи в цифровой форме сигналов, характеризующих изображение какого-либо объекта, дополнительно к аддитивным, вычитаемым из общего сигнала неинформационным компонентам, обеспечивает более широкие возможности систем распознавания образов.

Устройство считывания для двухмерных датчиков с адаптивной обработкой сигналов в цифровой форме выполнено на полупроводниковой подложке. Заявляемое устройство содержит конструктивные элементы: многовыходной коммутатор (1), усилитель (2), компаратор (3), арифметико-логическое устройство (АЛУ) (4), блок памяти (ОЗУ) (5), общую шину считывания (6), шину записи (7), аналогово-цифровой преобразователь (АЦП) (8), цифроаналоговый преобразователь (ЦАП) (9), первый МДП-транзистор (13), второй МДП-транзистор (14) (см. чертеж).

Усилитель (2), имеющий вход (10), выход (12), управляющий вход (11), аналогово-цифровой преобразователь (АЦП) (8), цифроаналоговый преобразователь (ЦАП) (9), первый МДП-транзистор (13), второй МДП-транзистор (14) образуют входной узел (ячейку усилителя). Устройство содержит N входных узлов (ячеек усилителя).

Компаратор (3), арифметико-логическое устройство (АЛУ) (4), блок памяти (ОЗУ) (5) образуют блок предпроцессорной обработки сигналов.

Многовыходной коммутатор имеет 1-(N+1) ячеек и 1.1-1.(N+1) выходов.

У каждого входного узла (ячейки усилителя) вход (10) усилителя (2) соединен с датчиком, выход (12) усилителя (2) связан с входом аналого-цифрового преобразователя (АЦП) (8) с разрядностью К, а управляющий вход (11) усилителя (2) - с выходом цифроаналогового преобразователя (ЦАП) (9) с разрядностью L. Исток первого МДП-транзистора (13) соединен с входом АЦП (8), выход которого соединен с выходом (12) усилителя (2), затвор соединен с соответствующим выходом многовыходного коммутатора (1), а сток, связан с соответствующей шиной считывания, составляющей общую шину считывания (6). Исток второго МДП-транзистора (14) связан с выходом ЦАП (9), вход которого связан с управляющим входом (11) усилителя (2), затвор связан с выходом следующей ячейки многовыходного коммутатора (1), а сток связан с соответствующей шиной записи, составляющей общую шину записи (7). Общая шина считывания (6) выполнена из количества шин, равного разрядности АЦП (8). Количество первых МДП-транзисторов (13) Т1.1÷Т1.К, соединенных затворами с выходом соответствующей ячейки многовыходного коммутатора (1), стоками с соответствующими шинами общих шин считывания (6), истоками с соответствующими входами АЦП (8), также равно К. Шина записи (7) выполнена из количества шин, равного разрядности ЦАП (9). Количество вторых МДП-транзисторов (14) T2.1÷T2.L, соединенных стоками с шиной записи (7), затворами - с выходом следующей ячейки многовыходного коммутатора (1), истоками - с соответствующими выходами ЦАП (9), также равно L.

Два входа компаратора (3) являются первым и вторым входами блока предпроцессорной обработки сигнала, первый из которых предназначен для подачи на него сигнала в цифровой форме, поступающего по общей шине считывания (6), а второй - для подачи опорного кода. Выход компаратора (3) связан с входом АЛУ (4), выход которого соединен с входом ОЗУ (5), выход ОЗУ (5), являющийся выходом блока предпроцессорной обработки сигналов, соединен с шиной записи (7).

В качестве конструктивных элементов предлагаемого многоканального устройства считывания могут быть использованы, например, элементы известного технического решения (И.И.Ли, М.В.Попов. Многовходовый процессор с адаптивными устройствами предпроцессорной обработки сигналов для многоэлементных датчиков. Автометрия, №6, 1997 г., стр.20-25).

Устройство работает следующим образом. Допустим на входы усилителей (2) подают сигналы с многоэлементных датчиков. Подачей управляющих напряжений на многовыходной коммутатор (1) на выходах 1.1÷1.N+1 формируют импульсы напряжений, последовательно открывающие первые и вторые МДП-транзисторы (13, 14). Усиленные сигналы с выходов (12) усилителей (2) подают на вход АЦП (8) и далее последовательно через первые МДП-транзисторы (13) Т1.1÷Т1.К сигналы в цифровой форме поразрядно поступают на общую шину считывания (6). Сигналы по общей шине считывания (6) поступают на один из входов компаратора (3). На другой вход компаратора (3) поступает постоянный опорный код. В зависимости от соотношения информационного сигнала и опорного кода на выходе компаратора (3) будут сформированы коды: +1 при Uсиг<Uоп; -1 при Uсиг>Uоп; 0 при Uсиг=Uоп. При коде +1 информация в i-той ячейке ОЗУ (5) увеличивается на дискрету младшего разряда ОЗУ, при коде -1 - уменьшается. В следующем такте при считывании информационного сигнала с i+1 ячейки усилителя (2) откорректированное значение соответствующей ячейки ОЗУ (5) для i-той ячейки усилителя (2) через шину записи (7) и вторые МДП-транзисторы (14) T2.1÷T2.L поступает на вход ЦАП (9) и далее в аналоговой форме на управляющий вход (11) i-того усилителя (2), который хранит его в аналоговом виде до следующего цикла считывания (коррекции). При постоянных сигналах на входах (10) усилителей (2), максимально через 2L циклов считывания, потенциалы на всех управляющих входах (11) входных узлов будут сформированы таким образом, что выходные сигналы на общей шине считывания (6) с точностью до младшего разряда АЦП (8) будут равны опорному, вне зависимости от вольтамперных характеристик присоединенных датчиков к входам усилителей (2) и неоднородности передаточных характеристик усилителей (2). В качестве датчиков могут быть, например, ИК фотоприемники.

Многоканальное устройство считывания может быть использовано для считывания сигналов с многоэлементных датчиков как линейчатого типа, так и двухмерных. При считывании информации с двухмерных датчиков многоканальное устройство считывания должно быть дополнено матрицей предусилителей, при этом на входы усилителей последовательно будут поступать сигналы со столбцовой шины считывания, то есть с разных строк и, следовательно, с разных датчиков. В этом случае необходимо изменить только формат ОЗУ. При считывании сигналов с двухмерной матрицы датчиков организация ОЗУ должна быть M×N×L, где М количество строк в двухмерной матрице датчиков. При считывании сигнала с (i+1, j) ячейки, где i номер элемента строки, j номер строки, на шину записи с ОЗУ должна поступать информация об элементе (i, j+1).

Положительным эффектом предлагаемого устройства считывания является расширение области применения.

Изобретение может быть использовано в системах обработки оптической информации. Техническим результатом является расширение динамического диапазона, повышение быстродействия и расширение функциональных возможностей. Сущность изобретения: в многоканальном устройстве считывания, выполненном на полупроводниковой подложке, содержащем N входных узлов, многовыходной коммутатор, общую шину считывания, шину записи, блок предпроцессорной обработки сигналов, содержащий компаратор, арифметико-логическое устройство, блок памяти, причем из двух входов компаратора один предназначен для подачи на него сигнала в цифровом коде и соединен с общей шиной считывания, а другой вход компаратора предназначен для подачи опорного сигнала, выход компаратора соединен с входом арифметико-логического устройства, выход которого соединен с входом блока памяти, а выход блока памяти связан с шиной записи, каждый входной узел выполнен в виде усилителя, имеющего вход, выход и управляющий вход, двух МДП-транзисторов, при этом затвор первого МДП-транзистора соединен с выходом соответствующей ячейки многовыходного коммутатора, а сток - с общей шиной считывания, затвор второго МДП-транзистора соединен с выходом следующей ячейки многовыходного коммутатора, а сток - с шиной записи, каждый входной узел дополнительно снабжен аналогово-цифровым преобразователем, имеющим разрядность К, цифроаналоговым преобразователем, имеющим разрядность L, исток первого МДП-транзистора соединен с выходом аналого-цифрового преобразователя, вход которого соединен с выходом усилителя, исток второго МДП-транзистора соединен с входом цифроаналогового преобразователя, выход которого соединен с управляющим входом усилителя, общая шина считывания выполнена из количества шин, равного разрядности аналого-цифрового преобразователя и количеству первых МДП-транзисторов, соединенных затворами с соответствующим выходом многовыходного коммутатора, стоками с соответствующими шинами общих шин считывания, истоками с соответствующими входами аналого-цифровых преобразователей, которое равно К, шина записи выполнена из количества шин, равного разрядности цифроаналогового преобразователя и количеству вторых МДП-транзисторов, соединенных стоками с соответствующими шинами, образующими шину записи, затворами - с выходом следующей ячейки многовыходного коммутатора, истоками - с соответствующими входами цифроаналогового преобразователя, которое равно L. 1 ил.

Многоканальное устройство считывания, выполненное на полупроводниковой подложке, содержащее N входных узлов, многовыходной коммутатор, общую шину считывания, шину записи, блок предпроцессорной обработки сигналов, содержащий компаратор, арифметико-логическое устройство, блок памяти, причем из двух входов компаратора один предназначен для подачи на него сигнала в цифровом коде и соединен с общей шиной считывания, а другой вход компаратора предназначен для подачи опорного сигнала, выход компаратора соединен с входом арифметико-логического устройства, выход которого соединен с входом блока памяти, а выход блока памяти связан с шиной записи, каждый входной узел выполнен в виде усилителя, имеющего вход, выход и управляющий вход, двух МДП-транзисторов, при этом затвор первого МДП-транзистора соединен с выходом соответствующей ячейки многовыходного коммутатора, а сток - с общей шиной считывания, затвор второго МДП-транзистора соединен с выходом следующей ячейки многовыходного коммутатора, а сток - с шиной записи, отличающееся тем, что каждый входной узел дополнительно снабжен аналогово-цифровым преобразователем, имеющим разрядность К, цифроаналоговым преобразователем, имеющим разрядность L, исток первого МДП-транзистора соединен с выходом аналого-цифрового преобразователя, вход которого соединен с выходом усилителя, исток второго МДП-транзистора соединен с входом цифроаналогового преобразователя, выход которого соединен с управляющим входом усилителя, общая шина считывания выполнена из количества шин, равного разрядности аналого-цифрового преобразователя и количеству первых МДП-транзисторов, соединенных затворами с соответствующим выходом многовыходного коммутатора, стоками с соответствующими шинами общих шин считывания, истоками с соответствующими входами аналого-цифровых преобразователей, которое равно К, шина записи выполнена из количества шин, равного разрядности цифроаналогового преобразователя и количеству вторых МДП-транзисторов, соединенных стоками с соответствующими шинами, образующими шину записи, затворами - с выходом следующей ячейки многовыходного коммутатора, истоками - с соответствующими входами цифроаналогового преобразователя, которое равно L.

| И.И | |||

| Ли, М.В | |||

| Попов | |||

| Многовходовый процессор с адаптивными устройствами предпроцессорной обработки сигналов для многоэлементных датчиков | |||

| Автометрия | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ | 1988 |

|

SU1702829A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ ДЛЯ ДВУМЕРНЫХ ПРИЕМНИКОВ ИЗОБРАЖЕНИЯ | 1993 |

|

RU2054753C1 |

| US 6129283 А, 10.10.2000. | |||

Авторы

Даты

2006-08-20—Публикация

2005-03-31—Подача