Техническое решение относится к области интегральной микроэлектроники и может быть использовано в системах обработки оптической информации.

Известно устройство считывания для многоэлементных фотоприемников инфракрасного излучения (Jehyuk Rhee and Youngjoong Joo, «Wide dynamic range CMOS image sensor with pixel level ADC», ELECTRONICS LETTERS, 20th February 2003, Vo. 39, No. 4, pp. 360-361) с многоканальной системой считывания в составе матрицы ячеек считывания, подключаемых к фотодиодам фотоприемника. Ячейка считывания подразделена на блок установки (reset block) и блок аналого-цифрового преобразования времени (TDC-block). В ячейке в блоке установки (reset block) выполнены интегрирующая емкость, компаратор, первый логический элемент, второй логический элемент, инвертор, первый и второй ключевые транзисторы, третий и четвертый ключевые транзисторы, пятый ключевой транзистор, шестой ключевой транзистор, управляющую шину Vreset, управляющую шину ref, управляющую шину ϕ1, управляющую шину ϕ2, управляющую шину Global reset, а в блоке аналого-цифрового преобразования времени (TDC-block) выполнены третий логический элемент, N разрядная ячейка памяти, седьмой ключевой транзистор, управляющая шина preset, управляющая шина read. Компаратор выполнен с двумя входами и одним выходом, первый логический элемент - с одним входом и одним выходом, второй логический элемент - с одним входом и одним выходом, инвертор - с двумя входами и одним выходом. Образующие пару первый и второй ключевые транзисторы соединены затворами соответственно с управляющей шиной ϕ1 и управляющей шиной ϕ2, стоками соединены друг с другом и подключены соединенными стоками к одному из входов инвертора, исток первого ключевого транзистора подключен к выходу первого логического элемента. Образующие пару третий и четвертый ключевые транзисторы соединены друг с другом стоками и истоками, затвор третьего ключевого транзистора соединен с управляющей шиной Global reset, соединенные истоки подключены к управляющей шине Vreset, соединенные стоки - к эмиттеру фотодиода, затвор четвертого ключевого транзистора соединен с выходом второго логического элемента. Вход второго логического элемента соединен со стоком пятого ключевого транзистора, исток которого соединен с выходом инвертора, а затвор - с управляющей шиной ϕ1. Вход первого логического элемента соединен с эмиттером фотодиода. К эмиттеру фотодиода подключен истоком шестой ключевой транзистор, сток которого соединен с одной обкладкой интегрирующей емкости, а затвор - с управляющей шиной ϕ1. Соединенной со стоком шестого ключевого транзистора обкладкой интегрирующая емкость подключена к одному из входов компаратора. Другой вход компаратора соединен с управляющей шиной ref. Третий логический элемент выполнен с двумя входами и одним выходом, N разрядная ячейка памяти - с двумя входами. Седьмой ключевой транзистор истоком соединен с выходом инвертора, стоком - с входом третьего логического элемента, а затвором - с выходом третьего логического элемента. Второй вход третьего логического элемента соединен с управляющей шиной preset. Выход третьего логического элемента соединен с одним из входов N разрядной ячейки памяти, второй вход которой подключен к управляющей шине read.

Управляющая шина ϕ1 выполнена с возможностью подачи импульса напряжения с длительностью, определяющей время накопления фотосигнала - длительностью первой фазы, а управляющая шина ϕ2 - с возможностью подачи импульса напряжения с длительностью, определяющей отсутствие накопления фотосигнала за счет изолирования фотодиода от входа компаратора, к которому он подключен своим эмиттером, - длительностью второй фазы. Управляющая шина Global reset выполнена с возможностью подачи короткого импульса напряжения относительно временного промежутка между началом первой фазы и окончанием второй фазы, приводящего по окончанию его к установлению на фотодиоде и интегрирующей емкости напряжения, подаваемого с управляющей шины Vreset. Управляющая шина ref выполнена с возможностью подачи на второй вход компаратора короткого импульса напряжения с его началом, совпадающим с падением напряжения на управляющей шине ϕ1, и окончанием, совпадающим с подачей напряжения на управляющей шине ϕ2, далее с равномерным увеличением напряжения с нулевого значения до значения Vreset на протяжении средней части временного промежутка отсутствия накопления фотосигнала, с последующим сохранением значения Vreset до окончания подачи импульса напряжения с длительностью, определяющей отсутствие накопления фотосигнала за счет изолирования фотодиода от входа компаратора, к которому он подключен своим эмиттером, и падением до нуля в момент окончания.

Управляющая шина preset выполнена с возможностью подачи двух коротких импульсов, с начало и окончание первого, совпадающими с началом и окончанием импульса управляющей шины Global reset, с длительностью второго импульса, равной длительности первого, с подачей его в момент равномерного увеличения напряжения с нулевого значения до значения Vreset на управляющей шине ref. Управляющая шина read выполнена с возможностью подачи сигнала считывания.

Устройство выполнено на полупроводниковой подложке.

Известное устройство не обеспечивает возможности для улучшения пространственного разрешения и снижения потребляемой мощности при работе устройства считывания в двух режимах - режиме формирования тепловизионного изображения и в режиме формирования трехмерного изображения. Устройство не может быть использовано для работы в двух указанных режимах. Невозможно определение дальности до объектов в одном кадре одновременно с получением тепловизионного изображения. Устройство считывания основано на истоковом повторителе. При работе устройства существует необходимость подавать высокое напряжение смещения на фотодиоды фотоприемника. Это обстоятельство является критичным для использования в многоэлементных фотоприемниках инфракрасного излучения.

В качестве ближайшего аналога взято устройство считывания для многоэлементных фотоприемников инфракрасного излучения (описание к патенту РФ №2529768 на изобретение, МПК: G06E 1/00, H01L 27/14 (2006.01)) с многоканальной системой считывания в составе матрицы ячеек считывания, в каждой из которых реализованы канал формирования тепловизионного изображения и канал формирования трехмерного изображения. Канал формирования тепловизионного изображения реализован на основе трансимпедансного усилителя, выход которого соединен с первой столбцовой шиной считывания, передающей фотосигнал в аналоговой форме на вход предусилителя ячейки мультиплексора. Канал формирования трехмерного изображения реализован из указанного трансимпедансного усилителя, фильтра высоких частот, усилителя, компаратора, N-разрядного счетчика, логического элемента «И», первой и второй строчных шин управления, второй столбцовой шиной считывания, третьей столбцовой шиной считывания.

Управляющий вход трансимпедансного усилителя соединен с второй строчной шиной управления, инвертирующий вход предназначен для соединения с фотодиодом, а неинвертирующий вход предназначен для подачи постоянного напряжения, определяющего напряжение смещения на фотодиоде. Вторая строчная шина управления соединена с выходом управляемого M-разрядного строчного счетчика, вход которого соединен с первой строчной шиной управления. Кроме того, выход трансимпедансного усилителя соединен с входом фильтра высокой частоты, выход которого соединен с входом усилителя. Выход усилителя связан с инвертирующим входом компаратора, а неинвертирующий вход компаратора предназначен для подачи постоянного напряжения смещения. Выход компаратора соединен со счетным входом выполненного в ячейке считывания N-разрядного счетчика и с инвертирующим входом выполненного в ячейке считывания логического элемента «И». Неинвертирующий вход логического элемента «И» соединен с управляющим входом N-разрядного счетчика и с первой строчной шиной управления. Выход N-разрядного счетчика соединен с второй столбцовой шиной считывания, предназначенной для передачи информации для формирования трехмерного изображения - информации о дальности до объектов изображения. Выход логического элемента «И» соединен с третьей столбцовой шиной считывания, предназначенной для определения времени прихода отраженного импульса лазерной подсветки в промежутке между i и i+1 импульсами, поступающими по первой строчной шине управления.

Первая и вторая строчные шины управления, управляемый M-разрядный строчный счетчик выполнены общими в отношении строк ячеек считывания. Первая, вторая и третья столбцовые шины считывания выполнены общими в отношении столбца ячеек считывания. Вторая строчная шина управления выполнена как M-разрядная строчная шина управления, вторая столбцовая шина считывания выполнена как N-разрядная столбцовая шина считывания. Третья столбцовая шина считывания выполнена с возможностью соединения с одним входом логического элемента «И» ячейки мультиплексора, другой вход которого соединен с первой строчной шиной управления, которая выполнена распараллеленной, выход логического элемента «И» ячейки мультиплексора соединен с второй M-разрядной выходной шиной мультиплексора, вторая столбцовая шина считывания выполнена с возможностью соединения с третьей N-разрядной выходной шиной мультиплексора, первая столбцовая шина считывания выполнена с возможностью соединения с входом канала считывания ячейки мультиплексора, выход которого соединен с первой выходной шиной мультиплексора.

Трансимпедансный усилитель выполнен в составе операционного усилителя, емкости, одна из обкладок которой соединена с инвертирующим входом операционного усилителя, являющимся инвертирующим входом трансимпедансного усилителя, а другая обкладка - с выходом операционного усилителя, являющимся выходом трансимпедансного усилителя, ключа, одним выходом соединенного с инвертирующим входом операционного усилителя, а другим выходом - с выходом операционного усилителя, и управляющим входом, соединенным с второй строчной шиной управления и являющимся управляющим входом трансимпедансного усилителя, с возможностью подачи на неинвертирующий вход операционного усилителя, являющегося неинвертирующим входом трансимпедансного усилителя, постоянного напряжения, определяющего напряжение смещения на фотодиоде, инвертирующий вход предназначен для соединения с фотодиодом. Кроме того, как правило, в трансимпедансном усилителе дополнительно реализованы в цепи обратной связи две емкости с величиной одной из них существенно большей величины второй, а также дополнительный ключ, обеспечивающий поочередную работу трансимпедансного усилителя в отношении указанных дополнительных емкостей.

Известное устройство не обеспечивает возможности для улучшения пространственного разрешения и снижения потребляемой мощности при работе устройства считывания в двух режимах - режиме формирования тепловизионного изображения и в режиме формирования трехмерного изображения. Причины заключаются в следующем.

Во-первых, устройство при формировании тепловизионного изображения обеспечивает передачу фотосигналов в мультиплексор по столбцовой шине считывания только в аналоговой форме.

Во-вторых, в составе трансимпедансного усилителя необходимо наличие еще двух емкостей с величиной одной из них существенно большей величины второй, дополнительного ключа, а также для функционирования канала формирования тепловизионного изображения необходимо устройство выборки и хранения. В режиме формировании тепловизионного изображения используется емкость, величина которой существенно больше, в режиме формирования трехмерного изображения - вторая емкость.

В третьих, младшие разряды фотосигналов в канале формирования трехмерного изображения, как и в канале формирования тепловизионного изображения, передаются в мультиплексор по столбцовой шине считывания в аналоговой форме.

Таким образом, для известного устройства считывания характерно большое количество узлов (блоков) в его ячейке, относительно большие геометрические размеры последней, большое количество управляющих сигналов.

Техническим результатом решения является улучшение пространственного разрешения и снижения потребляемой мощности при работе устройства считывания в двух режимах - режиме формирования тепловизионного изображения и в режиме формирования трехмерного изображения.

Технический результат достигается устройством считывания для многоэлементных фотоприемников инфракрасного излучения, содержащим многоканальную систему считывания в составе матрицы ячеек считывания, содержащих фильтр высоких частот, компаратор, N-разрядный счетчик, причем в составе каждой ячейки считывания также выполнены емкостной трансимпедансный усилитель с интегрирующей емкостью, преобразователь времени в напряжение, логический блок и M-разрядная схема памяти, при этом емкостной трансимпедансный усилитель реализован с четырьмя входами и одним выходом, первый вход емкостного трансимпедансного усилителя предназначен для подключения к фотодиоду, второй вход емкостного трансимпедансного усилителя предназначен для подачи напряжения смещения, управляющего полосой пропускания емкостного трансимпедансного усилителя, третий вход емкостного трансимпедансного усилителя, предназначен для подачи напряжения, обеспечивающего сброс интегрирующей емкости, четвертый вход емкостного трансимпедансного усилителя, предназначен для подачи напряжения, обеспечивающего сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, интегрирующая емкость в емкостном трансимпедансном усилителе одной обкладкой соединена с его первым входом, а второй обкладкой - с его выходом, выход емкостного трансимпедансного усилителя соединен с первым из трех входов фильтра высокой частоты, второй и третий входы фильтра высокой частоты предназначены для подачи напряжений смещения, определяющих граничную частоту, выход фильтра высокой частоты соединен через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, с инвертирующим входом компаратора, указанный инвертирующий вход компаратора соединен с выходом преобразователя времени в напряжение через ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор, неинвертирующий вход компаратора предназначен для подачи управляющего сигнала, выход компаратора соединен с первым входом логического блока, имеющего пять входов и три выхода, первый выход логического блока соединен с входом преобразователя времени в напряжение с возможностью подачи сигнала, разрешающего фиксацию текущего уровня напряжения в преобразователе времени в напряжение, второй вход логического блока предназначен для подачи сигнала, определяющего режим работы устройства, второй выход логического блока связан с четвертым входом емкостного трансимпедансного усилителя и предназначен для подачи на указанный вход напряжения, обеспечивающего сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, третий вход логического блока связан с шиной подачи сигнала, определяющего режим работы счетчика, третий выход логического блока связан со счетным входом N-разрядного счетчика с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком, четвертый вход логического блока связан с шиной подачи сигнала на сброс счетчика, пятый вход логического блока связан со столбцовой шиной подачи генерированных синхроимпульсов, преобразователь времени в напряжение выполнен с двумя входами и одним выходом, один из входов предназначен для подачи сигнала от логического блока, разрешающего фиксацию текущего уровня напряжения в преобразователе времени в напряжение, второй вход связан со столбцовой шиной подачи сигнала от генератора пилообразного сигнала, а выход связан с инвертирующим входом компаратора через ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор, N-разрядный счетчик выполнен с двумя входами и одним выходом, первый его вход связан с шиной подачи сигнала на сброс счетчика, второй, счетный, вход связан с третьим выходом логического блока с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком, выход N-разрядного счетчика связан с входом M-разрядной схемы памяти, второй и третий входы которой связаны соответственно со столбцовыми шинами считывания и записи, а выход M-разрядной схемы памяти соединен со строчной шиной выхода разрядностью N.

В устройстве N-разрядный счетчик и M-разрядная схема памяти выполнены соответственно N и М разрядными с N<M≤2N.

В устройстве в емкостном трансимпедансном усилителе с интегрирующей емкостью выполнены инвертирующий усилитель с двумя входами и одним выходом, являющимся выходом емкостного трансимпедасного усилителя, первый и второй ключи, каждый из которых выполнен с управляющим входом, один из входов инвертирующего усилителя выполнен в качестве первого входа емкостного трансимпедансного усилителя, второй вход - в качестве второго входа емкостного трансимпедансного усилителя, первый и второй ключи подключены к обкладкам интегрирующей емкости, управляющий вход первого ключа выполнен в качестве третьего входа емкостного трансимпедансного усилителя, с возможностью подачи на управляющий вход первого ключа напряжения, вызывающего его замыкание и обеспечивающего сброс емкости, а управляющий вход второго ключа выполнен в качестве четвертого входа емкостного трансимпедансного усилителя, с возможностью подачи на управляющий вход второго ключа напряжения, вызывающего его замыкание и обеспечивающего сброс емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя.

В устройстве фильтр высокой частоты выполнен в составе емкости и n-канального транзистора, который своим стоком подсоединен к одной из обкладок емкости с концом, являющимся выходом фильтра высокой частоты, соединенным через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, с инвертирующим входом компаратора, конец другой обкладки емкости, являющийся первым входом фильтра высокой частоты, соединен с выходом емкостного трансимпедансного усилителя, второй и третий входы фильтра высокой частоты, предназначенные для подачи напряжений смещения, определяющих граничную частоту, соединены соответственно с затвором и истоком n-канального транзистора, подложка n-канального транзистора выполнена с возможностью подачи на нее того же потенциала, что и на исток.

В устройстве фильтр высокой частоты выполнен в составе емкости и дифференциального усилителя, образованного первым и вторым p-канальными транзисторами, а также третьим, четвертым и пятым n-канальными транзисторами, подложки третьего, четвертого и пятого n-канальных транзисторов соединены с точкой «земли», подложки первого и второго p-канальных транзисторов выполнены с возможностью подачи потенциала на них, равного напряжению питания, истоки первого и второго p-канальных транзисторов соединены друг с другом с подачей на них напряжения питания, затворы первого и второго p-канальных транзисторов соединены друг с другом и подсоединены к стоку первого p-канального транзистора, сток первого p-канального транзистора соединен с истоком третьего n-канального транзистора, сток второго p-канального транзистора соединен с истоком четвертого n-канального транзистора и с его затвором, соединенные сток второго p-канального транзистора, исток четвертого n-канального транзистора и затвор n-канального транзистора подсоединены к одной из обкладок емкости с концом, являющимся выходом фильтра высокой частоты, соединенным через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, с инвертирующим входом компаратора, конец другой обкладки емкости, являющийся первым входом фильтра высокой частоты, соединен с выходом емкостного трансимпедансного усилителя, стоки третьего n-канального транзистора и четвертого n-канального транзистора соединены друг с другом и подсоединены к истоку пятого n-канального транзистора, сток пятого n-канального транзистора выполнен соединенным с точкой «земли», второй и третий входы фильтра высокой частоты, предназначенные для подачи напряжений смещения, определяющих граничную частоту, соединены соответственно с затвором третьего n-канального транзистора и затвором пятого n-канального транзистора.

В устройстве преобразователь времени в напряжение выполнен в составе емкости, заряжаемой линейно с течением времени, ключа, выполненного с управляющим входом, являющимся входом преобразователя времени в напряжение, предназначенным для подачи сигнала от логического блока, разрешающего фиксацию текущего уровня напряжения в преобразователе времени в напряжение, емкость одной обкладкой подсоединена к одному из концов указанного ключа, от подсоединения сформирован вывод, являющийся выходом преобразователя времени в напряжение, связанным с инвертирующим входом компаратора через ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор, вторая обкладка емкости соединена с точкой «земли», второй из концов указанного ключа, являющийся вторым входом преобразователя времени в напряжение, связан со столбцовой шиной подачи сигнала от генератора пилообразного сигнала.

В устройстве логический блок выполнен в составе RS-триггера, двух логических элементов «И-НЕ», логического элемента «И», двух мультиплексоров, характеризующихся одним адресным входом, двумя информационными входами и одним выходом, при этом вход S RS-триггера, являющийся первым входом логического блока, соединен с выходом компаратора, вход R RS-триггера выполнен как четвертый вход логического блока и связан с шиной подачи сигнала на сброс счетчика, инверсный выход RS-триггера соединен с одним из входов первого логического элемента «И-НЕ», второй вход которого выполнен как пятый вход логического блока, связанный со столбцовой шиной подачи генерированных синхроимпульсов, а инверсный выход первого логического элемента «И-НЕ» связан с первым информационным входом первого из мультиплексоров, нулевой информационный вход которого подключен к входу S RS-триггера, а адресный вход соединен с одним из входов второго логического элемента «И-НЕ», выход первого мультиплексора соединен с одним из входов логического элемента «И» и выполнен как третий выход логического блока, который связан со счетным входом N-разрядного счетчика с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком, вход второго логического элемента «И-НЕ», с которым соединен адресный вход первого мультиплексора, выполнен как третий вход логического блока, связанный с шиной подачи сигнала, определяющего режим работы счетчика, второй вход второго логического элемента «И-НЕ» выполнен как второй вход логического блока, предназначенный для подачи сигнала, определяющего режим работы устройства, инверсный выход второго логического элемента «И-НЕ» связан со вторым входом логического элемента «И», выход логического элемента «И» выполнен как второй выход логического блока, связанный с четвертым входом емкостного трансимпедансного усилителя и предназначенный для подачи на указанный вход напряжения, обеспечивающего сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, к инверсному выходу RS-триггера подсоединен первый информационный вход второго мультиплексора, адресный вход которого подсоединен к второму входу второго логического элемента «И-НЕ», который выполнен как второй вход логического блока, предназначенный для подачи сигнала, определяющего режим работы устройства, выход второго мультиплексора выполнен как первый выход логического блока, соединенный с входом преобразователя времени в напряжение с возможностью подачи сигнала, разрешающего фиксацию текущего уровня напряжения в преобразователе времени в напряжение, кроме того, логический блок снабжен дополнительным шестым входом, являющимся нулевым информационным входом второго мультиплексора, соединенным с точкой «земли».

В устройстве логический блок выполнен в составе RS-триггера, логического элемента «И-НЕ», трех мультиплексоров, характеризующихся одним адресным входом, двумя информационными входами и одним выходом, при этом вход S RS-триггера, являющийся первым входом логического блока, соединен с выходом компаратора, вход R RS-триггера выполнен как четвертый вход логического блока и связан с шиной подачи сигнала на сброс счетчика, инверсный выход RS-триггера соединен с одним из входов логического элемента «И-НЕ», второй вход которого выполнен как пятый вход логического блока, связанный со столбцовой шиной подачи генерированных синхроимпульсов, а инверсный выход связан с первым информационным входом первого из мультиплексоров, нулевой информационный вход первого мультиплексора подключен к входу S RS-триггера, а адресный вход соединен с адресным входом второго мультиплексора, при этом соединенные адресные входы первого и второго мультиплексоров выполнены как третий вход логического блока, связанный с шиной подачи сигнала, определяющего режим работы счетчика, выход первого мультиплексора выполнен как третий выход логического блока, который связан со счетным входом N-разрядного счетчика с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком, к выходу первого мультиплексора подсоединен нулевой информационный вход второго мультиплексора, выход второго мультиплексора, выполнен как второй выход логического блока, связанный с четвертым входом емкостного трансимпедансного усилителя и предназначенный для подачи на указанный вход напряжения, обеспечивающего сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, к инверсному выходу RS-триггера подсоединен первый информационный вход третьего мультиплексора, адресный вход которого выполнен как второй вход логического блока, предназначенный для подачи сигнала, определяющего режим работы устройства, выход третьего мультиплексора выполнен как первый выход логического блока, соединенный с входом преобразователя времени в напряжение с возможностью подачи сигнала, разрешающего фиксацию текущего уровня напряжения в преобразователе времени в напряжение, кроме того, логический блок снабжен дополнительным шестым входом, который образован соединенными первым информационным входом второго мультиплексора и нулевым информационным входом третьего мультиплексора, соединенными с точкой «земли».

В устройстве N-разрядный счетчик выполнен асинхронным со сбросом в составе N D-триггеров, входы сброса R всех D-триггеров соединены друг с другом, вход сброса первого D-триггера, являющийся первым входом N-разрядного счетчика, связан с шиной подачи сигнала на сброс счетчика, синхровход первого D-триггера, являющийся вторым, счетным, входом N-разрядного счетчика, связан с третьим выходом логического блока с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком, синхровход каждого последующего D-триггера соединен с выходом предыдущего D-триггера, выходы каждого из D-триггеров выполнены с возможностью формирования разряда числа с увеличением его веса, начиная с первого, образуя N-разрядный выход счетчика, информационный вход D каждого из D-триггеров соединен с его же инверсным выходом.

В устройстве каждый из D-триггеров выполнен в составе шести транзисторов, четырех инверторов, первый n-канальный транзистор истоком соединен с информационным входом D, стоком соединен с входом первого инвертора, выход которого соединен с входом второго инвертора, к стоку первого n-канального транзистора подсоединен исток второго n-канального транзистора, затвор которого соединен с входом сброса R, а сток соединен с точкой «земли», к соединенным стоку первого n-канального транзистора и истоку второго n-канального транзистора подсоединен исток третьего p-канального транзистора, сток которого соединен с выходом второго инвертора, а затвор соединен с затвором первого n-канального транзистора, исток четвертого p-канального транзистора подсоединен к стоку третьего p-канального транзистора, сток четвертого p-канального транзистора соединен с входом третьего инвертора, выход которого соединен с входом четвертого инвертора, кроме того, сток четвертого p-канального транзистора соединен с истоком пятого n-канального транзистора и истоком шестого n-канального транзистора, затвор пятого n-канального транзистора соединен с затвором второго n-канального транзистора, а сток пятого n-канального транзистора соединен с точкой «земли», затвор шестого n-канального транзистора соединен с затвором четвертого p-канального транзистора, соединенные затворы шестого n-канального транзистора и четвертого p-канального транзистора соединены с соединенными затворами первого n-канального транзистора и третьего p-канального транзистора с подключением к синхровходу D-триггера, сток шестого n-канального транзистора соединен с выходом четвертого инвертора с образованием прямого выхода D-триггера, а инверсный выход D-триггера выполнен в соединении выхода третьего инвертора с входом четвертого инвертора.

В устройстве каждый из инверторов выполнен в составе пары транзисторов - n-канального транзистора и p-канального транзистора, затворы транзисторов соединены друг с другом с подключением к входу инвертора, стоки транзисторов соединены друг с другом с подключением к выходу инвертора, исток n-канального транзистора соединен с точкой «земли», исток p-канального транзистора выполнен с возможностью подачи на него напряжения питания.

В устройстве M-разрядная схема памяти выполнена в составе двух запоминающих блоков статического или динамического типа, каждый из блоков выполнен с N-разрядным входом, предназначенным для связи с N-разрядным выходом N-разрядного счетчика, а также снабжен входами, предназначенными для подключения к столбцовым шинам считывания и записи с разрядностями, равными двум, с подключением каждого входа считывания и записи блоков к соответствующему ему разряду соответствующей двухразрядной шины, один из блоков выполнен с N-разрядным выходом и предназначен для записи количества полных циклов считывания, второй блок выполнен с (M-N)-разрядным выходом и предназначен для записи количества неполных циклов считывания, оба запоминающих блока выходами подключены к шине выхода с разрядностью N.

В устройстве запоминающий блок статического типа выполнен в составе запоминающих ячеек, равном разрядности блока, содержащих каждая по три инвертора, два из которых соединены друг с другом с подключением их входов к их выходам, между одними соединенными входом и выходом сформирован вход ячейки, снабженный входным ключом, между вторыми соединенными входом и выходом подключен своим входом третий инвертор, на выходе которого сформирован выход ячейки, снабженный выходным ключом, входные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по сигналу, подаваемому от столбцовой шины записи, на вход, предназначенный для подключения к указанной шине, выходные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по сигналу, подаваемому от столбцовой шины считывания, на вход, предназначенный для подключения к указанной шине.

В устройстве запоминающий блок динамического типа выполнен в составе запоминающих ячеек, равном разрядности блока, содержащих каждая по емкости с одной обкладкой, соединенной с точкой «земли», а второй обкладкой, подключенной между сформированным входом ячейки, снабженным входным ключом, и сформированным выходом ячейки, снабженным выходным ключом, входные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по сигналу, подаваемому от столбцовой шины записи, на вход, предназначенный для подключения к указанной шине, выходные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по сигналу, подаваемому от столбцовой шины считывания, на вход, предназначенный для подключения к указанной шине.

Сущность технического решения поясняется нижеследующим описанием и прилагаемыми фигурами.

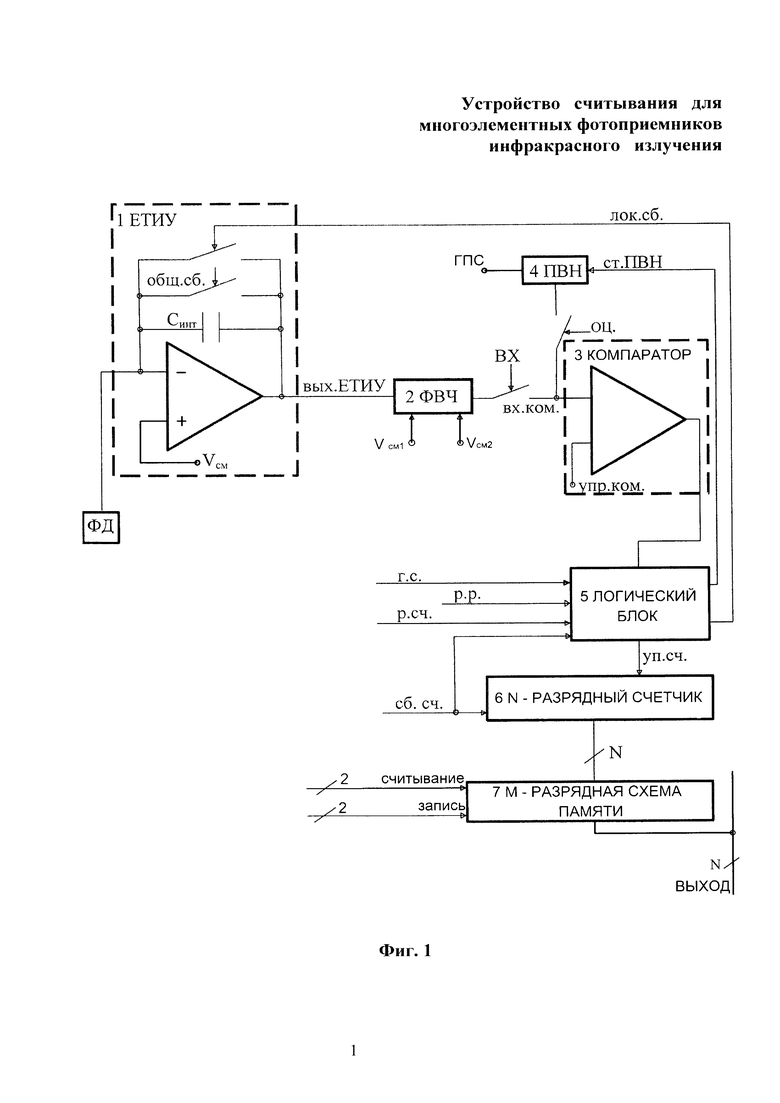

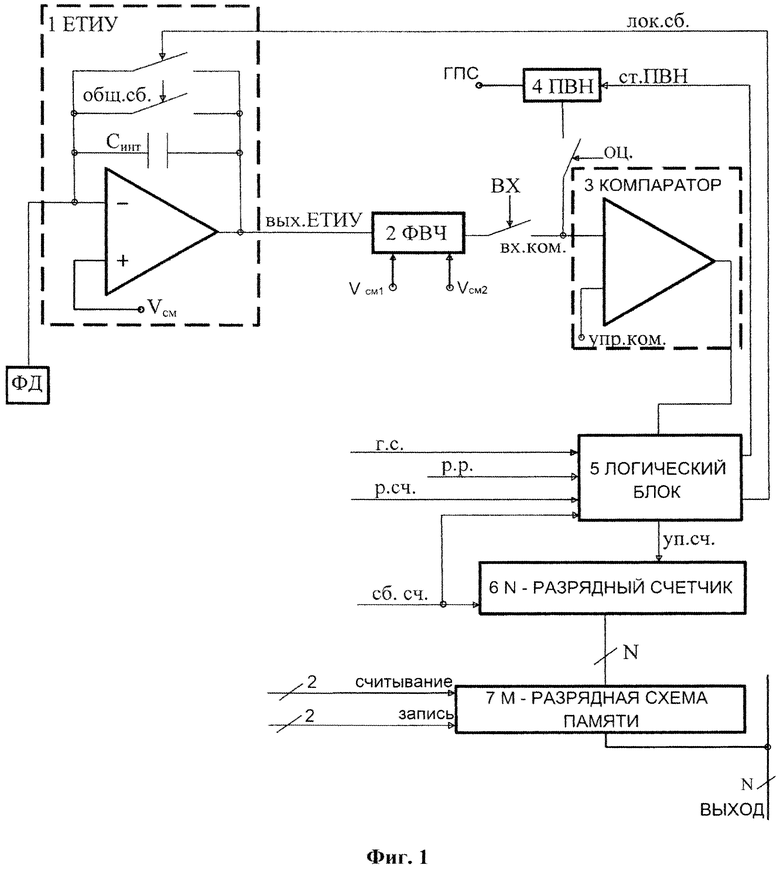

На Фиг. 1 представлена схема ячейки устройства считывания с подключением ее к фотодиоду, являющемуся фоточувствительным элементом фотоприемника инфракрасного излучения, где 1 - емкостной трансимпедансный усилитель (ЕТИУ); 2 - фильтр высоких частот (ФВЧ); 3 - компаратор; 4 - преобразователь времени в напряжение (ПВН); 5 - логический блок; 6 - N-разрядный счетчик; 7 - M-разрядная схема памяти; фотодиод (ФД); Cинт - интегрирующая емкость.

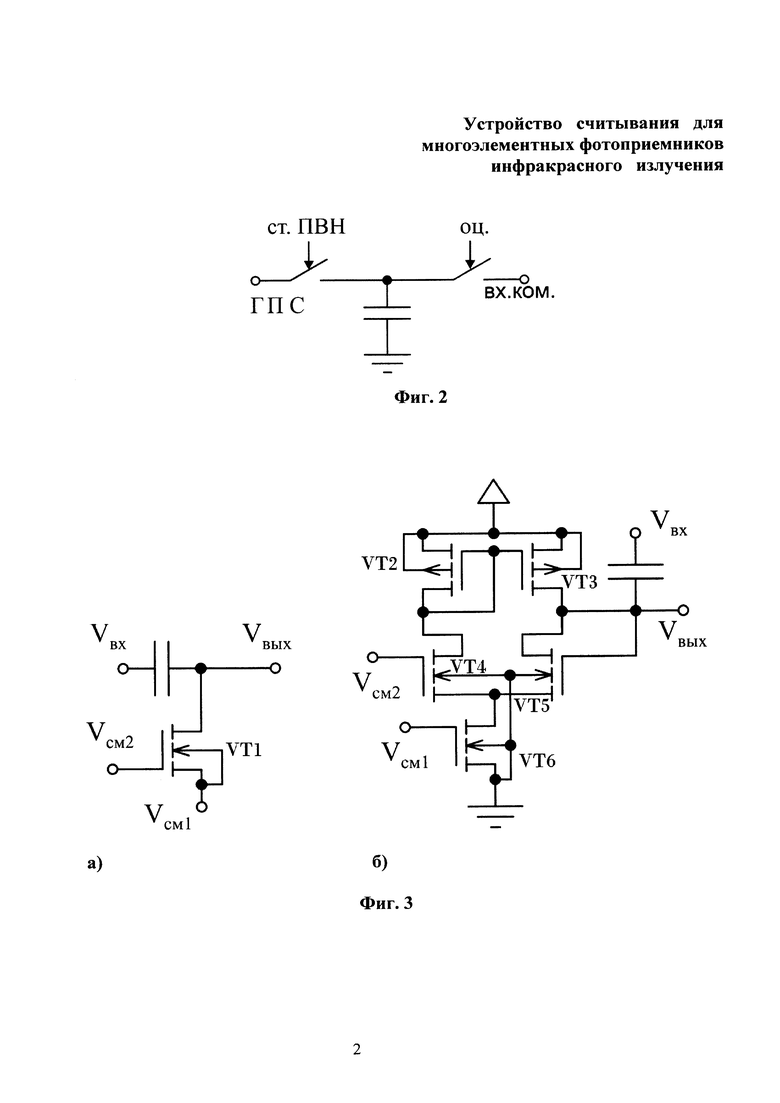

На Фиг. 2 представлен вариант реализации преобразователя времени в напряжение (ПВН) в составе емкости, ключа ПВН, выполненного с управляющим входом, являющимся входом преобразователя времени в напряжение, и одним концом, соединенным с генератором пилообразного сигнала (ГПС), а вторым - с обкладкой емкости, также показано соединение преобразователя ПВН с ключом, выполненным с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор.

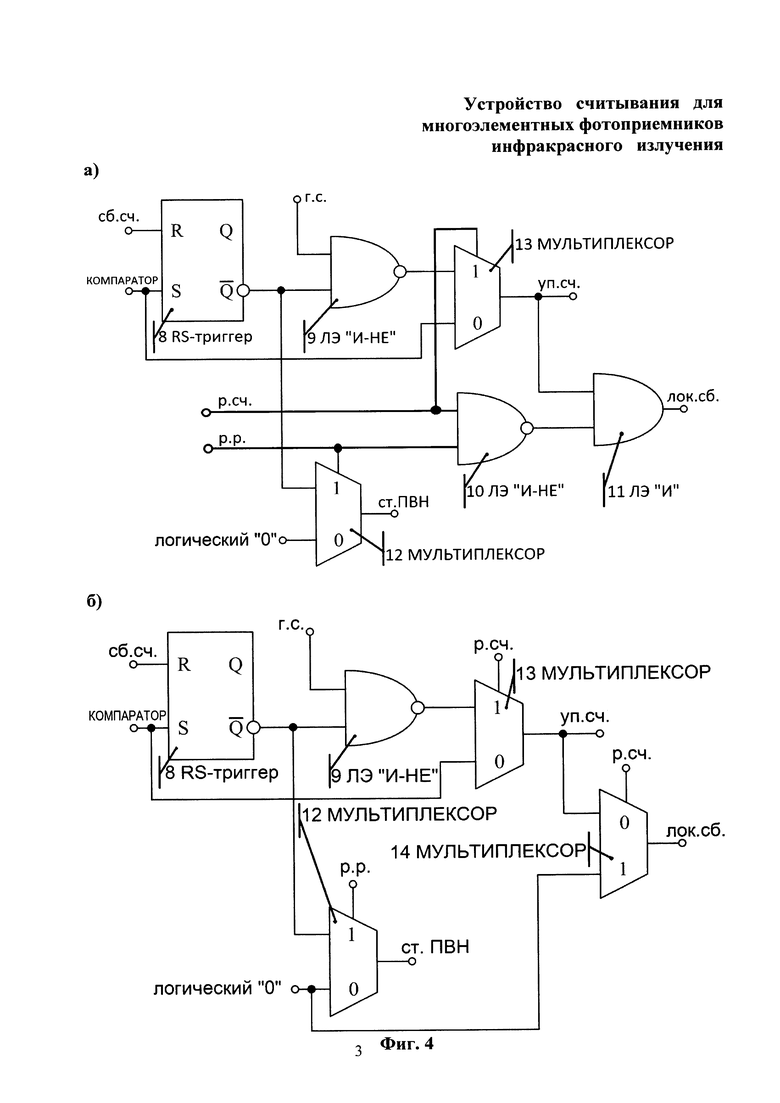

На Фиг. 3 представлены варианты схематического решения фильтра высокой частоты - ФВЧ: а) ФВЧ, выполненного в составе емкости и n-канального транзистора; б) ФВЧ, выполненный в составе емкости и дифференциального усилителя; где VT1 - n-канальный транзистор, VT2 - VT3 - p-канальные транзисторы дифференциального усилителя, VT4-VT6 - n-канальные транзисторы дифференциального усилителя.

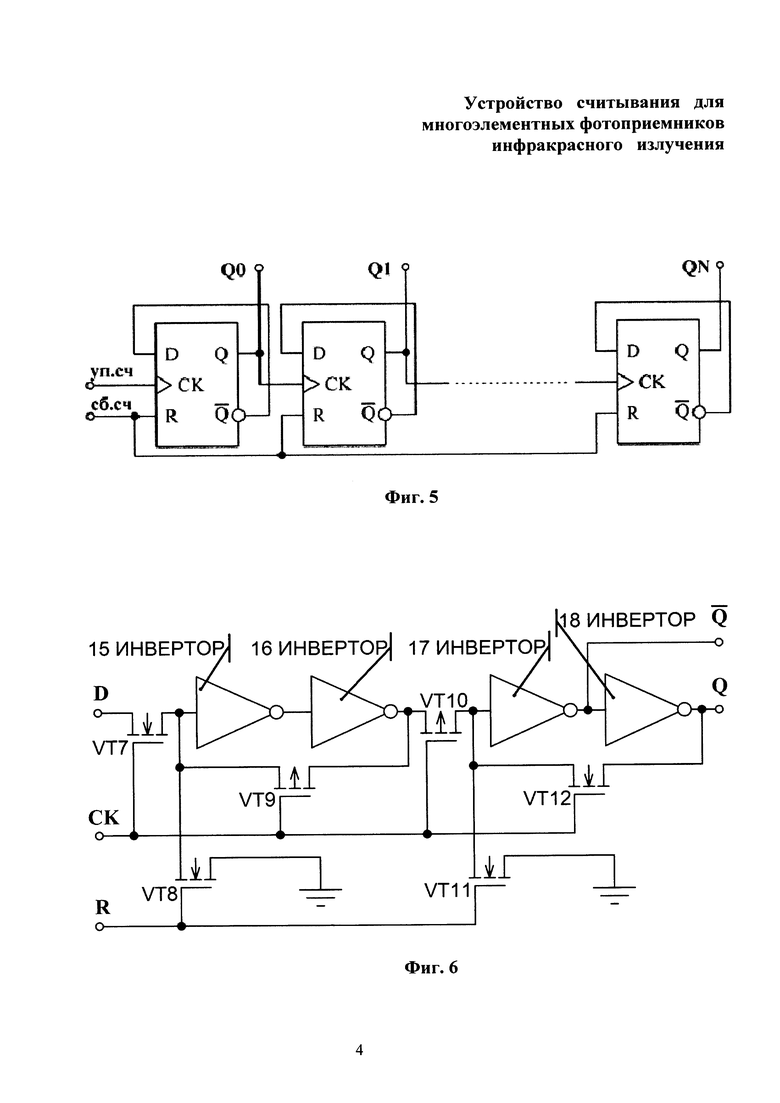

На Фиг. 4 представлены варианты выполнения логического блока: а) в составе RS-триггера, двух двухвходовых логических элементов «И-НЕ», одного двухвходового логического элемента «И», двух мультиплексоров из двух в один; б) в составе RS-триггера, одного двухвходового логического элемента «И-НЕ», трех мультиплексоров из двух в один; где 8 - RS-триггер; 9 и 10 - логический элемент (ЛЭ) «И-НЕ»; 11 - логический элемент (ЛЭ) «И»; 12, 13, 14 - мультиплексор.

На Фиг. 5 показано выполнение N-разрядного асинхронного счетчика со сбросом на D-триггерах.

На Фиг. 6 показана реализация D-триггера, на основе которых выполнен N-разрядный асинхронный счетчик: где 15, 16, 17, 18 - инвертор; VT7, VT8 - n-канальный транзистор; VT9, VT10 - p-канальный транзистор, VT11, VT12 - n-канальный транзистор.

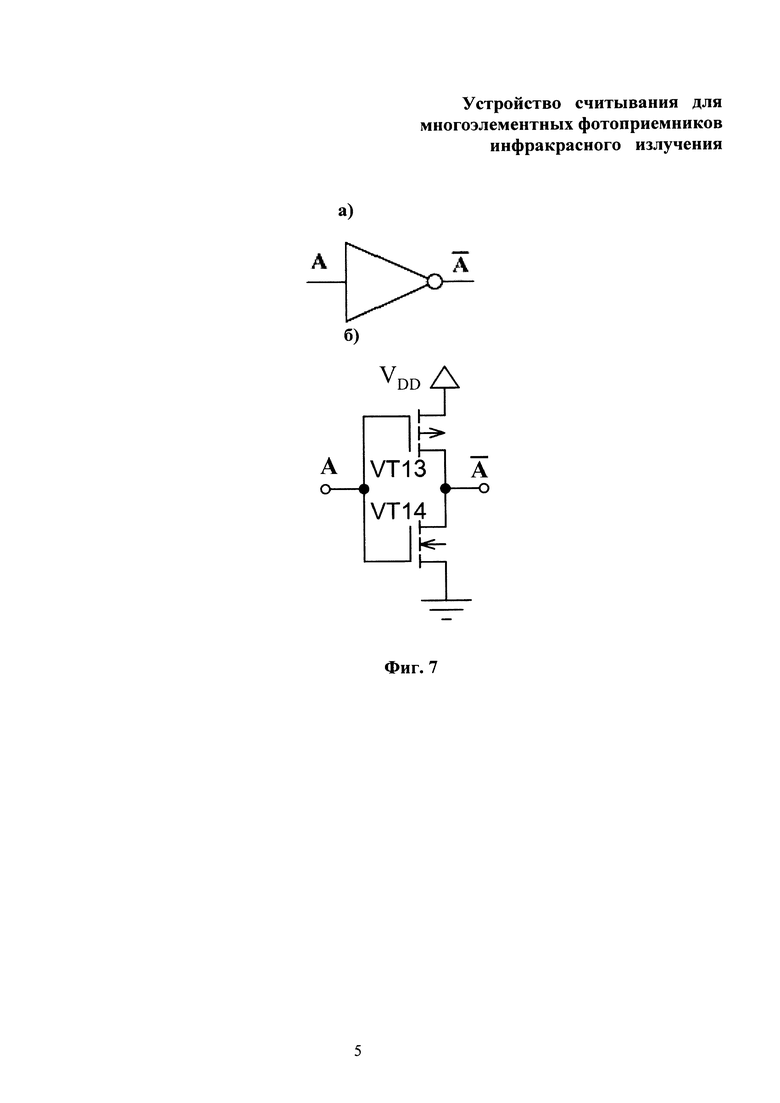

На Фиг. 7 показана реализация инвертора: а) условное обозначение; б) схема инвертора; где VT13 - n-канальный транзистор, VT14 - p-канальный транзистор.

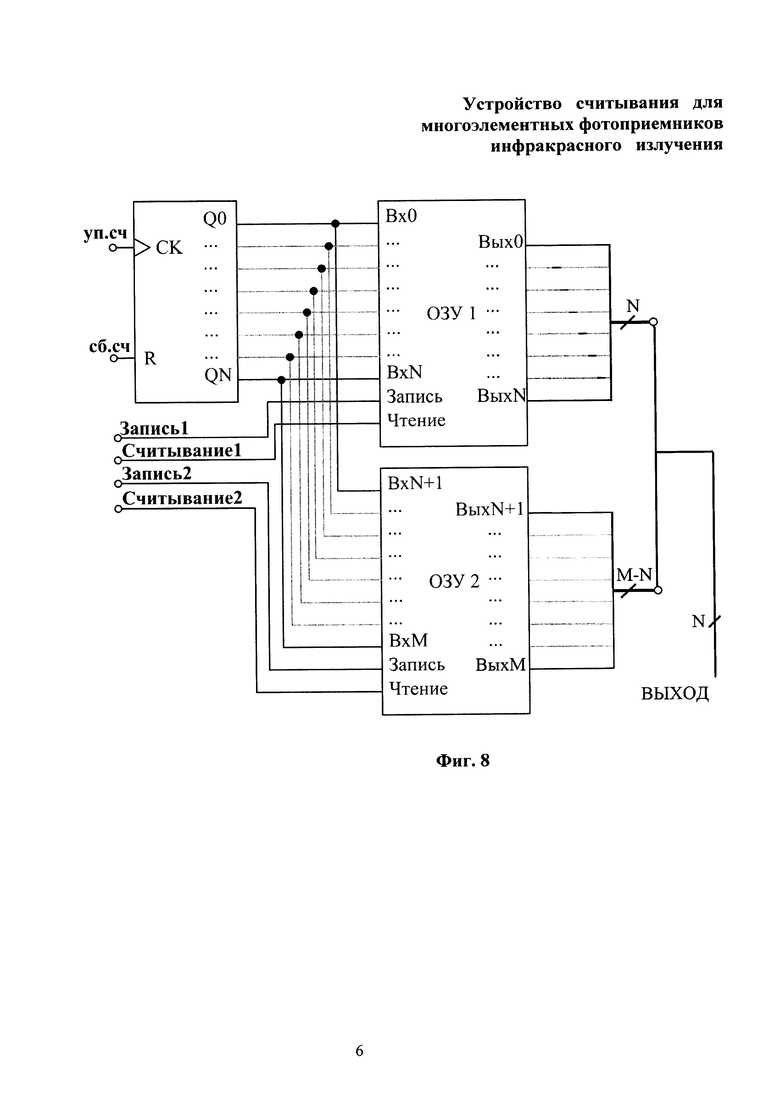

На Фиг. 8 показана реализация соединения M-разрядной схемы памяти в составе двух запоминающих блоков, один из которых предназначен для записи полных циклов считывания (ОЗУ 1), а второй - для записи неполных циклов считывания (ОЗУ 2), с N-разрядным асинхронным счетчиком.

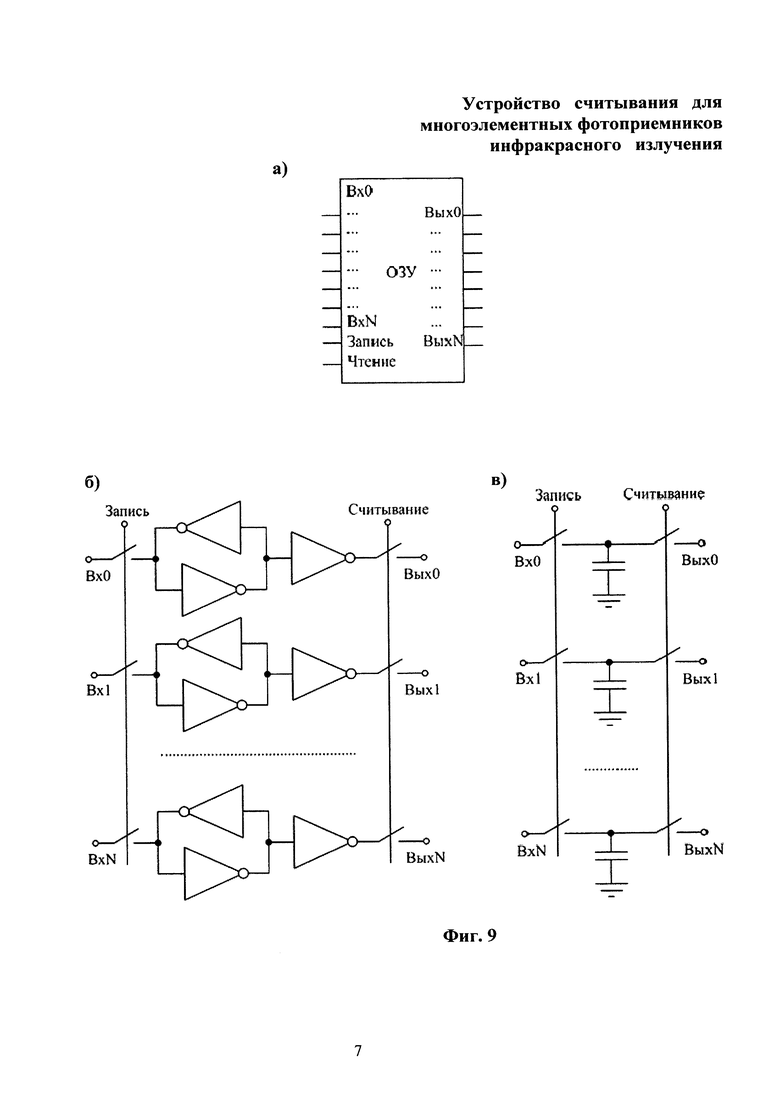

На Фиг. 9 приведены схемные реализации запоминающих блоков для построения M-разрядной схемы памяти на примере N-разрядного блока (ОЗУ): а) условное обозначение блока; б) схема N-разрядного блока статической памяти; в) схема N-разрядного блока динамической памяти.

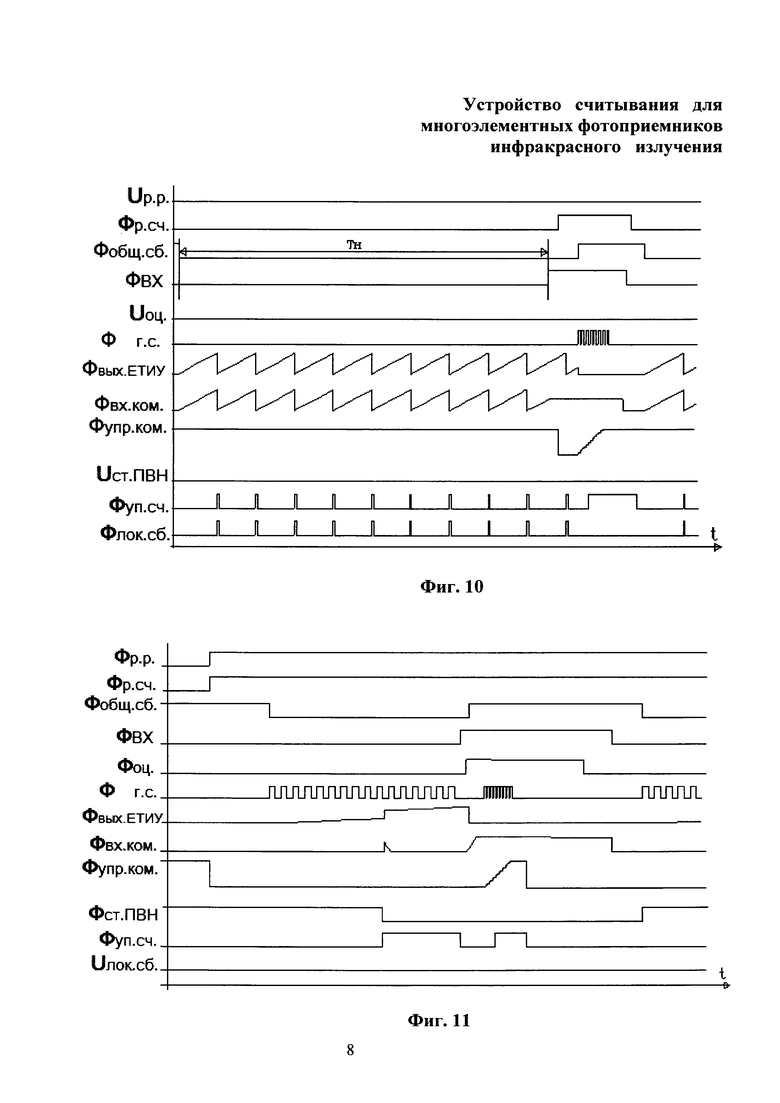

На Фиг. 10 представлены временные диаграммы управляющих напряжений и напряжений внутренних узлов устройства в тепловизионном режиме: где Up.p. - управляющий цифровой сигнал «режим работы»; Фр.сч. - управляющий цифровой сигнал «режим счета»; Фобщ.сб. - управляющий цифровой сигнал «общий сброс»; Фвх - управляющий цифровой сигнал «выборка и хранение»; Uоц. - управляющий цифровой сигнал «оцифровывание»; Ф г.с.- внешний сигнал тактовых импульсов «генерация синхроимпульсов»; Фвых.ЕТИУ - внутренний сигнал на выходе емкостного трансимпедансного усилителя; Фвх.ком. - внутренний сигнал на входе компаратора; Фупр.ком. - внешний управляющий аналоговый сигнал «управление компаратором»; Uст.ПВН - внутренний сигнал «остановка преобразователя времени в напряжение»; Фуп.сч. - внутренний сигнал «управление счетом»; Флок.сб. - внутренний сигнал «локальный сброс».

На Фиг. 11 представлены временные диаграммы управляющих напряжений и напряжений внутренних узлов устройства в режиме формирования трехмерного изображения: Фр.р. - управляющий цифровой сигнал «режим работы»; Фр.сч. - управляющий цифровой сигнал «режим счета»; Ф общ.сб. - управляющий цифровой сигнал «общий сброс»; Фвх - управляющий цифровой сигнал «выборка и хранение»; Фоц. - управляющий цифровой сигнал «оцифровывание»; Ф г.с. - внешний сигнал тактовых импульсов «генерация синхроимпульсов»; Фвых.ЕТИУ - внутренний сигнал на выходе емкостного трансимпедансного усилителя; Фвх.ком. - внутренний сигнал на входе компаратора; Ф упр.ком. - внешний управляющий аналоговый сигнал «управление компаратором»; Uст.ПВН - внутренний сигнал «остановка преобразователя времени в напряжение»; Фуп.сч. - внутренний сигнал «управление счетом»; Uлок.сб. - внутренний сигнал «локальный сброс».

Достижение технического результата в предлагаемом техническом решении базируется на следующем.

Сигналы при считывании, как в тепловизионном режиме, так и в режиме формирования трехмерного изображения формируются в ячейке устройства считывания (см. Фиг. 1) полностью в цифровой форме. Разработано схематическое решение ячейки считывания, при котором основные узлы (блоки) ячейки устройства считывания, обеспечивающие формирование сигналов при фотодетектировании для обоих режимов работы, - емкостной трансимпедансный усилитель (ЕТИУ) 1, фильтр высоких частот (ФВЧ) 2, компаратор 3, преобразователь времени в напряжение (ПВН) 4, логический блок 5, N-разрядный счетчик 6 и M-разрядная схема памяти 7 - последовательно используются в указанных режимах работы. Такая организация работы позволяет реализовать инфракрасное фотоприемное устройство (ИК ФПУ) с формированием в цифровой форме как тепловизионного изображения, так и трехмерного изображения в фокальной плоскости. В связи с этим предлагаемая схема ячейки устройства считывания (см. Фиг. 1) обеспечивает уменьшение количества узлов (блоков) в ячейке устройства считывания, снижение количества используемых управляющих сигналов и, как следствие, позволяет снизить потребляемую мощность и улучшить пространственное разрешение при работе устройства считывания в обоих режимах - режиме формирования тепловизионного изображения и в режиме формирования трехмерного изображения.

В общем случае выполнения (см. Фиг. 1) устройство считывания для многоэлементных фотоприемников инфракрасного излучения содержит многоканальную систему считывания в составе матрицы ячеек считывания, в каждой из которых имеются: емкостной трансимпедансный усилитель - ЕТИУ 1, фильтр высокой частоты - ФВЧ 2, компаратор 3, преобразователь времени в напряжение - ПВН 4, логический блок 5, N-разрядный счетчик 6, M-разрядная схема памяти 7.

ЕТИУ 1 характеризуется наличием интегрирующей емкости Синт, реализован с четырьмя входами и одним выходом (см. Фиг. 1). Интегрирующая емкость Синт в ЕТИУ 1 одной обкладкой соединена с его первым входом, а второй обкладкой - с его выходом. Первый вход ЕТИУ 1 предназначен для подключения к фотодиоду (ФД). Второй вход ЕТИУ 1 предназначен для подачи напряжения смещения (Vсм), управляющего его полосой пропускания. Третий вход ЕТИУ 1 предназначен для подачи напряжения, обеспечивающего сброс интегрирующей емкости Синт. Четвертый вход ЕТИУ 1 предназначен для подачи напряжения, обеспечивающего сброс интегрирующей емкости Синт при достижении порогового значения напряжения на выходе ЕТИУ 1. Выход ЕТИУ 1 соединен с первым входом ФВЧ 2.

ФВЧ 2 выполнен с возможностью настройки на определенную частоту отсечки сигнала, вырабатываемого на выходе ЕТИУ 1 и подаваемого на первый вход ФВЧ 2. ФВЧ 2 в этих целях снабжен вторым и третьим входами, которые предназначены для подачи напряжений смещения (соответственно Vсм 1 и Vсм 2), задающих граничную частоту. Частота отсечки регулируется подачей на указанные входы напряжений смещения, требуемых для регулирования частоты, в зависимости от того, в каком режиме работает устройство считывания в тепловизионном режиме или же в режиме формирования трехмерных изображений при поочередной их реализации. В тепловизионном режиме подачей напряжения смещения ФВЧ настраивается на низкую частоту отсечки сигнала. Обеспечивается режим коррелированной двойной выборки. В режиме формирования трехмерных изображений частотная полоса ФВЧ 2 меняется. Выход ФВЧ 2 для передачи сигнала, считанного с ФД и подвергнутого частотной обработке, соединен с инвертирующим входом компаратора 3.

Соединение выхода ФВЧ 2 и инвертирующего входа компаратора 3 реализовано через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала.

Неинвертирующий вход компаратора 3 предназначен для подачи управляющего сигнала.

Кроме того, указанный инвертирующий вход компаратора 3 также соединен с выходом ПВН 4. Соединение инвертирующего входа компаратора 3 и выхода ПВН 4 реализовано также через ключ, который выполнен с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из ПВН 4 в компаратор 3.

При работе устройства указанные ключи с управляющими входами для подачи сигнала, замыкающего их, и связывающие инвертирующий вход компаратора с ФВЧ 2 и ПВН 4 находятся в замкнутом состоянии поочередно.

Выход компаратора 3 соединен с первым входом логического блока 5, на который подается считываемый сигнал.

Логический блок 5 имеет пять входов и три выхода. Первый вход предназначен для подачи внутреннего вырабатываемого сигнала с компаратора 3 в результате считывания. Первый выход логического блока 5 соединен с входом ПВН 4 с возможностью подачи сигнала, разрешающего фиксацию текущего уровня напряжения в ПВН 4, который вырабатывает логический блок 5. Второй вход логического блока 5 предназначен для подачи внешнего сигнала, определяющего режим работы устройства. Второй выход логического блока 2 связан с четвертым входом ЕТИУ 1 и предназначен для подачи на указанный вход вырабатываемого логическим блоком 5 напряжения, обеспечивающего сброс интегрирующей емкости Синт при достижении порогового значения напряжения на выходе ЕТИУ 1. Третий вход логического блока 5 связан с шиной подачи внешнего сигнала, определяющего режим работы счетчика. Третий выход логического блока 5 связан со счетным входом N-разрядного счетчика 6 с возможностью подачи на указанный вход вырабатываемого логическим блоком 5 сигнала управления счетом в форме импульсов напряжения, сформированных в результате считывания сигнала, меняющих состояние счетчика. Четвертый вход логического блока 5 связан с шиной подачи внешнего сигнала на сброс счетчика. Пятый вход логического блока 5 связан со столбцовой шиной подачи генерированных синхроимпульсов, также относящихся к внешним сигналам.

ПВН 4 выполнен с двумя входами и одним выходом. Первый вход предназначен для подачи сигнала от логического блока 5, разрешающего фиксацию текущего уровня напряжения в ПВН 4. Второй вход ПВН 4 связан со столбцовой шиной подачи внешнего сигнала от генератора пилообразного сигнала. Выход ПВН 4 связан с инвертирующим входом компаратора 3. Как указано, соединение реализовано через ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из ПВН 4 в компаратор 3 (см. Фиг. 2).

N-разрядный счетчик 6 выполнен с двумя входами и одним выходом. Первый его вход связан с шиной подачи внешнего сигнала на сброс счетчика. Второй вход выполнен счетным и связан с третьим выходом логического блока 5 с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком 5. Выход N-разрядного счетчика 6 связан с входом M-разрядной схемы памяти 7.

M-разрядная схемы памяти 7 кроме входа, к которому подключен выход N-разрядного счетчика 6, имеет второй и третий входы. Второй и третий ее входы связаны соответственно со столбцовыми шинами считывания и записи. Выход M-разрядной схемы памяти 7 соединен со строчной шиной выхода разрядностью N.

Предлагаемое устройство может иметь следующие особенности его выполнения.

Так, N-разрядный счетчик 6 и M-разрядная схема памяти 7 выполнены соответственно N и М разрядными с N<M≤2N.

ЕТИУ 1 с интегрирующей емкостью Синт реализован на основе инвертирующего усилителя с двумя входами и одним выходом. Выход инвертирующего усилителя является выходом ЕТИУ 1. В составе ЕТИУ 1 имеются первый и второй ключи. Каждый из них выполнен с управляющим входом. Один из входов инвертирующего усилителя выполнен в качестве первого входа ЕТИУ 1, к нему подключен фотодиод. Второй вход инвертирующего усилителя является вторым входом ЕТИУ 1. Первый и второй ключи подключены к обкладкам интегрирующей емкости Синт. Управляющий вход первого ключа выполнен в качестве третьего входа ЕТИУ 1, с возможностью подачи на управляющий вход первого ключа напряжения, вызывающего его замыкание и обеспечивающего сброс интегрирующей емкости Синт. Управляющий вход второго ключа выполнен в качестве четвертого входа ЕТИУ 1, с возможностью подачи на управляющий вход второго ключа напряжения, вызывающего его замыкание и обеспечивающего сброс интегрирующей емкости Синт при достижении порогового значения напряжения на выходе ЕТИУ 1.

ФВЧ 2 может быть реализован, например, следующими вариантами.

Во-первых, ФВЧ 2 может быть выполнен в составе емкости и n-канального транзистора (см. Фиг. 3a)). VT1 - n-канальный транзистор своим стоком подсоединен к одной из обкладок емкости с концом, являющимся выходом ВФЧ 2, соединенным через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, с инвертирующим входом компаратора 3. Конец другой обкладки емкости, являющийся первым входом ФВЧ 2, соединен с выходом ЕТИУ 1. Второй и третий входы ФВЧ 2, предназначенные для подачи напряжений смещения, определяющих граничную частоту, соединены соответственно с затвором и истоком n-канального транзистора VT1. Подложка VT1 выполнена с возможностью подачи на нее того же потенциала, что и на исток.

Во-вторых, ФВЧ 2 может быть выполнен в составе емкости и дифференциального усилителя (см. Фиг. 3б)). Дифференциальный усилитель образован первым (VT2) и вторым (VT3) p-канальными транзисторами, а также третьим (VT4), четвертым (VT5) и пятым (VT6) n-канальными транзисторами. Подложки третьего (VT4), четвертого (VT5) и пятого (VT6) n-канальных транзисторов соединены с точкой «земли». Подложки первого (VT2) и второго (VT3) p-канальных транзисторов выполнены с возможностью подачи потенциала, равного напряжению питания. Истоки первого (VT2) и второго (VT3) p-канальных транзисторов соединены друг с другом с подачей на них напряжения питания. Затворы первого (VT2) и второго (VT3) p-канальных транзисторов соединены друг с другом и подсоединены к стоку первого (VT2) p-канального транзистора. Сток первого (VT2) p-канального транзистора соединен с истоком третьего (VT4) n-канального транзистора, сток второго (VT3) p-канального транзистора соединен с истоком четвертого (VT5) n-канального транзистора и с его затвором, соединенные сток второго (VT3) p-канального транзистора, исток четвертого (VT5) n-канального транзистора и его затвор подсоединены к одной из обкладок емкости с концом, являющимся выходом ФВЧ 2 соединенным через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, с инвертирующим входом компаратора 3. Конец другой обкладки емкости, являющийся первым входом ФВЧ 2, соединен с выходом ЕТИУ 1. Стоки третьего (VT4) n-канального транзистора и четвертого (VT5) n-канального транзистора соединены друг с другом и подсоединены к истоку пятого (VT6) n-канального транзистора. Сток пятого (VT6) n-канального транзистора выполнен соединенным с точкой «земли». Второй и третий входы ФВЧ 2, предназначенные для подачи напряжений смещения, определяющих граничную частоту, соединены соответственно с затвором третьего (VT4) n-канального транзистора и затвором пятого (VT6) n-канального транзистора.

Логический элемент 5 выполнен, например, следующими вариантами.

Во-первых, логический элемент 5 может быть выполнен в составе RS-триггера 8, двух логических элементов «И-НЕ» 9 и 10, логического элемента «И» 11, двух мультиплексоров 12 и 13, характеризующихся одним адресным входом, двумя информационными входами и одним выходом (см. Фиг. 4 а)).

При этом вход S RS-триггера 8, являющийся первым входом логического блока 5, соединен с выходом компаратора 3. Вход R RS-триггера 8 выполнен как четвертый вход логического блока 5 и связан с шиной подачи внешнего сигнала на сброс счетчика. Инверсный выход RS-триггера 8 соединен с одним из входов первого логического элемента «И-НЕ» 9. Второй вход первого логического элемента «И-НЕ» 9 выполнен как пятый вход логического блока 5, связанный со столбцовой шиной подачи внешних генерированных синхроимпульсов. Инверсный выход первого логического элемента «И-НЕ» 9 связан с первым информационным входом первого мультиплексора 13, нулевой информационный вход которого подключен к входу S RS-триггера 8, а адресный вход соединен с одним из входов второго логического элемента «И-НЕ» 10. Выход указанного мультиплексора 13 соединен с одним из входов логического элемента «И» 11 и выполнен как третий выход логического блока 5, который связан со счетным входом N-разрядного счетчика 6 с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком 5. Вход второго логического элемента «И-НЕ» 10, с которым соединен адресный вход указанного мультиплексора 13, выполнен как третий вход логического блока 5, связанный с шиной подачи внешнего сигнала, определяющего режим работы счетчика. Второй вход второго логического элемента «И-НЕ» 10 выполнен как второй вход логического блока 5, предназначенный для подачи внешнего сигнала, определяющего режим работы устройства. Инверсный выход второго логического элемента «И-НЕ» 10 связан со вторым входом логического элемента «И» 11. Выход логического элемента «И» 11 выполнен как второй выход логического блока 5, связанный с четвертым входом ЕТИУ 1 и предназначенный для подачи на указанный вход вырабатываемого логическим блоком 5 напряжения, обеспечивающего сброс интегрирующей емкости Синт при достижении порогового значения напряжения на выходе ЕТИУ 1. К инверсному выходу RS-триггера 8 подсоединен первый информационный вход второго мультиплексора 12, адресный вход которого подсоединен к второму входу второго логического элемента «И-НЕ» 10, который выполнен как второй вход логического блока 5, предназначенный для подачи внешнего сигнала, определяющего режим работы устройства. Выход второго мультиплексора 12 выполнен как первый выход логического блока 5, соединенный с входом ПВН 4 с возможностью подачи сигнала, разрешающего фиксацию текущего уровня напряжения в ПВН 4. Кроме того, логический блок 5 снабжен дополнительным шестым входом, являющимся нулевым информационным входом второго мультиплексора 12, соединенным с точкой «земли».

Во-вторых, логический элемент 5 может быть выполнен в составе RS-триггера 8, логического элемента «И-НЕ» 9, трех мультиплексоров 12, 13, 14, характеризующихся одним адресным входом, двумя информационными входами и одним выходом.

При этом вход S RS-триггера 8, являющийся первым входом логического блока 5, соединен с выходом компаратора 3. Вход R RS-триггера 8 выполнен как четвертый вход логического блока 5 и связан с шиной подачи внешнего сигнала на сброс счетчика. Инверсный выход RS-триггера 8 соединен с первым входом логического элемента «И-НЕ» 9. Второй вход логического элемента «И-НЕ» 9 выполнен как пятый вход логического блока 5, связанный со столбцовой шиной подачи внешних генерированных синхроимпульсов. Инверсный выход логического элемента «И-НЕ» 9 связан с первым информационным входом первого мультиплексора 13. Нулевой информационный вход первого мультиплексора 13 подключен к входу S RS-триггера 8. Адресный вход первого мультиплексора 13 соединен с адресным входом второго мультиплексора 14, при этом соединенные адресные входы первого и второго мультиплексоров соответственно 13 и 14 выполнены как третий вход логического блока 5, связанный с шиной подачи внешнего сигнала, определяющего режим работы счетчика. Выход первого мультиплексора 13 выполнен как третий выход логического блока 5, который связан со счетным входом N-разрядного счетчика 6 с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком 5. К выходу первого мультиплексора 13 подсоединен нулевой информационный вход второго мультиплексора 14. Выход второго мультиплексора 14 выполнен как второй выход логического блока 5, связанный с четвертым входом ЕТИУ 1 и предназначенный для подачи на указанный вход вырабатываемого логическим блоком 5 напряжения, обеспечивающего сброс интегрирующей емкости Синт при достижении порогового значения напряжения на выходе ЕТИУ 1. К инверсному выходу RS-триггера 8 подсоединен первый информационный вход третьего мультиплексора 12. Адресный вход третьего мультиплексора 12 выполнен как второй вход логического блока 5, предназначенный для подачи внешнего сигнала, определяющего режим работы устройства. Выход третьего мультиплексора 12 выполнен как первый выход логического блока 5, соединенный с входом ПВН 4 с возможностью подачи сигнала, разрешающего фиксацию текущего уровня напряжения в ПВН 4. Кроме того, логический блок 5 снабжен дополнительным шестым входом. Шестой вход логического блока 5 образован соединенными первым информационным входом второго мультиплексора 14 и нулевым информационным входом третьего мультиплексора 12, соединенными с точкой «земли».

ПВН 4 может быть реализован следующим образом (см. Фиг. 2).

ПВН 4, например, может быть выполнен в составе емкости преобразователя времени в напряжение и ключа преобразователя времени в напряжение. Указанная емкость заряжаема линейно с течением времени. Указанный ключ выполнен с управляющим входом, являющимся входом преобразователя времени в напряжение, предназначенным для подачи сигнала от логического блока 5, разрешающего фиксацию текущего уровня напряжения в ПВН 4. Указанная емкость одной обкладкой подсоединена к одному из концов указанного ключа. От подсоединения сформирован вывод, являющийся выходом ПВН 4, связанным с инвертирующим входом компаратора 3 через ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из ПВН 4 в компаратор 3. Вторая обкладка указанной емкости соединена с точкой «земли». Второй из концов указанного ключа, являющийся вторым входом ПВН 4, связан со столбцовой шиной подачи внешнего сигнала от генератора пилообразного сигнала.

N-разрядный счетчик 6 выполнен, например, асинхронным со сбросом. N-разрядный счетчик 6 содержит N D-триггеров (см. Фиг. 5). При этом входы сброса R всех D-триггеров соединены друг с другом. Вход сброса первого D-триггера, являющийся первым входом N-разрядного счетчика 6, связан с шиной подачи сигнала на сброс счетчика. Синхровход первого D-триггера, являющийся вторым, счетным, входом N-разрядного счетчика 6, связан с третьим выходом логического блока 5 с возможностью подачи на указанный вход сигнала управления счетом, вырабатываемого логическим блоком 5. Синхровход каждого последующего D-триггера соединен с выходом предыдущего D-триггера. Выходы каждого из D-триггеров выполнены с возможностью формирования разряда числа с увеличением его веса, начиная с первого, образуя N-разрядный выход счетчика. Информационный вход D каждого из D-триггеров соединен с его же инверсным выходом.

Каждый из D-триггеров выполнен в составе шести транзисторов VT7-VT12, четырех инверторов 15-18 (см. Фиг. 6). Первый (VT7) n-канальный транзистор истоком соединен с информационным входом D, стоком соединен с входом первого инвертора 15, выход которого соединен с входом второго инвертора 16. К стоку первого (VT7) n-канального транзистора подсоединен исток второго (VT8) n-канального транзистора. Затвор второго (VT8) n-канального транзистора соединен с входом сброса R D-триггера. Сток второго (VT8) n-канального транзистора соединен с точкой «земли». К соединенным стоку первого (VT7) n-канального транзистора и истоку второго (VT8) n-канального транзистора подсоединен исток третьего (VT9) p-канального транзистора. Сток третьего (VT9) p-канального транзистора соединен с выходом второго инвертора 16. Затвор третьего (VT9) p-канального транзистора соединен с затвором первого (VT7) n-канального транзистора. Исток четвертого (VT10) p-канального транзистора подсоединен к стоку третьего (VT9) p-канального транзистора. Сток четвертого (VT10) p-канального транзистора соединен с входом третьего инвертора 17. Выход третьего инвертора 17 соединен с входом четвертого инвертора 18. Кроме того, сток четвертого (VT10) p-канального транзистора соединен с истоком пятого (VT11) n-канального транзистора и истоком шестого (VT12) n-канального транзистора. Затвор пятого (VT11) n-канального транзистора соединен с затвором второго (VT8) n-канального транзистора. Сток пятого (VT11) n-канального транзистора соединен с точкой «земли». Затвор шестого (VT12) n-канального транзистора соединен с затвором четвертого (VT10) p-канального транзистора. Соединенные затворы шестого (VT12) n-канального транзистора и четвертого (VT10) p-канального транзистора соединены с соединенными затворами первого (VT7) n-канального транзистора и третьего (VT9) p-канального транзистора с подключением к синхровходу D-триггера. Сток шестого (VT12) n-канального транзистора соединен с выходом четвертого инвертора 18 с образованием прямого выхода D-триггера. Инверсный выход D-триггера выполнен в соединении выхода третьего инвертора 17 с входом четвертого инвертора 18.

Каждый из инверторов 15-18 (см. Фиг. 7а)) выполнен в составе пары транзисторов (см. Фиг. 7б)) - n-канального транзистора (VT13) и p-канального транзистора (VT14). Затворы транзисторов VT13 и VT14 соединены друг с другом с подключением к входу инвертора. Стоки транзисторов VT13 и VT14 соединены друг с другом с подключением к выходу инвертора. Исток n-канального транзистора (VT13) соединен с точкой «земли». Исток p-канального транзистора (VT14) выполнен с возможностью подачи на него напряжения питания.

M-разрядная схема памяти 7 выполнена (см. Фиг. 8) в составе двух запоминающих блоков (ОЗУ 1 и ОЗУ 2) статического или динамического типа. Каждый из запоминающих блоков выполнен с N-разрядным входом, предназначенным для связи с N-разрядным выходом N-разрядного счетчика 6. Кроме того, каждый из запоминающих блоков снабжен входами, предназначенными для подключения к столбцовым шинам считывания и записи с разрядностями, равными двум, с подключением каждого входа считывания и записи блоков к соответствующему ему разряду соответствующей двухразрядной шины. Один из запоминающих блоков (ОЗУ 1) выполнен с N-разрядным выходом и предназначен для записи количества полных циклов считывания. Второй запоминающий блок (ОЗУ 2) выполнен с (M-N)-разрядным выходом и предназначен для записи количества неполных циклов считывания. Оба запоминающих блока выходами подключены к шине выхода с разрядностью N.

Запоминающий блок (см. Фиг. 9а)) статического типа (см. Фиг. 9б)) выполнен в составе запоминающих ячеек, равном разрядности блока. Каждая из запоминающих ячеек статического запоминающего блока содержит по три инвертора. Два инвертора запоминающей ячейки соединены друг с другом с подключением их входов к их выходам. Между одними соединенными входом и выходом сформирован вход ячейки, снабженный входным ключом. Между вторыми соединенными входом и выходом двух инверторов запоминающей ячейки подключен своим входом третий инвертор запоминающей ячейки. На выходе третьего инвертора сформирован выход ячейки, снабженный выходным ключом. Входные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по внешнему сигналу, подаваемому от столбцовой шины записи, на вход, предназначенный для подключения к указанной шине. Выходные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по внешнему сигналу, подаваемому от столбцовой шины считывания, на вход, предназначенный для подключения к указанной шине.

Запоминающий блок (см. Фиг. 9а)) динамического типа (см. Фиг. 9в)) выполнен в составе запоминающих ячеек, равном разрядности блока. Каждая из запоминающих ячеек содержит по емкости. Емкость запоминающей ячейки одной обкладкой соединена с точкой «земли». Емкость запоминающей ячейки второй обкладкой подключена между сформированным входом ячейки, снабженным входным ключом, и сформированным выходом ячейки, снабженным выходным ключом. Входные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по сигналу, подаваемому от столбцовой шины записи, на вход, предназначенный для подключения к указанной шине. Выходные ключи запоминающих ячеек выполнены с возможностью управления их замыканием по сигналу, подаваемому от столбцовой шины считывания, на вход, предназначенный для подключения к указанной шине.

Устройство выполнено на полупроводниковой подложке кремния.

Работа устройства считывания для многоэлементных фотоприемников инфракрасного излучения осуществляется следующим образом.

Каждый из фотодиодов (ФД), являющийся фоточувствительным элементом матрицы фотоприемника инфракрасного излучения, подключают к соответствующей ему ячейке считывания устройства считывания для многоэлементных фотоприемников инфракрасного излучения, содержащего многоканальную систему считывания в составе матрицы ячеек считывания. Фотодиод подключают к первому входу инвертирующего усилителя ЕТИУ 1 с интегрирующей емкостью Синт в цепи обратной связи, являющемуся первым входом ЕТИУ 1. Интегрирующая емкость Синт в цепи обратной связи производит интегрирование заряда при считывании сигнала с фотодиода, осуществляя его накапливание. Управление процессами интегрирования сигнала осуществляется посредством подачи на третий и четвертый входы ЕТИУ 1 внешнего управляющего цифрового сигнала «общий сброс» - общ. сб. и внутреннего сигнала «локальный сброс» - лок. сб. соответственно на управляющие ключи ЕТИУ 1 - первый и второй ключи, подключенные к обкладкам интегрирующей емкости. Кроме того, на второй вход инвертирующего усилителя, являющегося вторым входом ЕТИУ 1 подают сигнал Vсм напряжения смещения, управляющего полосой пропускания ЕТИУ 1. На первый вход фильтра высокой частоты - ФВЧ 2, в частности, настроенный на низкую частоту отсечки сигнала, подается вырабатываемый на выходе инвертирующего усилителя ЕТИУ 1, являющемся выходом ЕТИУ 1, сигнал вых.ЕТИУ. На второй и третий входы ФВЧ 2 подают напряжения смещения, определяющие граничную частоту, регулирующие частоту отсечки сигнала, таким образом, обеспечивая режим коррелированной двойной выборки. На инвертирующий вход компаратора 3 от ФВЧ 2 через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, подается сигнал вырабатываемый ФВЧ 2. Ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, замыкается от внешнего управляющего цифрового сигнала «выборка и хранение» - ВХ. Кроме того, на инвертирующий вход компаратора 3 от преобразователя времени в напряжение - ПВН 4 подается также и другой сигнал, вырабатываемый ПВН 4, через ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор 3. Ключ, выполненный с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор 3, замыкается от внешнего управляющего цифрового сигнал «оцифровывание» - оц. На неинвертирующий вход компаратора 3 подается внешний управляющий аналоговый сигнал «управление компаратором» - упр. ком. Работа устройства считывания осуществляется также при участии логического блока 5, имеющегося в каждой из ячеек считывания, вырабатывающего необходимые сигналы, при поступлении на его вход сигнала с выхода компаратора, а также при поступлении со столбцовых шин на его входы сигналов: внешнего управляющего цифрового сигнала «режим работы» - p.p.; внешнего управляющего цифрового сигнала «режим счета» - р.сч; внешнего сигнала на сброс счетчика - сб.сч.; внешнего сигнала тактовых импульсов «генерация синхроимпульсов» - г.с. Режим работы логического блока 5 определяется: внешним управляющим цифровым сигналом «режим работы» - p.p.; внешним управляющим цифровым сигналом «режим счета» - р.сч; внешним сигналов на сброс счетчика - сб.сч.; внешним сигналов тактовых импульсов «генерация синхроимпульсов» - г.с. Логический блок 5 вырабатывает на выходах сигналы: сигнал, разрешающий фиксацию текущего уровня напряжения в преобразователе времени в напряжение, - ст. ПВН; напряжение, обеспечивающее сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, - лок.сб.; сигнал управления счетом - уп.сч. Внутренний сигнал, разрешающий фиксацию текущего уровня напряжения в преобразователе времени в напряжение, - ст. ПВН поступает на первый вход ПВН 4, а на второй вход ПВН 4 подают внешний сигнал со столбцовой шины подачи сигнала от генератора пилообразного сигнала - ГПС. При сигнале, разрешающем фиксацию текущего уровня напряжения в преобразователе времени в напряжение, - ст. ПВН, соответствующему логическому «0» работа ПВН 4 блокируется. При окончании импульса напряжения, обеспечивающего сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, - лок.сб. начинается новый цикл накопления заряда интегрирующей емкостью Синт ЕТИУ 1. На выходе ПВН 4 вырабатывается сигнал, который через ключ с управляющим входом поступает на инвертирующий вход компаратора 3. Данный ключ, как указано выше, выполнен с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор посредством подачи на управляющий вход внешнего управляющего цифрового сигнала «оцифровывание» - оц. На первый вход N-разрядного счетчика 6 поступает внешний сигнал на сброс счетчика - сб.сч., на второй его вход поступает внутренний сигнал с третьего выхода логического блока 5 управления счетом - уп.сч. Режим работы N-разрядного счетчика 6 определяется внешним сигналом на сброс счетчика - сб.сч. С N-разрядного выхода N-разрядного счетчика 6 вырабатываемый им сигнал поступает на M-разрядной схемы памяти 7 вход M-разрядной схемы памяти 7 для записи. На второй и третий входы M-разрядной схемы памяти 7 подаются внешние сигналы со столбцовых двухразрядных шин считывания и записи. На N-разрядном выходе M-разрядной схемы памяти 7 формируется сигнал, передаваемый на строчную шину выхода разрядностью N.

В тепловизионном режиме устройство работает следующим образом. Работу устройства иллюстрируют временные диаграммы (см. Фиг. 10) управляющих внешних сигналов и сигналов, вырабатываемых внутренними узлами.

В тепловизионном режиме значение внешнего управляющего цифрового сигнала «режим работы» - p.p. равно нулю. Сброс интегрирующей емкости Синт ЕТИУ 1 осуществляют импульсом внешнего управляющего цифрового сигнала «общий сброс» - общ.сб. При его изменении с логической «1» на логический «0» начинается процесс интегрирования заряда. Логический блок 5 устанавливает уровень сигнала ст. ПВН, соответствующим логическому «0», который подается на управляющий вход ключа, выполненного с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор, в результате чего, ключ оказывается в разомкнутом состоянии, а ПВН 4 - отключенным от инвертирующего входа компаратора 3. Сигнал, вырабатываемый на выходе ЕТИУ 1, проходит через ФВЧ 2, на выходе которого формируется сигнал с учетом настройки ФВЧ 2 на низкую частоту отсечки сигнала. Частота отсечки регулируется подаваемыми на второй и третий входы ФВЧ 2 соответствующими внешними напряжениями смещения Vсм1 и Vсм2. Таким образом, обеспечивается режим коррелированной двойной выборки. Далее с выхода ФВЧ 2, который соединен через ключ, выполненный с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, - ВХ сигнал поступает на инвертирующий вход компаратора 3. Компаратор 3 работает в асинхронном режиме, и сигнал на инвертирующем входе - вх.ком. при достижении порогового уровня, задаваемого внешним управляющим аналоговым сигналом «управление компаратором» - упр.ком., подаваемым на неинвертирующий вход, сбрасывается, затем снова нарастает и сбрасывается и т.д., пока на неинвертирующий вход компаратора 3 подают соответствующий сигнал упр.ком. При таком режиме логический блок 5 на втором и третьем своих выходах вырабатывает импульсные напряжения (см. Фиг. 10) - Флок.сб. и Фуп.сч., соответственно. Напряжение, обеспечивающее сброс интегрирующей емкости при достижении порогового значения напряжения на выходе емкостного трансимпедансного усилителя, - лок.сб. подается на управляющий вход второго ключа ЕТИУ 1 и приводит к выравниванию напряжения на его выходе относительно напряжения на его первом входе, а с окончанием его импульса - Флок.сб. начинается новый цикл интегрирования заряда интегрирующей емкостью Синт ЕТИУ 1. Импульс напряжения Фуп.сч. (сигнал управления счетом), вырабатываемый на третьем выходе логического блока 5, подается на счетный вход N-разрядного счетчика 6 и обеспечивает увеличение его внутреннего значения на единицу. Временной промежуток между импульсами внешнего управляющего цифрового сигнала «общий сброс» - общ.сб. и сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, - ВХ определяет время накопления фотосигнала.

Уровень фотосигналов, задаваемый количеством фотоэлектронов фотодиода, Qфс определяется выражением: Qфc=N×Cинт×Vупр.ком+Cинт×Vп, где N - количество полных циклов накопления, Vп - напряжение на инвертирующем входе компаратора в последнем, неполном цикле накопления на момент появления переднего фронта сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, - ВХ.

За временной промежуток между импульсами внешнего управляющего цифрового сигнала «общий сброс» - общ.сб. и сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, - ВХ интегрирующая емкость Синт сбрасывается некоторое количество раз, что подсчитывается N-разрядным счетчиком 6, формируя старшие N разрядов фотосигналов. Значение на N-разрядном счетчике 6 передается в M-разрядную схему памяти 7 по внешнему управляющему сигналу «запись», в первый блок, осуществляющий запись количества полных циклов считывания (ОЗУ 1, см. Фиг. 8). Причем разрядность M-разрядной схемы памяти 7 выше разрядности N-разрядного счетчика 6, N<M≤2N.

При размыкании ключа, связывающего ФВЧ 2 и компаратор 3, посредством соответствующего значения сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, - ВХ на инвертирующем входе компаратора 3 сохраняется напряжение Vп. Его значение является определяющим для младших разрядов фотосигналов.

Для получения младших разрядов сохраненный сигнал на инвертирующем входе компаратора 3 оцифровывается посредством сравнения с пилообразным сигналом следующим образом. На неинвертирующий вход компаратора 3 подается пилообразный сигнал. Пятый вход логического блока 5 предварительно сбрасывают подачей сигнала, равного логической «1», на четвертый вход логического блока 5, наряду со сбросом счетчика подачей этого же сигнала на первый вход счетчика. Синхронно с подачей на неинвертирующий вход компаратора 3 пилообразного сигнала на пятый вход логического блока 5 от столбцовой шины генерированных синхроимпульсов - г.с. подают импульсы, что вызывает изменение состояния N-разрядного счетчика 6. При равенстве сигналов на инвертирующем входе компаратора 3 и неинвертирующем входе компаратора 3, на третьем выходе логического блока 5 вырабатывается стоп-сигнал для N-разрядного счетчика 6 (см. Фиг. 10, изменение уровня Фуп.сч. с низкого на высокий). Значение на N-разрядном счетчике 6 передается в M-разрядную схему памяти 7 по внешнему управляющему сигналу «запись», во второй блок, осуществляющий запись количества неполных циклов считывания (ОЗУ 2, см. Фиг. 8).

Для работы устройства в следующем кадре счетчик сбрасывается. В течение работы устройства в следующем кадре, цифровые значения из M-разрядной схемы памяти 7 по N-разрядной выходной шине поступают в соответствующую ячейку мультиплексора (на Фиг. 1 не показано).

В режиме формирования трехмерных изображений устройство работает следующим образом. Работу устройства иллюстрируют временные диаграммы (см. Фиг. 11) управляющих внешних сигналов и сигналов, вырабатываемых внутренними узлами.

В этом режиме значение внешнего управляющего цифрового сигнала «режим работы» - p.p. равно единице. Также изменяется частотная полоса ФВЧ 2 в результате подачи на второй и третий входы ФВЧ 2 внешних напряжений смещения Vсм1 и Vсм2 других значений. На протяжении всей реализации данного режима подаваемый на третий вход логического блока 5 внешний управляющий цифровой сигнал «режим счета» - р.сч. равен единице, поскольку требуется подсчитывать только синхроимпульсы. В промежуток времени между двумя следующими друг за другом импульсами внешнего управляющего цифрового сигнала «общий сброс» - общ.сб., подаваемыми на третий вход ЕТИУ 1, устройство находится в режиме ожидания отраженного объектом наблюдения импульса от подсветки, срабатываемой синхронно с наступлением ожидания (начало ожидания соответствует изменению уровня Фобщ.сб. с высокого на низкий, см. Фиг. 11). С началом ожидания отраженного импульса на пятый вход логического блока 5 от столбцовой шины генерированных синхроимпульсов - г.с. подают импульсы для счета времени до прихода отраженного сигнала объектом, передаваемые на второй счетный вход N-разрядного счетчика 6. На второй вход ПВН 4 с началом ожидания подают внешний сигнал со столбцовой шины подачи сигнала от генератора пилообразного сигнала - ГПС, период которого равен периоду генерированных синхроимпульсов - г.с. В момент прихода отраженного импульса объектом на выходе ЕТИУ 1, на первом входе ФВЧ 2, которые соединен с выходом ЕТИУ 1, уровень напряжения резко меняется, в результате на выходе ФВЧ 2, на инвертирующем входе компаратора 3, связанном с выходом ФВЧ 2, возникает пик напряжения (Фвх.ком., см. Фиг. 11). При превышении значения указанного пика напряжения, поступающего на инвертирующий вход компаратора 3, значения напряжения на неинвертирующем входе компаратора 3 (Фупр.ком., см. Фиг. 11) происходит срабатывание компаратора 3. В результате логический блок 5 останавливает передачу от столбцовой шины генерированных синхроимпульсов - г.с. на счетный вход N-разрядный счетчик 6, а также вырабатывает сигнал остановки ПВН 4 - уровень сигнала Фст.ПВН. меняется с высокого на низкий. Полученное значение в N-разрядном счетчике 6 записывается в M-разрядную схему памяти 7 по внешнему управляющему сигналу «запись», в первый блок, осуществляющий запись количества полных циклов считывания (ОЗУ 1,см. Фиг. 8).

С окончанием ожидания отраженного импульса объектом наблюдения, что соответствует изменению уровня Фобщ.сб. с низкого на высокий (см. Фиг. 11) инвертирующий вход компаратора 3 изолируется от выхода ФВЧ 2 посредством размыкания соединяющего ключа, выполненного с управляющим входом для подачи сигнала, замыкающего ключ и обеспечивающего выполнение выборки и хранения фотосигнала, от соответствующего внешнего управляющего цифрового сигнала «выборка и хранение» - ВХ. Замыканием ключа, выполненного с управляющим входом, предназначенным для подачи напряжения, замыкающего ключ для обеспечения передачи сигнала из преобразователя времени в напряжение в компаратор 3, сигнал с выхода ПВН 4 передается на инвертирующий вход компаратора 3. Ключ замыкается от внешнего управляющего цифрового сигнал «оцифровывание» - оц.

Для получения младших разрядов сохраненный сигнал на инвертирующем входе компаратора 3 оцифровывается посредством сравнения с пилообразным сигналом следующим образом. На неинвертирующий вход компаратора 3 подается пилообразный сигнал. Пятый вход логического блока 5 предварительно сбрасывают подачей сигнала, равного логической «1», на четвертый вход логического блока 5, наряду со сбросом счетчика подачей этого же сигнала на первый вход счетчика. Синхронно с подачей на неинвертирующий вход компаратора 3 пилообразного сигнала на пятый вход логического блока 5 от столбцовой шины генерированных синхроимпульсов - г.с. подают импульсы, что вызывает изменение состояния N-разрядного счетчика 6. При равенстве сигналов на инвертирующем входе компаратора 3 и неинвертирующем входе компаратора 3, на третьем выходе логического блока 5 вырабатывается стоп-сигнал для N-разрядного счетчика 6 (см. Фиг. 11, изменение уровня Фуп.сч. с низкого на высокий). Значение на N-разрядном счетчике 6 передается в M-разрядную схему памяти 7 по внешнему управляющему сигналу «запись», во второй блок, осуществляющий запись количества неполных циклов считывания (ОЗУ 2, см. Фиг. 8).