Изобретение относится к аппаратным средствам персонального компьютера /PC/ и может использоваться в качестве монитора в PC.

Прототипом принят телевизионный приемник из цифровой системы телевидения [1, с.5], содержащий синтезатор частот, три канала, каждый из которых включает последовательно соединенные блок обработки кодов, накопитель кодов и блок импульсных усилителей, блок модуляции излучений, последовательно соединенные делитель частоты и блок строчной развертки из задающего генератора и выходного каскада, первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, четыре источника опорных напряжений, проекционную оптическую систему и матовый экран. Блок обработки кодов выполняет удвоение отсчетов в строке. Накопители кодов выполняют сосредоточение кодов кадра раздельно каждого цветового сигнала. Блок модуляции излучений выполняет яркостную модуляцию излучений излучателей одновременно 300 строк, преобразуя цифровые коды в изменение яркости излучений 300 излучателей соответственно значениям кодов. Один пьезодефлектор выполняет строчную развертку параллельно 300 строк с повторением их 300 раз за первое поле кадра, второй пьезодефлектор производит смещение на шаг строки при развертке 300 четных строк во втором поле кадра с повторением их 300 раз. На экран изображение проецируется оптической системой, увеличивая его в несколько раз. Недостатки прототипа: нельзя использовать в качестве монитора в компьютере, не создает условия стереоэффекта для восприятия зрителем трехмерного изображения.

Цель изобретения - воспроизвести в мониторе условия получения стереоэффекта для пользователя РС.

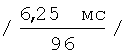

Техническим результатом является получение в заявляемом мониторе условий воспроизведения стереоэффекта и увеличение разрешающей способности кадра. Результат достигается применением с видеоадаптера РС видеорежима 640×480 при частоте 160 Гц, удвоением числа отсчетов в строке до 1280 /640×2/, удвоением строк до 960 /480×2/, разверткой кадра одновременно 480 нечетными и 480 четными строками с повторением каждой их группы за период кадра по 48 раз. Этот способ дает увеличение усредненной яркости изображения в 46080 раз /960стр×48/. Технический результат по восприятию объемного изображения достигается использованием ЗД-очков с ИК-приемником на оправе очков и ИК-передатчика на экране монитора.

С раздельных выходов компьютера аналоговые видеосигналы R, G, В поступают на 1-3 информационные входы цифрового монитора, на первый и второй управляющие входы монитора с соответствующих выходов видеоадаптера PC поступают рабочая частота и синхроимпульсы стереопар 80 Гц. Вслед за синхроимпульсом стереопары следует левый кадр стереопары. Синтезатор частот, синхронизируясь по переднему фронту синхроимпульса стереопары и используя рабочую частоту с PC, выдает со своих выходов частоту дискретизации кодов fд, двойную частоту дискретизации, частоту строк 76,8 кГц, частоту кадров 160 Гц и соответствующую частоту выдачи кодов fвых 19,6608 МГц. Аналоговые цветовые сигналы R, G, В преобразуются 1-3 АЦП в 8-и разрядные двоичные коды отсчетов строк, которые после удвоения отсчетов в строке и удвоения числа строк поступают в накопители кодов, с которых после усиления сигналов разрядов кодов в импульсных усилителях поступают в излучатели блока модуляции излучений, где преобразуются в модулированные по яркости излучения трех цветов для каждой строки. Излучения 480 излучателей одновременно поступают на отражатель пьезодефлектора, с него на отражатель следующего пьезодефелектора, выполняющего строчную развертку параллельно 480 нечетных строк, проекционный объектив проецирует изображение нечетных строк на экран. При обратной /справа налево/ развертке идет развертка 480 четных строк, на экран проецируется изображение четных строк. За период кадра развертка нечетных и четных строк повторяется по 48 раз.

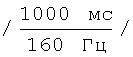

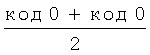

Длительность кадра 6,25 мс  . Частота дискретизации кодов АЦП 49,152 МГц /640отсч×480строк×160 Гц/. Длительность строки с АЦП 13,02 мкс

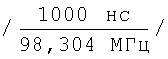

. Частота дискретизации кодов АЦП 49,152 МГц /640отсч×480строк×160 Гц/. Длительность строки с АЦП 13,02 мкс  , частота строк 76,8 кГц. Длительность строки на экране 65,1 мкс

, частота строк 76,8 кГц. Длительность строки на экране 65,1 мкс  . 96 - частота повторов строк в кадре /48×2/, частота строк 15,36 кГц

. 96 - частота повторов строк в кадре /48×2/, частота строк 15,36 кГц  . Между глазами и экраном размещаются электронно-управляемые ЗД-очки [2, с.558-565], в которых синхронно и синфазно со сменой кадров перекрывается поле зрения тому из глаз, кадр которого отсутствует.

. Между глазами и экраном размещаются электронно-управляемые ЗД-очки [2, с.558-565], в которых синхронно и синфазно со сменой кадров перекрывается поле зрения тому из глаз, кадр которого отсутствует.

Сущность изобретения в том, что в цифровой монитор, содержащий синтезатор частот, три канала, каждый из которых включает блок обработки кодов и последовательно соединенные накопитель кодов и блок импульсных усилителей, блок модуляции излучений, делитель частоты и блок строчной развертки, первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, четыре источника опорных напряжений, проекционный объектив и матовый экран, введены второй делитель частоты, выход которого подключен к входу второго усилителя, ИК-передатчик, расположенный над матовым экраном, ЗД-очки с ИК-приемником на оправе очков, в каждый канал введены АЦП и блок удвоения строк, входы которого подключены к выходам блока обработки кодов, а выходы подключены к входам накопителя кодов.

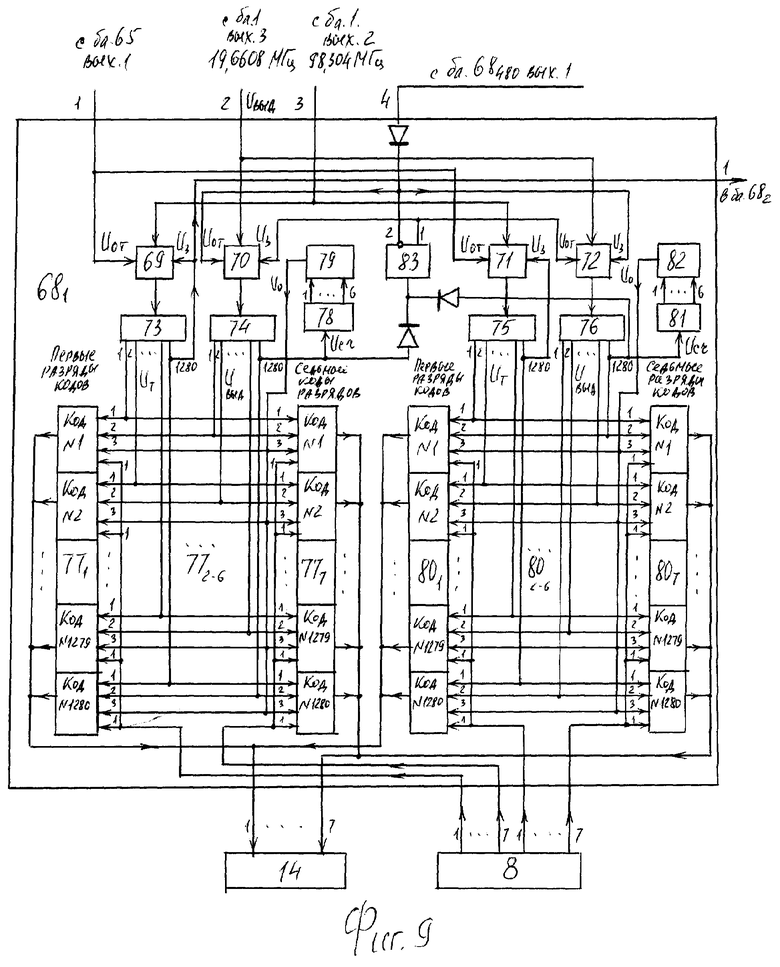

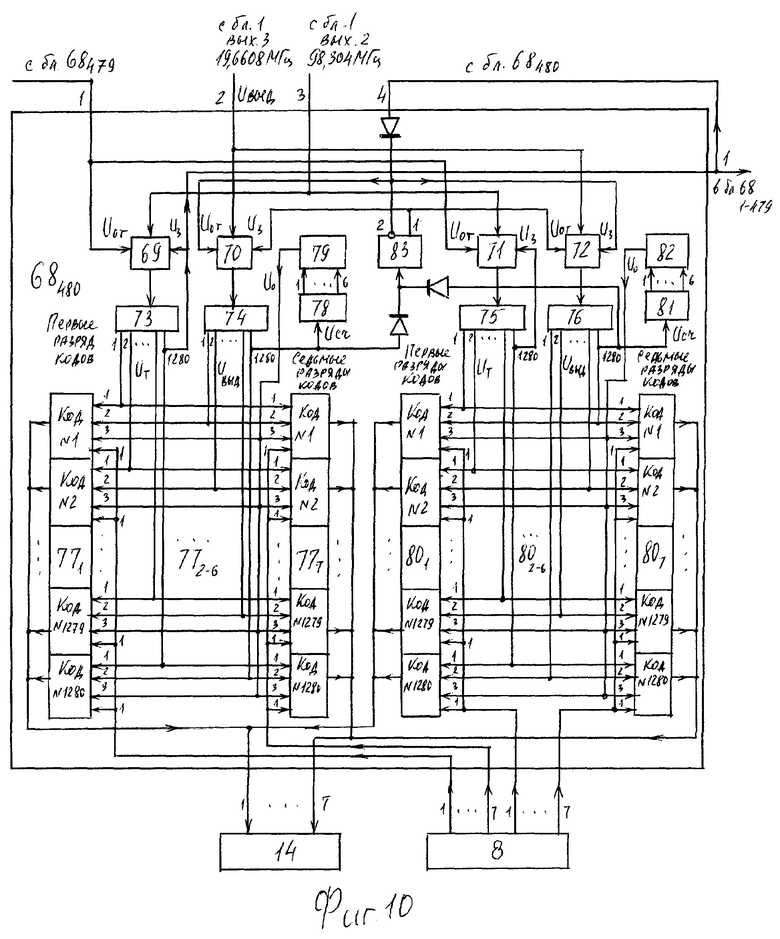

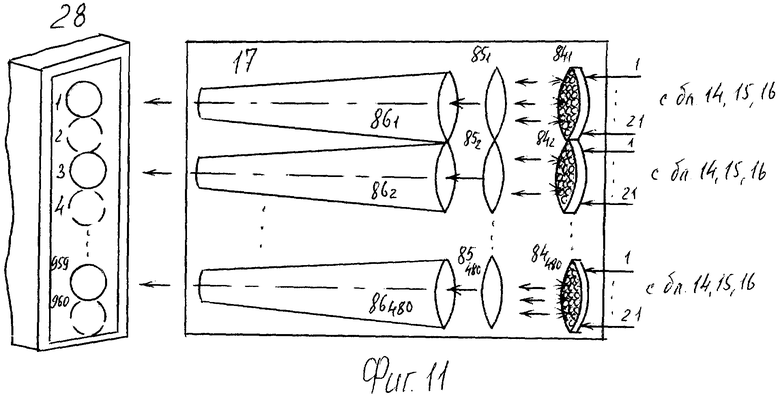

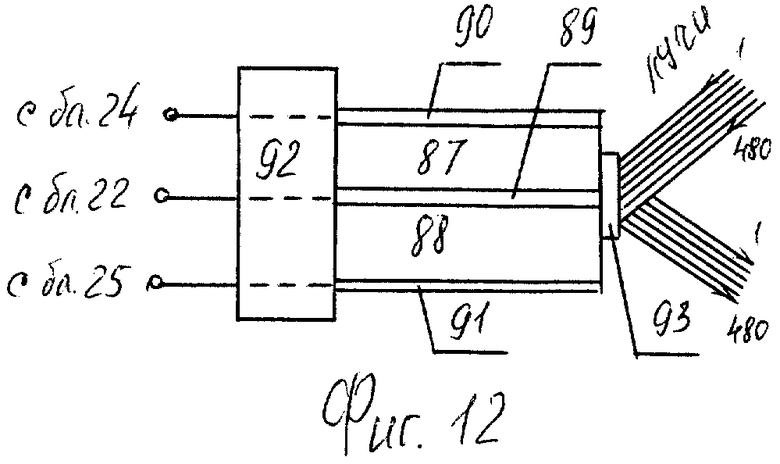

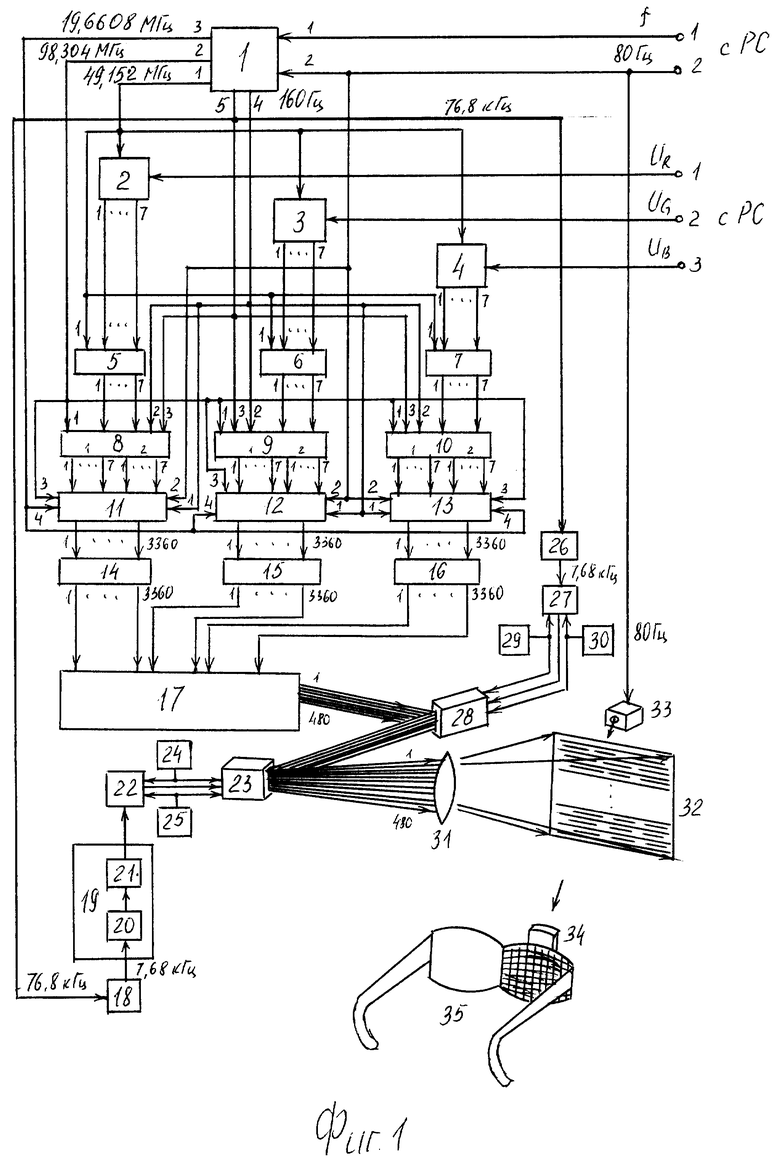

Функциональная схема цифрового монитора на фиг.1, растр и форма управляющего напряжения развертки строк на фиг.2, АЦП видеосигнала на фиг.3, блок обработки кодов на фиг.4, блок удвоения строк на фиг.5, первый блок задержек на фиг.6, накопитель кодов на фиг.7, накопитель кодов нечетного /четного/ кадра на фиг.8, блок регистров на фиг.9 и 10, блок модуляции излучений на фиг.11, конструкция пьезодефлектора на фиг.12. Цифровой монитор /фиг.1/ включает синтезатор 1 частот, три канала, первый канал содержит последовательно соединенные первый АЦП 2, первый блок 5 обработки кодов, первый блок 8 удвоения строк, первый накопитель 11 кодов и первый блок 14 импульсных усилителей, второй канал содержит последовательно соединенные второй АЦП 3, второй блок 6 обработки кодов, второй блок 9 удвоения строк, второй накопитель 12 кодов и второй блок 15 импульсных усилителей, третий канал содержит последовательно соединенные третий АЦП 4, третий блок 7 обработки кодов, третий блок 10 удвоения строк, третий накопитель 13 кодов и третий блок 16 импульсных усилителей, включает блок 17 модуляции излучений, последовательно соединенные первый делитель 18 частоты /10:1/, блок 19 строчной развертки из последовательно соединенных задающего генератора 20 и выходного каскада 21, первый усилитель 22 и первый пьезодефлектор 23 с отражателем на торце, первый источник 24 положительного опорного напряжения, второй источник 25 отрицательного опорного напряжения, последовательно соединенные второй делитель 26 частоты /10:1/, второй усилитель 27 и второй пьезодефлектор 28 с отражателем на торце, третий источник 29 положительного опорного напряжения, четвертый источник 30 отрицательного опорного напряжения, проекционный объектив 31, матовый экран 32, ИК-передатчик 33, расположенный над экраном 32, ИК-приемник 34 на оправе ЗД-очков 35.

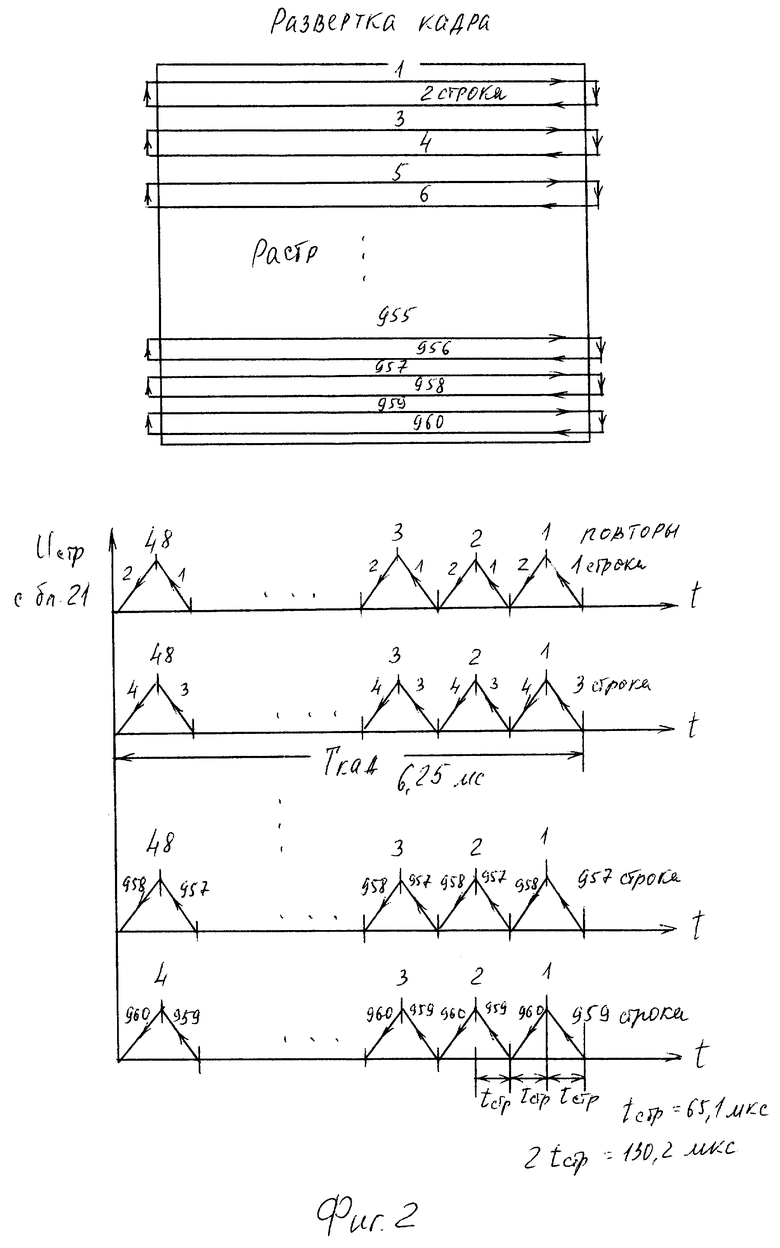

АЦП 2, 3, 4 идентичны, каждый содержит /фиг.3/ последовательно соединенные видеоусилитель 36 и пьезодефлектор 37 о отражателем на торце, источник 38 положительного опорного напряжения, источник 39 отрицательного опорного напряжения, излучатель из импульсного светодиода 40, щелевой диафрагмы 41 и микрообъектива 42, линейку 43 многоэлементного фотоприемника и шифратор 44, являющийся выходом АЦП.

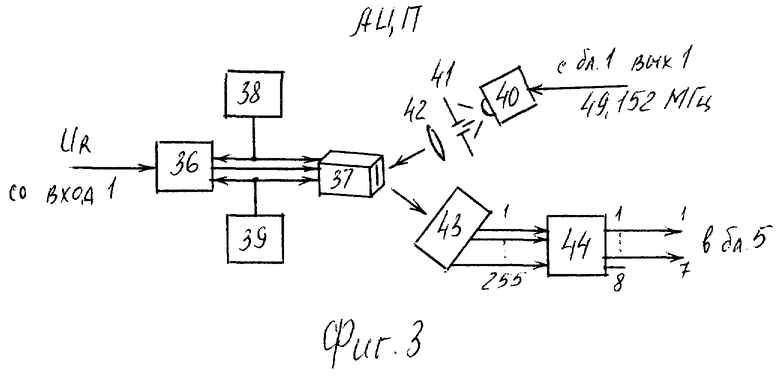

Блоки 5, 6, 7 обработки кодов идентичны, каждый включает /фиг.4/ триггер 45, первый 46, второй 47 блоки ключей, первый 48, второй 49, третий 50, четвертый 51 регистры, сумматор 52, первый 53 и второй 54 блоки задержек и 14 диодов. Блоки 53, 54 выполняют задержку кодов на 20 нс.

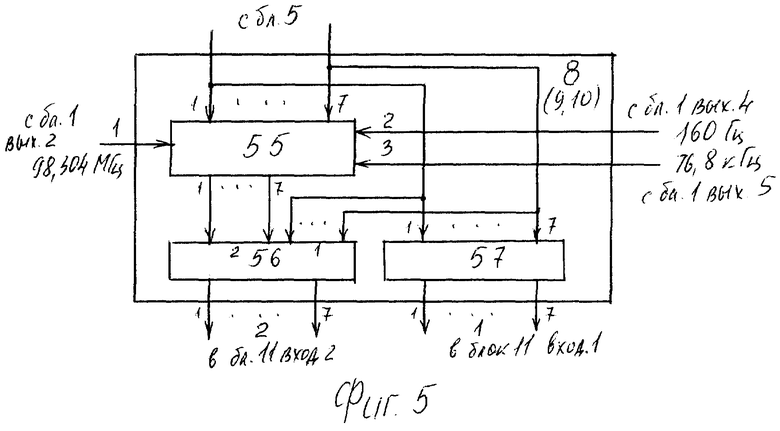

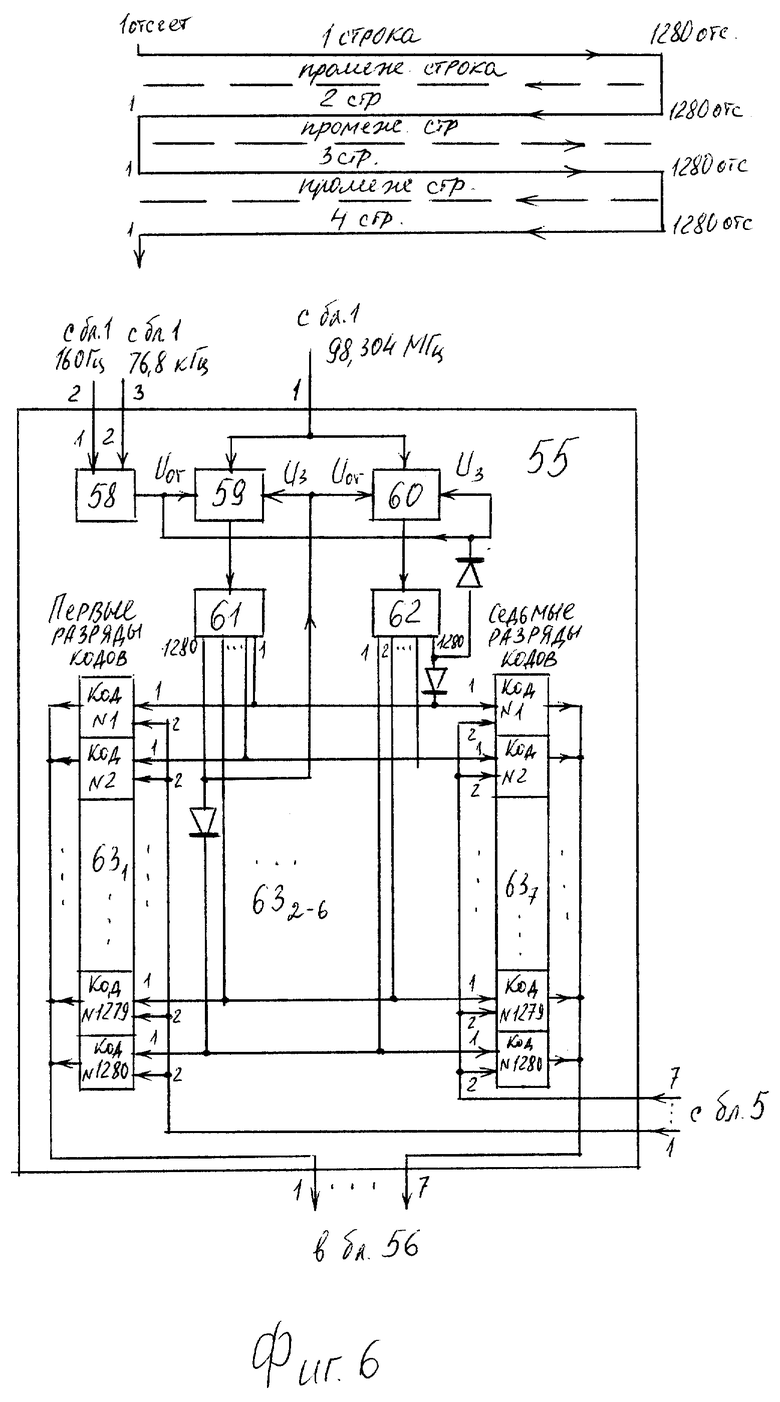

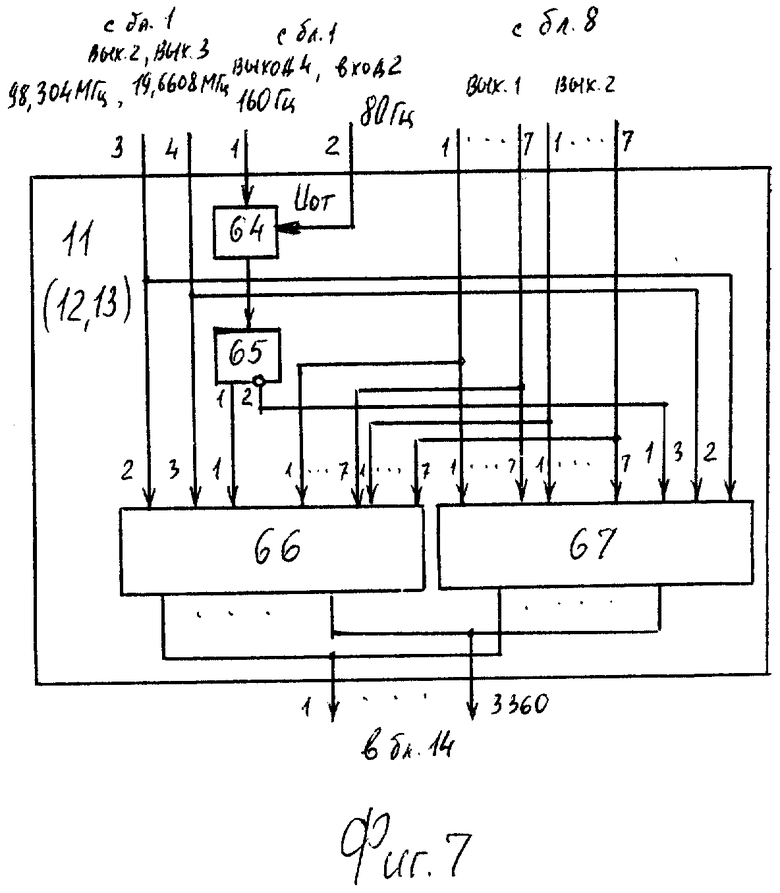

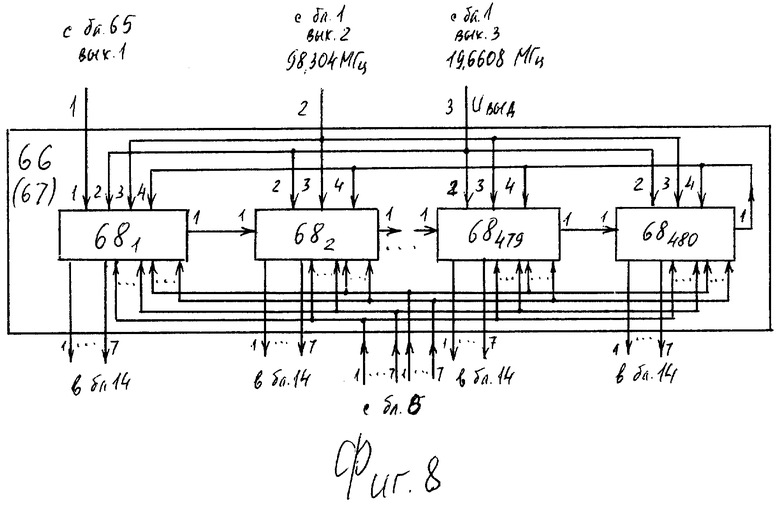

Блоки 8, 9, 10 удвоения строк /фиг.5/ идентичны, каждый включает последовательно соединенные первый блок 55 задержек и сумматор 56 и второй блок 57 задержек. Первые блоки 55 задержек идентичны /фиг.6/, каждый включает последовательно соединенные элемент И 58 и первый ключ 59, второй ключ 60, первый 61, второй 62 распределители импульсов и семь регистров 631-7, каждый на 1280 разрядов. Блок 55 задерживает коды на длительность строки 13,02 мкс / /. Накопители 11, 12, 13 кодов идентичны /фиг.7/, каждый включает ключ 64, триггер 65, накопитель 66 кодов нечетного кадра /левого/, накопитель 67 кодов четного кадра /правого/. Первым и вторым информационными выходами блоков 11, 12, 13 являются поразрядно объединенные первые 1-7 и вторые 1-7 входы накопителя 66 и 67, подключенные к первому и второму выходам соответственно блоков 8, 9, 10 удвоения строк. Управляющими входами являются: первым - сигнальный вход ключа 64, подключенный к выходу 4 синтезатора 1 частот, вторым - управляющий вход ключа 64, подключенный к второму входу синтезатора 1 частот, третьим - объединенные вторые управляющие входы накопителей 66 и 67, четвертым - объединенные третьи управляющие входы накопителя 66 кодов нечетного кадра и накопителя кодов 67 четного кадра. Третий управляющий вход подключен к выходу 1 синтезатора 1 частот, четвертый подключен к выходу 3 синтезатора 1 частот. Первый управляющий вход накопителя 66 кодов подключен к первому выходу триггера 65, первый управляющий вход накопителя 67 кодов подключен к второму выходу триггера 65. Выходы блоков 66, 67 поразрядно объединены и являются 1-3360 выходами накопителя 11 /12, 13/ кодов, подключены к входам блока 14 /15, 16/ импульсных усилителей. Накопитель 66 кодов нечетного кадра и накопитель 67 кодов четного кадра идентичны /фиг.8/. Каждый включает по числу строк /480/ блоки 681-480 регистров. Первым и вторым информационными входами блока 66 /67/ являются первые 1-7 и вторые 1-7 входы, подключенные к выходам 1 и 2 блока 8 /9, 10/ удвоения отрок. Блок 66 производит накопление кодов нечетных /левых/ кадров, блок 67 производит накопление кодов четных /правых/ кадров. Блоки 681-480 регистров идентичны /фиг.9 и 10/, каждый включает первый 69, второй 70, третий 71, четвертый 72 ключи, первый 73, второй 74, третий 75, четвертый 76 распределители импульсов, первые семь регистров 771-7, первый счетчик 78 импульсов и первый дешифратор 79, вторые семь регистров 801-7, второй счетчик 81 импульсов и второй дешифратор 82 и триггер 83. Первым и вторым информационными входами блока 68 регистров являются объединенные поразрядно первые /информационные/ входы разрядов первых семи регистров 771-7 и объединенные поразрядно первые /информационные/ входы разрядов вторых семи регистров 801-7. Выходы разрядов в каждом регистре объединены и являются 1-7 выходами блока 68 регистров. Управляющих входов четыре: первым являются объединенные первые управляющие входы первого 69 и третьего 71 ключей, подключенные к первому выходу триггера 65 в блоке 11 /фиг.7/, вторым - объединенные сигнальные входы второго 70 и четвертого 72 ключей, подключенные к третьему выходу блока 1, третьим - объединенные сигнальные входы ключей 69 и 71, подключенные к первому выходу блока 1, четвертым - объединенные первый управляющий вход ключа 70, второй управляющий вход ключа 72 и второй выход триггера 83, подключенные через диод к первому управляющему выходу блока 68 480 регистров.

/. Накопители 11, 12, 13 кодов идентичны /фиг.7/, каждый включает ключ 64, триггер 65, накопитель 66 кодов нечетного кадра /левого/, накопитель 67 кодов четного кадра /правого/. Первым и вторым информационными выходами блоков 11, 12, 13 являются поразрядно объединенные первые 1-7 и вторые 1-7 входы накопителя 66 и 67, подключенные к первому и второму выходам соответственно блоков 8, 9, 10 удвоения строк. Управляющими входами являются: первым - сигнальный вход ключа 64, подключенный к выходу 4 синтезатора 1 частот, вторым - управляющий вход ключа 64, подключенный к второму входу синтезатора 1 частот, третьим - объединенные вторые управляющие входы накопителей 66 и 67, четвертым - объединенные третьи управляющие входы накопителя 66 кодов нечетного кадра и накопителя кодов 67 четного кадра. Третий управляющий вход подключен к выходу 1 синтезатора 1 частот, четвертый подключен к выходу 3 синтезатора 1 частот. Первый управляющий вход накопителя 66 кодов подключен к первому выходу триггера 65, первый управляющий вход накопителя 67 кодов подключен к второму выходу триггера 65. Выходы блоков 66, 67 поразрядно объединены и являются 1-3360 выходами накопителя 11 /12, 13/ кодов, подключены к входам блока 14 /15, 16/ импульсных усилителей. Накопитель 66 кодов нечетного кадра и накопитель 67 кодов четного кадра идентичны /фиг.8/. Каждый включает по числу строк /480/ блоки 681-480 регистров. Первым и вторым информационными входами блока 66 /67/ являются первые 1-7 и вторые 1-7 входы, подключенные к выходам 1 и 2 блока 8 /9, 10/ удвоения отрок. Блок 66 производит накопление кодов нечетных /левых/ кадров, блок 67 производит накопление кодов четных /правых/ кадров. Блоки 681-480 регистров идентичны /фиг.9 и 10/, каждый включает первый 69, второй 70, третий 71, четвертый 72 ключи, первый 73, второй 74, третий 75, четвертый 76 распределители импульсов, первые семь регистров 771-7, первый счетчик 78 импульсов и первый дешифратор 79, вторые семь регистров 801-7, второй счетчик 81 импульсов и второй дешифратор 82 и триггер 83. Первым и вторым информационными входами блока 68 регистров являются объединенные поразрядно первые /информационные/ входы разрядов первых семи регистров 771-7 и объединенные поразрядно первые /информационные/ входы разрядов вторых семи регистров 801-7. Выходы разрядов в каждом регистре объединены и являются 1-7 выходами блока 68 регистров. Управляющих входов четыре: первым являются объединенные первые управляющие входы первого 69 и третьего 71 ключей, подключенные к первому выходу триггера 65 в блоке 11 /фиг.7/, вторым - объединенные сигнальные входы второго 70 и четвертого 72 ключей, подключенные к третьему выходу блока 1, третьим - объединенные сигнальные входы ключей 69 и 71, подключенные к первому выходу блока 1, четвертым - объединенные первый управляющий вход ключа 70, второй управляющий вход ключа 72 и второй выход триггера 83, подключенные через диод к первому управляющему выходу блока 68 480 регистров.

Блок 17 модуляции излучений /фиг.11/ выполнен из 480 каналов, каждый включает последовательно расположенные излучатель 84 трех основных цветов R, G, B, микрообъектив 85 и фокусирующий конус световода 86 /фокон/ [3, с.77]. Входами блока 17 являются входы излучателей 841-480, подключенные к выходам блоков 14, 15, 16 импульсных усилителей, выходами являются излучения 480 выходных окон фоконов 861-480. Микрообъективы 85 вводят излучения излучателей 84 во входные окна фоконов 86. 480 фоконов образуют вертикальную линейку, а выходные их окна формируют на отражателе пьезодефлектора 28 /фиг.11/ 480 цветовых кругов, каждый диаметром 0,02 мм. Выходные окна фоконов 86 расположены по вертикали с шагом в размер диаметра 0,02 мм, поэтому на отражателе пьезодефлектора 28 проекции кругов расположены с шагом 0,02 мм. При развертке 480 строк слева направо /фиг.2/ на отражатель пьезодефлектора 28 проецируются фоконами 86 круги излучений нечетных строк растра, при развертке строк справа налево отражатель пьзодефлектора 28 по управляющему сигналу с блока 27 /фиг.1/ смещается на шаг в 0,02 мм с наклоном вниз, и круги излучений четных строк проецируются фоконами в промежутки между кругами от нечетных строк /фиг.2/. Длина отражателя пьезодефлектора 28 составляет 19,2 мм /480×0,02 мм/. Излучающая плоскость излучателя 84 находится в задней фокальной плоскости объектива 85, в передней фокальной плоскости которого расположено входное окно фокона 86. Излучающие стороны излучателей 84 через микрообъективы 85, фоконы 86, отражатель пьезодефлектора 28 оптически соединены с отражателем первого пьезодефлектора 23. Каждый излучатель является матрицей из 21 светодиода. В составе матрицы 7 светодиодов красного излучения, 7 - зеленого и 7 - синего. Свободный торец с отражателем пьезодефлектора 28 совершает колебательные движения с амплитудой 0,02 мм по управляющему импульсу с второго усилителя 27, который формирует управляющие сигналы по амплитуде и длительности, частота управляющих сигналов 7,68 кГц. Блок 26 производит деление частоты 76,8 кГц 10:1, на вход усилителя 27 поступают импульсы 7,68 кГц длительности, равной длительности строки 65,1 мкс /форма сигналов меандр/. Пьезодефлекторы 23 и 28 идентичны /фиг.12/, являются торцевыми из двух биморфных пьезопластин и светового отражателя на свободном торце. Конструктивно выполнены [4, с.118] из первой 87 и второй 88 пьезопластин, внутреннего электрода 89, первого 90 и второго 91 внешних электродов, один конец пьезопластин жестко закреплен в держателе 92, на свободном торце закреплен отражатель 93. Пьезодефлектор 23 выполняет строчную развертку одновременно 480 строк. Делитель 18 частоты выполняет деление частоты 76,8 кГц 10:1. На вход задающего генератора 20 в блоке 16 поступают импульсы 7,68 кГц. Блок 20 формирует управляющие прямоугольные импульсы с периодом следования двух строк /65,1 мкс×2/ 130,2 мкс, которые поступают в выходной каскад 21, формирующий управляющее напряжение треугольной формы /фиг.2/ с периодом 130,2 мкс, поступающее на вход усилителя 22, усиливающего управляющее напряжение до необходимой величины, которое поступает на внутренний электрод 89 пьезодефлектора 23 /фиг.12/. На внешние электроды 90, 91 поступают соответствующие опорные напряжения с первого 24 и второго 25 источников опорных напряжений, торец пьезодефлектора 23 с отражателем приходит в колебательное движение [4, с.122] с частотой 7,68 кГц и производит развертку нечетных 460 отрок слева направо и 480 четных строк при движении справа налево /фиг.2/. За период кадра 6,25 мс пьезодефлектор 23 выполняет 96 повторов разверток параллельно 480 строк: 48 разверток слева направо нечетных строк и 48 разверток справа налево четных строк /65,1 мкс×96=6,25 мс/. Отражатель пьезодефлектора 23 расположен в задней фокальной плоскости проекционного объектива 31, являющегося широкоугольным для сокращения расстояния до экрана. Матовый экран 32 расположен во внешней фокальной плоскости проекционного объектива 31, проецирующего на экран 32 изображения последовательно левого и правого кадров, изображение с экрана воспринимается зрителем объемным через ЗД-очки 35 [2, с.558-563, 565]. При воспроизведении последовательно левого и правого кадров стекла ЗД-очков поочередно теряют прозрачность, каждый глаз видит только свой кадр, что и дает стереоэффект. Стекла ЗД-очков выполнены по технологии ЖК-ячеек просветного типа, используемые как электронно-управляемые фильтры /затворы/. С приходом синхроимпульса стереопары 80 Гц в ИК-передатчик 33 он излучает ИК-импульс длительностью 6,25 мс, длительность кадра, принимаемый ИК-приемником 34 /фиг.1/, расположенным на оправе ЗД-очков. ИК-приемник 34 выдает управляющий сигнал в ЖК-ячейку правого стекла, затемняя его на 6,25 мс, затем выдает второй управляющий сигнал в ЖК-ячейку левого стекла, затемняя его прозрачность на 6,25 мс. Каждый глаз видит свой кадр. Прозрачность ЖК-ячеек в открытом состоянии менее 100%, отсюда необходимость в увеличении яркости изображения на экране 32. С этой целью применяется развертка кадра на экране одновременно 480 строками с повторением 96 раз, позволяющая повысить яркость изображения для глаза зрителя в 46080 раз /960стр×48/. Частота дискретизации кодов АЦП 2, 3, 4 составляет:

480строк×640отсч×160 Гц=49,152 МГц.

где: 160 Гц - частота кадров /80 левых + 80 правых/,

640 - число отсчетов в строке при видеорежиме

640×480×160.

С видеоадаптера РС на первый вход блока 1 монитора поступает fP рабочая частота, на второй вход блока 1 монитора поступают синхроимпульсы стереопары 80 Гц. Синтезатор 1 частот выдает: с первого выхода импульсы дискретизации 49,152 МГц, поступающие в три АЦП и блоки 5, 6, 7 /вход 1/, с второго выхода - импульсы удвоенной частоты дискретизации 98,304 МГц в блоки 8, 9, 10 /вход 1/, с третьего - сигналы Uвыд в блоки 11, 12, 13 /вход 4/ 19,6608 МГц, с четвертого - импульсы кадров 160 Гц в блоки 11, 12, 13 /вход 1/, с пятого выхода - импульсы, частотой 76,8 кГц в блоки 8, 9, 10 /вход 3/, в блок 18 и 26. Аналоговые видеосигналы R, G, B с видеоадаптера PC последовательно левого и правого кадров поступают на 1, 2, 3 информационные входы цифрового монитора и с них на информационные входы соответственно АЦП 2, АЦП 3, АЦП 4. АЦП 2, 3, 4 преобразуют аналоговые цветовые сигналы в 8-разрядные двоичные коды с частотой дискретизации 49,152 МГц, которые поступают на управляющий вход АЦП /импульсный светодиод/, фиг.3. С выходов АЦП коды видеосигналов в параллельном виде с 1 по 7 разряды /младший 8 разряд опускается/ поступают на информационные 1-7 входы соответственно блоков 5, 6, 7. Выход восьмого разряда кода не используется ввиду его малой значимости /0,39% при излучении/. АЦП имеют один принцип преобразования, заключающийся в развертке луча /фиг.3/ от импульсного светодиода 40 отражателем пьезодефлектора 37 по плоскости входных зрачков фотоприемников линейки 43, в которой световой сигнал преобразуется в электрический, возбуждающий соответствующую шину шифратора 44, выдающего 8-разрядный код мгновенного значения входного сигнала в параллельном виде. Преобразование выполняется с частотой 49,152 МГц. Источником излучения принят импульсный светодиод с временем срабатывания до 20 нс. Линейка 43 содержит 255 фотоприемников для кодирования видеосигнала 8-разрядным кодом. Фотоприемниками являются лавинные фотодиоды ЛФД с временем срабатывания 10 нс. Шифратор является микросхемой К155ИВ1 с временем срабатывания 20 нс [5, c.231]. Шифратор 44 формирует коды c 00000001 по 11111111. Первому фотоприемнику линейки 43 соответствует код 00000001, второму - код 00000010, третьему - код 00000011 и т.д., 255-у - код 11111111. Коды с шифратора АЦП поступают в параллельном виде /без младшего разряда/ на информационный вход блока 5 /6, 7/ обработки кодов /фиг.4/, а в блоке 5 на информационные входы блока 46 ключей. Блок 5 выполняет удвоение отсчетов в строке с 640 до 1280.

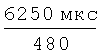

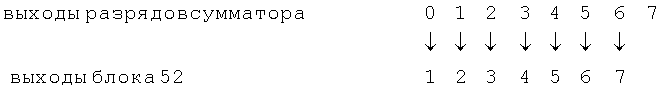

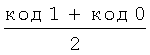

Удвоение отсчетов выполняется получением кодов промежуточных /средних/ отсчетов между каждым прошедшим и последующим отсчетами: в блоке производится сложение предыдущего кода с последующим и деление суммы пополам. Каждый код используется дважды: первый раз как последующий, второй раз как предыдущий, поэтому блок 5 имеет четыре регистра 48, 49, 50, 51. С поступлением первого импульса 49,152 МГц на вход триггера 45 импульс Uвыд1 открывает ключи в блоке 46, выдает "код 0" с второго регистра 49 на первые входы сумматора 52 и "код 0" с регистра 50 в блок 54 задержек и через диоды на вторые входы сумматора 52. А регистры 48, 49 заполняются первым кодом "код 1". Сумматор 52 производит сложение кодов, выполнен из микросхем К500ИМ180 [5, с.440] с временем сложения 10 нс. По окончании сложения сумматор 52 обнуляется импульсом U0, он же и выдает код суммы на выход, деление кода суммы выполняется сдвигом кода на один разряд так, что младший разряд кода суммы отбрасывается. Сдвиг на один разряд выполняется соответствующим подключением выходов разрядов сумматора к выходам самого блока 52:

Разряд 0 означает перенос в старший разряд при сумме кодов. После удвоения отсчетов в строке с 640 до 1280 период следования кодов составляет 10 нс  , это времясоответствует времени сложения кодов сумматором 52. По истечении 10 нс сложения с выхода блока 52 следует код №1

, это времясоответствует времени сложения кодов сумматором 52. По истечении 10 нс сложения с выхода блока 52 следует код №1  .

.

Через 10 нс за кодом №1 следует код с блока 54 задержек код №2, это ″код 0″. Блоки 53 и 54 выполняют задержку кодов на 20 нс.

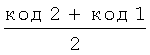

Первая половина задержки /10 нс/ приходится на сложение в сумматоре 52, вторая половина задержки /10 нс/ является периодом следования кодов после удвоения отсчетов. С приходом второго импульса в триггер 45 сигнал Uвыд2 со второго выхода триггера открывает ключи в блоке 47, выдает "код 0" с регистра 51 в сумматор и ″код 1″ с регистра 48 в блоки 53 задержек и через диоды в сумматор 52. Регистры 50 и 51 заполняются кодом ″код 2″. Следует сложение, деление кода суммы пополам, и код №3  следует на выход. Через 10 нс за ним следует с блока 53 код №4 "код 1". С приходом третьего импульса в триггер 45 сигнал Uвыд3 /он же Uвыд1/ с первого выхода триггера открывает ключи в блоке 46, выдает "код 1" с регистра 49 в сумматор 52, выдает "код 2" с регистра 50 в блок 54 задержек и через диоды в сумматор. Регистры 48, 49 заполняются кодом "код 3". Идет сложение и деление, и код №5

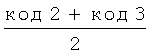

следует на выход. Через 10 нс за ним следует с блока 53 код №4 "код 1". С приходом третьего импульса в триггер 45 сигнал Uвыд3 /он же Uвыд1/ с первого выхода триггера открывает ключи в блоке 46, выдает "код 1" с регистра 49 в сумматор 52, выдает "код 2" с регистра 50 в блок 54 задержек и через диоды в сумматор. Регистры 48, 49 заполняются кодом "код 3". Идет сложение и деление, и код №5  следует на выход. Через 10 нс за ним с блока 54 идет код №6 ″код 2″. С приходом 4-го импульса в триггер 45, сигнал Uвыд4 /он же Uвыд2/ с второго выхода триггера открывает ключа в блоке 47, выдает "код 2" с регистра 51, "код 3" с регистра 48 в блок 53 задержек и через диоды в сумматор 52. Регистры 50, 51 заполняются кодом "код 4". Идет сложение и деление, и код №7

следует на выход. Через 10 нс за ним с блока 54 идет код №6 ″код 2″. С приходом 4-го импульса в триггер 45, сигнал Uвыд4 /он же Uвыд2/ с второго выхода триггера открывает ключа в блоке 47, выдает "код 2" с регистра 51, "код 3" с регистра 48 в блок 53 задержек и через диоды в сумматор 52. Регистры 50, 51 заполняются кодом "код 4". Идет сложение и деление, и код №7  следует на выход, за ним через 10 нс следует с блока 53 код №8 ″код 3″. С приходом 5-го импульса и последующих в триггер 45 процессы повторяются. Выходы сумматора 52 и блоков 53, 54 задержек поразрядно объединены и являются выходом блока 5. С выхода блока 5 коды в параллельном виде поступают на входы первого блока 55 задержек в блоке 8, 9, 10 удвоения строк, на входы второго блока 57 задержек и на первые входы сумматора 56. Блок 55 выполняет задержку кодов строки на длительность строки /13,02 мкс/ и участвует в формировании отсчетов промежуточных строк. Так как развертка нечетных строк и четных в растре идет встречно /фиг.6/, то для получения нечетных промежуточных строк необходимо выдавать коды в сумматор 56 в последовательности с последнего кода /1280-го/ в строке к первому, а при получении четных промежуточных строк выдавать коды с блока 55, начиная с первого кода строки к последнему, при развертке первой строки растра в блоке 55 открывается первый ключ 59 /фиг.6/, импульсы двойной частоты дискретизации 98,304 МГц поступают в первый распределитель 61 импульсов, выдающий тактовые импульсы с 1-го по 1280 последовательности на первые управляющие входы, начиная с первых разрядов регистров 631-7 к 1280 разрядам, при развертке первой строки кадра регистры 631-7 заполняются кодами первой строки: первые разряды кодов поступают в регистр 631, вторые разряды кодов поступают в регистр 632, третьи разряды кодов поступают в регистр 633..., седьмые разряды кодов поступают в регистр 637. Импульс с последнего 1280-го выхода блока 61 закрывает ключ 59, открывает ключ 60. На вход второго распределителя 62 импульсов поступают импульсы 98,304 МГц. Выходы с распределителя 62 импульсов подключены к первым управляющим входам разрядов регистров 631-7 в обратном порядке: первый выход подключен к последнему 1280-м разрядам, а последний выход /1280/ подключен к первым разрядам регистров 631-7. При развертке второй строки кадра импульсы с выходов второго распределителя 62 импульсов выдают на вторые входы сумматора 56 коды задержанной первой строки в последовательности с 1280 кода к первому, соответственно следованию отсчетов при развертке второй текущей строки кадра. Сумматор 56 формирует первую промежуточную строку. Освобождающиеся разряды регистров 631-7, заполняются кодами отсчетов второй /текущей/ строки в порядке с 1280 кода к 1-у. Импульс с последнего выхода /1280/ распределителя 62 закрывает ключ 60 и открывает ключ 59. Следует развертка третьей строки /текущей/, при которой коды второй строки выдаются из регистров 63 в сумматор 56, начиная с 1-го кода к 1280-у. Сумматор 56 формирует /фиг.5/ вторую промежуточную строку. Далее процессы повторяются. Коды с выходов сумматоров 56 блоков 8, 9, 10 являются кодами 640 промежуточных строк. Вторые блоки задержек 57 в блоках 8, 9, 10 выполняют задержку кодов текущих строк на 10 нс, на время срабатывания сумматоров 56, чтобы коды текущих строк с блока 57 и коды промежуточных строк с блока 56 приходили на входы накопителей 11, 12, 13 кодов синхронно и синфазно.

следует на выход, за ним через 10 нс следует с блока 53 код №8 ″код 3″. С приходом 5-го импульса и последующих в триггер 45 процессы повторяются. Выходы сумматора 52 и блоков 53, 54 задержек поразрядно объединены и являются выходом блока 5. С выхода блока 5 коды в параллельном виде поступают на входы первого блока 55 задержек в блоке 8, 9, 10 удвоения строк, на входы второго блока 57 задержек и на первые входы сумматора 56. Блок 55 выполняет задержку кодов строки на длительность строки /13,02 мкс/ и участвует в формировании отсчетов промежуточных строк. Так как развертка нечетных строк и четных в растре идет встречно /фиг.6/, то для получения нечетных промежуточных строк необходимо выдавать коды в сумматор 56 в последовательности с последнего кода /1280-го/ в строке к первому, а при получении четных промежуточных строк выдавать коды с блока 55, начиная с первого кода строки к последнему, при развертке первой строки растра в блоке 55 открывается первый ключ 59 /фиг.6/, импульсы двойной частоты дискретизации 98,304 МГц поступают в первый распределитель 61 импульсов, выдающий тактовые импульсы с 1-го по 1280 последовательности на первые управляющие входы, начиная с первых разрядов регистров 631-7 к 1280 разрядам, при развертке первой строки кадра регистры 631-7 заполняются кодами первой строки: первые разряды кодов поступают в регистр 631, вторые разряды кодов поступают в регистр 632, третьи разряды кодов поступают в регистр 633..., седьмые разряды кодов поступают в регистр 637. Импульс с последнего 1280-го выхода блока 61 закрывает ключ 59, открывает ключ 60. На вход второго распределителя 62 импульсов поступают импульсы 98,304 МГц. Выходы с распределителя 62 импульсов подключены к первым управляющим входам разрядов регистров 631-7 в обратном порядке: первый выход подключен к последнему 1280-м разрядам, а последний выход /1280/ подключен к первым разрядам регистров 631-7. При развертке второй строки кадра импульсы с выходов второго распределителя 62 импульсов выдают на вторые входы сумматора 56 коды задержанной первой строки в последовательности с 1280 кода к первому, соответственно следованию отсчетов при развертке второй текущей строки кадра. Сумматор 56 формирует первую промежуточную строку. Освобождающиеся разряды регистров 631-7, заполняются кодами отсчетов второй /текущей/ строки в порядке с 1280 кода к 1-у. Импульс с последнего выхода /1280/ распределителя 62 закрывает ключ 60 и открывает ключ 59. Следует развертка третьей строки /текущей/, при которой коды второй строки выдаются из регистров 63 в сумматор 56, начиная с 1-го кода к 1280-у. Сумматор 56 формирует /фиг.5/ вторую промежуточную строку. Далее процессы повторяются. Коды с выходов сумматоров 56 блоков 8, 9, 10 являются кодами 640 промежуточных строк. Вторые блоки задержек 57 в блоках 8, 9, 10 выполняют задержку кодов текущих строк на 10 нс, на время срабатывания сумматоров 56, чтобы коды текущих строк с блока 57 и коды промежуточных строк с блока 56 приходили на входы накопителей 11, 12, 13 кодов синхронно и синфазно.

Работа накопителей 11, 12, 13 кодов /фиг.7, 8/.

При развертке первого кадра синхроимпульс стереопары со второго управляющего входа цифрового монитора открывает в накопителе 11 /12, 13/ кодов ключ 64 /на время всего процесса работы/ и кадровый импульс /160 Гц/, принадлежащий левому кадру, поступает на вход триггера 65, с первого выхода которого он запускает в работу накопитель 66 кодов нечетного кадра. С приходом в триггер 65 второго кадрового импульса, являющегося импульсом правого кадра, сигнал со второго выхода триггера 65 запускает в работу накопитель 67 кодов четного кадра.

В блоке 66 сосредотачиваются коды каждого нечетного кадра /левого/, в блоке 67 сосредотачиваются коды каждого четного кадра, т.е. правого. Блоки 66, 67 каждый /фиг.8, 9/ включает по 480 блоков 68 1-480 регистров, которые, в свою очередь, каждый содержит первые семь регистров 77 1-7 и вторые семь регистров 80 1-7. В первом периоде кадра блок 66 накапливает коды 960 строк первого кадра, во втором периоде кадра идет выдача со всех блоков 68 1-480 /фиг.8/ кодов одновременно 480 нечетных строк и следом 480 четных строк, которая повторяется по 48 раз и тех и других. В это же время /в периоде второго кадра/ блок 67 накапливает коды 960 строк второго кадра /правого/. В третий период кадра следует выдача кодов с блока 67 и идет накопление кодов 960 строк третьего кадра блоком 66, и так чередуясь, процесс повторяется.

Блоки 68 регистров работают следующим образом. Все ключи блоков 68 в исходном состоянии закрыты. С приходом на вход триггера 65 /фиг.7/ первого кадрового импульса /левого кадра/ с 1-го выхода триггера 65 импульс открывает первый ключ 69 /фиг.9/ и третий ключ 71, которые пропускают частоту 49,152 МГц в распределители 73 и 75 импульсов. С выходов этих блоков тактовые сигналы Uт последовательно поступают на первые управляющие входы разрядов резисторов 771-7 и 801-7. На информационные /первые/ входы которых поступают сигналы кодов строки с блока 8 /9, 10/, причем коды с первого выхода блока 8 поступают в разряды регистров 77, а коды со второго выхода блока 8 /9, 10/ поступают в разряды регистров 801-7, т.е. регистры 77 заполняются кодами текущих строк с блока 57, а регистры 80 заполняются кодами промежуточных строк с блока 56. По окончании периода строки регистры 77 и 80 заполнены 1280 кодами первой строки. Импульс с 1280-го выхода блока 73 закрывает ключ 69 и является первым управляющим выходом /фиг.9/ в следующий блок 682, сигнал которого открывает те же ключи 69, 71 во втором блоке 682 /фиг.10/ и в нем следует идентичный процесс заполнения кодами второй строки регистров 771-7, 801-7. Аналогично идет заполнение кодами 3...960 строк регистров 77, 80 в блоках 683-480. В результате блок 66 сосредотачивает коды 960 строк первого кадра. С приходом на вход триггера 65 /фиг.7/ второго кадрового импульса /правого кадра/ импульс с второго выхода триггера 65 открывает ключи 69, 71 в блоке 68 накопителя 67 кодов четного кадра /правого/, и в нем идут идентичные процессы накопления кодов 960 строк правого кадра стереопары. В это же время управляющий сигнал с управляющего выхода 1 блока 68480 в накопителе 66 /фиг.8/ поступает параллельно на четвертые управляющие входы всех блоков 681-480 и открывает в них ключи 70, 72, которые пропускают на входы распределителей 74, 76 импульсов сигналы Uвыд 19,6608 МГц. Выходы блока 74 подключены к вторым управляющим входам разрядов регистров 771-7 в последовательности с 1-го по 1280: первый выход к вторым управляющим входам первых разрядов регистров 77, последний выход /1280/ к вторым управляющим входам последних разрядов регистров 77. Развертка 480 нечетных строк идет слева направо /фиг.2/, выдача кодов выполняется одновременно с регистров 771-7 всех 480 блоков 68 /фиг.8/. При обратном повороте отражателя пьезодефлектора 23 /справа налево/ идет развертка 460 четных строк, выдача кодов идет параллельно с регистров 801-7 всех 480 блоков 681-480 /фиг.8/. А коды с регистров 80 выдаются, начиная с 1280-х разрядов регистров к 1-м разрядам, и выходы распределителя 76 импульсов подключены к вторым управляющим входам разрядов регистров 801-7 в обратном порядке: первый выход подключен к последним разрядам /1280/, а последний выход подключен к первым разрядам регистров 80 /фиг.9, 10/. За период колебания пьезодефлектор 23 выполняет развертку двух строк: первая нечетная при развертке слева направо, вторая четная при развертке справа налево. Длительность отроки 65,1 мкс  , 96 - частота повторения строк. Делитель 18 частоты выполняет деление 10:1 частоты 76,8 кГц. На вход задающего генератора 20 /фиг.1/ поступает частота 7,68 кГц. Развертка всех строк выполняется за кадр 96 раз: 48 раз слева направо и 48 раз справа налево, повтор по 48 раз задается счетчиками 78, 81 импульсов и дешифраторами 79, 82. В конце каждой строки сигнал с 1280 выхода блока 74 /76/ в качестве счетного импульса поступает в счетчик 78 /81/. После 48 разверток счетчик формирует код 110000, который дешифрируется дешифратором 79, 82, выходной сигнал с дешифратора обнуляет разряды регистров 77, 80, подготавливая их к заполнению кодами следующего кадра. Смену последовательности выдачи кодов от строки к строке задает триггер 83. Вход его через диоды подключен к 1280-м выходам блоков 74, 76. Первый выход триггера 83 подключен к второму управляющему входу ключа 70 и первому управляющему входу ключа 72, второй выход триггера подключен к первому управляющему входу ключа 70 и к второму управляющему входу ключа 72. Каждый накопитель 11, 12, 13 кодов выдает в параллельном виде коды 480 строк с 1-3360 выходов /480×7/. Коды с блока 11 поступают в блок 14 импульсных усилителей, с блока 12 в блок 15, с блока 13 в блок 16 импульсных усилителей. Каждый из блоков импульсных усилителей включает по 3360 импульсных усилителей с временем срабатывания до 10 нс К531АП4П [5, с.128]. Соответствующие выходы блоков 14, 15, 16 подключены к входам своих излучателей в блоке 17 модуляции излучений /фиг.1/. Каждый излучатель 84 включает 21 светодиод, из которых 7 - красного излучения, 7 - зеленого и 7 - синего излучения. Для излучения светодиод запитывается импульсным сигналом со своего импульсного усилителя. 480 излучателей содержат 10080 светодиодов /480×21/. Исключение 8-го разряда из кодов ввиду его весовой незначительности 0,39% /табл.1/ позволяет сократить в блоках 14, 15, 16, 1440 штук импульсных усилителей /480×3/, в блоке 17 сократить 1440 светодиодов /480×3/ и определенное число регистров в блоках 681-480. Блок 17 выполняет яркостную модуляцию излучений 480-ю излучателями 84 /фиг.11/, в которых применяются светодиоды типа HL МР компании "Хьюлетт-паккард" [6, с.71]. Для красного излучения применяются светодиоды HL MP-AL00 с силой света 0,4 кд, длиной волны 0,56 мкм при токе 0,02 A [6, c.71], для зеленого - светодиоды HL MP-АМ00 с силой света 0,8 кд, длиной волны 0,526 мкм при токе 0,02 А, для синего излучения светодиоды HL MP-AB00 с силой света 0,3 кд, длиной волны 0,475 мкм при токе 0,02 А. Яркостная модуляция излучений выполняется включением на излучение числа светодиодов в излучателе 84 соответственно весу разряда в коде по таблице 1.

, 96 - частота повторения строк. Делитель 18 частоты выполняет деление 10:1 частоты 76,8 кГц. На вход задающего генератора 20 /фиг.1/ поступает частота 7,68 кГц. Развертка всех строк выполняется за кадр 96 раз: 48 раз слева направо и 48 раз справа налево, повтор по 48 раз задается счетчиками 78, 81 импульсов и дешифраторами 79, 82. В конце каждой строки сигнал с 1280 выхода блока 74 /76/ в качестве счетного импульса поступает в счетчик 78 /81/. После 48 разверток счетчик формирует код 110000, который дешифрируется дешифратором 79, 82, выходной сигнал с дешифратора обнуляет разряды регистров 77, 80, подготавливая их к заполнению кодами следующего кадра. Смену последовательности выдачи кодов от строки к строке задает триггер 83. Вход его через диоды подключен к 1280-м выходам блоков 74, 76. Первый выход триггера 83 подключен к второму управляющему входу ключа 70 и первому управляющему входу ключа 72, второй выход триггера подключен к первому управляющему входу ключа 70 и к второму управляющему входу ключа 72. Каждый накопитель 11, 12, 13 кодов выдает в параллельном виде коды 480 строк с 1-3360 выходов /480×7/. Коды с блока 11 поступают в блок 14 импульсных усилителей, с блока 12 в блок 15, с блока 13 в блок 16 импульсных усилителей. Каждый из блоков импульсных усилителей включает по 3360 импульсных усилителей с временем срабатывания до 10 нс К531АП4П [5, с.128]. Соответствующие выходы блоков 14, 15, 16 подключены к входам своих излучателей в блоке 17 модуляции излучений /фиг.1/. Каждый излучатель 84 включает 21 светодиод, из которых 7 - красного излучения, 7 - зеленого и 7 - синего излучения. Для излучения светодиод запитывается импульсным сигналом со своего импульсного усилителя. 480 излучателей содержат 10080 светодиодов /480×21/. Исключение 8-го разряда из кодов ввиду его весовой незначительности 0,39% /табл.1/ позволяет сократить в блоках 14, 15, 16, 1440 штук импульсных усилителей /480×3/, в блоке 17 сократить 1440 светодиодов /480×3/ и определенное число регистров в блоках 681-480. Блок 17 выполняет яркостную модуляцию излучений 480-ю излучателями 84 /фиг.11/, в которых применяются светодиоды типа HL МР компании "Хьюлетт-паккард" [6, с.71]. Для красного излучения применяются светодиоды HL MP-AL00 с силой света 0,4 кд, длиной волны 0,56 мкм при токе 0,02 A [6, c.71], для зеленого - светодиоды HL MP-АМ00 с силой света 0,8 кд, длиной волны 0,526 мкм при токе 0,02 А, для синего излучения светодиоды HL MP-AB00 с силой света 0,3 кд, длиной волны 0,475 мкм при токе 0,02 А. Яркостная модуляция излучений выполняется включением на излучение числа светодиодов в излучателе 84 соответственно весу разряда в коде по таблице 1.

Суммарное излучение светодиодов трех цветов R, G, В от излучателя 84 смешивается при фокусировке объективом 85 /фиг.11/ и вводится во входное окно фокона 86, который выводит излучение в форме круга диаметром 0,02 мм.

480 излучателей дают на отражателе пьезодефлектора 28 480 кругов. Яркость, насыщенность и цветовой тон результирующего цвета круга на отражателе определяется суммарной энергией и взаимным соотношением трех цветов. Суммарная сила света одного излучателя с учетом, что светодиоды всех цветов имеют силу света 0,3 кд /синего светодиода/ составляет:

3×0,3 кд/1+0,5+0,25+0,125+0,0625+0,03125+0,0156/=0,9 кд×1,98=1,782 кд.

где: 3 - число цветов в излучателе,

1...0,0156 - коэффициенты 1-7 двоичных разрядов кода.

Суммарная сила света от 480 излучателей: 1,782 кд×480=855,36 кд.

При 96 повторах строчных разверток за кадр:

855 кд×96=82080 кд.

С учетом потерь при проекции от излучателей до экрана 32 в 20 раз усредненная максимально возможная сила излучения составит: 820×80 кд:20=4104 кд.

Яркость изображения на экране 32 зависит от его размеров, т.e. удаленности экрана, принимая кратность увеличения изображения проекционным объективом 31 в 10 раз, размеры экрана составят:

по горизонтали 10·/0,04 мм×1280отсч/=512 мм,

по вертикали 10·/0,04 мм×960строк/=384 мм,

по диагонали 640 мм или 25 дюймов. 0,04 мм элемент разрешения на отражателе пьезодефлектора 23. Восприятие объемного изображения на экране 25′′ при силе излучения изображения в 4104 кд создаст пользователю индивидуального РС хорошее удовлетворение аппаратурой. Технические характеристики заявляемого цифрового монитора в таблице 2.

Работа цифрового монитора. Аналоговые видеосигналы трех световых сигналов левого и правого кадров стереопары поступают с видеоадаптера РС раздельно на 1-3 информационные входы монитора, на 1 и 2 управляющие входы которого поступают с РС рабочая частота /вход 1/ и синхроимпульсы стереопар /80 Гц/, вход 2. АЦП 2, 3, 4 преобразуют аналоговые видеосигналы в 8-разрядные коды цветовых сигналов R, G, В. Дискретизация преобразования 49,152 МГц. Коды с АЦП в параллельном виде поступают в блоки 5, 6, 7 обработки кодов, выполняющие удвоение числа отсчетов в строке. С выходов блоков 5, 6, 7 удвоенные по частоте коды поступают на входы блоков 8, 9, 10, выполняющие удвоение строк в кадре с 480 до 960. Блоки 8, 9, 10 имеют по два выхода: с первого на первый вход накопителя 11 /12, 13/ кодов следуют коды 480 нечетных строк кадра, со второго выхода на второй вход накопителя 11 /12, 13/ кодов следуют коды 480 четных строк кадра. Каждый накопитель 11, 12, 13 кодов содержит накопитель 66 кодов нечетного кадра и накопитель 67 кодов четного кадра.

После сосредоточения кодов нечетного /левого/ кадра в блоке 66 следует выдача кодов с блока 66 в блок 14 /15, 16/ импульсных усилителей. В период их выдачи идет накопление кодов следующего четного /правого/ кадра в блоке 67. В период следующего нечетного кадра идет выдача кодов из блока 67 в блок 14 /15, 16/ импульсных усилителей и накопление кодов нечетного кадра опять в блоке 66. Блок 17 модуляции излучений выполняет яркостную модуляцию соответственно величин кодов параллельно 480 строк. Излучение от 480 излучателей проецируется 480-й фокусирующими конусами световодов 86 на отражатель пьезодефлектора 28 с шагом в диаметр строки 0,02 мм, отражаясь с которого излучения строк поступают на отражатель пьезодефлектора 23, который выполняет строчную развертку одновременно 480 нечетных строк при повороте отражателя слева направо, при повороте отражателя справа налево выполняется развертка четных строк 480. Проецирование излучений фоконами 86 при четных строках выполняется в промежутки между нечетными строками /фиг.11/. Для этого отражатель пьезодефлектора 28 поворачивается на смещение излучений на 0,02 мм управляющим сигналом, поступающим на внутренний электрод 89 /фиг.12/ с усилителя 26. За кадр развертка всех строк повторяется 48 раз. На вход задающего генератора 20 в блоке 19 поступают импульсы 7,68 кГц. Задающий генератор 20 формирует управляющие прямоугольные импульсы с периодом следования 130,2 мкс /период длительности двух строк/, которые поступают в выходной каскад 21, формирующий управляющее напряжение треугольной формы /фиг.2/ с периодом 130,2 мкс, поступающее на вход усилителя 22 и с него на внутренний электрод 89 пьезодефлектора 23. На внешние электроды поступают напряжения с первого 24 и второго 25 источников опорных напряжений. Торец пьезодефлектора 23 с отражателем приходит в колебательное движение [4, с.122] с частотой 7,68 кГц и производит развертку 960 строк в задней фокальной плоскости проекционного объектива 31, который проецирует изображение кадра на матовый экран 32 с увеличением в 10 раз. Объемное изображение зритель воспринимает через ЗД-очки 35 с ИК-приемником 34 на оправе, который принимает управляющие сигналы с ИК-передатчика 33, расположенного над экраном 32. Управляющим сигналом для ИК-передатчика 33 является синхроимпульс стереопары 80 Гц, поступающий на вход ИК-передатчика со второго управляющего входа цифрового монитора.

Использованные источники

1. Патент №2248103, кл. Н 04 N 11/04, бюл. №7 за 2005 г., прототип.

2. Колесниченко О.В, Шишигин И.В. Аппаратные средства PC. 5-е изд, СПб, 2004, с.558-565.

3. Л.М.Кучекян. Световоды. М., 1973, с.77.

4. Фридлянд И.В., Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118, рис.5.5, с.122, рис.5.10.

5. Цифровые интегральные микросхемы, справочник, Минск, 1991, с.440, 231, 128.

6. "Радио" №7 за 1998 г., с.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ОБЪЕМНОЙ ВИДЕОЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ | 2006 |

|

RU2315439C1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2006 |

|

RU2310287C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2006 |

|

RU2303334C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2304362C2 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2003 |

|

RU2248103C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2326508C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2316142C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2004 |

|

RU2270529C1 |

Изобретение относится к аппаратным средствам персонального компьютера. Техническим результатом является получение в цифровом мониторе условий воспроизведения стереоэффекта, увеличение разрешающей способности кадра и увеличение усредненной яркости изображения. Технический результат достигается тем, что в цифровой монитор, содержащий синтезатор частот, три канала, в каждом из которых содержатся блок обработки кодов, накопитель кодов и блок импульсивных усилителей, блок модуляции излучений, блок строчной развертки, два пьезодефлектора, четыре источника опорных напряжений, проекционный объектив и матовый экран, введены ИК-передатчик, 3Д-очки с ИК-приемником на оправе очков, в каждый канал введены АЦП и блок удвоения строк. 12 ил., 2 табл.

Цифровой монитор, содержащий синтезатор частот, три канала, каждый из которых включает блок обработки кодов и последовательно соединенные накопитель кодов и блок импульсных усилителей, блок модуляции излучений, входы которого подключены к выходам блоков импульсных усилителей, последовательно соединенные первый делитель частоты, блок строчной развертки, первый усилитель и первый пьезодефлектор с отражателем на торце, первый источник положительного опорного напряжения, выход которого подключен к вторым входам первого усилителя и первого пьезодефлектора, второй источник отрицательного опорного напряжения, выход которого подключен к третьим входам первого усилителя и первого пьезодефлектора, последовательно соединенные второй усилитель и второй пьезодефлектор с отражателем на торце, третий источник положительного опорного напряжения, выход которого подключен к вторым входам второго усилителя и второго пьезодефлектора, четвертый источник отрицательного опорного напряжения, выход которого подключен к третьим входам второго усилителя и второго пьезодефлектора, проекционный объектив, во внешней фокальной плоскости которого расположен матовый экран, первый выход импульсов дискретизации синтезатора частот подключен к первым управляющим входам с первого по третий блоков обработки кодов, блок строчной развертки включает последовательно соединенные задающий генератор и выходной каскад, выход которого является выходом блока строчной развертки и подключен к входу первого усилителя, блоки обработки кодов идентичны, каждый содержит триггер, с первого по четвертый регистры, сумматор и соответствующее число диодов, вход триггера, объединенный с управляющим входом сумматора, является управляющим входом блока обработки кодов и подключен к первому выходу импульсов дискретизации синтезатора частот, информационные входы первого и второго регистров поразрядно объединены, информационные входы третьего и четвертого регистров поразрядно объединены, первый выход триггера подключен к управляющим входам второго и третьего регистров, второй выход триггера подключен к управляющим входам первого и четвертого регистров, выходы второго регистра и первого регистра через диоды поразрядно объединены и подключены к первой группе входов сумматора, выходы четвертого регистра и третьего регистра через диоды поразрядно объединены и подключены к второй группе входов сумматора, управляющий вход которого подключен к входу триггера, накопители кодов идентичны, каждый содержит соответствующее число блоков регистров, третьи управляющие входы которых объединены и подключены к соответствующему выходу синтезатора частот, четвертые управляющие входы блоков регистров объединены и подключены к первому управляющему выходу последнего блока регистров, выходы блока регистров являются выходами накопителя кодов и подключены к входам своего блока импульсных усилителей, информационные входы блоков регистров поразрядно объединены, блоки регистров идентичны, каждый включает с первого по четвертый ключи, первый, второй, третий и четвертый распределители импульсов, первые семь регистров, вторые семь регистров, последовательно соединенные первый счетчик импульсов и первый дешифратор, последовательно соединенные второй счетчик импульсов и второй дешифратор, первый управляющий вход первого ключа является первым управляющим входом блока регистров, первый управляющий вход второго ключа является четвертым управляющим входом блока регистров, второй управляющий вход первого ключа является и первым управляющим выходом блока регистров, выход первого ключа подключен к входу первого распределителя импульсов, выходы которого последовательно подключены к первым управляющим входам с первого по последний разряды первых семи регистров, выход второго ключа подключен к входу второго распределителя импульсов, выходы которого последовательно подключены к вторым управляющим входам с первого по последний разряды первых семи регистров, последний выход первого распределителя импульсов подключен к второму управляющему входу первого ключа, последний выход второго распределителя импульсов подключен к входу первого счетчика импульсов, выход первого дешифратора подключен параллельно к третьим управляющим входам разрядов первых семи регистров, выход третьего ключа подключен к входу третьего распределителя импульсов, выходы которого последовательно подключены к первым управляющим входам с первого по последний разряды вторых семи регистров, последний выход его подключен к второму управляющему входу третьего ключа, выход четвертого ключа подключен к входу четвертого распределителя импульсов, последний выход которого подключен к входу второго счетчика импульсов, выход второго дешифратора подключен параллельно к третьим управляющим входам разрядов вторых семи регистров, выходы разрядов первых семи регистров и выходы разрядов вторых семи регистров поразрядно объединены и являются выходами блока регистров, и подключены к информационным входам соответствующего блока импульсных усилителей, первый управляющий выход каждого предыдущего блока регистров подключен к первому управляющему входу первого ключа каждого последующего блока регистров, а первый управляющий выход последнего блока регистров подключен параллельно к четвертым управляющим входам всех блоков регистров, первый, второй и третий блоки импульсных усилителей идентичны, каждый включает импульсных усилителей по числу блоков регистров в накопителях кодов и по числу разрядов в коде, блок модуляции излучений выполнен из соответствующего числа каналов, каждый из которых содержит последовательно расположенные излучатель трех основных цветов, микрообъектов и фокусирующий конус световода (фокон), входами блока являются входы излучателей, подключенные к соответствующим выходам блоков импульсных усилителей, излучающие плоскости излучателей находятся в задней фокальной плоскости микрообъективов, в передней фокальной плоскости которых находятся входные окна фокусирующих конусов световодов, излучатели через микрообъективы, фокусирующие конусы световодов, отражатель второго пьезодефлектора оптически соединены с отражателем первого пьезодефлектора, который расположен в фокальной плоскости проекционного объектива, во внешней фокальной плоскости которого расположен матовый экран, отличающийся тем, что в него введены второй делитель частоты, выход которого подключен к входу второго усилителя, ИК-передатчик, расположенный над матовым экраном и вход которого подключен к второму управляющему входу синхроимпульсов стереопар синтезатора частот, а излучающее окно ИК-передатчика расположено в сторону от экрана, ЗД-очки с ИК-приемником, расположенным на оправе ЗД-очков, входное окно которого расположено против излучающего окна ИК-передатчика, в каждый из трех каналов введены АЦП, выходы которого подключены к входам блока обработки кодов, и блок удвоения строк, входы которого подключены к выходам блока обработки кодов своего канала, а первые, вторые и третьи управляющие входы подключены соответственно к второму выходу импульсов удвоений частоты дискретизации, четвертому выходу кадров и пятому выходу импульсов частоты строк синтезатора частот, первый управляющий вход рабочей частоты и второй управляющий вход синхроимпульсов стереопар синтезатора частот подключены к соответствующим выходам видеоадаптера персонального компьютера, выходы синтезатора частот подключены: первый выход импульсов дискретизации подключен параллельно к управляющим входам первого, второго и третьего АЦП, к первым управляющим входам с первого по третий блоков обработки кодов, второй выход импульсов удвоенной частоты дискретизации подключен к первым управляющим входам с первого по третий блоков удвоения строк и к третьим управляющим входам первого, второго и третьего накопителей кодов, третий выход сигналов выдачи подключен к четвертым управляющим входам с первого по третий накопителей кодов, четвертый выход импульсов кадров подключен к вторым управляющим входам блоков удвоения строк, к первым управляющим входам накопителей кодов, пятый выход импульсов частоты строк подключен к входам первого и второго делителей частоты, к третьим управляющим входам блоков удвоения строк, первый, второй и третий АЦП идентичны, каждый включает последовательно соединенные видеоусилитель, вход которого является входом АЦП, и пьезодефлектор с отражателем на торце, источник положительного опорного напряжения, выход которого подключен к вторым входам видеоусилителя и пьезодефлектора, источник отрицательного опорного напряжения, выход которого подключен к третьим входам видеоусилителя и пьезодефлектора, излучатель из импульсного светодиода, вход которого является управляющим входом АЦП, щелевой диафрагмы и микрообъектива, линейку многоэлементного фотоприемника и шифратор, выходы которого являются выходами АЦП, входные окна линейки многоэлементного фотоприемника через отражатель пьезодефлектора оптически сопряжены через микрообъектив и щелевую диафрагму с излучающей стороной импульсного светодиода, входы первого, второго и третьего АЦП являются соответственно первым, вторым и третьим информационными входами цифрового монитора, подключенные к соответствующим выходам адаптера персонального компьютера, первый, второй и третий блоки удвоения строк идентичны, каждый включает последовательно соединенные первый блок задержек и сумматор и второй блок задержек, информационные входы первого, второго блока задержек и первые входы сумматора поразрядно объединены и подключены к выходам блока обработки кодов своего канала, выходы второго блока задержек являются первым выходом блока удвоения строк, вторым выходом которого являются выходы сумматора, первый, второй и третий управляющие входы первого блока задержек являются первым, вторым и третьим управляющими входами блока удвоения строк и подключены соответственно к второму, четвертому и пятому выходам синтезатора частот, первые блоки задержек идентичны, каждый включает последовательно соединенные элемент И и первый ключ, второй ключ, первый и второй распределители импульсов и семь регистров с соответствующим числом разрядов каждый, сигнальные входы первого и второго ключей объединены и являются первым управляющим входом, подключены к второму выходу синтезатора частот, вторым и третьим управляющими входами являются первый и второй входы элемента И, подключенные к четвертому и пятому выходам синтезатора частот, выход элемента И подключен к второму управляющему входу второго ключа, выход первого ключа подключен к входу первого распределителя импульсов, выходы которого последовательно подключены к первым управляющим входам с первого по последний разряды семи регистров, последний выход первого распределителя импульсов подключен к второму управляющему входу первого ключа и к первому управляющему входу второго ключа и через диод подключен к первым управляющим входам последних разрядов семи регистров, выход второго ключа подключен к входу второго распределителя импульсов, выходы которого подключены к первым управляющим входам с последнего разряда к первому разряду семи регистров, причем последний выход второго распределителя импульсов подключен через диод к управляющим входам первых разрядов семи регистров и через диод подключен к второму управляющему входу второго ключа и к первому управляющему входу первого ключа, информационные входы разрядов в каждом из семи регистров объединены и являются с первого по седьмой информационными входами первого блока задержек, выходы разрядов в каждом из семи регистров объединены и являются выходами первого блока задержек, подключены к вторым входам сумматора в блоке удвоения строк, в каждый блок обработки кодов введены первый и второй блоки ключей, входы которых поразрядно объединены и являются информационными входами блока обработки кодов, подключенные к выходам своего АЦП, управляющий вход первого блока ключей подключен к первому выходу триггера, управляющий вход второго блока ключей подключен к второму выходу триггера, введены первый и второй блоки задержек, входы первого блока задержек подключены к выходам первого регистра, входы второго блока задержек подключены к выходам третьего регистра, выходы первого, второго блоков задержек и выходы сумматора поразрядно объединены и являются выходами блока обработки кодов, первый, второй и третий накопители кодов идентичны, в каждый введены последовательно соединенные ключ и триггер, накопитель кодов нечетного кадра (левого) и накопитель кодов четного кадра (правого), первым и вторым информационными входами являются поразрядно объединенные первые и вторые группы входов накопителя кодов нечетного кадра и накопителя кодов четного кадра, подключенные к первой и второй группам выходов блока удвоения строк, первый выход триггера подключен к первому управляющему входу накопителя кодов нечетного кадра, второй выход триггера подключен к первому управляющему входу накопителя кодов четного кадра, первым управляющим входом накопителя кодов является сигнальный вход ключа, подключенный к четвертому выходу синтезатора частот, вторым управляющим входом является управляющий вход ключа, подключенный к второму управляющему входу синхроимпульсов стереопар синтезатора частот, третьим управляющим входом являются объединенные вторые управляющие входы накопителя кодов нечетного кадра и накопителя кодов четного кадра, подключенные к второму выходу импульсов двойной частоты дискретизации синтезатора частот, четвертым управляющим входом являются объединенные третьи управляющие входы накопителя кодов нечетного кадра и накопителя кодов четного кадра, подключенные к третьему выходу сигналов выдачи синтезатора частот, накопитель кодов нечетного кадра и накопитель кодов четного кадра идентичны, каждый включает по 480 блоков регистров, первый управляющий вход первого блока регистров является первым управляющим входом накопителя кодов нечетного (четного) кадра, вторые управляющие входы блоков регистров объединены и являются третьим управляющим входом накопителя кодов нечетного (четного) кадра, третьи управляющие входы блоков регистров объединены и являются вторым управляющим входом, выходы блоков регистров являются выходами накопителя кодов нечетного (четного) кадра, объединенные поразрядно первые и вторые входы блоков регистров являются первым и вторым информационными входами накопителя кодов нечетного (четного) кадра, в каждый блок регистров введен триггер, вход которого подключен через диоды к последнему выходу второго распределителя импульсов и к последнему выходу четвертого распределителя импульсов, первый выход триггера подключен к второму управляющему входу второго ключа и к первому управляющему входу четвертого ключа, второй выход триггера подключен к первому управляющему входу второго ключа и к второму управляющему входу четвертого ключа, а четвертый управляющий вход блока регистров подключен через диод к второму выходу триггера, сигнальные входы второго и четвертого ключей объединены и являются вторым управляющим входом блока регистров, выходы четвертого распределителя импульсов подключены к вторым управляющим входам в последовательности с последнего к первому разрядам вторых семи регистров, информационные (первые) входы разрядов первых семи регистров поразрядно объединены и подключены к первой группе выходов блока удвоения строк, информационные (первые) входы разрядов вторых семи регистров поразрядно объединены и подключены к второй группе выходов блока удвоения строк, выходы разрядов в каждом регистре первых семи регистров объединены и выходы разрядов в каждом регистре вторых семи регистров объединены и являются выходами блока регистров, а выходы всех блоков регистров являются выходами накопителя кодов нечетного кадра и выходами накопителя кодов четного кадра, которые объединены соответствующим образом и являются выходами накопителя кодов.

| СПОСОБ ПОЛУЧЕНИЯ И ВОСПРОИЗВЕДЕНИЯ ОБЪЕМНОГО ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1995 |

|

RU2097940C1 |

| СПОСОБ ФОРМИРОВАНИЯ СТЕРЕОСКОПИЧЕСКОГО ИЗОБРАЖЕНИЯ НА ЭКРАНЕ ДИСПЛЕЯ И СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1991 |

|

RU2117414C1 |

| JP 2004363802, 24.12.2004 | |||

| JP 2002262310, 13.09.2002. | |||

Авторы

Даты

2007-01-27—Публикация

2005-07-11—Подача