Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники.

Известно пересчетное устройство, а.с. СССР №1667245, МКл. Н03К 23/74, 1991, содержащее дешифратор и логические элементы И, количество которых равно количеству разрядов счетчика, выходы дешифратора, соответствующие различным кодовым комбинациям на его входах, подсоединены к первым входам логических элементов И, вторые входы которых объединены и подключены к клемме счетного входа, выходы элементов И подключены к счетным входам каждой триггерной ячейки, выход старшего разряда счетчика соединен с входом младшего разряда, входы дешифратора подсоединены к дополнительным выходам каждой триггерной ячейки, а выходом устройства служит один из выходов дешифратора.

Устройство обладает увеличенным ресурсом наработки за счет равномерности загрузки электромагнитных реле по количеству срабатываний, однако ограничения по быстродействию и количеству срабатываний у электромагнитных реле снижают надежность устройства в целом, что является общим недостатком большинства известных устройств на электромагнитных реле.

Устройство, выбранное за прототип, представляет собой многоразрядный счетчик с неразрушающейся информацией, а.с. СССР №1626378, МКл. Н03К 23/74, 1991, содержащий для каждого разряда разрядную ячейку, выполненную на поляризованном реле с переключающей контактной группой и раздельными обмотками срабатывания и возврата. Блоки разделения импульсов и реверса выполнены на реверсивном счетчике импульсов с предварительной установкой, каждый вход предварительной установки которого подключен через переключающую контактную группу соответствующей разрядной ячейки к плюсовой и общей шинам питания. Тактовый вход реверсивного счетчика импульсов подключен к формирователю импульсов, а вход сложение/вычитание - к плюсовой и общей шинам питания через переключатель реверса, вход разрешения предварительной установки - к выходу времязадающего устройства, вход которого подключен к плюсовой шине питания. Каждый разрядный выход реверсивного счетчика импульсов подключен к соответствующему входу первого инвертирующего буфера, каждый соответствующий выход которого подключен одновременно к соответствующему входу второго инвертирующего буфера и через соответствующий первый транзисторный ключ - к обмотке возврата соответствующей разрядной ячейки. Каждый соответствующий вход второго инвертирующего буфера подключен через соответствующий второй транзисторный ключ к обмотке срабатывания соответствующей разрядной ячейки. Входы инвертирующих буферов, управляющие высокоимпедансным состоянием своих выходов, подключены через сдвоенный выключатель/переключатель источника питания к его плюсовой и общей шинами питания, при этом источник питания имеет временную задержку снятия питания при его включении.

Счетчик имеет повышенную надежность по сравнению с известными устройствами за счет его высокого быстродействия, поскольку прямой и обратный счет импульсов осуществляется без участия поляризованных реле, и экономичности по числу срабатываний поляризованных реле вследствие их однократного срабатывания при выключении питания, однако имеет при этом следующие недостатки:

- счетчик не запоминает цифровую информацию при несанкционированном выключении первичного питания;

- импульс напряжения на обмотках поляризованных реле при записи цифровой информации имеет форму спадающей экспоненты и отсутствие "полки" в напряжении влияет на надежность запоминания цифровой информации;

- счетчик имеет достаточно сложную схему запоминания цифровой информации, в частности транзисторные ключи, что влияет на его надежность и массогабаритные характеристики при наращивании счетчика.

Задачей предлагаемого изобретения является повышение надежности запоминания цифровой информации при одновременном упрощении схемы запоминания,

Согласно предлагаемому изобретению решение поставленной задачи достигается тем, что в реверсивном счетчике с памятью, содержащем разрядные ячейки, выполненные для каждого разряда на поляризованном реле с переключающей контактной группой и раздельными обмотками срабатывания и возврата, зашунтированными соответствующими диодами, источник питания с временной задержкой снятия питания на конденсаторе и сдвоенном выключателе/включателе, а также формирователь импульсов, времязадающее устройство и реверсивный счетчик импульсов с предварительной установкой и переключателем реверса, входы предварительной установки которого подключены через переключающие контактные группы соответствующих разрядных ячеек к плюсовой и общей шинами питания, тактовый вход реверсивного счетчика импульсов подключен к формирователю импульсов, а вход сложение/вычитание - к плюсовой и общей шинам питания через переключатель реверса, вход разрешения предварительной установки - к выходу времязадающего устройства, вход которого подключен к плюсовой шине питания;

- каждый разрядный выход реверсивного счетчика импульсов подключен соответственно к неинвертирующему входу первого и инвертирующему входу второго введенных компараторов напряжения, вторые входы которых объединены и подключены к среднему уровню напряжения, выход первого компаратора подключен к обмотке возврата поляризованного реле соответствующей разрядной ячейки, а выход второго компаратора - к обмотке срабатывания поляризованного реле этой же разрядной ячейки, начала обмоток поляризованных реле объединены и подключены к плюсовой шине питания через выключатель источника питания, который дополнен электронным ключом, подключающим при несанкционированном выключении первичного питания конденсатор источника питания к плюсовой шине питания и началам обмоток поляризованных реле;

- источник питания с временной задержкой снятия питания и электронным ключом выполнен на транзисторе р-п-р типа и реле, обмотка которого зашунтирована диодом и подключена своим началом к первичному питанию, конец обмотки - к общей шине питания через включатель источника питания, при этом замыкающий контакт реле подключен первым выводом к первичному питанию, а вторым выводом - к плюсовой шине питания и базе транзистора, эмиттер которого подключен: к конденсатору, коллектор - к началам обмоток поляризованных реле, а база-эмиттерный переход зашунтирован диодом в обратном направлении.

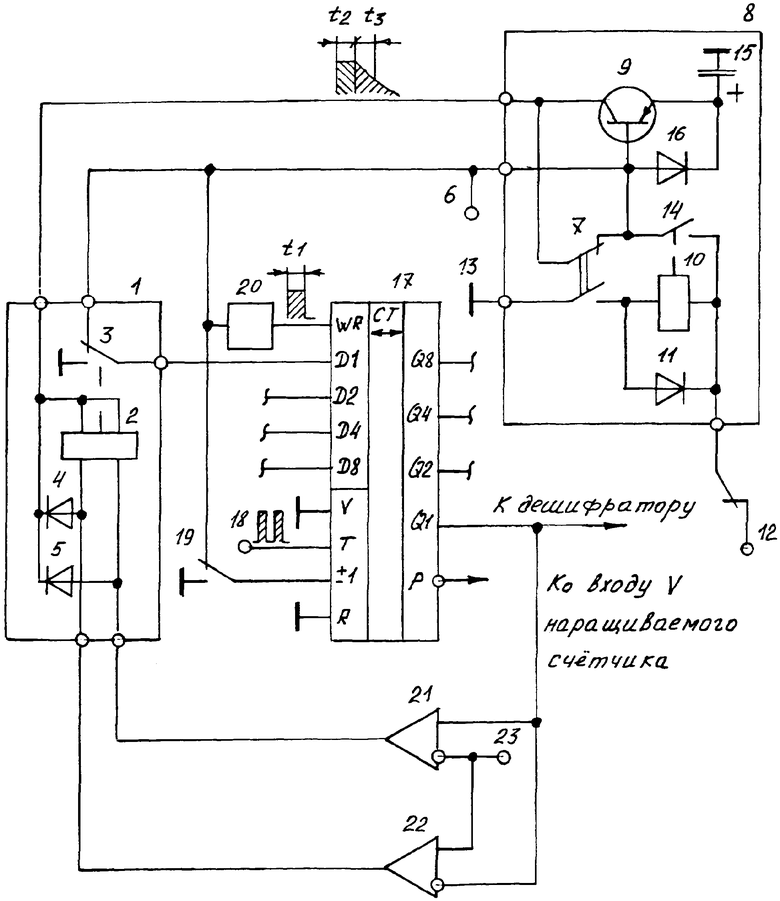

На чертеже представлена функциональная схема реверсивного счетчика о памятью.

Счетчик содержит для каждого счетного разряда разрядную ячейку 1, выполненную на поляризованном реле 2 с переключающей контактной группой 3 и раздельными обмотками срабатывания и возврата, зашунтированными диодами 4, 5, начала обмоток поляризованных реле объединены и подключены к плюсовой шине питания 6 через выключатель сдвоенного выключателя/включателя 7 источника питания 8 с временной задержкой снятия питания с его плюсовой шины 6, реализованный на транзисторе 9 р-п-р типа и реле (контакторе) 10, обмотка которого зашунтирована диодом 11 и подключена своим началом к первичному питанию 12, конец обмотки подключен к общей шине питания 13 через включатель 7 источника питания 8, при этом замыкающий контакт 14 реле 10 подключен первым выводом к первичному питанию 12, а вторым выводом - к плюсовой шине питания 6 и базе транзистора 9, эмиттер которого подключен к накопительному конденсатору 15, коллектор - к началам обмоток поляризованных реле, а база-эмиттерный переход зашунтирован диодом 16 в обратном направлении, счетчик содержит также реверсивный счетчик импульсов 17 с предварительной установкой, каждый вход Д1...Д8 которой подключен через переключающую контактную группу 3 соответствующей разрядной ячейки 1 к плюсовой 6 и общей 13 шинам питания, тактовый вход Т реверсивного счетчика импульсов 17 подключен к формирователю импульсов 18, входы переноса V и установки нуля R - к общей шине питания 13, выход переноса Р - к входу V наращиваемого реверсивного счетчика, а вход сложение/вычитание ±1 - к плюсовой 6 и общей 13 шинам питания через переключатель реверса 19, вход разрешения предварительной установки WR - к выходу времязадающего устройства 20, вход которого подключен к плюсовой шине питания 6, а каждый разрядный выход Q1...Q8 реверсивного счетчика импульсов 17 подключен соответственно к неинвертирующему входу первого компаратора напряжения 21 и инвертирующему входу второго компаратора напряжения 22, вторые входы которых объединены и подключены к среднему уровню напряжения 23, выход первого компаратора 21 подключен к обмотке возврата поляризованного реле 2 соответствующей разрядной ячейки 1, а выход второго компаратора 22 - к обмотке срабатывания полярированного реле 2 этой же разрядной ячейки.

Реверсивный счетчик импульсов может быть выполнен на микросхеме 564ИЕ14, компараторы напряжения - на микросхеме 521CA301.

Реверсивный счетчик с памятью работает следующим образом.

При включении питания срабатывает реле 10 и появляется напряжение на плюсовой шине питания 6, через диод 16 заряжается накопительный конденсатор 15, время задающее устройство 20 формирует импульс напряжения t1 на входе WR реверсивного счетчика импульсов 17, при этом выходы его разрядов Q1-Q8 устанавливаются через входы предварительной установки Д1-Д8 в состояния лог."1" или лог."0", соответствующие для каждого разряда положению переключающей контактной группы 3 соответствующей разрядной ячейки 1. Одновременно при включении питания начала обмоток поляризованных реле через выключатель 7 и закрытый транзистор 9 отключаются от первичного источника питания 12.

Реверсивный счетчик импульсов 17 в зависимости от положения переключателя реверса 19 производит прямой или обратный счет пачек импульсов, поступающих на его тактовый вход Т от формирователя импульсов 18. Цифровая информация по каждому разряду Q1-Q8 реверсивного счетчика импульсов 17 поступает на соответствующие входы компараторов напряжения 21, 22, где сравнивается со средним уровнем напряжения 23, при этом лог "0" на неинвертирующем входе компаратора 21 открывает его выход, а лог."1" закрывает его выход, и наоборот, лог."0" на инвертирующем входе компаратора 22 закрывает его выход, а лог."1" открывает его выход, тем самым по каждому счетному разряду готовятся цепи запитки либо обмотки возврата, либо обмотки срабатывания поляризованного реле 2 соответствующей разрядной ячейки 1 и установки переключающей контактной группы 3 в положения лог."0" или лог."1".

При штатном выключении источника питания 8 начала обмоток поляризованных реле через выключатель 7 запитываются в течение времени отпускания реле 10 (интервал t2) от первичного источника питания 12, при этом формируется "полка" напряжения на соответствующих обмотках поляризованных реле и плюсовой шине питания 6. При размыкании контакта 14 реле 10 дополнительно формируется рабочий уровень напряжения на плюсовой шине питания 6 и соответствующих обмотках поляризованных реле в течение интервала t3 за счет разряда конденсатора 15 через смещенный в прямом направлении база-эмиттерный переход транзистора 9, что в общем итоге повышает надежность записи цифровой информации в разрядные ячейки на поляризованных реле.

При несанкционированном выключении первичного питания 12 происходит автоматическое открывание транзистора 9 и разряд конденсатора 15 по его цепям эмиттер-коллектор и эмиттер-база, тем самым формируется рабочий импульс напряжения на соответствующих обмотках поляризованных реле и плюсовой шине питания 6, при этом основной базовый ток транзистора 9 определяется разрядом конденсатора 15 через замкнутый контакт 14 и обмотку реле 10, а также замкнутый контакт включателя 7 до момента отпускания реле 10.

Таким образом предложенный реверсивный счетчик за счет прямоугольного импульса напряжения питания при штатном запоминании цифровой информации, а также возможности ее запоминания при несанкционированном выключении первичного питания, а также упрощения схемы запоминания обладает повышенной надежностью при записи цифровой информации в разрядные ячейки на поляризованных реле.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядный счетчик с неразрушающейся информацией | 1988 |

|

SU1626378A1 |

| Счетчик с неразрушающейся информацией | 1989 |

|

SU1651380A1 |

| Многоразрядный счетчик | 1984 |

|

SU1225012A1 |

| Реверсивный декадный счетчик с памятью | 1983 |

|

SU1088138A1 |

| Двоичный счетчик с неразрушающейся информацией | 1982 |

|

SU1081805A2 |

| Устройство для автоматического выбора направления движения объекта | 1984 |

|

SU1184768A1 |

| Релейный счетчик | 1982 |

|

SU1043828A1 |

| Многоразрядный счетчик | 1985 |

|

SU1270892A2 |

| Устройство для дистанционного управления раздаточной тележкой | 1988 |

|

SU1667015A1 |

| Устройство для раздельного управления реверсивным вентильным преобразователем | 1987 |

|

SU1443098A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Технический результат заключается в повышении надежности запоминания цифровой информации при одновременном упрощении схемы запоминания. Реверсивный счетчик с памятью (PC) содержит разрядные ячейки, выполненные для каждого разряда на поляризованном реле (ПР) (1) с переключающей контактной группой (3) и раздельными обмотками (2) срабатывания и возврата, зашунтированными соответствующими диодами (4, 5), источник питания (ИП) (8) с временной задержкой снятия питания на конденсаторе (15) и сдвоенном выключателе/включателе (7), а также формирователь импульсов (18), времязадающее устройство (20) и реверсивный счетчик импульсов (PC) (17) с предварительной установкой и переключателем реверса (19). Каждый разрядный выход PC (17) подключен соответственно к неинвертирующему входу первого (21) и инвертирующему входу второго (22) введенных компараторов (К) напряжения, вторые входы которых объединены и подключены с среднему уровню напряжения (23). Выходы К (21, 22) подключены к обмоткам (2) возврата и срабатывания поляризованного реле (1) соответствующей разрядной ячейки, начала обмоток (2) объединены и подключены к плюсовой шине питания через выключатель (7) ИП (8), который дополнен электронным ключом (9), подключающим при несанкционированном выключении первичного питания конденсатор (15) ИП (8) к плюсовой шине питания и началам обмоток поляризованных реле. 1 з.п. ф-лы, 1 ил.

| Многоразрядный счетчик с неразрушающейся информацией | 1988 |

|

SU1626378A1 |

| Пересчетное устройство | 1989 |

|

SU1667245A1 |

| Многоразрядный счетчик | 1984 |

|

SU1225012A1 |

| Реверсивный счетчик импульсов в коде Грея | 1982 |

|

SU1045401A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

Авторы

Даты

2008-03-27—Публикация

2006-12-04—Подача