I. Область техники, к которой относится изобретение

Данное изобретение относится, в общем случае, к связи, и, более определенно, к способам для выполнения демодуляции данных в системе связи с множественным доступом с кодовым разделением каналов (CDMA).

II. Уровень техники

В системе CDMA базовая станция передает данные по «кодовым» каналам на беспроводные терминалы. Каждый кодовый канал связан с соответствующим ортогональным кодом. Базовая станция направляет данные для кодового канала, перемножая каждый символ данных, который будет передан по кодовому каналу, со всеми L сегментами L-сегментного ортогонального кода, назначенного кодовому каналу, для получения L канальных символов данных, которые после этого передаются. L является коэффициентом распространения (SF) или длиной ортогонального кода и равен четырем или более (т.е. L≥4). Терминал получателя восстанавливает данные, посланные по кодовому каналу, с помощью первого перемножения полученной выборки с L сегментами того же самого ортогонального кода для того, чтобы получить выборки без образцов. Терминал после этого накапливает группы L выборки без образцов для полного ортогонального кода для того, чтобы получить восстановленные символы данных, которые являются оценками символов данных, посланных по кодовому каналу базовой станцией.

При формировании каналов достигается ортогональность среди всех кодовых каналов, передаваемых одновременно базовой станцией. Для широкополосного CDMA (W-CDMA) формирование каналов упоминается как «распространение», кодовые каналы упоминаются как «физические» каналы, и ортогональный переменный коэффициент распространения (OVSF) кодов используются для ортогональных кодов. Для IS-95 и IS-2000 формирование каналов упоминается как «покрытие», кодовые каналы упоминаются как каналы «трафика», и коды Волша (Walsh) и квазиортогональные функции (QOF) используются для ортогональных кодов. Таким образом, различные стандарты CDMA могут использовать различную терминологию для процесса формирования каналов. Для ясности, для следующего описания используется терминология W-CDMA.

Базовая станция может передавать данные на множестве физических каналов на единственный терминал для достижения более высокой скорости передачи данных. Базовая станция может также выполнять другую обработку на символах данных до передачи на терминал. Например, базовая станция может использовать разнесение передачи в пространстве и времени (STTD) и передавать символы данных от множества антенн для получения пространственного разнесения, которое может бороться с вредными эффектами пути. Терминал выполняет демодуляцию данных для восстановления символов данных, посланных по множеству физических каналов. Как часть демодуляции данных, терминал обычно выполняет свертывание для каждого физического канала, чтобы получить свернутые символы для этого физического канала. Терминал после этого выполняет другую обработку (например, компенсацию каналов и декодирование STTD) на свернутых символах для каждого физического канала для того, чтобы получить восстановленные символы данных для физического канала. Обработка для демодуляции данных сильно увеличивается, когда увеличивается число физических каналов.

Поэтому есть потребность в данной области техники для способов более эффективного выполнения демодуляции данных в системе CDMA.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Здесь обеспечиваются способы для выполнения демодуляции данных на частично свернутых символах. Частично свернутый символ для физического канала с коэффициентом распространения L получается с помощью накопления выборки без образцов по длине короче, чем L (т.е. накапливаясь по L/2 или L/4). Демодуляция данных на частично свернутых символах уменьшает число требуемых умножений.

В одном варианте воплощения интегральная схема, действующая для выполнения демодуляции данных на частично свернутых символах, включает в себя модуль свертки, модуль компенсации канала и объединитель символов. Модуль свертки свертывает входные выборки и предоставляет свернутые символы первому кодовому каналу с первым коэффициентом распространения (т.е. SF=8). Модуль компенсации канала умножает свернутые символы на оценку канала и предоставляет демодулированные символы. Объединитель символов объединяет группы демодулированных символов для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения (т.е. SF=16), который является целочисленным множителем первого коэффициента распространения. Компенсация канала и объединение символа зависят от того, действительно ли используется STTD, как описано ниже.

Для схемы с мультиплексированием с временным разделением (TDM) свернутые символы для множества первых кодовых каналов могут быть обработаны способом TDM для получения восстановленных символов данных для множества вторых кодовых каналов. Селектор канала получает свернутые символы для множества первых кодовых каналов и предоставляет один свернутый символ для одного первого кодового канала одновременно модулю компенсации канала. Модуль компенсации канала и объединитель символа используются конвейерным способом. Модуль компенсации канала перемножает свернутые символы из селектора канала с оценкой канала и предоставляет демодулированные символы. Объединитель символа объединяет демодулированные символы от модуля компенсации канала с накопленными символами и предоставляет объединенные символы. Накопленные символы показательны для частичных результатов объединения для восстановленных символов данных, и объединенные символы показательны для модифицированных результатов объединения для восстановленных символов данных. Буфер символа предоставляет накопленные символы и хранит объединенные символы.

Способы, описанные здесь, могут использоваться для различных систем и стандартов CDMA. Например, второй кодовый канал может быть высокоскоростным физическим нисходящим совместно используемым каналом (HS-PDSCH) в W-CDMA, каналом передачи пакетных данных (PDCH) в IS-2000, и так далее.

Различные аспекты и варианты воплощений изобретения описаны более подробно ниже.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Особенности и сущность данного изобретения станут более очевидными из подробного описания, сформулированного ниже, когда оно рассматривается вместе с чертежами, в которых подобные ссылочные позиции идентифицируют подобные элементы повсюду и в которых:

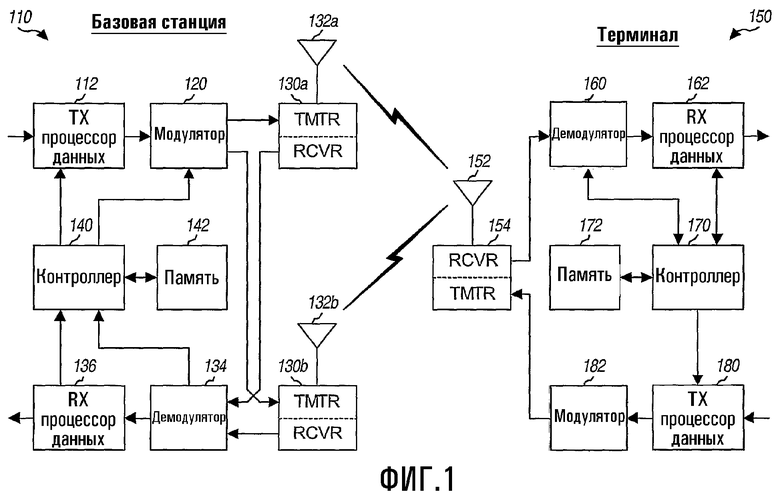

фиг.1 показывает базовую станцию и беспроводной терминал в системе W-CDMA;

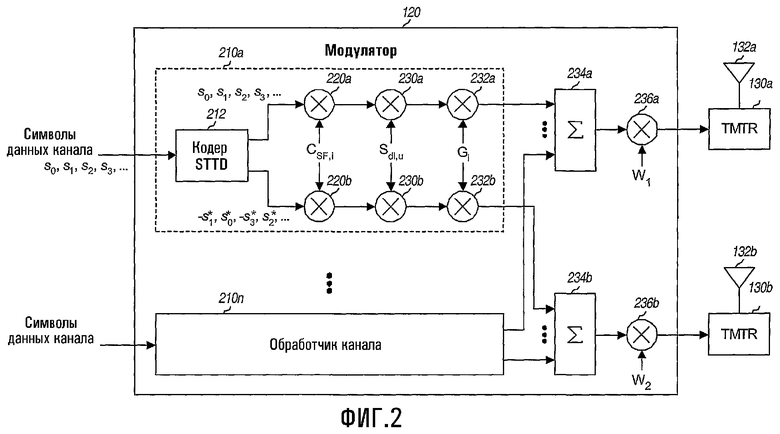

фиг.2 показывает модулятор в пределах базовой станции;

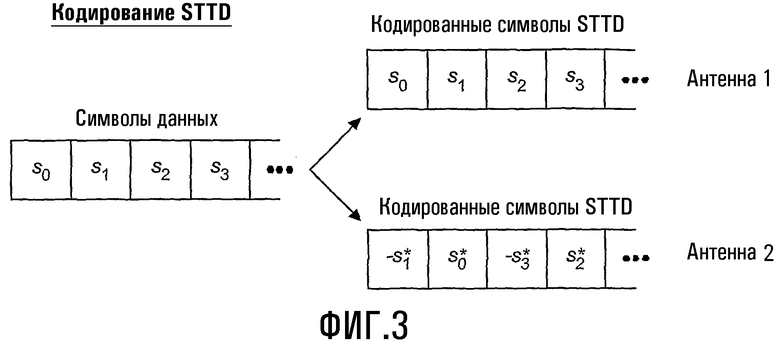

фиг.3 иллюстрирует STTD кодирование в W-CDMA;

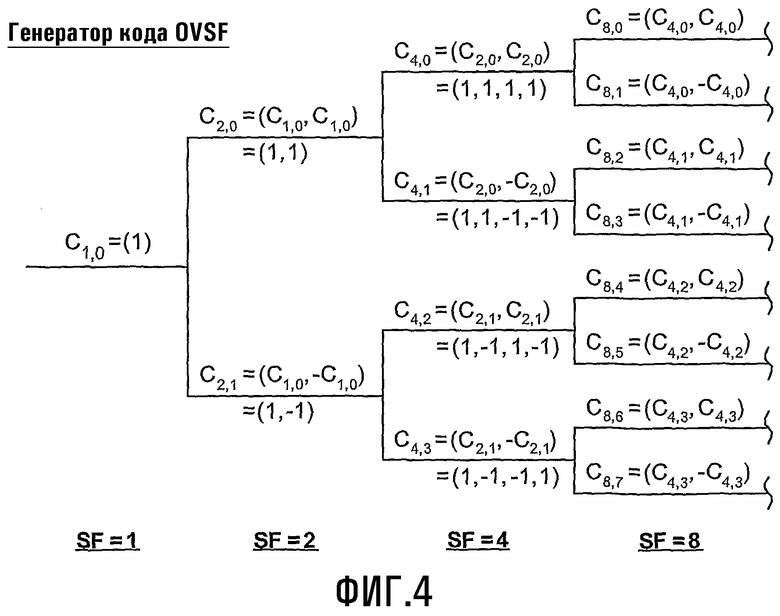

фиг.4 показывает порождение кодов OVSF, используемых в W-CDMA;

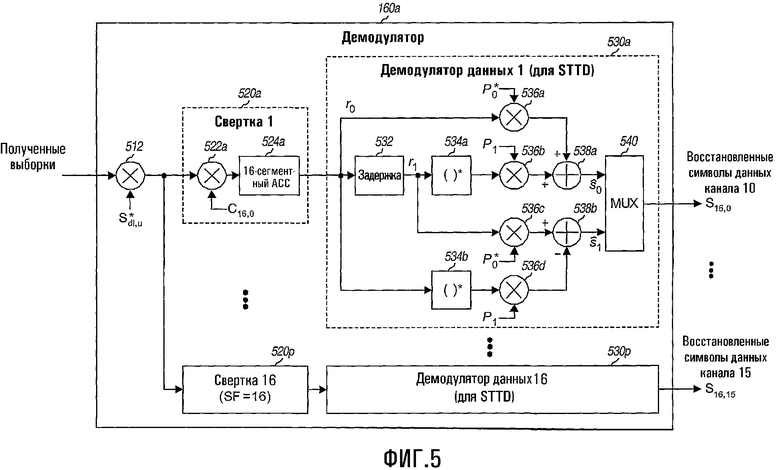

фиг.5 показывает демодулятор, который выполняет демодуляцию данных на полностью свернутых символах;

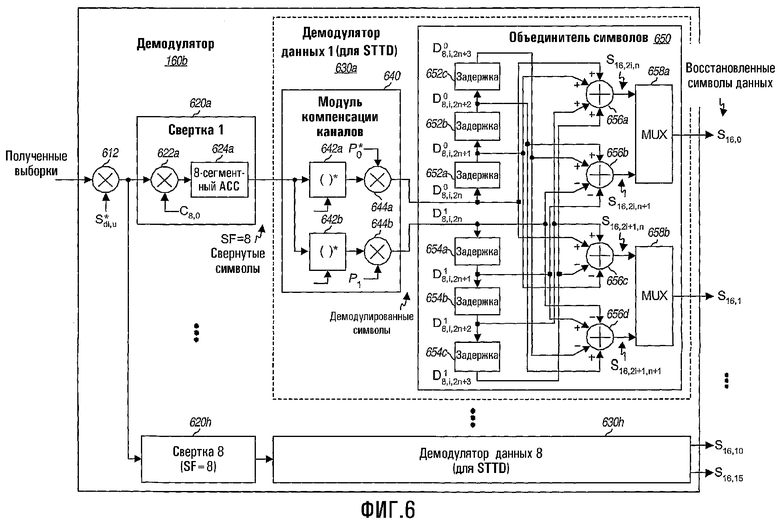

фиг.6 показывает демодулятор, который выполняет демодуляцию данных на частично свернутых символах;

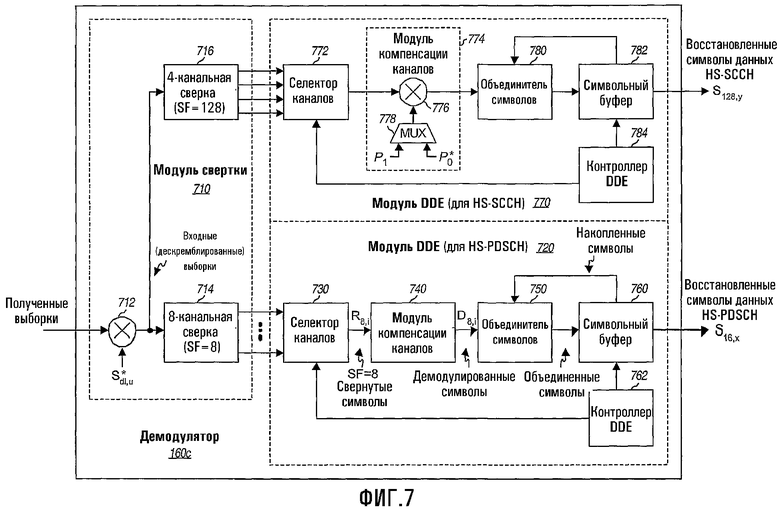

фиг.7 показывает демодулятор, который выполняет демодуляцию данных на частично свернутых символах способом TDM;

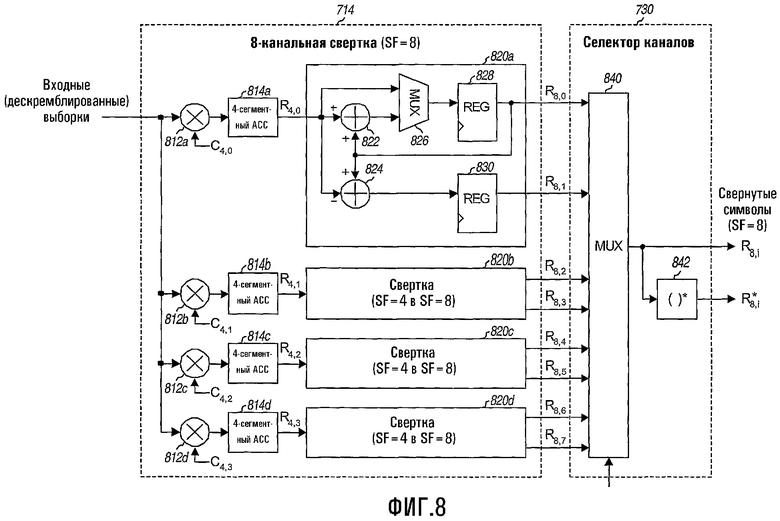

фиг.8 показывает 8-канальную свертку;

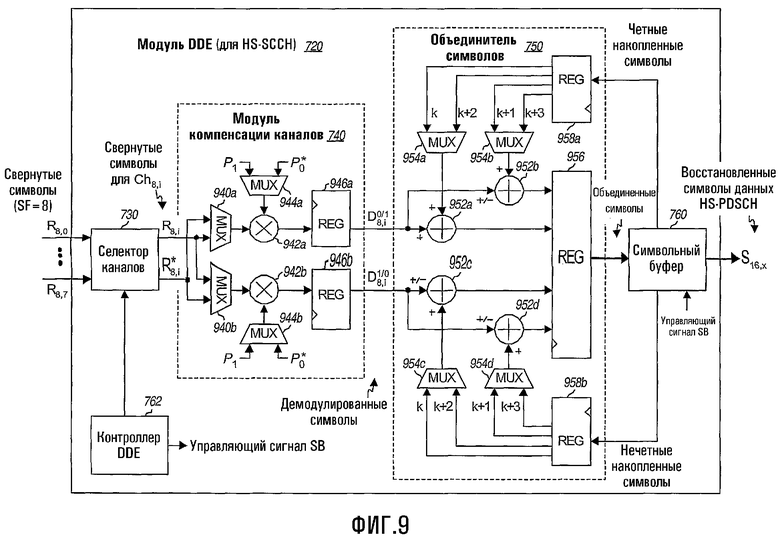

фиг.9 показывает модуль механизма демодуляции данных (DDE);

фиг.10А и 10B показывает конвейерную обработку модулем DDE;

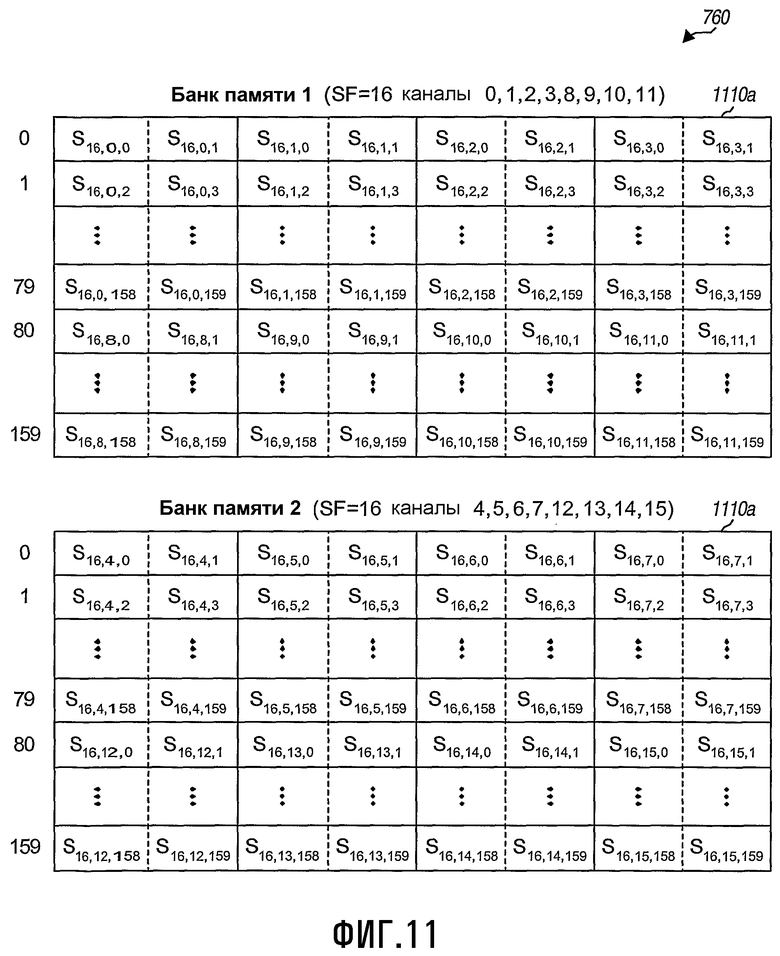

фиг.11 показывает символьный буфер в модуле DDE; и

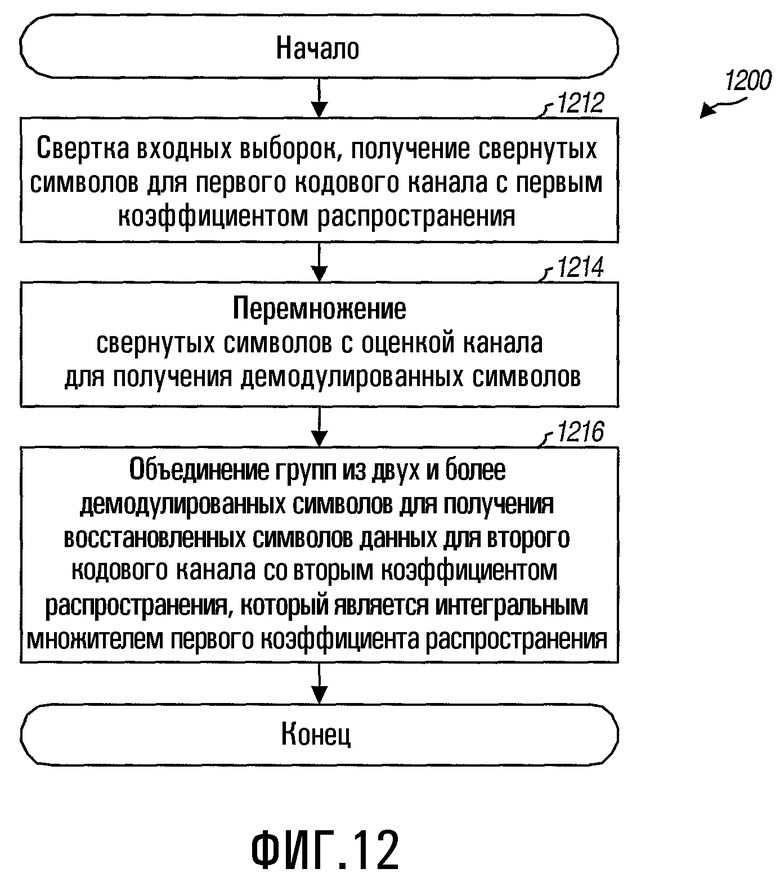

фиг.12 показывает процесс для выполнения демодуляции данных на частично свернутых символах.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Слово «примерный» используется здесь для обозначения «служить примером, образцом, или иллюстрацией». Любой вариант воплощения или дизайн, описанные здесь как «примерный», не должны обязательно рассматриваться как предпочтительные или выгодные перед другими вариантами воплощения или дизайнами.

W-CDMA релиз 5 поддерживает высокоскоростной пакетный доступ для передачи по нисходящей линии связи (HSDPA), который является набором каналов и процедур, допускающих высокоскоростную передачу пакетных данных при передаче по нисходящей линии связи. Для HSDPA, данные обрабатываются в блоках, которые мультиплексированы для совместно используемого канала высокоскоростной передачи по нисходящей линии связи (HS-DSCH). HS-DSCH после этого отображается к одному или более совместно используемым высокоскоростным физическим каналам по нисходящей линии связи (HS-PDSCH), которые являются физическими каналами. Физический канал связан с кодом OVSF и другими атрибутами (например, управлением мощностью). HS-PDSCH может использоваться способом для передачи данных с временным и кодовым мультиплексированием (TDM/CDM) для множества терминалов. Информация управления для HS-PDSCH передается на один или более HS-SCCH, которые совместно используют физические каналы управление для HS-DSCH. Информация управления включает в себя различные параметры, используемые терминалами для того, чтобы должным образом получить и обрабатывать HS-PDSCH.

Фиг.1 показывает блок-схему базовой станции 110 и беспроводного терминала 150 в системе W-CDMA. Базовая станция упоминается как Узел B, и терминал упоминается как пользовательское оборудование (UE) в терминологии W-CDMA. Терминал 150 может связываться с одной или более базовыми станциями при передаче по каналу нисходящей линии связи (т.е. коммуникационной связи с базовой станции на терминал) и/или восходящей связи (т.е. коммуникационной связи от терминала до базовой станции) в любой данный момент времени.

При передаче по нисходящей линии связи передающий (TX) процессор 112 данных получает и обрабатывает (например, форматирует, кодируют и чередует) данные для транспортных каналов, отображает обработанные данные на физические каналы и предоставляет символы данных для каждого физического канала. Модулятор (MOD) 120 дополнительно обрабатывает (т.е. канализирует, спектрально распространяет и масштабирует) символы данных от процессора 112 данных TX и предоставляет поток выходных сегментов для каждой антенны, используемой для передачи данных. Каждый поток выходных сегментов адаптируется (т.е. преобразуется в аналоговый, усиливается, фильтруется и повышается по частоте) соответствующим модулем 130 передатчика (TMTR) для того, чтобы сгенерировать передачу модулированного сигнала по нисходящей линии связи, который после этого передается с соответствующей антенны 132.

В терминале 150 модулированный сигнал(ы) передачи по нисходящей линии связи получается антенной 152 и предоставляется модулю 154 получателя (RCVR). Модуль 154 получателя адаптирует (т.е. понижает частоту, фильтрует и усиливает) полученный сигнал от антенны 152 и оцифровывает адаптированный сигнал для получения полученной выборки. Демодулятор 160 (DEMOD) дополнительно обрабатывает (т.е. дешифрует, сворачивает и демодулирует) полученные выборки для того, чтобы получить восстановленные символы данных, которые являются оценками символов данных, переданных базовой станцией 110. Процессор 162 данных RX дополнительно обрабатывает (т.е. убирает чередование и декодирует) восстановленные символы данных для получения декодированных данных.

На канале связи процессор 180 данных TX получает и обрабатывает различные типы данных (т.е. подтверждает передачу пакетных данных по нисходящей линии связи). Обработанные данные от процессора 180 данных TX дополнительно обрабатываются (т.е. распространяются и шифруются) модулятором 182 и адаптируются модулем 154 передатчика для генерации модулируемого сигнала канала связи, который после этого передается через антенну 152. В базовой станции 110 модулируемый сигнал канал связи получается антеннами 132a и 132b и адаптируется и оцифровывается модулями 130a и 130b получателя для предоставления выборок. Демодулятор 134 и процессор 136 данных дополнительно обрабатывают выборки для того, чтобы восстановить данные, переданные терминалом.

Контроллеры 140 и 170 направлены на операции различных процессоров в пределах базовой станции 110 и терминала 150 соответственно. Модули 142 и 172 памяти хранят данные и коды программы, используемые различными процессорами в базовой станции 110 и терминале 150 соответственно.

Фиг.2 показывает блок-схему модулятора 120 в базовой станции 110 фиг.1. Базовая станция обычно использует множество физических каналов для передачи данных к одному или множеству терминалов в любой данный момент времени. Модулятор 120 включает в себя N процессоров 210a-210n канала, один процессор канала для каждого физического канала, используемого для передачи данных. В пределах процессора 210 канала для физического канала ChSF,i STTD кодер 212 получает символы данных для физического канала. Для не-STTD режима (т.е. с не разрешенным STTD) STTD кодер 212 предоставляет те же самые символы данных обоим множителям 220a и 220b. Для STTD режима (т.е. с разрешенным STTD), как показано на фиг.2, STTD кодер 212 предоставляет кодированные символы STTD для антенны 1 к множителю 220a и кодированные символы STTD для антенны 2 к множителю 220b. STTD выбирается базовой станцией 110.

Для каждой антенны множитель 220 умножает кодированные символы STTD для этой антенны с кодом OVSF CSF,i, назначенного каналу ChSF,i, и предоставляет канализированные символы. Множитель 220 выполняет распространение для канала ChSF,i. Отношение символа в множителе 220 равно 1/Ts, и отношение символа от множителя 220 - SF/Ts, где Ts равен одному периоду символьных данных. Каждому физическому каналу назначается различный код OVSF, но тот же самый код OVSF используется для обеих антенн для физического канала. Канализированные символы для каждой антенны тогда скремблируются (т.е. умножаются) с комплексным значением кода скремблирования Sdl,u с помощью множителя 230 и дополнительно масштабируются с коэффициентом веса Gi множителем 232. Код скремблирования Sdl,u назначается терминалу, на который направлен канал ChSF,i. Коэффициент веса Gi определяет количество передаваемой мощности, используемой для канала ChSF,i. Множитель 232a предоставляет скремблированные и взвешенные символы для антенны 1 на объединитель 234a, и множитель 232b предоставляет скремблированные и взвешенные символы для антенны 2 на объединитель 234b.

Объединитель 234a получает и объединяет скремблированные и взвешенные данные для канала ChSF,i с данными для других физических каналов для антенны 1 и предоставляет составные символы для антенны 1. Множитель 236a умножает составные символы с комплексным по значение весовым коэффициентом W1 и предоставляет взвешенные символы для антенны 1. Объединитель 234b и множитель 236b выполняют подобную обработку для антенны 2. Весовые коэффициенты W1 и W2 используются для настройки стадии в режиме 1 петли в W-CDMA и для стадии и настройки амплитуды в режиме 2 петли. Режимы 1 и 2 петли применяются только к DPCH и соответствующей PDSCH. Когда режим петли допускается, данные не являются закодированным STTD и множителям 236a и 236b предоставляются соответствующе коэффициенты веса W1 и W2. Когда режим петли не допускается, множители 236a и 236b обходятся с помощью установки обоих коэффициентов веса W1 и W2 в единицу. Множители 236a и 236b предоставляют взвешенные символы (т.е. потоки выходных сегментов) для антенн 1 и 2 к модулям 130a и 130b передатчика, соответственно, где надбавка может быть единицей или неединичными коэффициентами веса W1 и W2.

Фиг.3 иллюстрирует STTD кодирование в W-CDMA. Данные для каждого физического канала являются последовательностью битов, которые могут быть выражены как {b0, b1, b2, b3, b4, b5, b6, b7, ...}. STTD кодер 212 получает входную последовательность битов и предоставляет две последовательности битового вывода для этих двух антенн. Последовательность битового вывода для антенны 1 та же самая, что и входная последовательность битов. Последовательность битов вывода для антенны 2 - {-b2, b3, b0, -b1, -b6, b7, b4, -b5, ...}. Последовательность битов вывода для каждой антенны демультиплексируется в синфазную (I) последовательность и квадратичную (Q) последовательность. Последовательность I для антенны 1 является {b0, b2, b4, b6, ...} и Q последовательность для антенны 1 является {b1, b3, b5, b7, ...}. I и Q последовательности для антенны 1 могут рассматриваться как комплексная по значению символьная последовательность {s0, s1, s2, s3, ...}, где s0=b0+jb1, s1=b2+jb3 и так далее. Точно так же последовательность I для антенны 2 является {-b2, b0, -b6, b4, ...} и последовательность Q для антенны 2 является {b3, -b1, b7, -b5, ...}. I и Q последовательности для антенны 2 могут рассматриваться как комплексная по значению символьная последовательность {-s1 *, s0 *, -s3 *, s2 *, ...}, где -s1 *=-b2+jb3, s0 *=-b0- jb1 и так далее, где s0 * является комплексно сопряженным значением s0. Кодирования STTD фактически передает каждую пару символов данных (т.е. s0 и s1) по двум антеннам для достижения пространственного разнообразия, которое может бороться с вредными эффектами пути. Кроме того, символы данных для антенны 2 перестраиваются для того, чтобы обеспечить разнообразие по времени.

Фиг.4 показывает генерацию кодов OVSF, используемых в W-CDMA. Каждый код OVSF идентифицируется обозначением CSF,i, где префикс «SF» обозначает коэффициент распространения кода OVSF и i обозначает номер кода. Коэффициент распространения является длиной кода OVSF, и i обозначает номер сегмента. Номер кода i находится в диапазоне от 0 до SF-1, т.e. i=0, 1..., SF-1. Коды OVSF являются структурированными кодами, и последовательно длинные OVSF коды могут быть сгенерированы из коротких OVSF кодов в соответствии с определенными правилами. OVSF коды длины 2L могут быть сгенерированы с помощью формирования двух длинных OVSF кодов с каждым коротким OVSF кодом длиной L. Первый длинный OVSF код формируется с помощью повторения короткого OVSF кода дважды, т.е. Ch2L,2i=(ChL,I, ChL,i). Второй длинный OVSF код формируется с помощью повторения короткого OVSF кода дважды и инвертирования второго повторения, т.е., Ch2L,2i+1=(ChL,i,-ChL,i). Структурный характер кодов OVSF может эксплуатироваться для того, чтобы упростить демодуляцию данных, как описано ниже.

Для HSDPA базовая станция может передавать до пяти HS-PDSCH на данный терминал в любой данный момент времени. HS-PDSCH разделены среди всех терминалов в зоне охвата базовой станции. Каждому HS-PDSCH назначен определенный код OVSF с коэффициентом распространения 16 (SF=16). Базовая станция также передает до четырех HS-SCCH, где каждому HS-SCCH назначен определенный код OVSF с коэффициентом распространения 128. HS-PDSCH и HS-SCCH для HSDPA описаны стандартом W-CDMA релиз 5, который является публично доступным.

HS-SCCH несет информацию управления для HS-PDSCH. Информация управления указывает код OVSF, схему модуляции и терминал получателя для каждого HS-PDSCH. Базовая станция посылает информацию управления на два слота HS-SCCH перед соответствующими передачами пакета на HS-PDSCH. Терминал получает информацию управления только от одного HS-SCCH, если вообще получает, но может получать пакетные данные от одного или множества HS-PDSCH.

Фиг.5 показывает блок-схему демодулятора 160a, который выполняет демодуляцию данных на полностью свернутых символах для HS-PDSCH. Демодулятора 160a является одной реализацией демодулятора 160 фиг.1.

В демодуляторе 160a множитель 512 умножает полученные выборки от модуля получателя 154 с дескремблированным кодом S* dl,u на терминал 150 и предоставляет дескремблированные выборки. Для HSDPA дескремблированные выборки предоставляются к шестнадцати SF=16 сверткам 520a-520p, одной свертке 520 для каждого из шестнадцати SF=16 каналов Ch16,0-Ch16,15, которые могут использоваться для HS-PDSCH базовой станцией 110. В пределах сверток 520 для канала Ch16,i множитель 522 умножает дескремблированные выборки с OVSF кодом C16,i для канала Ch16,i. Сумматор 524 тогда накапливает вывод множителя 522 по длине кода OVSF C16,i (который является 16 сегментами для SF=16) и предоставляет свернутые символы для канала Ch16,i. Множитель 522 и сумматор 524 выполняет свертывание для канала Ch16,i.

Для не-STTD режима символы данных для каждого физического канала передаются от одной антенны базовой станции. Полученные символы в терминале могут быть выражены как:

где s является символом данных, переданный базовой станцией;

r является символом, полученным терминалом;

h является увеличением пути сигнала от антенны базовой станции до антенны терминала; и

n является шумом, связанным с полученным символом r.

Терминал может получить оценку  , переданного символа s данных, следующим образом:

, переданного символа s данных, следующим образом:

Обработка в уравнении (2) упоминается как демодуляция данных или согласованная фильтрация.

Для режима STTD терминал выполняет дополнительное декодирование STTD для того, чтобы возвратить переданные символы данных. Для STTD передачи пары символов данных, s0 и s1, базовая станция передает последовательности s0 и s1 в два периода символьных данных от антенны 1 и передает последовательности -s1 * и s0 * в тот же самый 2-символьный период от антенны 2, как показано на фиг.3. Если терминал оборудован единственной антенной, то полученные символы могут быть выражены как:

где r0 и r1 являются двумя символами, полученными терминалом в два символьных периода;

h0 и h1 являются увеличением пути сигнала от антенн 1 и 2 базовой станции к антенне терминала в течение 2-символьного периода; и

n0 и n1 являются шумом, связанным с двумя полученными символами r0 и r1 соответственно.

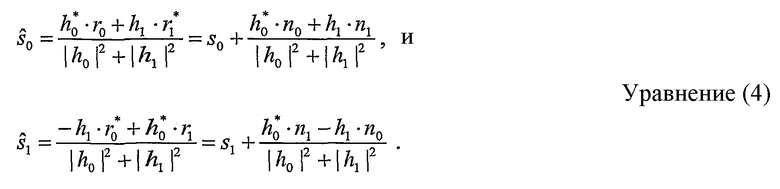

Терминал может получить оценки двух переданных символов, так s0 и s1 следующим образом:

Обработка в наборе уравнений (4) упоминается как демодуляция данных для STTD.

Демодулятор 160a включает в себя шестнадцать демодуляторов 530a-530p данных для шестнадцати SF=16 каналов. Каждый демодуляторов 530 данных выполняет демодуляцию данных для STTD для одного SF=16 канала, как показано в наборе уравнений (4). В пределах демодулятора 530 для канала Ch16,i, свернутые символы для канала Ch16,i (которые соответствуют r0 в наборе уравнений (4)), предоставляются модулю 532 задержки, модулю 534b комплексного сопряжения и множителю 536a. Модуль 532 задержки предоставляет один SF=16 символьный период задержки и предоставляет отложенные свернутые символы (которые соответствуют r1) к модулю 534a комплексного сопряжения и множителю 536c. Множитель 536a умножает свернутые символы с оценкой канала P0 * (который соответствует h0 *) и предоставляет демодулированные символы, соответствующие выражению h1 *·r1 *. Множитель 536b умножает сопряженные и отложенные свернутые символы с оценкой канала (который соответствует h1) и предоставляет демодулированные символы, соответствующие выражению h1·r1 *. Множитель 536c умножает отложенные свернутые символы с оценкой канала P0 * и предоставляет демодулированные символы, соответствующие выражению h0 *·r1. Множитель 536d умножает сопряженные свернутые символы с оценкой канала P1 и предоставляет демодулированные символы, соответствующие выражению h1·r0 *. Оценки канала обычно получают, основываясь на контрольном сигнале, переданном базовой станцией, и таким образом обычно упоминаются как контрольные оценки.

Сумматор 538a добавляет демодулированные символы от множителей 536a и 536b для получения восстановленных символов данных, соответствующие  . Сумматор 538b вычитает демодулированные символы из множителя 536d из демодулированных символов от множителя 536c для получения восстановленных символов данных, соответствующие

. Сумматор 538b вычитает демодулированные символы из множителя 536d из демодулированных символов от множителя 536c для получения восстановленных символов данных, соответствующие  . Мультиплексор 540 (MUX) получает восстановленные символы данных для

. Мультиплексор 540 (MUX) получает восстановленные символы данных для  и

и  и предоставляет преобразованные в последовательную форму восстановленные символы данных каналу Ch16,i (обозначенные как S16,i).

и предоставляет преобразованные в последовательную форму восстановленные символы данных каналу Ch16,i (обозначенные как S16,i).

Для варианта осуществления, показанного на фиг.5, шестнадцать множителей 522a-522p используются для получения свернутых символов для шестнадцати SF=16 каналов Ch16,0-Ch16,15. Четыре комплексных множителя 536a-536d используются для компенсации канала STTD для каждого физического канала. Общее количество 64 комплексных множителей, необходимое для обработки этих шестнадцати каналов Ch16,0-Ch16,15, может использоваться для HS-PDSCH.

Демодулятор может быть разработан для эксплуатации структурного характера кодов OVSF и выполнения демодуляции данных на частично свернутых символах для HS-PDSCH. Частично свернутый символ для физического канала с коэффициентом распространения L получается с помощью накопления по длине короче чем L (т.е. накапливая по L/2 или L/4). Частично свернутый символ для физического канала с коэффициентом распространения L является полностью свернутым символом для другого физического канала с коэффициентом распространения, меньшим чем L. Демодуляция данных на частично свернутых символах уменьшает число требуемых умножений.

Демодуляция данных на частично свернутых символах для HS-PDSCH может быть выполнена различными способами. Две примерных схемы описаны ниже.

1. Умножить свернутый символ для SF=4 канала Ch4,i с оценками канала и объединить с SF=4 демодулированных символов для получения восстановленных символов данных для четырех SF=16 каналов Ch16,4i-Ch16,4i+3.

2. Умножить свернутый символ для SF=8 каналов Ch8,i с оценками канала и объединить SF=8 демодулированных символов для получения восстановленных символов данных для двух SF=16 каналов Ch16,2i-Ch16,2i+1.

Схема 2 требует меньшего количества вычисления и меньшего количества доступов к памяти. Примерный дизайн для схемы 2 описан ниже.

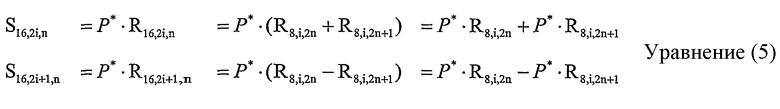

Для не-STTD режима демодуляция данных для SF=16 каналов с SF=8 свернутых символов может быть выражена как:

где P является оценкой канала;

RSF,i,n является свернутым символом для канала ChSF,i для символьного периода n; и

SSF,i,n является восстановленным символом данных для канала ChSF,i для символьного периода n.

Для режима STTD демодуляция данных для SF=16 каналов с SF=8 свернутых символов может быть выражена как:

где P0 является оценкой канала для антенны 1;

P1 является оценкой канала для антенны 2; и

Da SF,i,n является демодулированным символом для канала ChSF,i для символьного периода n, который получен с оценкой канала Pa.

В уравнениях (6)-(9) S16,2i,n является четным восстановленным символом данных для четного SF=16 канала, S16,2i,n+1 является нечетным восстановленным символом данных для четного SF=16 канала, S16,2i+1,n является четным восстановленным символом данных для нечетного SF=16 канала и S16,2i+1,n+1 является нечетным восстановленным символом данных для нечетного SF=16 канала. Четные SF=16 каналы имеют четные индексы 2i, и нечетные SF=16 каналы имеют нечетные индексы 2i+1. Четные восстановленные символы данных имеют четные SF=16 индексы символьного периода n, и нечетные восстановленные символы данных имеют нечетные индексы символьного периода n+1.

Как показано в уравнениях (6)-(9), для режима STTD четыре последовательных восстановленных символа R8,i,2n-R8,i,2n+3 для одного SF=8 канала Ch8,i обрабатываются для получения четырех восстановленных символов данных для двух SF=16 каналов Ch16,2i и Ch16,2i+1 (т.е. один нечетный и один четный восстановленный символ данных для каждого SF=16 канала). Каждый SF=8 свернутый символ R8,i,x (где x=2n, 2n+1, 2n+2 или 2n+3) умножаются на Po * и P1 для того, чтобы получить два демодулированных символа D0 S,i,x и D1 S,i,x соответственно. Каждый демодулированный символ используется для двух из четырех восстановленных символов данных для каналов Ch16,2i и Ch16,2i+1. Каждый свернутый символ используется, таким образом, для всех четырех восстановленных символов данных для каналов Ch16,2i и Ch16,2i+1.

Фиг.6 показывает блок-схему демодулятора 160b, который выполняет демодуляцию данных на свернутых символах для HS-PDSCH. Демодулятор 160b является вариантом воплощения демодулятора 160 фиг.1. В демодуляторе 160b множитель 612 умножает полученные выборки с дескремблированным кодом S* dl,u и обеспечивает дескремблированные выборки восьми SF=8 сверткам 620a-620h для восьми SF=8 каналов Ch8,0-Ch8,7 соответственно.

В пределах сверток 620 для канала Ch8,i множитель 622 умножает дескремблированные выборки с кодом OVSF C8,i для канала Ch8,i. Сумматор 624 накапливает вывод от множителя 622 по длине кода OVSF C8,i (т.е. более чем 8 сегментов) и предоставляет свернутые символы для канала Ch8,i. Свертки 620a-620h предоставляют свернутые символы для восьми каналов Ch8,0-Ch8,7 к демодуляторам 630a-630h данных соответственно.

Каждый демодулятор 630 данных включает в себя модуль 640 компенсации канала и объединитель 650 символов. В пределах демодулятора 630 данных для канала Ch8,i свернутые символы для канала Ch8,i предоставляются модулям 642a и 642b в модуле 640 компенсации канала. Каждый модуль 642 предоставляет или полученные свернутые символы или комплексно сопряженные свернутые символы, как обозначено уравнениями (6)-(9), к соответствующему множителю 644. Множитель 644a умножает вывод от модуля 642a с оценкой канала P* 0 и предоставляет демодулированные символы D0 8,i,2n к модулю 652a задержки в пределах объединителя 650 символов. Модули 652a, 652b и 652c задержки соединены последовательно и предоставляют отложенные демодулированные символы D0 8,i,2n+1, D0 8,i,2n+2 и D0 8,i,2n+3 соответственно. Точно так же множитель 644b умножает вывод от модуля 642b с оценкой канала P1 и предоставляет демодулированные символы модулю 654a задержки. Модули 654a, 654b и 654c задержки соединены последовательно и предоставляют отложенные демодулированные символы D1 8,i,2n+1, D1 8,i,2n+2 и D1 8,i,2n+3 соответственно.

Сумматор 656a суммирует демодулированные символы D0 8,i,2n, D0 8,i,2n+1, D1 8,i,2n+2 и D1 8,i,2n+3, как показано в уравнении (6), и предоставляет восстановленный символ данных S16,2i,n. Сумматор 656b суммирует демодулированные символы D0 8,i,2n+2 и D0 8,i,2n+3 и вычитает демодулированные символы D1 8,i,2n и D1 8,i,2n+1, как показано в уравнении (7), и предоставляет восстановленный символ данных S16,2i,n+1. Мультиплексор 658a получает восстановленные символы данных S16,2i,n и S16,2i,n+1 и предоставляет преобразованные в последовательную форму восстановленные символы данных для канала Ch16,2i. Сумматор 656c суммирует демодулированные символы и вычитает демодулированные символы D0 8,i,2n и D1 8,i,2n+2, как показано в уравнении (8), и предоставляет восстановленный символ данных S16,2i+1,n. Сумматор 656d суммирует демодулированные символы D1 8,i,2n+1 и D0 8,i,2n+2 и вычитает демодулированные символы D1 8,i,2n и D0 8,i,2n+3,как показано в уравнении (9), и предоставляет восстановленный символ данных S16,2i+1,n+1. Мультиплексор получает восстановленные символы данных S16,2i+1,n и S16,2i+1,n+1 и предоставляет преобразованные в последовательную форму восстановленные символы данных для канала Ch16,2i+1.

Для варианта воплощения, показанного на фиг.6, демодуляция данных с SF=8 свернутых символов требует только двух комплексных множителей 644a и 644b для каждой пары каналов, или всего шестнадцать комплексных множителей для всех шестнадцати SF=16 каналов. Это является одной четвертью числа комплексных множителей, требуемых для варианта реализации, показанного на фиг.5.

Аппаратные средства для демодулятора могут быть дополнительно уменьшены при дизайне TDM. Для дизайна TDM используется один модуль механизма демодуляции данных (DDT) для выполнения обработки для всех восьми SF=8 каналов способом TDM для того, чтобы получить восстановленные символы данных для всех шестнадцати SF каналов. В одном варианте воплощения модуль DDE циклически проходит восемь SF=8 каналов в восьми тактовых циклах. Для каждого SF=8 канала модуль DDE вычисляет два демодулированных символа для свернутого символа для этого канала и накапливают эти демодулированные символы с результатами частичного объединения для четырех восстановленных символов данных для двух SF=16 каналов, соответствующих каналу SF=8. Буфер символа используется для хранения результатов объединения.

Фиг.7 показывает блок-схему демодулятора 160c, который выполняет демодуляцию данных на SF=8 свернутых символов для HS-PDSCH способом TDM. Демодулятор 160c является другим вариантом воплощения демодулятора 160 фиг.1. Демодулятор 160c включает в себя модуль 710 свертки, модуль 720 DDE для HS-PDSCH и модуль 770 DDE для HS-SCCH. Демодулятор 160c может также включать в себя другие модули обработки (например, для других физических каналов), которые не показаны на фиг.7 для простоты.

В пределах модуля 710 свертки множитель 712 умножает полученные выборки с дескремблированным кодом S* dl,u и предоставляет дескремблированные выборки. 8-канальный модуль 714 свертки выполняет свертывание на дескремблированных выборках для восьми каналов Ch8,0-Ch8,7 и предоставляет свернутые символы для этих восьми каналов. Модуль 716 свертки выполняет свертывание на дескремблированных выборках для всех четырех HS-SCCH и предоставляет свернутые символы для этих четырех каналов.

В пределах модуля 720 DDE селектор 730 канала получает от модуля 714 свертки свернутые символы для восьми SF=8 каналов Ch8,0-Ch8,7 и предоставляет один свернутый символ для одного канала одновременно модулю 740 компенсации канала. Модуль 740 компенсации канала умножает свернутый символ R8,i для канала Ch8,i с оценкой канала P* 0 для антенны 1 и оценкой канала P1 для антенны 2 и предоставляет демодулированные символы D0 8,i и D1 8,i на объединитель 750 символов.

Объединитель 750 символов объединяет все демодулированные символы для каждого восстановленного символа данных. Объединение выполняется кусочно по мере того, как получаются демодулированные символы для каждого SF=8 свернутого символа. Объединение дополнительно зависит от того, использует или нет базовая станция STTD, как описано ниже. Буфер 760 символов предоставляет накопленные символы, которые являются промежуточными результатами объединения, на объединитель 750 символов. Объединитель 750 символов объединяет накопленные символы с потоком демодулированных символов и предоставляет объединенные символы, которые являются модифицированными результатами объединения. Буфер 760 символов хранит объединенные символы от объединителя 750 символов, которые становятся восстановленными символами данных после объединения всех демодулированных символов. Контроллер 762 DDE предоставляет информацию управления для селектора 730 канала, модуля 740 компенсации канала, объединителя 750 символа и буфера 760 символа.

В модуле 770 DDE селектор 772 канала получает от модуля 716 свертки свернутые символы для четырех SF=128 каналов, используемых для HS-SCCH, и предоставляет свернутый символ для одного канала одновременно модулю 774 компенсации канала. В модуле 774 компенсации канала мультиплексор 778 получает оценки канала P0 и P1 и предоставляет оценку канала для надлежащей антенны множителю 776. Множитель 776 выполняет комплексное умножение свернутого символа из селектора 772 канала с оценкой канала от мультиплексора 776, и предоставляет демодулированный символ на объединитель 780 символов. Объединитель 780 символов объединяет все демодулированные символы для каждого восстановленного символа данных для HS-SCCH. Буфер 782 символов предоставляет накопленные символы на объединитель 780 символов для того, чтобы объединить их с потоком демодулированных символов и сохраняет объединенные символы от объединителя 780 символов. Контроллер 784 DDE предоставляет управляющую информацию селектору 772 канала, модулю 774 компенсации канала, объединителю 780 символов и буферу 782 символов.

Фиг.8 показывает блок-схему 8-канального модуля 714 свертки в пределах демодулятора 160c. Входные выборки (т.е. дескремблированные выборки) предоставляются к четырем множителям 812a-812h для четырех каналов Ch4,0-Ch4,3 соответственно. Каждый множитель 812 умножает дескремблированные выборки с соответствующими кодами OVSF C4,i для канала Ch4,i и предоставляет выборки без образцов. Накопитель 814 накапливают каждую группу четырех выборок без образцов для четырех сегментов кода OVSF C4,i для получения свернутого символа для канала Ch4,i. Накопители 814a-814d предоставляют свернутые символы для SF=4 каналов Ch4,0-Ch4,3 соответственно.

Четыре модуля 820a-820d свертки получают свернутые символы для каналов Ch4,0-Ch4,i соответственно. В пределах модулей 820 свертки для канала Ch4,3 свернутые символы для этого канала предоставляются к сумматорам 822 и 824 и мультиплексору 826. Для каждой пары SF=4 свернутых символов первый символ в паре проходит через мультиплексор 826 и сохраняется в регистре 828. Когда второй свернутый символ в паре получен, сумматор 822 суммирует первый и второй символы в паре для того, чтобы получить свернутый символ для SF=8 канала Ch8,2i. Сумматор 824 вычитает второй символ в паре из первого символа для того, чтобы получить свернутый символ для SF=8 канала Ch8,2i+1. Свернутый символ для канала Ch8,2i направляется через мультиплексор 826 и сохраняется в регистре 828, и свернутый символ для канала Ch8,2i+1 сохраняется в регистре 830. Каждый модуль 820 свертки предоставляет свернутые символы для пары SF=8 каналов Ch8,2i-Ch8,2i+1. В селекторе 730 канала мультиплексор 840 получает свернутые символы для всех восьми SF=8 каналов Ch8,0 и Ch8,7 от модуля 820a-820d свертки. Мультиплексор 840 предоставляет свернутый символ R8,i для одного SF=8 канала одновременно, основываясь на сигнале управления от контроллера 762 DDE. Модуль 842 получает свернутый символ от мультиплексора 840 и предоставляет сопряженный свернутый символ R* 8,i.

Демодулятор 160c может выполнить демодуляцию данных на частично свернутых символах и для не-STTD режима и для STTD режима. Демодуляция данных для режима STTD описана ниже.

Фиг.9 показывает блок-схему модуля 720 DDE для HS-PDSCH. Модуль 720 DDE используется конвейерным способом и обрабатывает один свернутый символ для одного SF=8 канала в каждом тактовом цикле. Селектор 730 канала получает свернутые символы для восьми SF=8 каналов от модуля 710 свертки. Селектор 730 канала циклически проходит восемь SF=8 каналов в восьми тактовых циклах и для каждого тактового цикла предоставляет один свернутый символ для одного канала модулю 740 компенсации канала.

В модуле 740 компенсации канала мультиплексор 940a получает свернутый символ R8,i и сопряженный свернутый символ R* 8,i для канала Ch8,i от селектора 730 канала и предоставляет надлежащим образом свернутый символ к множителю 942a. Мультиплексор 940b также получает свернутый символ R8,i и сопряженный свернутый символ R* 8,i и предоставляет надлежащим образом свернутый символ множителю 942b. Множитель 942a умножает свернутый символ от мультиплексора 940a или на P0 * или на P1 и предоставляет демодулированный символ регистру 946a. Точно так же множитель 942b умножает свернутый символ от мультиплексора 940b или на P1 или на P0 * и предоставляет демодулированный символ регистру 946b. В зависимости от управляющей информации для мультиплексоров 940a, 940b, 944a и 944b регистр 946a предоставляет или демодулированный символ D0 8,i, или D1 8,i (обозначенный как D0/1 8,i) на сумматоры 952a и 952b в объединителе 750 символов, и регистр 946b предоставляет другой демодулированный символ D1 8,i или D0 8,i (обозначенный как D1/0 8,i) на сумматоры 952c и 952d.

Чтобы достигнуть желательной производительности одного SF=8 свернутого символа за тактовый цикл, каждый доступ к памяти буфера 760 символа идет для четырех SF=16 каналов. Четные и нечетные накопленные символы для четырех SF=16 каналов найдены в буфере 760 символа для каждой операции чтения. Четные и нечетные объединенные символы для четырех SF=16 каналов извлекаются из буфера 760 символа для каждой операции записи. Шестнадцать SF=16 каналов разделены на четыре группы следующим образом:

каналы группы 0: Ch16,0, Ch16,1, Ch16,2 и Ch16,3,

каналы группы 1: Ch16,4, Ch16,5, Ch16,6 и Ch16,7,

каналы группы 2: Ch16,8, Ch16,9, Ch16,10 и Ch16,11,и

каналы группы 3: Ch16,12, Ch16,13, Ch16,14 и Ch16,15.

Обработка для канала группы 0 описана ниже. Когда селектор 730 канала предоставляет свернутый символ R8,0 для канала Ch8,0, четные и нечетные накопленные символы для четырех SF=16 каналов в группе 0 извлекаются из буфера 760 символа, четные накопленные символы сохраняются в регистре 958a, и нечетные накопленные символы сохраняются в регистре 958b, мультиплексор 954a получает четные накопленные символы для первого и третьего SF=16 каналов в группе, Ch16,0 и Ch16,2, и мультиплексор 954b получают четные накопленные символы для второго и четвертого SF=16 каналов в группе, Ch16,1 и Ch16,3. Символ «k» на фиг.9 обозначает индекс канала в пределах группы. Мультиплексор 954c получает нечетные накопленные символы для каналов Ch16,0 и Ch16,2, и мультиплексор 954d получает нечетные накопленные символы для каналов Ch16,1 и Ch16,3.

Для свернутого символа R8,0 для канала Ch8,0 мультиплексоры 954a и 954b предоставляют четные накопленные символы для каналов Ch16,0 и Ch16,1 на сумматоры 952a и 952b соответственно, и мультиплексоры 954c и 954d предоставляют нечетные накопленные символы для каналов Ch16,0 и Ch16,1 на сумматоры 952c и 952d соответственно. Каждый сумматор 952 или добавляет или вычитает демодулированный символ из соответствующего регистра 946 с накопленным символом от соответствующего мультиплексора 954 и предоставляет объединенный символ регистру 956. В назначенное время регистр 956 предоставляет четыре объединенных символа от сумматоров 952a-952d (которые имеются для четных и нечетных символов для каналов Ch16,0 и Ch16,1) на буфер 760 символов для хранения.

Для свернутого символа R8,1 для канала Ch8,1 мультиплексоры 954a и 954b предоставляют четные накопленные символы для каналов Ch16,2 и Ch16,3 на сумматоры 952a и 952b соответственно, и мультиплексоры 954c и 954d предоставляют нечетные накопленные символы для каналов Ch16,2 и Ch16,3 на сумматоры 952c и 952d соответственно. Каждый сумматор 952 или добавляет или вычитает демодулированный символ из соответствующего регистра 946 с накопленным символом от соответствующего мультиплексора 954 и предоставляет объединенный символ к регистру 956. Регистр 956 предоставляет четыре объединенных символа для каналов Ch16,2 и Ch16,3 к буферу 760 символа для хранения.

Обработка для других SF=8 свернутых символов для групп каналов 1, 2 и 3 происходит сходным образом, как и для группы канала 0. Когда селектор 730 канала предоставляет свернутые символы для SF=8 каналов Ch8,2, Ch8,4 и Ch8,6, буфер 760 символа предоставляет четные и нечетные накопленные символы для четырех SF=16 каналов в группах 1, 2 и 3 соответственно на мультиплексоры 954a-954d. Для четного SF=8 канала мультиплексоры 954a-954d предоставляют четные и нечетные накопленные символы для первой пары SF=16 каналов в группе. Для нечетных SF=8 каналов мультиплексоры 954a-954d предоставляют четные и нечетные накопленные символы для второй пары SF=16 каналов в группе.

Фиг.10A и 10B показывает конвейерную обработку модулем 720 DDE для режима STTD. В тактовом цикле 0 четные и нечетные накопленные символы для Ch16,0-Ch16,3 извлекаются из буфера 760 символов и сохраняются в регистрах 958a и 958b. Также в тактовом цикле 0 свернутые символы R8,0 для канала Ch8,0 умножается на оценки канала P0 * и P1, и демодулированные символы D0 8,0 и D1 8,0 сохраняются в регистрах 946a и 946b. В тактовом цикле 1 демодулированные символы D0 8,0 иD1 8,0 из регистров 946a и 946b объединяются с четными и нечетными накопленными символами для Ch16,0 и Ch16,1, и объединенные символы сохраняются в регистре 956. Также в тактовом цикле 1 свернутый символ R8,1 для канала Ch8,1 умножается на оценку канала P* 0 и P1, и демодулированные символы D0 8,1 и D1 8,1 сохраняются в регистрах 946a и 946b.

В тактовом цикле 2 демодулированные символы D0 8,1 и D1 8,1 от регистров 946a и 946b объединяются с четными и нечетными накопленными символами для Ch16,2 и Ch16,3, и объединенные символы сохраняются в регистре 956. В том же самом тактовом цикле свернутый символ R8,2 для канала Ch8,2 умножается на оценки канала P* 0 и P1, и демодулированные символы D0 8,1 и D1 8,1 сохраняются в регистрах 946a и 946b. Также в тактовом цикле 2 четные и нечетные накопленные символы для Ch16,4-Ch16,7 извлекаются из буфера 760 символа и сохраняются в регистрах 958a и 958b.

В тактовом цикле 3 объединенные символы для Chl6,0-Chl6,0 из регистров 956 сохраняются обратно в буфер 760 символа. В том же самом тактовом цикле демодулированные символы D0 8,1 и D1 8,1 из регистров 946a и 946b символов объединяются с четными и нечетными накопленными символами для Chl6,4 и Chl6,5, и объединенные символы сохраняются в регистре 956. Также в тактовом цикле 3 свернутый символ 3 для канала Ch8,3 умножается на оценки канала P* 0 и P1 и демодулированные символы D0 8,3 и D1 8,4, сохраненные в регистраторах 946a и 946b.

Как показано на фиг.10A, обработка для одного свернутого символа для одного канала SF=8 охватывает четыре тактовых цикла. Обработка для свернутых символов для других SF=8 каналов продолжает сходным образом. Фиг.10A и 10B также показывают скорость прохождения одного SF=8 свернутого символа за период времени. К буферу 760 символа обращаются в каждом четном тактовом цикле для извлечения накопленных символов для группы четырех SF=16 каналов, и обращаются в каждом нечетном тактовом цикле для сохранения объединенных символов для группы четырех SF=16 каналов.

Фиг.11 показывает вариант воплощения буфера 760 символа в модуле 720 DDE. Чтобы достигнуть высокой скорости передачи данных, требуемой для поддержки демодуляции данных одного SF=8 свернутого символа в период времени, буфер 760 символа осуществлен с двумя банками памяти, 1110a и 1110b. Банк 1110a памяти хранит объединенные символы для восьми SF=16 каналов в группах 0 и 2. Банк 1110b памяти хранит объединенные символы для восьми SF=16 каналов в группах 1 и 3. Каждый банк 1110 памяти хранит один слот объединенных символов для всех восьми SF=16 каналов. Так как слот включает в себя 160 символов для SF=16 в W-CDMA, каждый банк 1110 памяти хранит 1280 символов (т.е. 1280=160×8) для восьми SF=16 каналов.

Каждое местоположение адреса хранит два последовательных объединенных символа для четырех SF=16 каналов. С архитектурой памяти, показанной на фиг.11, четные и нечетные символы для одной группы из четырех SF=16 каналов могут быть извлечены из одного местоположения памяти в одном банке памяти в одном тактовом цикле. Объединенные символы для другой группы четырех SF=16 каналов могут быть записаны в одно местоположение в другом банке памяти в следующем тактовом цикле. К банкам 1110a и 1110b памяти обращаются, таким образом, на дополнительных тактовых циклах.

Банки 1110a и 1110b памяти сохраняются на диск в начале каждого слота для того, чтобы установить все накопленные символы в ноль. Этим способом накопление может быть выполнено должным образом, когда приходит первый свернутый символ для каждого восстановленного символа данных. Восстановленные символы данных в банках памяти могут быть обработаны RX процессором 162 данных, как только объединение будет закончено.

Обратимся вновь к фиг.10B, после того как все восемь свернутых символов для этих восьми SF=8 каналов Ch8,0-Ch8,7 в течение символьного периода 2n обработаны, та же самая обработка повторяется для свернутых символов для тех SF=8 каналов в течение следующего символьного периода 2n+1, начинающегося на правой стороне толстой сплошной линии 1010 на фиг.10B.

Как показано в уравнениях (6)-(9), четыре демодулированных символа для четырех последовательных символьных периодов 2n - 2n+3 для SF=8 канала Ch8,i объединяются для того, чтобы получить четыре восстановленных символа данных для двух SF=16 каналов Ch16,2i иCh16,2i+1. В таблице 1 перечислены (1) свернутые символы, предоставленные мультиплексорами 940a и 940b, и оценки каналов, предоставленные мультиплексорами 944a и 944b множителям 942a и 942b и (2) операция (или добавление, или вычитание), выполняемая каждым из сумматоров 952a-952d в течение каждого символьного периода. Управляющая информация для мультиплексоров 940a и 940b, 944a и 944b, и 954a-954d предоставляются контроллером 762 DDE.

Демодулятор 160c может также выполнить демодуляцию данных для не-STTD режима. В этом случае процессоры в объединителе 750 символа конфигурируются для того, чтобы реализовать набор уравнений (5) для не-STTD режима. Свернутый символ R8,i для SF=8 канала Ch8,i умножается только на одну оценку канала P для одной антенны для генерации этого демодулированного символа. Два демодулированных символа для двух символьных периодов объединяются (добавлением и вычитанием) для того, чтобы получить два восстановленных символа данных для двух SF=16 каналов Ch16,2i и Ch16,2i+1, как показано в наборе уравнений (5).

Для варианта воплощения, показанного на фиг.7-11, демодулятор 160c выполняет демодуляцию данных на свернутых символах для получения восстановленных символов данных для SF=16 каналов. Демодулятор 160c объединяет два последовательных свернутых символа для SF=4 канала Ch4,i для получения двух SF=8 каналов свернутых символов для двух каналов Ch8,2i и Ch8,2i+1. Демодулятор 160c умножает свернутый символ для канала Ch8,2i на оценку канала и объединяет демодулированные символы с накопленными символами для двух SF=16 каналов Ch16,4i и Ch16,4i+1. Демодулятор 160c умножает свернутый символ для канала Ch8,2i+1 на оценку канала и объединяет демодулированные символы с накопленными символами для двух SF=16 каналов Ch16,4i+2 и Ch16,4i+3. Демодулятор 160c сохраняет объединенные символы для всех четырех SF=16 каналов Ch16,4i-Ch16,4i+3 назад в буфер символов.

В альтернативном варианте воплощения демодулятор может выполнить демодуляцию данных на свернутых символах для SF=4 каналов для получения восстановленных символов данных для SF=16 каналов. Для этого варианта воплощения демодулятор может умножить свернутый символ для SF=4 канала Ch4,i с оценками канала, объединить демодулированные символы с накопленными символами для четырех SF=16 каналов Ch16,4i-Ch16,4i+3, и сохранить объединенные символы для этих четырех SF=16 каналов обратно в буфере символов.

Вообще, демодулятор может выполнить демодуляцию данных на свернутых символах для SF=L каналах для того, чтобы получить восстановленные символы данных для SF=M·L каналов, где M>1. Меньше вычислений и меньшее количество доступов к памяти могут потребоваться, когда M=2. Например, демодуляция данных на SF=8 свернутых символов требует меньшего количества вычислений и меньшего количества доступов к памяти, чем демодуляция данных на SF=4 свернутых символах.

Фиг.12 показывает блок-схему 1200 процесса выполнения демодуляции данных на частично свернутых символах. Входные выборки являются свернутыми для того, чтобы получить свернутые символы для первого кодового канала с первым фактором распространением L (т.е. SF=L=8) (шаг 1212). Свернутые символы умножаются на оценки каналов для того, чтобы получить демодулированные символы (шаг 1214). Группы демодулированных символов для различных символьных периодов после этого объединяются для того, чтобы получить восстановленные символы данных для второго кодового канала со вторым коэффициентом распространения M·L, который является целочисленным множителем первого коэффициента распространения (т.е. SF=M·L=16 и М=2) (шаг 1216). Для структурных ортогональных кодов типа кодов OVSF свернутые символы для одного первого кодового канала могут использоваться для получения восстановленных символов данных для М вторых кодовых каналов.

Компенсация канала и объединение символа зависят от того, используется ли не-STTD или STTD режим. Для не-STTD режима каждый свернутый символ умножается на одну оценку канала для одной антенны для того, чтобы получить один демодулированный символ. М демодулированных символов для М символьных периодов объединяются для получения одного восстановленного символа данных для второго кодового канала. Для режима STTD каждый свернутый символ умножается на две оценки канала для двух антенн для того, чтобы получить два демодулированных символа. 2·M демодулированных символов для 2·M символьных периодов объединяются для получения одного восстановленного символа данных для второго кодового канала.

Свертывание на шаге 1212, компенсация канала на шаге 1214 и объединение символов на шаге 1216 может быть выполнено для множества первых кодовых каналов. Компенсация канала и объединение символа могут быть выполнены в TDM и конвейерным способом для того, чтобы уменьшить аппаратную сложность.

Сигнал, передаваемый базовой станцией 110, может достигнуть терминала 150 через множество путей сигнала. Полученный сигнал в терминале может, таким образом, включать в себя множество мультипутевых компонентов, один мультипутевой компонент для каждого пути сигнала. Беспорядочный получатель часто используется для обработки множества мультипутевых компонентов в полученном сигнале. Беспорядочный получатель обычно включает в себя один или более элементов поиска (или просто «искатель»), который ищет сильные мультипутевые компоненты в полученном сигнале. Искатели обеспечивают синхронизацию и силу каждого мультипутевого компонента, найденного в полученном сигнале. Каждый мультипутевой компонент, представляющий интерес (т.е. достаточной силы), после этого обрабатывается для получения восстановленных символов данных для этого мультипутевого компонента. Восстановленные символы данных для всех мультипутевых компонентов, представляющих интерес, объединяются для того, чтобы получить конечные восстановленные символы данных, которые после этого обрабатываются (т.е. с них снимается чередование и они декодируются) для восстановления переданных данных.

Демодулятор 160c может использоваться для обработки любого числа мультипутевых компонентов, представляющих интерес. В модуле 154 получателя полученные выборки сохраняются в буфере выборок так, чтобы они могли быть извлечены и обработаны множество раз для различных мультипутевых компонентов. Для каждого мультипутевого компонента, который будет обработан, надлежащая доля полученных выборок извлекается из буфера выборок (например, основываясь на синхронизации мультипутевой компоненты) и обрабатывается для получения свернутых символов, выравнивается в границах символа. Каждый свернутый символ умножается на оценку(и) канала, и демодулированный символ(ы) объединяется с надлежащими накопленными символами из буфера 760 символа. Контроллер 762 DDE получает информацию синхронизации для мультипутевого компонента, который обрабатывается, и определяет надлежащие накопленные символы для извлечения из буфера 760 символов для объединения. Буфер 760 символов также функционирует с «компенсацией сдвига по фазе» для выравнивания по времени символов для различных мультипутевых компонентов для объединения.

Для ясности, способы выполнения демодуляции данных на частично свернутых символах были определенно описаны для HS-PDSCH, используемого для HSDPA в W-CDMA. Эти способы могут использоваться для других систем и стандартов CDMA. Например, эти методы могут использоваться для 1xEV-DV (1x развитие, данные и голос), который является стандартом, хорошо известным в данной области техники. Способы, описанные здесь, могут использоваться вместе и без разнообразия передач (т.е., STTD). Способы, описанные здесь, могут также использоваться как для передачи по восходящей, так и по нисходящей линии связи.

Способы, описанные здесь, могут быть осуществлены различными средствами. Например, эти способы могут быть осуществлены аппаратными средствами, программным обеспечением или их комбинацией. Для аппаратного осуществления процессорные модули, используемые для выполнения демодуляции данных на частично свернутых символах, могут быть осуществлены в пределах одной или более специализированных для приложения интегральных схем (ASIS), процессоров цифровых сигналов (DSP), цифровых устройств обработки сигналов (DSPD), программируемых логических устройств (PLD), программируемых пользователем вентильных матриц (FPGA), процессоров, контроллеров, микроконтроллеров, микропроцессоров, других электронных модулей, предназначенных для выполнения функций, описанных здесь, или в их комбинации. Способы могут также быть осуществлены на одной или более интегральных схемах.

Для программного осуществления способы, описанные здесь, могут быть осуществлены в модулях (т.е. процедурах, функциях и так далее), которые выполняют функции, описанные здесь. Программные коды могут быть сохранены в модуле памяти (например, модуль 142 или 172 памяти на фиг.1) и исполняться процессором (например, контроллером 140 или 170). Модуль памяти может быть осуществлен в процессоре или быть внешним к процессору, в этом случае он может быть подсоединен к процессору через различные средства, известные в данной области техники.

Предшествующее описание раскрытых вариантов воплощения предоставлено для того, чтобы дать возможность любому специалисту в данной области техники сделать или использовать данное изобретение. Различные модификации к этим вариантам воплощения будут очевидны специалистам в данной области техники, и общие принципы, определенные здесь, могут быть применены к другим вариантам воплощения, не отступая от сущности или объема изобретения. Таким образом, данное изобретение не предназначено для того, чтобы быть ограниченным вариантами воплощения, показанными здесь, но должно получить самые широкие возможности, совместимые с принципами и новыми особенностями, раскрытыми здесь.

Изобретение относится к системам связи. Технический результат заключается в повышении эффективности демодуляции данных. Интегральная схема, действующая для выполнения демодуляции данных, содержит: модуль свертки, действующий для свертки входной выборки и предоставления свернутых символов для первого кодового канала с первым коэффициентом распространения; модуль компенсации канала, действующий для перемножения свернутых символов с оценками канала и предоставления демодулированных символов для первого кодового канала; и объединитель символов, действующий для объединения группы демодулированных символов для первого кодового канала для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения, который является целочисленным множителем первого коэффициента распространения. 7 н. и 19 з.п. ф-лы, 13 ил., 1 табл.

модуль свертки, действующий для свертки входной выборки и предоставления свернутых символов для первого кодового канала с первым коэффициентом распространения;

модуль компенсации канала, действующий для перемножения свернутых символов с оценками канала и предоставления демодулированных символов для первого кодового канала; и

объединитель символов, действующий для объединения группы демодулированных символов для первого кодового канала для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения, который является целочисленным множителем первого коэффициента распространения.

модуль свертки, действующий для свертки входной выборки и предоставления свернутых символов для первого кодового канала с первым коэффициентом распространения;

модуль компенсации канала, действующий для перемножения свернутых символов с оценками канала и предоставления демодулированных символов для первого кодового канала; и

объединитель символов, действующий для объединения группы демодулированных символов для первого кодового канала для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения, который является целочисленным множителем первого коэффициента распространения.

средство для свертки входной выборки для получения свернутых символов для первого кодового канала с первым коэффициентом распространения;

средство для перемножения свернутых символов с оценкой канала для получения демодулированных символов для первого кодового канала;

и средство для объединения группы демодулированных символов для первого кодового канала для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения, который является целочисленным множителем первого коэффициента распространения.

свертки входных выборок для получения свернутых символов для первого кодового канала с первым коэффициентом распространения;

перемножения свернутых символов с оценками канала для получения демодулированных символов для первого кодового канала; и

объединения группы демодулированных символов для первого кодового канала для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения, который является целочисленным множителем первого коэффициента распространения.

свертывают входные выборки для получения свернутых символов для первого кодового канала с первым коэффициентом распространения;

перемножают свернутые символы для первого кодового канала с оценкой канала для получения демодулированных символов; и

объединяют группы демодулированных символов для первого кодового канала для получения восстановленных символов данных для второго кодового канала со вторым коэффициентом распространения, который является целочисленным множителем первого коэффициента распространения.

модуль свертки, действующий для свертки входной выборки и предоставления свернутых символов множеству первых кодовых каналов с первым коэффициентом распространения;

модуль компенсации канала, действующий для перемножения свернутых символов для каждого из множества первых кодовых каналов с оценками канала и предоставления демодулированных символов для первого кодового канала; и

объединитель символов, действующий для объединения группы демодулированных символов для каждого из множества первых кодовых каналов, которые получают восстановленные символы данных для набора вторых кодовых каналов со вторым коэффициентом распространения и соответствующих первому кодовому каналу, при этом второй коэффициент распространения является целочисленным множителем первого коэффициента распространения.

селектор канала, действующий для получения свернутых символов для множества первых кодовых каналов и предоставления свернутых символов для одного первого кодового канала в один момент времени к модулю компенсации канала.

буфер символов, действующий для предоставления накопленных символов и хранения объединенных символов.

средство для свертки входной выборки для получения свернутых символов для множества первых кодовых каналов с первым коэффициентом распространения;

средство для перемножения свернутых символов для каждого из множества первых кодовых каналов с оценкой канала для того, чтобы получить демодулированные символы для первого кодового канала; и

средство для объединения группы демодулированных символов для каждого из множества первых кодовых каналов, которые получают восстановленные символы данных для набора вторых кодовых каналов со вторым коэффициентом распространения и соответствующих первому кодовому каналу, при этом второй коэффициент распространения является целочисленным множителем первого коэффициента распространения.

| НОСИТЕЛЬ ЗАПИСИ, СПОСОБ И УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИОННЫХ ФАЙЛОВ И УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ИНФОРМАЦИИ С ТАКОГО НОСИТЕЛЯ ЗАПИСИ | 1991 |

|

RU2073913C1 |

| КОНВЕЙЕРНЫЙ ПРИЕМНИК БАЗОВОЙ СТАНЦИИ СОТОВОЙ ЯЧЕЙКИ ДЛЯ УПЛОТНЕНННЫХ СИГНАЛОВ С РАСШИРЕННЫМ СПЕКТРОМ | 1996 |

|

RU2154913C2 |

| US 2002136278 A, 26.09.2002 | |||

| US 6222875 В1, 24.04.2001 | |||

| 0 |

|

SU156162A1 | |

Авторы

Даты

2008-10-27—Публикация

2004-10-18—Подача