Область техники

Настоящее изобретение относится в общем к системе беспроводной связи. Более конкретно, настоящее изобретение относится к устройству и способу обработки цифровых сигналов в системе беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA).

Описание предшествующего уровня техники

Система мобильной связи, использующая технологию сотовой связи, является типичной системой беспроводной связи. Такая система мобильной связи использует схемы множественного доступа для того, чтобы одновременно связываться с множеством пользователей. Схемы множественного доступа классифицируются как схема множественного доступа с временным разделением каналов (TDMA), схема множественного доступа с кодовым разделением каналов (CDMA) и схема множественного доступа с частотным разделением каналов (FDMA). Система связи, использующая схему CDMA, с быстрым прогрессом технологии CDMA получила свое развитие от предшествующей системы связи, главным образом предоставлявшей голосовую услугу, до усовершенствованной системы связи, обеспечивающей передачу пакетных данных с высокой скоростью. Для того чтобы преодолеть ограниченное использование источников кода в схеме CDMA, была предложена схема с множественным доступом с ортогональным частотным разделением каналов (OFDMA).

Схема мультиплексирования с ортогональным частотным разделением каналов (OFDM) представляет собой схему передачи данных с использованием множества несущих частот и является видом схемы модуляции с множеством несущих (MCM), которая параллельно преобразует последовательный входной поток символов в параллельные символы и модулирует отдельные параллельные символы с помощью множества ортогональных поднесущих, то есть множества ортогональных каналов поднесущих, перед передачей.

Схема MCM впервые была применена в радиосвязи военного назначения высокой точности (HF) в конце 1950-х годов. Схема OFDM, которая перекрывает множество ортогональных поднесущих, разрабатывается с 1970-х годов, но имеет ограничения в применении к фактической системе из-за проблем в реализации ортогональной модуляции на множестве несущих. Однако быстрое развитие схемы OFDM было начато с опубликования в 1971 году работы Вайнштейна и др., посвященной возможности эффективной модуляции/демодуляции на основе OFDM с использованием дискретного преобразования Фурье (DFT). DFT преобразует сигнал временной области в сигнал частотной области, тогда как обратное дискретное преобразование Фурье (IDFT), процесс, т.е. обратный процессу DFT, преобразует сигнал частотной области в сигнал временной области. Кроме того, возможное использование защитного интервала и возможная вставка циклического префикса (CP) в защитный интервал добиваются уменьшенных дефектов системы, вызванных многолучевым распространением и расширением за счет задержки.

Благодаря развитию технологии OFDM схема OFDM теперь широко применяется к таким технологиям цифровой передачи как цифровое радиовещание (DAB), цифровое телевидение (DTV), беспроводная локальная сеть (WLAN) и режим беспроводной асинхронной передачи (WATM). То есть схема OFDM, которая широко не использовалась из-за своей аппаратной сложности, может теперь быть осуществлена благодаря современному развитию различных технологий обработки цифрового сигнала, включающих в себя быстрое преобразование Фурье (FFT) и обратное быстрое преобразование Фурье (IFFT). Схема OFDM, подобная традиционной схеме мультиплексирования с частотным разделением каналов (FDM), характеризуется передачей множества поднесущих при сохранении ортогональности между ними, таким образом обеспечивая оптимальную эффективность передачи во время высокоскоростной передачи данных. Кроме того, схема OFDM имеет высокую частотную эффективность и является устойчивой против замирания вследствие многолучевого распространения, обеспечивая оптимальную эффективность передачи при высокоскоростной передаче данных. Кроме того, так как схема OFDM перекрывает частотные спектры, она имеет высокую частотную эффективность, она является устойчивой по отношению к частотно-избирательному замиранию и замиранию вследствие многолучевого распространения, может уменьшить межсимвольные помехи (ISI) с использованием защитного интервала, обеспечить простую конструкцию аппаратного обеспечения компенсатора и является устойчивой по отношению к импульсным помехам. Поэтому схема OFDM теперь широко применяется к системе связи.

В системе связи OFDMA передатчик терминала выполняет IDFT на M-ичных символах, вставляет CP с соответствующей длиной в обработанные с помощью IFDT символы и доставляет символы с вставленным CP в свой радиочастотный (RF) каскад. Вообще, передатчик использует IFFT, чтобы эффективно выполнить IDFT. Приемник удаляет CP из принятого сигнала и выполняет FFT над сигналом с удаленным CP, чтобы компенсировать эффект от IFFT, полученный во время передачи.

В коммерческой системе обычно вместо алгоритма с плавающей точкой реализуется алгоритм с фиксированной точкой для уменьшения затрат на производство. Даже в IFFT- или FFT-процессе система обычно выполняет IFFT или FFT с использованием алгоритма с фиксированной точкой. Алгоритм с фиксированной точкой характеризует сигнал конкретным числом битов данных. В процессе выполнения квантования с использованием алгоритма с фиксированной точкой сигнал выражается некоторым числом битов после удаления значений, следующих за конкретным разрядом после десятичной запятой, вызывая ошибку квантования.

В общем случае, когда ошибка квантования относительно ниже, чем аддитивный шум, допустимый в системе, число битов данных определяется согласно отношению сигнал - шум квантования (SQNR), требуемому системой, так как полная эффективность алгоритма в меньшей степени подвергается воздействию ошибки квантования. То есть действительно реализованные аппаратные средства распределяют число битов данных, принимая во внимание SQNR, требуемое в системе, реализуя таким образом все данные с фиксированной точкой. Например, система OFDMA, использующая 1024 поднесущих, использует 13 бит данных для SQNR, равного 40 дБ.

В системе OFDMA поднесущие, выделенные терминалу, подвергаются изменению, и битовая ширина данных, требуемая для поддержания постоянного SQNR, из-за изменения в выделенных поднесущих также подвергается изменению. Соответственно, имеется возрастающая потребность в системе и способе для изменения числа битов данных согласно числу поднесущих, выделеных терминалу при IFFT.

Сущность изобретения

Задачей настоящего изобретения является решение, по существу, вышеописанных и других проблем и создание устройства и способа обработки цифрового сигнала для изменяющихся числа битов данных, используемых при IFFT в передатчике терминала, согласно числу поднесущих, выделенных терминалу.

Также задачей настоящего изобретения является создание устройства и способа обработки цифрового сигнала для реализации IFFT, используемого для передатчика с уменьшенной мощностью в системе беспроводной связи OFDMA.

Согласно одному аспекту настоящего изобретения предусмотрено устройство для обработки цифрового сигнала в системе беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Устройство содержит память для хранения числа поднесущих, выделенных мобильному терминалу, и хранения коэффициента обратного дискретного преобразования Фурье (IDFT), контроллер для вывода сигнала выбора режима, указывающего режим передачи или режим приема, и блок обратного быстрого преобразования Фурье (IFFT) для умножения первого результата, полученного посредством определения битовой ширины для коэффициента IDFT согласно числу поднесущих, на второй результат, полученный определением битовой ширины для данных согласно числу поднесущих.

Согласно другому аспекту настоящего изобретения предусмотрено устройство для обработки цифрового сигнала в системе беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Устройство содержит память для хранения числа поднесущих, выделенных мобильному терминалу, и хранения коэффициента обратного дискретного преобразования Фурье (IDFT), контроллер для вывода сигнала выбора режима, указывающего режим передачи или режим приема, первый регулятор битовой ширины для определения, при приеме данных передачи, битовой ширины для данных согласно числу выделенных поднесущих, второй регулятор битовой ширины для определения битовой ширины для коэффициента IDFT согласно числу выделенных поднесущих и умножитель для выполнения вычислений умножения по данным и коэффициенту IDFT, выведенным из первого и второго регуляторов битовой ширины.

Согласно другому аспекту настоящего изобретения предусмотрен способ обработки цифрового сигнала в системе беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Способ содержит этапы проверки числа поднесущих, выделенных мобильному терминалу, определение битовой ширины для коэффициента обратного дискретного преобразования Фурье (IDFT) согласно числу выделенных поднесущих, определение битовой ширины для данных согласно числу выделенных поднесущих и выполнение вычислений умножения по коэффициенту IDFT и данным.

Краткое описание чертежей

Вышеописанные и другие аспекты, признаки и преимущества настоящего изобретения поясняются в последующем детальном описании, иллюстрируемом чертежами, на которых представлено следующее:

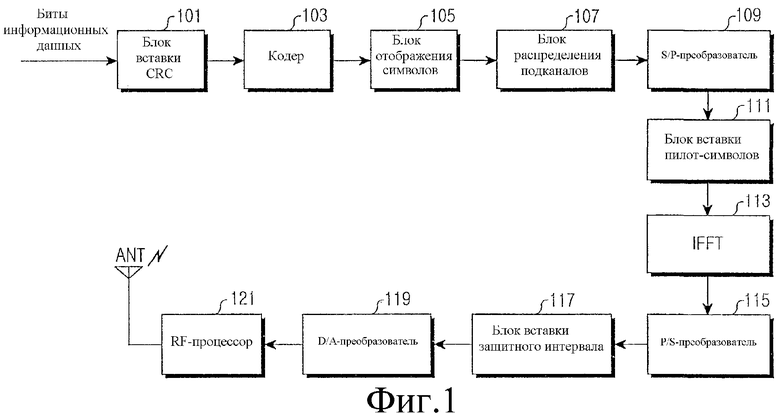

Фиг.1 - блок-схема, иллюстрирующая примерную структуру передатчика для системы OFDMA, в которой использован вариант осуществления настоящего изобретения;

Фиг.2 - схема, иллюстрирующая примерное соотношение между числом M битов и отношением сигнал - шум квантования (SQNR) при IFFT-обработке в передатчике терминала, использующего M поднесущих в общей системе OFDMA;

Фиг.3 - блок-схема, иллюстрирующая примерный блок IFFT с адаптивной битовой шириной для выполнения IFFT-обработки в зависимости от числа поднесущих, согласно варианту осуществления настоящего изобретения;

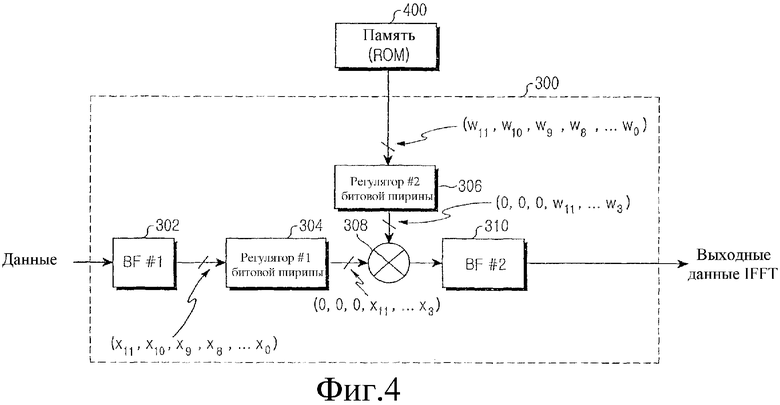

Фиг.4 - блок-схема, иллюстрирующая примерную внутреннюю структуру блока IFFT с адаптивной битовой шириной согласно варианту осуществления настоящего изобретения;

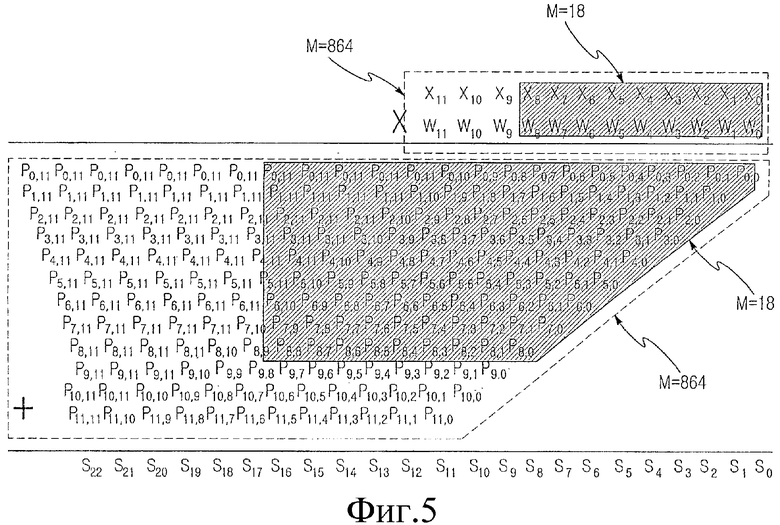

Фиг.5 - схема, иллюстрирующая ограниченное использование ресурсов, необходимых для вычисления умножения в зависимости от числа используемых битов на основе числа поднесущих в примерном блоке IFFT с адаптивной битовой шириной согласно варианту осуществления настоящего изобретения; и

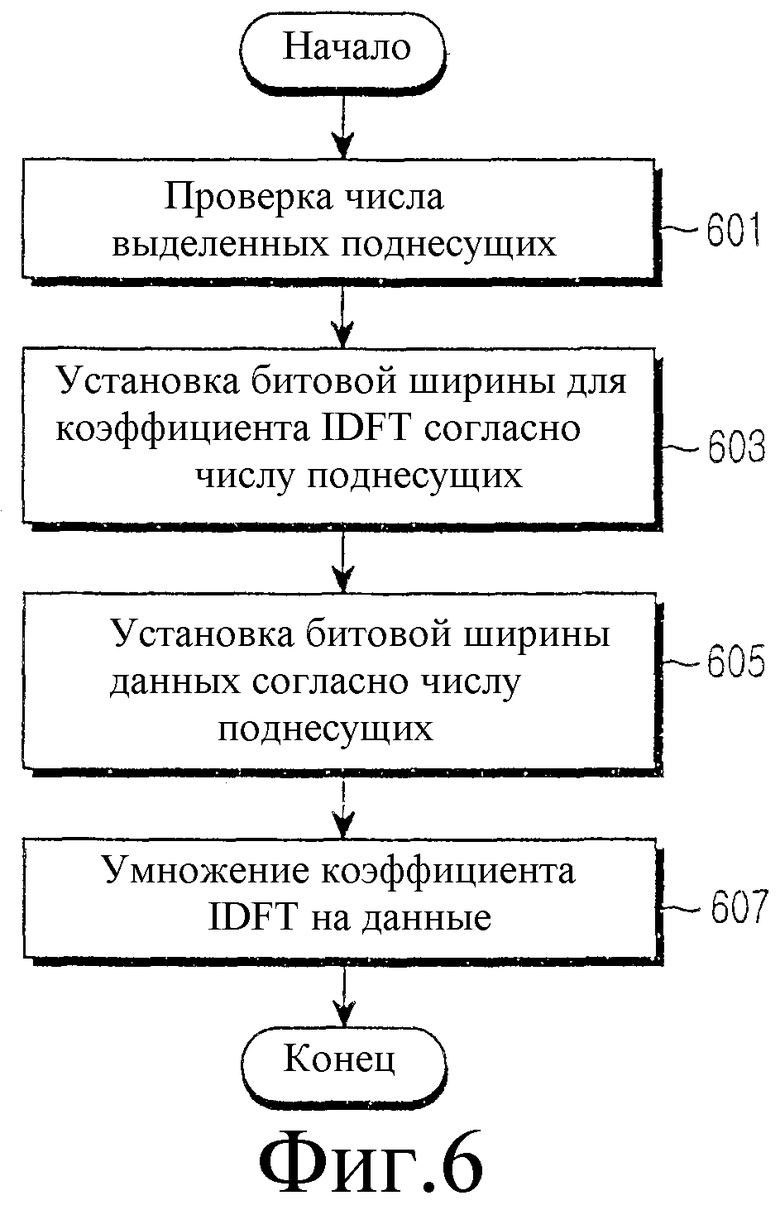

Фиг.6 - блок-схема, иллюстрирующая примерную IFFT-обработку с адаптивной битовой шириной в блоке IFFT с адаптивной битовой шириной согласно варианту осуществления настоящего изобретения.

На всех чертежах одинаковые ссылочные позиции обозначают сходные части, компоненты и структуры.

Подробное описание типичных вариантов осуществления

Ниже со ссылками на чертежи представлено детальное описание типичных вариантов осуществления настоящего изобретения. На чертежах одинаковые или сходные элементы обозначены одинаковыми ссылочными позициями, даже если они изображены на разных чертежах. В последующем описании детальное описание известных функций и конфигураций опущено в целях ясности и краткости.

Варианты осуществления настоящего изобретения позволяют передатчику терминала выполнить IFFT с использованием числа битов, требуемого для поднесущих, выделенных терминалу, путем выполнения IFFT с помощью оптимизированных вычислений.

Со ссылкой на фиг.1 ниже приведено описание варианта осуществления передатчика терминала для выполнения IFFT.

Фиг.1 является блок-схемой, иллюстрирующей структуру передатчика для системы OFDMA, к которой применяется вариант осуществления настоящего изобретения. Передатчик на фиг.1 содержит блок 101 вставки циклического избыточного кода (CRC), кодер 103, блок 105 отображения символов, блок 107 распределения подканалов, преобразователь 109 последовательного кода в параллельный (S/P), блок 111 вставки пилот-символов, блок 113 IFFT, преобразователь 115 параллельного кода в последовательный (P/S), блок 117 вставки защитного интервала, цифроаналоговый (D/A) преобразователь 119 и радиочастотный (RF) процессор 121.

Согласно фиг.1, биты пользовательских данных или биты управляющих данных (далее упоминаемые как "биты информационных данных"), которые должны передаваться, вводятся в блок 101 вставки CRC. Блок 101 вставки CRC вставляет биты CRC в биты входных информационных данных и выводит биты информационных данных с добавленным CRC в кодер 103. Кодер 103 кодирует выходной сигнал блока 101 вставки CRC с использованием предварительно определенной схемы кодирования и выводит кодированный сигнал в блок 105 отображения символов. Здесь, схема кодирования может представлять собой схему турбокодирования или схему традиционного кодирования с предварительно определенной скоростью кодирования.

Блок 105 отображения символов модулирует кодированные биты, выведенные из кодера 103 для получения символов модуляции с использованием предварительно определенной схемы модуляции, и выводит символы модуляции в блок 107 распределения подканалов. Здесь схема модуляции может представлять собой, в частности, квадратурную фазовую манипуляцию (QPSK) или 16-ную квадратурную амплитудную модуляцию (16QAM), которые хорошо известны специалистам в данной области техники. Блок 107 распределения подканалов выделяет подканалы символам модуляции, выведенным из блока 105 отображения символов, и выводит распределенные по подканалам символы модуляции в S/P-преобразователь 109.

S/P-преобразователь 109 преобразует символы последовательной модуляции, которым выделены подканалы и поддиапазоны, выведенные из блока 107 распределения подканалов, в символы параллельной модуляции и выводит символы параллельной модуляции в блок 111 вставки пилот-символов. Здесь S/P-преобразователь 109 преобразует символы последовательной модуляции в символы параллельной модуляции для обеспечения выполнения IFFT блоком 113 IFFT. Блок 111 вставки пилот-символов вставляет пилот-символы в символы параллельной модуляции, выведенные из S/P-преобразователя 109, и выводит символы модуляции со вставленным пилот-символом в блок 113 IFFT.

Блок 113 IFFT выполняет N-точечное IFFT над выходным сигналом блока 111 вставки пилот-символов и выводит обработанный посредством IFFT сигнал в P/S-преобразователь 115. Здесь процедура в блоке 113 IFFT выполняется согласно схеме IFFT с адаптивной битовой шириной, предложенной в примерном варианте осуществления настоящего изобретения, описанной ниже более детально.

P/S-преобразователь 115 преобразует выходной сигнал блока 113 IFFT в последовательный сигнал и выводит последовательный сигнал в блок 117 вставки защитного интервала. Блок 117 вставки защитного интервала вставляет предварительно определенный сигнал защитного интервала в выходной сигнал P/S-преобразователя 115 и выводит сигнал со вставленным защитным интервалом в D/A-преобразователь 119. Сигнал защитного интервала вставляется, чтобы нейтрализовать интерференцию между предыдущим OFDM-символом, переданным в предыдущий момент времени OFDM-символа, и текущим OFDM-символом, передаваемым в текущий момент OFDM-символа, в системе связи OFDMA.

D/A-преобразователь 119 преобразует выходной сигнал блока 117 вставки защитного интервала в аналоговый сигнал и выводит аналоговый сигнал в RF-процессор 121. RF-процессор 121, содержащий фильтр и входной блок, выполняет RF-обработку выходного сигнала D/A-преобразователя 119 для обеспечения возможности радиопередачи и передает RF-сигнал через передающую антенну ANT.

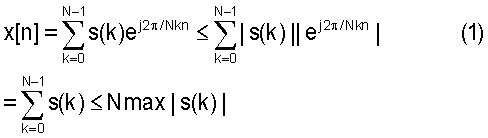

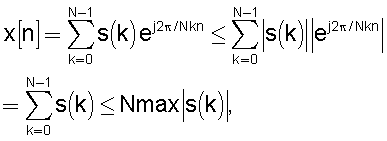

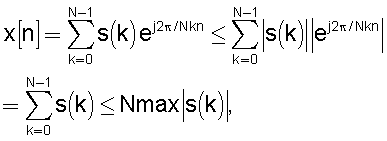

Если, например, число поднесущих, выделенных терминалу в системе OFDMA, равно N, то IDFT сигнал x[n] входного сигнала s(k), подаваемого в блок 113 IFFT, определяется Уравнением (1) ниже.

Здесь следует отметить, что сигнал x[n] получается сложением N элементов s(k)e(...), так как индексы, указывающие сумму, включают в себя от 0 до N-1, что вызывает заметные вариации уровня сигнала. В общем случае увеличение вариаций уровня сигнала требует увеличения числа битов данных, чтобы удовлетворить отношению сигнал - шум квантования (SQNR).

Например, числа, которые могут выражаться с помощью 2 битов, включают в себя 1 (01), -1 (11) и 0 (10 или 00), максимальное абсолютное значение которых равно 1. В случае 3 битов диапазон чисел, которые могут быть выражены с помощью 3 битов, увеличивается от -2 до 2. В этом случае, так как ошибка квантования пропорциональна числу N поднесущих в терминах диапазона уровня сигнала, увеличение в числе N поднесущих требует большого увеличения в числе битов данных для удовлетворения предварительно определенному SQNR.

Однако OFDMA терминалу выделяется несколько из, например, M поднесущих в качестве восходящей линии связи. Следовательно, битовая ширина (или ширина данных) для терминала, использующего M поднесущих, представляется уравнением (2) ниже.

|x[n]|<Mmax[s(k)] (2)

Когда M < N, можно удовлетворить SQNR, требуемое системой даже с меньшим числом битов по сравнению с числом битов, используемых для IFFT-обработки в обычном блоке N-точечного IFFT.

Со ссылкой на фиг.2 ниже приведено описание числа битов данных, требуемых согласно числу M поднесущих, выделенных терминалу, при IFFT-обработке в приведенном для примера передатчике терминала. Фиг.2 иллюстрирует соотношение между числом M битов и SQNR приема IFFT-обработки в передатчике терминала, использующего M поднесущих в обычной системе OFDMA. Конкретно, фиг.2 является графиком, иллюстрирующим результаты моделирования.

Согласно фиг.2, число M поднесущих, выделенных терминалу, включает в себя 32, 256 и 1024. Предполагая, например, что SQNR, требуемое системой, равно 40дБ, может быть отмечено, что битовая ширина, требуемая при IFFT-обработке, равна 10 битов для M=32, 12 битов для M=256 и 13 битов для M=1024. Следовательно, по сравнению с M=1024, M=32 использует на три бита меньше для поддержания того же SQNR.

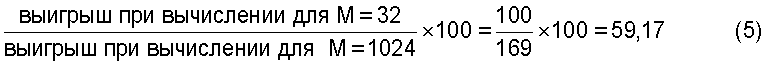

Как правило, вычисления в операции умножения при IFFT-обработке пропорциональны числу используемых битов. Следовательно, когда блок IFFT-передатчика терминала реализован на основе SQNR=40дБ на фиг.2, выигрыш при вычислении, полученный для M=32, может быть найден посредством уравнения (3), а выигрыш при вычислении, полученный для M=1024, может быть определен уравнением (4), приведенным ниже.

Следовательно, выигрыш при вычислении для M=32 равен 59% от выигрыша при вычислении для M=1024. Это может быть выражено следующим образом.

Из уравнения (5) очевидно, что M=32 по сравнению с M=1024 обеспечивает снижение объема вычислений. Следовательно, меньшее число поднесущих требует меньшего числа битов, содействуя уменьшению объема вычислений. Следовательно, варианты осуществления настоящего изобретения используют число битов, требуемых для числа поднесущих, выделенных терминалу, при IFFT-обработке в передатчике терминала, таким образом, используя блок IFFT с оптимальными вычислениями.

В стандарте TTA WiBro для базового блока передачи используется минимальное число поднесущих M=18 в одном OFDM-символе и максимальное число поднесущих M=864. Разница в числе битов между двумя случаями равна 2,5 битов, используемых в блоке IFFT для получения одинакового SQNR. Если, например, 12 битов используются для M=864, 9 битов используются для M=18, обеспечивается одинаковая ошибка квантования. Кроме того, по сравнению с использованием 12 битов для M=864, использование 9 битов для M=18 на 56% уменьшает объем вычислений.

Таким образом, варианты осуществления настоящего изобретения уменьшают объем вычислений с использованием меньшего числа бит данных посредством изменения числа битов данных, используемых согласно числу поднесущих, выделенных терминалу, при IFFT-обработке в передатчике терминала, делая возможным осуществления IFFT при меньшей мощности.

Так как число M поднесущих, выделенных передатчику терминала, является информацией, предварительно определенной согласно протоколу между терминалом и базовой станцией, способ реализации блока IFFT с адаптивной битовой шириной, использующий эту информацию, описан ниже со ссылкой на фиг.3.

Со ссылкой на фиг.3 ниже описан примерный блок 300 IFFT с адаптивной битовой шириной, который выполняет IFFT-обработку с использованием числа битов данных, требуемых согласно числу M поднесущих, выделенных передатчику терминала. Фиг.3 иллюстрирует блок IFFT с адаптивной битовой шириной для выполнения IFFT-обработки с использованием оптимальной битовой ширины в зависимости от числа поднесущих согласно варианту осуществления настоящего изобретения.

Входные данные блока 300 IFFT с адаптивной битовой шириной содержат данные передачи, число поднесущих и сигнал выбора режима. Сигнал выбора режима, который может быть управляющим сигналом, выведенным из контроллера 310, указывает, является ли текущий режим терминала режимом или режимом приема. Если принимается число выделенных поднесущих, то блок 300 IFFT определяет битовую ширину, которая должна использоваться для IFFT, с использованием этого числа поднесущих и затем выполняет соответствующие вычисления с определенной битовой шириной. Блок 300 IFFT с адаптивной битовой шириной выполняет IDFT и DFT для передачи. Когда входной сигнал выбора режима указывает режим приема, он использует максимальную битовую ширину, поскольку все поднесущие имеют данные своего собственного терминала или других терминалов. Однако, когда сигнал выбора режима, принятый от контроллера 310, указывает режим передачи, блок 300 IFFT с адаптивной битовой шириной определяет битовую ширину на основе числа выделенных поднесущих и устанавливает все остальные биты, кроме битов, которые должны быть использованы, в '0'. Блок 300 IFFT с адаптивной битовой шириной, как описано выше, регулирует битовую ширину согласно числу поднесущих.

Внутренняя структура блока 300 IFFT с адаптивной битовой шириной, показанная на фиг.3, описана ниже более детально со ссылкой на фиг.4. Фиг.4 иллюстрирует примерную внутреннюю структуру блока 300 IFFT с адаптивной битовой шириной согласно варианту осуществления настоящего изобретения. Блок IFFT с адаптивной битовой шириной, представленный на фиг.4, реализован согласно стандарту TTA WiBro в качестве примера. Блок 300 IFFT с адаптивной битовой шириной содержит первый и второй полосовые фильтры 302 и 310, первый и второй регуляторы 304 и 306 битовой ширины и комплексный умножитель 308.

Для того чтобы использовать оптимальную битовую ширину при IFFT-обработке, блок 300 IFFT с адаптивной битовой шириной управляет битовой шириной, то есть числом битов, вводимых в комплексный умножитель 308, согласно числу поднесущих, выделенных терминалу. Блок 300 IFFT с адаптивной битовой шириной предназначен, чтобы поддерживать максимальную битовую ширину, и {exp}-значения, выраженные с помощью битовой ширины для получения предварительно определенного SQNR, требуемого системой, сохраняются в нем как табличные значения. Табличные значения хранятся в памяти или постоянном запоминающем устройстве (ROM) 400. Память 400 хранит данные с 13 битами, основанными на максимальном M=1024, и при предоставлении 13-битных данных вычислительному устройству, ввиду изменения в M, число битов уменьшается. Например, для M=32 блок 300 IFFT с адаптивной битовой шириной смещает на 3 бита вправо 13-битные данные, сохраненные в памяти 400, чтобы удалить 3 наименее значимых бита (LSB), имеющих низший приоритет (или значимость), создавая 10-битные данные, перед выполнением вычисления над ними.

Если данные передачи вводятся в первый регулятор 304 битовой ширины через первый полосовой фильтр (BF) 302, первый регулятор 304 битовой ширины регулирует битовую ширину согласно числу выделенных поднесущих и обеспечивает на выходе установленную битовую ширину. Первый регулятор 304 битовой ширины определяет битовую ширину согласно числу поднесущих, выделенных контроллером терминала, и выводит управляющий сигнал для регулировки битовой ширины до определенной битовой ширины на комплексный умножитель 308, таким образом регулируя соответствующую битовую ширину. То есть первый регулятор 304 битовой ширины просто удаляет число битов с низким приоритетом, и число битов, которые должны быть удалены, сообщается первому регулятору 304 битовой ширины контроллером терминала.

Если, например, коэффициент IFFT вводится из памяти 400 во второй регулятор 306 битовой ширины, то второй регулятор 306 битовой ширины устанавливает битовую ширину согласно числу выделенных поднесущих и обеспечивает на выходе установленную битовую ширину. То есть регуляторы 304 и 306 битовой ширины уменьшают свои входные данные до оптимальной битовой ширины, полученной на основе числа M используемых поднесущих, и заполняют верхние биты нулями.

Если данные и коэффициент IDFT, выведенные из регуляторов 304 и 306 битовой ширины, вводятся в комплексный умножитель 308, то комплексный умножитель 308 выполняет вычисления умножения над входными данными и выводит результат умножения через второй полосовой фильтр (BF) 310.

Если число поднесущих изменяется с M=864 на M=18, регуляторы 304 и 306 битовой ширины устанавливают свои значения битовой ширины согласно числу поднесущих и выводят установленные значения битовой ширины на комплексный умножитель 308. Поэтому блок 300 IFFT с адаптивной битовой шириной изменяет входные данные, подаваемые на комплексный умножитель 308 согласно числу поднесущих. При описании реализации отдельных умножителей в комплексном умножителе 308 можно оптимизировать величину используемой мощности согласно выделенному числу поднесущих M, если использование ресурсов сумматора ограничено, путем использования канала прямой связи для неиспользованной части старших битов и младшей части сложения на основе выходного бита MSB.

Можно отметить, что ресурсы сумматора, требуемые в зависимости от числа поднесущих M при IFFT-обработке с адаптивной битовой шириной, согласно варианту осуществления настоящего изобретения уменьшаются пропорционально к площади битовой ширины, как показано на фиг.5. Фиг.5 иллюстрирует ограниченное использование ресурсов, необходимых для вычисления умножения в зависимости от числа используемых битов, на основе числа поднесущих в блоке IFFT с адаптивной битовой шириной согласно варианту осуществления настоящего изобретения.

Для M=864 комплексный умножитель 308 выполняет вычисления умножения над битами W11, W10, W9, W8, W7, W6, W5, W4, W3, W2, W1, W0, принятыми от второго регулятора 306 битовой ширины, и битами X11, X10, X9, X8, X7, X6, X5, X4, X3, X2, X1, X0 данных, принятыми от первого регулятора 304 битовой ширины.

Однако для M=18 комплексный умножитель 308 выполняет вычисления умножения над битами 0, 0, 0, W11, W10, W9, W8, W7, W6, W5, W4, W3, принятыми от второго регулятора 306 битовой ширины, и битами 0, 0, 0, X11, X10, X9, X8, X7, X6, X5, X4, X3 данных, принятыми от первого регулятора 304 битовой ширины.

Следовательно, для M=18 комплексный умножитель 308 использует только заштрихованные части в качестве своих входных или выходных данных. В результате, по сравнению с M=864, вариант при M=18 характеризуется меньшим объемом вычислений, что способствует уменьшению потребляемой мощности при IFFT-обработке.

Фиг.6 иллюстрирует примерную IFFT-обработку с адаптивной битовой шириной в блоке IFFT с адаптивной битовой шириной согласно варианту осуществления настоящего изобретения.

На этапе 601 блок 300 IFFT с адаптивной битовой шириной проверяет число выделенных поднесущих.

Второй регулятор 306 битовой ширины в блоке 300 IFFT с адаптивной битовой шириной устанавливает на этапе 603 битовую ширину для коэффициента IDFT согласно числу поднесущих, а первый регулятор 304 битовой ширины устанавливает на этапе 605 битовую ширину для данных согласно числу поднесущих. Следует отметить, что порядок этапов 603 и 605 может изменяться.

На этапе 607 комплексный умножитель 308 выполняет вычисления умножения над коэффициентом IDFT и данными и выводит результаты умножения через второй полосовой фильтр 310.

Как следует из предыдущего описания, варианты осуществления настоящего изобретения позволяют системе OFDMA реализовать блок IFFT с переменной битовой шириной согласно числу поднесущих, выделенных терминалу. Данная реализация блока IFFT с переменной битовой шириной позволяет реализовать блок IFFT низкой мощности для использования в OFDMA-передатчике.

Хотя варианты осуществления настоящего изобретения были показаны и описаны со ссылкой на определенные примерные варианты его осуществления, специалистам в данной области техники должно быть понятно, что различные изменения по форме и в деталях могут быть сделаны без отступления от сущности и объема изобретения, как определено прилагаемой формулой изобретения. Например, хотя варианты осуществления настоящего изобретения описаны со ссылкой на вариант осуществления, в котором блок IFFT в передатчике терминала оптимально устанавливает битовую ширину согласно числу выделенных поднесущих перед выполнением IFFT-обработки, настоящее изобретение может также применяться к альтернативным вариантам осуществления, в которых блок FFT в приемнике терминала оптимально устанавливает битовую ширину согласно числу выделенных поднесущих перед выполнением FFT-обработки.

Изобретение относится к устройству и способу обработки цифрового сигнала в мобильном терминале системы беспроводной связи с множественным доступом с ортогональным частотным разделением каналов (OFDMA). Достигаемый технический результат - осуществление обработки при меньшей мощности. В устройстве обработки память хранит число поднесущих, выделенных мобильному терминалу, и коэффициент обратного дискретного преобразования Фурье (IDFT). Блок обратного быстрого преобразования Фурье (IFFT) определяет каждое из числа битов для коэффициента IDFT и числа битов для данных согласно числу поднесущих. Блок IFFT выполняет вычисления умножения над коэффициентом IDFT и данными. Контроллер выводит в блок IFFT сигнал выбора режима, указывающий режим передачи или режим приема. 3 н. и 15 з.п. ф-лы, 6 ил.

память для хранения числа выделенных поднесущих и хранения коэффициента обратного дискретного преобразования Фурье (IDFT);

блок обратного быстрого преобразования Фурье (IFFT) для определения каждого из числа битов для коэффициента IDFT и числа битов для данных согласно числу поднесущих и выполнения вычислений умножения над коэффициентом IDFT и упомянутыми данными; и

контроллер для вывода в блок IFFT сигнала выбора режима, указывающего режим передачи или режим приема.

где х[n] обозначает коэффициент IDFT, N обозначает число выделенных поднесущих, a s(k) обозначает входной сигнал блока IFFT.

первый регулятор битовой ширины для определения числа битов для данных согласно числу выделенных поднесущих;

второй регулятор битовой ширины для определения числа битов для коэффициента IDFT согласно числу выделенных поднесущих; и

умножитель для выполнения вычислений умножения над данными и коэффициентом IDFT, выведенными из первого и второго регуляторов битовой ширины.

память для хранения числа выделенных поднесущих и хранения коэффициента обратного дискретного преобразования Фурье (IDFT);

первый регулятор битовой ширины для определения числа битов для данных согласно числу выделенных поднесущих;

второй регулятор битовой ширины для определения числа битов для коэффициента IDFT согласно числу выделенных поднесущих;

умножитель для выполнения вычислений умножения над данными и коэффициентом IDFT, выведенными из первого и второго регуляторов битовой ширины; и

контроллер для вывода в первый регулятор битовой ширины и второй регулятор битовой ширины сигнала выбора режима, указывающего режим передачи или режим приема.

где х[n] обозначает коэффициент IDFT, N обозначает число выделенных поднесущих, и s(k) обозначает входной сигнал блока обратного быстрого преобразования Фурье (IFFT).

проверяют число выделенных поднесущих;

определяют число битов для коэффициента обратного дискретного преобразования Фурье (IDFT) согласно числу выделенных поднесущих;

определяют число битов для данных согласно числу выделенных поднесущих; и

выполняют вычисления умножения над коэффициентом IDFT и данными.

где х[n] обозначает коэффициент IDFT, N обозначает число выделенных поднесущих, a s(k) обозначает входной сигнал блока обратного быстрого преобразования Фурье (IFFT).

| US 5854758 А, 29.12.1998 | |||

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОЙ ПЕРЕДАЧИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НЕСКОЛЬКИХ СКОРОСТЕЙ | 1996 |

|

RU2142199C1 |

| СПОСОБ ДВОИЧНОГО КОДИРОВАНИЯ ПЕРЕДАВАЕМОГО СИГНАЛА | 1992 |

|

RU2108666C1 |

| СПОСОБ ПЕРЕДАЧИ МОДУЛИРОВАННЫХ ВОЛН, ПЕРЕДАЮЩЕЕ УСТРОЙСТВО И ПРИЕМНОЕ УСТРОЙСТВО | 1989 |

|

RU2101870C1 |

Авторы

Даты

2009-03-10—Публикация

2005-11-16—Подача