Изобретение относится к вычислительной и измерительной технике, а также может быть использовано в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Известен аналого-цифровой преобразователь последовательного счета, содержащий счетчик, цифро-аналоговый преобразователь (ЦАП), компаратор, схему управления, генератор тактовых импульсов (ГТИ) [1].

Недостатком этого устройства является переменное время преобразования и наибольшее количество тактов преобразования - 2n для n-разрядного АЦП.

Наиболее близким по технической сущности является аналого-цифровой преобразователь последовательного приближения, содержащий регистр последовательного приближения, цифро-аналоговый преобразователь, компаратор, схему управления и генератор тактовых импульсов [2].

Недостатком прототипа является требование n тактов преобразования для n разрядного ЛЦП. При этом в некоторых случаях выходной код формируется менее чем за n тактов полного цикла преобразования. В этих случаях можно уменьшить количество тактов в цикле преобразования.

Задача изобретения - уменьшение среднего количества тактов в цикле преобразования.

Это достигается тем, что аналого-цифровой преобразователь содержит регистр последовательных приближений (РПП), цифровые выходы которого соединены с соответствующими выходами "результирующий код" устройства, цифро-аналоговый преобразователь (ЦАП), первый компаратор, первый вход которого соединен с входом преобразуемого напряжения Uвх устройства, а выход подключен к информационному входу РПП, схему управления, первый логический вход которой соединен с входом сигнала "Пуск" устройства, а выход подключен к управляющему входу РПП, генератор тактовых импульсов, выход которого подключен к тактовому входу РПП, причем ЦАП содержит источник опорного напряжения (отрицательное напряжение), n масштабных резисторов (21R,…,2nR), первые выводы которых подключены к источнику опорного напряжения, а вторые выводы масштабных резисторов через соответствующие ключи (k1…kn) подключены к инвертирующему входу первого операционного усилителя ОУ1, неинвертирующий вход которого соединен с шиной нулевого потенциала устройства, а выход подключен ко второму входу первого компаратора и через первый резистор R к инвертирующему входу первого операционного усилителя ОУ1, при этом управляющие входы ключей (k1…kn) подключены к соответствующим цифровым выходам РПП, (n+1)-й масштабный резистор (2n+1R), который вместе с ЦАП образуют блок суммирования, первый вывод (n+1)-го масштабного резистора (2n+1R) подключен к источнику опорного напряжения, а второй вывод подключен к инвертирующему входу первого операционного усилителя ОУ1, блок вычитания, включающий второй операционный ОУ2 и третий дифференциальный ОУ3 усилители, второй, третий, четвертый, пятый, шестой резисторы (R) и резистор (2n+1-1)R, причем неинвертирующий вход второго операционного усилителя ОУ2 соединен с шиной нулевого потенциала устройства, инвертирующий вход второго операционного усилителя ОУ2 через второй резистор (R) подключен к выходу первого операционного усилителя ОУ1 и через третий резистор (R) к выходу второго операционного усилителя ОУ2, выход второго операционного усилителя ОУ2 через четвертый резистор (R) подключен к инвертирующему входу третьего дифференциального усилителя ОУ3, неинвертирующий вход которого через резистор (2n+1-1)R подключен к источнику опорного напряжения, а через пятый резистор (R) к шине нулевого потенциала устройства, инвертирующий вход третьего дифференциального усилителя ОУ3 через шестой резистор (R) подключен к выходу третьего дифференциального усилителя ОУ3, выход третьего дифференциального усилителя ОУ3 подключен ко второму входу второго компаратора, первый вход которого соединен с входом преобразуемого напряжения Uвх устройства, а выход подключен к первому логическому входу элемента "исключающее ИЛИ-НЕ", второй вход которого подключен к выходу первого компаратора, а выход элемента "исключающее ИЛИ-НЕ" подключен ко входу генератора тактовых импульсов ГТИ.

Предлагаемый преобразователь имеет существенное отличие от прототипа. Существенным отличием является то, что в заявляемое устройство дополнительно введены блоки: (n+1)-й масштабный резистор, блок вычитания, второй компаратор и элемент "исключающее ИЛИ-НЕ". Существенное отличие заявляемого устройства позволяет достичь эффекта, заключающегося в уменьшении среднего количества тактов преобразования. В данном предлагаемом устройстве среднее количество тактов преобразования уменьшается за счет того, что цикл преобразования прекращается раньше в тот момент, когда входное напряжение находится между выходными напряжениями блока суммирования и вычитания. Уменьшение среднего относительного количества тактов преобразования зависит от разрядности АЦП. Например, для 4-разрядного АЦП относительное количество тактов сокращения составляет 0.7, а для 16 разрядного АЦП составляет 0.9997. Предлагаемое устройство позволяет сократить количество тактов преобразования, и при увеличении количества разрядов количество сокращаемых тактов увеличивается и приближается к единице. Сокращение количества тактов преобразования, которое обеспечивается в предлагаемом устройстве, приводит к улучшению такой важной характеристики АЦП, как время преобразования. Например, для 4-разрядного АЦП среднее относительное время преобразования уменьшается на 17.5%, а для 16 разрядного АЦП позволяет уменьшить на 6.25%. Таким образом, предлагаемое устройство позволяет обеспечить существенный эффект, заключающийся в сокращении среднего времени преобразования.

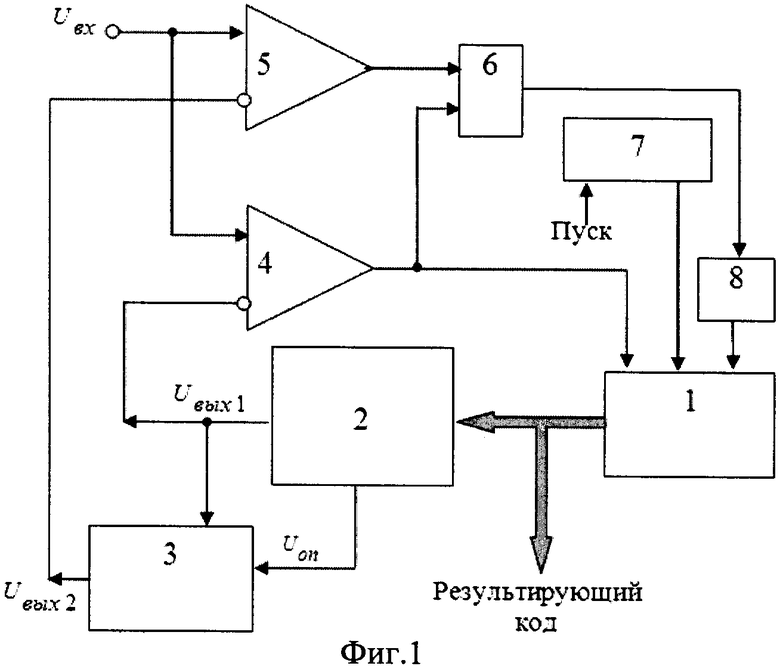

На фиг. 1 представлена структурная схема АЦП, где: 1 - регистр последовательных приближений (РПП), 2 - блок суммирования, 3 - блок вычитания, 4, 5 - компараторы, 6 - элемент "исключающее" ИЛИ-НЕ, 7 - схема управления, 8 - генератор тактовых импульсов (ГТИ).

На фиг.2 представлен блок суммирования, включающий 14 - (n+1)-й масштабный резистор (2n+1R) и цифро-аналоговый преобразователь (ЦАП), где: 9 - источник опорного напряжения (отрицательное напряжение), 10 - операционный усилитель ОУ1, 11 - n масштабных резисторов (21R,…,2nR), 12 - коммутатор, имеющий n ключей (k1…kn), 13 - резистор (R).

На фиг.3 представлен блок вычитания, где: 15 - второй операционный усилитель

ОУ2, 16 - третий операционный усилитель ОУ3, 17-21 - второй, третий, четвертый, пятый и шестой резисторы (R), 22 - резистор (2n+1-1)R.

Преобразователь содержит РПП 1, блок суммирования 2, блок вычитания 3, первый и второй компараторы 4, 5, элемент "исключающее" ИЛИ-НЕ 6, схему управления 7, генератор тактовых импульсов (ГТИ) 8. Причем блок суммирования 2, включающий цифро-аналоговый преобразователь (ЦАП), который содержит источник опорного напряжения (отрицательное напряжение) 9, n масштабных резисторов 11 (21R…2nR), первые выводы которых подключены к источнику 9 опорного напряжения, а вторые выводы масштабных резисторов 11 через соответствующие n ключей {k1…kn) коммутатора 12 подключены к инвертирующему входу первого операционного усилителя 10 ОУ1, (n+1)-й масштабный резистор 14 (2n+1R), первый вывод (n+1)-го масштабного резистора (2n+1R) подключен к источнику 9 опорного напряжения, а второй вывод подключен к инвертирующему входу первого операционного усилителя ОУ1, неинвертирующий вход которого соединен с шиной нулевого потенциала устройства, а выход подключен через первый резистор (R) 13 к инвертирующему входу первого операционного усилителя ОУ1, при этом управляющие входы ключей (k1…kn) подключены к соответствующим цифровым выходам РПП 1, выход блока суммирования 2 подключен ко второму входу первого компаратора 4, первый вход первого компаратора 4 соединен с входом преобразуемого напряжения Uвх устройства, а выход подключен к информационному входу РПП 1, блок вычитания 3, включающий второй 15 операционный ОУ2 и третий 16 дифференциальный ОУ3 усилители, второй 17, третий 18, четвертый 19, пятый 21, шестой 20 резисторы (R) и резистор (2n+1-1)R 22, причем неинвертирующий вход второго операционного усилителя 15 ОУ2 соединен с шиной нулевого потенциала устройства, инвертирующий вход второго операционного усилителя 15 ОУ2 через второй резистор (R) 17 подключен к выходу первого операционного усилителя 10 ОУ1 и через третий резистор (R) 18 к выходу второго операционного усилителя 15 ОУ2, выход второго операционного усилителя 15 ОУ2 через четвертый резистор (R) 19 подключен к инвертирующему входу третьего дифференциального усилителя 16 ОУ3, неинвертирующий вход которого через резистор (2n+1-1)R 22 подключен к источнику 9 опорного напряжения, а через пятый резистор (R) 21 к шине нулевого потенциала устройства, инвертирующий вход третьего дифференциального усилителя 16 ОУ3 через шестой резистор (R) 20 подключен к выходу третьего дифференциального усилителя 16 ОУ3, выход третьего дифференциального усилителя 16 ОУ3 подключен ко второму входу второго компаратора 5, первый вход которого соединен с входом преобразуемого напряжения Uвх устройства, а выход подключен к первому логическому входу элемента 6 "исключающее ИЛИ-НЕ", второй логический вход которого подключен к выходу первого компаратора 4, а выход элемента 6 "исключающее ИЛИ-НЕ" подключен ко входу генератора тактовых импульсов ГТИ, первый логический вход схемы управления 7 соединен с входом сигнала "Пуск" устройства, а выход схемы управления 7 подключен к управляющему входу РПП 1, при этом выход ГТИ 8 подключен к тактовому входу РПП1.

Устройство работает следующим образом.

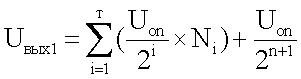

На первом этапе на схему управления 7 поступает внешний сигнал "Пуск"; одновременно на вход генератора тактовых импульсов 8 с элемента 6 "исключающее ИЛИ-НЕ" поступает сигнал, разрешающий прохождение тактовых импульсов, так как на выходе Uвых1 блока суммирования 2 присутствует нулевое напряжение и на выходах блоках компараторов 4, 5 присутствуют одинаковые логические сигналы; при этом со схемы управления 7 на управляющий вход РПП 1 поступает сигнал, разрешающий подбор кода. В результате в старшем разряде выходного кода РПП 1 устанавливается "1", код с РПП 1 подается на ЦАП. Тогда на каждом шаге (такте) напряжение на выходе блока суммирования 2 будет

,

,

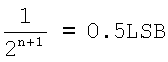

где  ,

,

Ni - бит управления операцией суммирования.

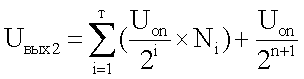

Напряжение на выходе блока вычитания 3

.

.

Напряжение Uвых1 с выхода блока суммирования 2 и напряжение Uвых2 с выхода блока вычитания 3 сравниваются с входным аналоговым сигналом Uвх соответственно с помощью компараторов 4, 5. Если напряжения на выходах блоков суммирования и вычитания оба меньше или оба больше входного напряжения Uвх, то производится следующий шаг. Если Uвых1>Uвх на входах первого компаратора 4 и Uвых2≤Uвх на входах второго компаратора 5, то на выходах компараторов 4, 5 присутствуют разноименные логические сигналы; при этом с элемента 6 "исключающее ИЛИ-НЕ" на вход генератора тактовых импульсов 8 поступает сигнал, запрещающий прохождение тактовых импульсов, и преобразование прекращается. Управление продолжением подбора кода осуществляется элементом 6 "исключающее ИЛИ-НЕ", на который поступают выходные сигналы компараторов. В результате получается двоичный код на выходе РПП 1.

Цикл преобразования содержит уменьшенное количество тактов на некоторых значениях входного (преобразуемого) напряжения.

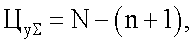

Среднее количество тактов, на которое уменьшаются циклы преобразования, оценивается

где N=2n - количество дискретов напряжения;

Цу∑ - суммарное количество тактов, на которое уменьшаются циклы преобразования для всех возможных значений входного напряжения.

При этом

где τ - количество разрядов.

Пример конкретного выполнения: Для 8 разрядов Цу∑=247, а для 16 разрядов Цу∑=65519. Тогда среднее количество тактов, на которое уменьшаются циклы преобразования, можно оценить по формуле (1). Отсюда для 16 разрядов ЦуСр=0,999≈1.

Таким образом, в предлагаемом АЦП цикл преобразования содержит, в среднем, меньшее количество тактов преобразования по сравнению с прототипом.

Источники информации

1. Аналоговые и цифровые интегральные микросхемы. С.В.Якубовский, - 2-е изд., перераб. и доп. - М.: Радио и связь, 1985. с 357-358, рис.6.85.

2. Волович Г.И. Схемотехника аналоговых и аналого-цифровых электронных устройств. - М.: Издательский дом « Додэка-XXI », 2005. с 444-446, рис.9.11 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2549114C2 |

| УНИВЕРСАЛЬНЫЙ МОДУЛЬ ЧАСТОТНОГО ИНТЕГРИРУЮЩЕГО РАЗВЁРТЫВАЮЩЕГО ПРЕОБРАЗОВАТЕЛЯ ДЛЯ ДАТЧИКОВ ФИЗИЧЕСКИХ ВЕЛИЧИН | 2016 |

|

RU2631494C1 |

| Многоканальный источник тока для задания рабочих режимов в двухкубитных и многокубитных системах | 2021 |

|

RU2763014C1 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

| ПРОГРАММИРУЕМЫЙ ARC-ФИЛЬТР | 1990 |

|

RU2040853C1 |

| УПРАВЛЯЕМЫЙ ИСТОЧНИК ТОКА ДЛЯ ЗАЗЕМЛЕННОЙ НАГРУЗКИ | 2014 |

|

RU2549252C1 |

| УСТРОЙСТВО АВТОКОРРЕКЦИИ НУЛЯ ОПЕРАЦИОННОГО УСИЛИТЕЛЯ В КОНТУРЕ УПРАВЛЕНИЯ ОБОРУДОВАНИЕМ С ЧПУ | 2009 |

|

RU2397058C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ДАВЛЕНИЯ ГАЗА | 2016 |

|

RU2665753C2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Устройство сопряжения аналогового процессора с вентильным коммутатором | 1988 |

|

SU1649555A1 |

Изобретение относится к области вычислительной техники и может быть использовано для преобразования аналоговых сигналов в цифровой код. Техническим результатом изобретения является уменьшение среднего количества тактов в цикле преобразования. Этот результат достигается тем, что в устройство, состоящее из регистра последовательного приближения (РПП), блока суммирования, который содержит цифро-аналоговый преобразователь (ЦАП), компаратора, схемы управления, генератора тактовых импульсов (ГТИ) и источника опорного напряжения (отрицательное напряжение), дополнительно введены блок вычитания, второй компаратор и элемент "исключающее" ИЛИ-НЕ. 3 ил.

Аналого-цифровой преобразователь, содержащий регистр последовательных приближений (РПП), цифровые выходы которого соединены с соответствующими выходами "результирующий код" устройства, цифроаналоговый преобразователь (ЦАП), первый компаратор, первый вход которого соединен с входом преобразуемого напряжения Uвх устройства, а выход подключен к информационному входу РПП, схему управления, первый логический вход которой соединен с входом сигнала "Пуск" устройства, а выход подключен к управляющему входу РПП, генератор тактовых импульсов, выход которого подключен к тактовому входу РПП, причем ЦАП содержит источник опорного напряжения (отрицательное напряжение), n масштабных резисторов (21R,…,2nR), первые выводы которых подключены к источнику опорного напряжения, а вторые выводы масштабных резисторов через соответствующие ключи (k1…kn) подключены к инвертирующему входу первого операционного усилителя ОУ1, неинвертирующий вход которого соединен с шиной нулевого потенциала устройства, а выход подключен ко второму входу первого компаратора и, через первый резистор R, к инвертирующему входу первого операционного усилителя ОУ1, при этом управляющие входы ключей (к1…кn) подключены к соответствующим цифровым выходам РПП, отличающийся тем, что дополнительно содержит (n+1)-й масштабный резистор (2n+1R), который вместе с ЦАП образуют блок суммирования, первый вывод (n+1)-го масштабного резистора (2n+l R) подключен к источнику опорного напряжения, а второй вывод подключен к инвертирующему входу первого операционного усилителя ОУ1, блок вычитания, включающий второй операционный ОУ2 и третий дифференциальный ОУ3 усилители, второй, третий, четвертый, пятый, шестой резисторы (R) и резистор (2n+1-1)R, причем неинвертирующий вход второго операционного усилителя ОУ2 соединен с шиной нулевого потенциала устройства, инвертирующий вход второго операционного усилителя ОУ2 через второй резистор (R) подключен к выходу первого операционного усилителя ОУ1 и, через третий резистор (R), к выходу второго операционного усилителя ОУ2, выход второго операционного усилителя ОУ2 через четвертый резистор (R) подключен к инвертирующему входу третьего дифференциального усилителя ОУ3, неинвертирующий вход которого через резистор (2n+l-1)R подключен к источнику опорного напряжения, а через пятый резистор (R) к шине нулевого потенциала устройства, инвертирующий вход третьего дифференциального усилителя ОУ3 через шестой резистор (R) подключен к выходу третьего дифференциального усилителя ОУ3, выход третьего дифференциального усилителя ОУ3 подключен ко второму входу второго компаратора, первый вход которого соединен с входом преобразуемого напряжения Uвх устройства, а выход подключен к первому логическому входу элемента "исключающее ИЛИ-НЕ", второй вход которого подключен к выходу первого компаратора, а выход элемента "исключающее ИЛИ-НЕ" подключен ко входу генератора тактовых импульсов ГТИ.

| ВОЛОВИЧ Г.И | |||

| Схемотехника аналоговых и аналого-цифровых электронных устройств | |||

| - М.: Издательский дом «Додэка-XXI», 2005, с.444-446, рис.9.11 | |||

| Аналого-цифровой преобразователь | 1984 |

|

SU1244792A1 |

| US 5870052 А, 09.02.1999 | |||

| US 4989004 А, 29.01.1991. | |||

Авторы

Даты

2009-06-20—Публикация

2007-10-23—Подача