11358094

Изобретение относится к им1ульс- ной технике и может быть использовано например для построения быстродействующих и прецизионных трактов амплитудного .анализа в многоканальных спектрометрах.

Цель изобретения - повышение быстродействия и точности преобразования.

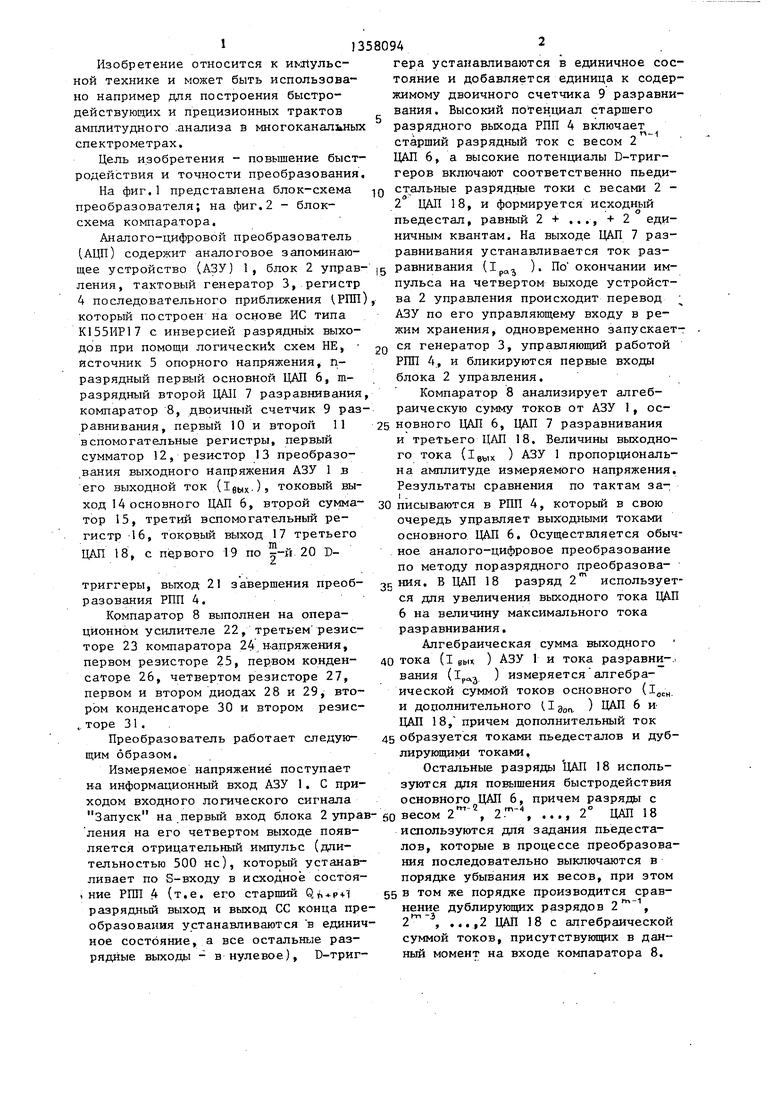

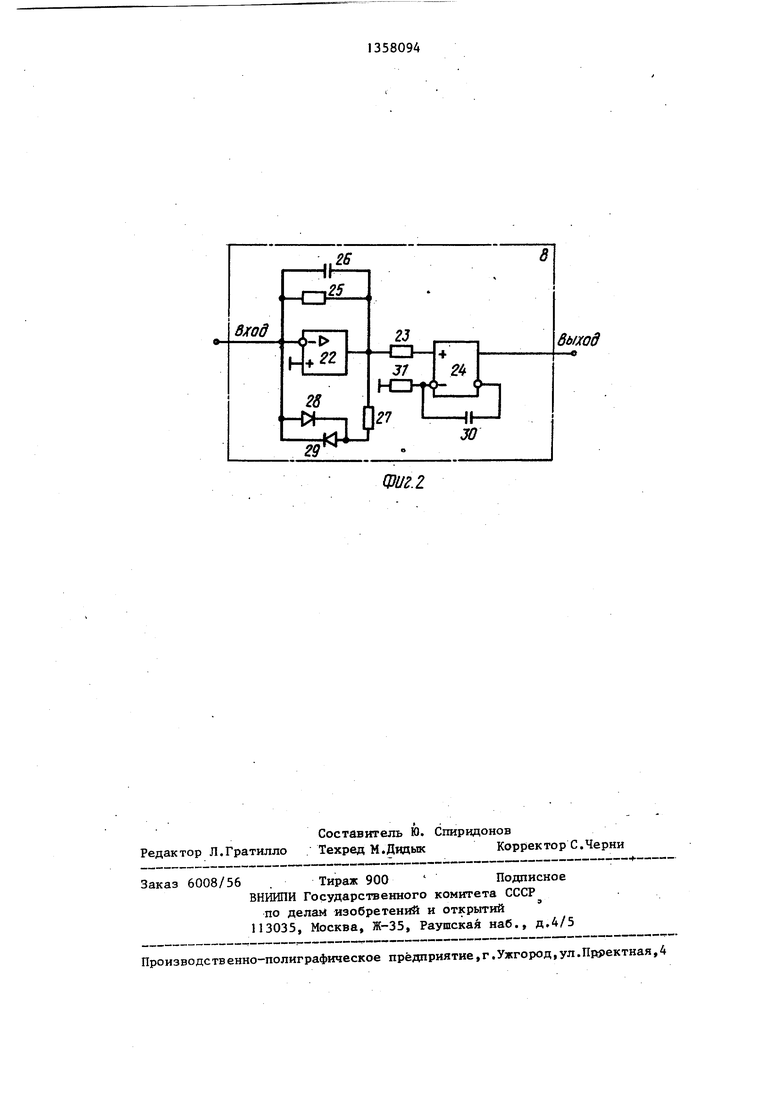

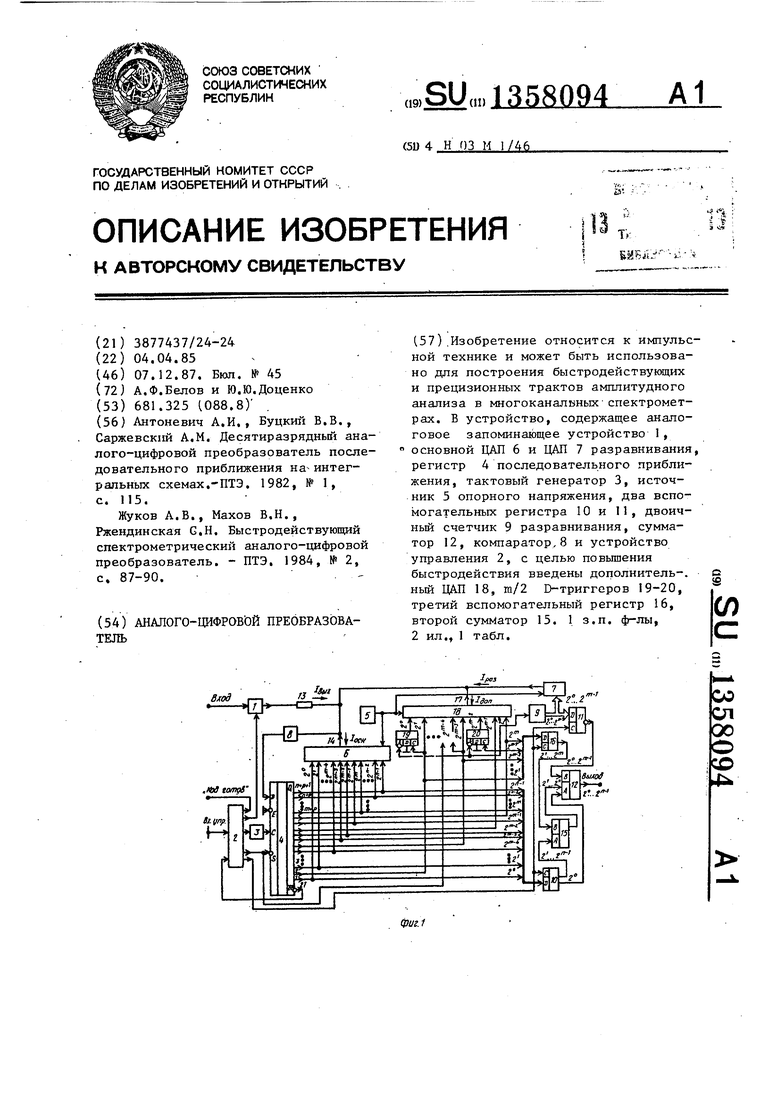

На фиг.1 представлена блок-схема IQ преобразователя; на фиг.2 - блок- схема компаратора.

Аналого-цифровой преобразователь (АЦП) содержит аналоговое заломинаюгера устанавливаются в единичное сос тояние и добавляется единица к содер жимому двоичного счетчика 9 разравнивания . Высокий потенциал старшего разрядного выхода РПП 4 включает

«„о -

старшин разрядный ток с весом 2 ДАЛ 6, а высокие потенциалы D-триг- геров включают соответственно пьеди- стальные разрядные токи с весами 2 - 2 ЦАП 18, и формируется исходный пьедестал, равный 2 + ..., + 2 единичным квантам. На выходе ЦАП 7 разравнивания устанавливается ток раз20

щее устройство (АЗУ) 1, блок 2 управ- ig равнивания (Ip ). По окончании им- ления, тактовый генератор 3, регистр 4 последовательного приближения (.РПП), который построен на основе ИС типа К155ИР17 с инверсией разряднь1х выходов при помощи лoгичecкиk схем НЕ, ИСТОЧНИК 5 опорного напряжения Поразрядный первый основной ЦАП 6, га- разрядный второй ЦАП 7 разравнивания, компаратор 8, двоичный счетчик 9 разравнивания, первый 10 и второй 11 вспомогательные регистры, первый сумматор 12, резистор 13 преобразования выходного напряжения АЗУ 1 в его выходной ток (1вых.-)5 токовый выр 5

пульса на четвертом выходе устройства 2 управления происходит перевод АЗУ по его управляющему входу в режим хранения, одновременно запускает ся генератор 3, управляющий работой РШ1 4, и бликируются первые входы блока 2 управления.

Компаратор 8 анализирует алгебраическую сумму токов от АЗУ 1, ос- 25 новного ЦАП 6, ЦАП 7 разравнивания и третьего ЦАП 18. Величины выходного тока (igbix ) АЗУ 1 пропорциональна амплитуде измеряемого напряжения. Результаты сравнения по тактам заход 14 основного ЦАП 6, второй сумма- зо писываются в РПП 4, который в свою тор 15, третий вспомогательный регистр 16, токовый выход 17 третьего

т д тт 1 о -,.1 . J

очередь управляет выходными токами основного ЦАП 6. Осуществляется обычное аналого-цифровое преобразование по методу поразрядного преобразова- триггеры, выход 21 завершения преоб- разряд 2 использует, с первого 19 по -й 20 Dразования РПП 4.

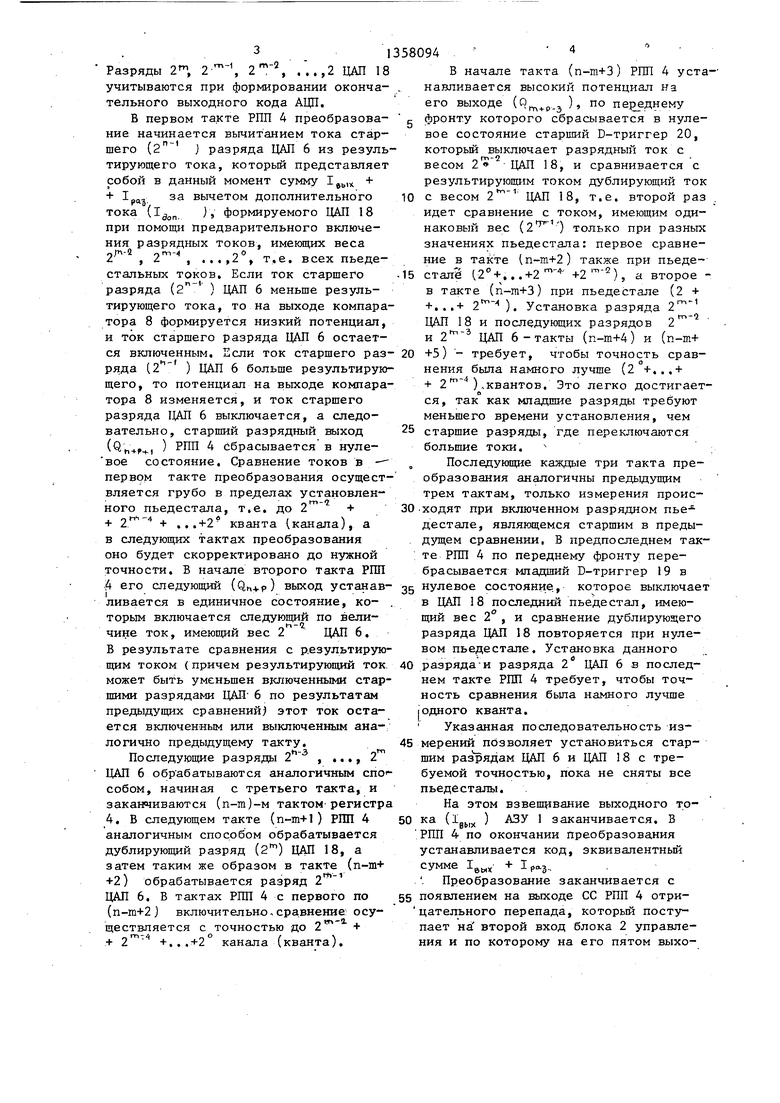

Компаратор 8 выполнен на операционном усилителе 22, третьем резисторе 23 компаратора 24,напряжения, первом резисторе 25, первом конденсаторе 26, четвертом резисторе 27, первом и втором диодах 28 и 29, втором конденсаторе 30 и втором резис- ,. торе 31.

Преобразователь работает следующим образом.

Измеряемое напряжение поступает на информационный вход АЗУ I. С приходом входного логического сигнала

ся для увеличения выходного тока ЦАП 6 на величину максимального тока разравнивания.

Алгебраическая сумма выходного

40 тока (l вых ) АЗУ 1 и тока разравни-.. вания (lpa,3 ) измеряется алгебраической суммой токов основнаго (IOCH. и дополнительного dson. ) ЦАП 6 и ЦАП 18, причем дополнительный ток

45 образуется токами пьедесталов и дублирующими токами.

Остальные разряды ЦАП 18 используются для повышения быстродействия основного ЦАП 6, причем разряды с

Запуск на первый вход блока 2 управ- 60 весом 2 , 2. , ,.., 2 ЦАП 18

, - , ,

ления на его четвертом выходе появляется отрицательный импульс (длительностью 500 не), который устанавливает по S-входу в исходное состоя- ( ние РПП 4 (т.е. его старший Qt, + p4l разрядный выход и выход СС конца преобразования устанавливаются в единичное состояние, а все остальные разрядные выходы - в нулевое), D-триггера устанавливаются в единичное состояние и добавляется единица к содержимому двоичного счетчика 9 разравнивания . Высокий потенциал старшего разрядного выхода РПП 4 включает

«„о -

старшин разрядный ток с весом 2 ДАЛ 6, а высокие потенциалы D-триг- геров включают соответственно пьеди- стальные разрядные токи с весами 2 - 2 ЦАП 18, и формируется исходный пьедестал, равный 2 + ..., + 2 единичным квантам. На выходе ЦАП 7 разравнивания устанавливается ток раз

равнивания (Ip ). По окончании им-

ульса на четвертом выходе устройства 2 управления происходит перевод АЗУ по его управляющему входу в режим хранения, одновременно запускается генератор 3, управляющий работой РШ1 4, и бликируются первые входы блока 2 управления.

Компаратор 8 анализирует алгебраическую сумму токов от АЗУ 1, ос- новного ЦАП 6, ЦАП 7 разравнивания и третьего ЦАП 18. Величины выходного тока (igbix ) АЗУ 1 пропорциональна амплитуде измеряемого напряжения. Результаты сравнения по тактам зася для увеличения выходного тока ЦАП 6 на величину максимального тока разравнивания.

Алгебраическая сумма выходного

40 тока (l вых ) АЗУ 1 и тока разравни-.. вания (lpa,3 ) измеряется алгебраической суммой токов основнаго (IOCH. и дополнительного dson. ) ЦАП 6 и ЦАП 18, причем дополнительный ток

45 образуется токами пьедесталов и дублирующими токами.

Остальные разряды ЦАП 18 используются для повышения быстродействия основного ЦАП 6, причем разряды с

60 весом 2 , 2. , ,.., 2 ЦАП 18

, - , ,

используются для задания пьедесталов, которые в процессе преобразования последовательно выключаются в порядке убывания их весов, при зтом 55 в том же порядке производится сравнение дублирующих разрядов 2

т-1

, м-1 -3

..,,2 ЦАП 18 с алгебраической суммой токов, присутствуюпщх в данный момент на входе компаратора 8.

, ...,2 ЦАП 18

Разряды 2,

учитываются при формировании оконча- . тельного выходного кода АЦП,

В первом такте РПП 4 преобразование начинается вычитанием тока старшего ( j разряда ЦАП 6 из результирующего тока, который представляет собой в данный момент сумму + Ipaj за вычетом дополнительного тока ( V формируемого ЦАП 18 при помощи предварительного включения разрядных токов, имеющих веса , , ...,2°, т.е. всех пьеде- стальных токов. Если ток старшего разряда (2 ) ЦАП 6 меньше результирующего тока, то на выходе компаратора 8 формируется низкий потенциал, и ток старшего разряда ЦАП 6 остает13

.

ся включенным. Если ток старшего раз- 20 +5) - требует, чтобы точность срав- ряда ) ЦАП 6 больше результирую- нения была намного лучше (2°+...+ щего, то потенциал на вьпсоде компара- + 2 ),квантов. Это легко достигает- тора 8 изменяется, и ток старшего разряда ЦАП 6 выключается, а следося, так как младшие разряды требуют меньшего времени установления, чем

вательно, старший разрядный выход

25

(Q.

) РПП 4 сбрасывается в нулестаршие разряды, где переключаются большие токи.

, Последующие каждые три такта преобразования аналогичны предьщушим трем тактам, только измерения проис- 30.ходят при включенном разрядном пье дестале, являющемся старшим в предыдущем сравнении, В предпоследнем так- ; те РПП 4 по переднему фронту перебрасывается младший D-триггер 19 в А его следующий () выход устанав- 35 нулевое состояние., которое выключает

в ЦАП 18 последний пьедестал, имеющий вес 2 , и сравнение дублирующего разряда ЦАП 18 повторяется при нулевом пьедестале. Установка данного щим током (причем результирующий ток 40 разряда-и разряда 2 ЦАП 6 в послед- может быть умсньщен включенными стар- нем такте РПП 4 требует, чтобы точность сравнения бьша намного лучше .одного кванта.

Указанная последовательность из- 45 мерений позволяет установиться старшим раз рядам ЦАП 6 и ЦАП 18 с требуемой точностью, пока не сняты все пьедесталы.

На этом взвешивание выходного то- АЗУ 1 заканчивается. В

h + P-n

вое состояние. Сравнение токов в - первом такте преобразования осуществляется грубо в пределах установленного пьедестала, т.е. до 2 + + + ...+2 кванта (канала), а в следующих тактах преобразования оно будет скорректировано до нужной точности. В начале второго такта РПП

ливается в единичное состояние, ко- . торым включается следующий по величине ток, имеюпдий вес 2 ЦАП 6. В результате сравнения с результирующими разрядами ЦАП 6 по результатам предыдущих сравнений этот ток остается включенным или выключенным аналогично предыдущему такту.

Последующие разряды , «.., 2 ЦАП 6 обрабатываются аналогичным спо- собом, начиная с третьего такта, и заканчиваются (п-т)-м тактом-регистра 4. В следующем такте (n-m+1) РПП 4 аналогичным способом обрабатывается дублирующий разряд (2) ЦАП 18, а затем таким же образом в такте (n-m+ +2) обрабатывается разряд 2 ЦАП 6. В тактах РПП 4 с первого по (п-т+2) включительно,сравнение: осуществляется с точностью до 2 + + +...+2° канала (кванта).

50 ка (Ig, )

РПП 4 по окончании преобразования устанавливается код, эквивалентный сумме 1ц„, + .. . Преобразование заканчивается с 55 появлением на выходе СС РПП 4 отри- цательного перепада, который поступает на второй вход блока 2 управления и по которому на его пятом выхо .

1358094 /

В начале такта (n-m+3) РПП 4 устанавливается высокий потенциал на

его выходе (. ), по переднему фронту которого сбрасывается в нулевое состояние старший D-триггер 20, который выключает разрядный ток с весом 2 ЦАП 18, и сравнивается с результирующим током дублирующий ток

0 с весом 2 ЦАП 18, т.е. второй раз идет сравнение с током, имеющим одинаковый вес () только при разных значениях пьедестала: первое сравнение в такте (n-m+2) также при пьеде-5 стапё (2° + . .. ), а второе - в такте (п-га+3) при пьедестале (2 + + ...+ ). Установка разряда

ЦАП 18 и последующих разрядов 2

m-l

и ЦАП 6-такты (n-m+4) и (n-m+

+5) - требует, чтобы точность срав- нения была намного лучше (2°+...+ + 2 ),квантов. Это легко достигает

ся, так как младшие разряды требуют меньшего времени установления, чем

старшие разряды, где переключаются большие токи.

На этом взвешивание выходного то- АЗУ 1 заканчивается. В

50 ка (Ig, )

РПП 4 по окончании преобразования устанавливается код, эквивалентный сумме 1ц„, + .. . Преобразование заканчивается с 55 появлением на выходе СС РПП 4 отри- цательного перепада, который поступает на второй вход блока 2 управления и по которому на его пятом выхо51358094

формируется стробирующий импульс. 18,

отк рио лее

По этому импульсу переписываются коды в первьп 10, второй 11 и третий 16 вспомогательные регистры соответственно. Кроме того, АЗУ 1 переходит в режим выборки по его управляющему входу, появляется импульс Код готов и разблокируются первые входы блока 2.

В сумматоре 15 суммируются управляющие коды ЦАП 6 и ЦАП 18, которые поступают с выходов 2 , . . ., 2 первого регистра 10 и выходов 2 ,...

при

2 третьего регистра 16, и на выходе ig время преобразования АЦП составлять

сумматора 15 формируется код 2 ,.«.,

2.

Полученный в сумматоре 15 код и код младшего разряда регистра 10,

в такте (n+p+l ) , , .

Из таблицы видно, что старшие шесть разрядов успевают установитьс 20.(поеле их включения при грубом срав нении) с требуемой точностью до сня тия пьедесталов 2° и 2, а мпадшие разряды устанавливаются за время, меньшее, чем 3,0i -

имеющего вес 2 , поступает на первые входы первого сумматора 12, на вторые выходы которого с Инверсных выходов второго регистра 11 постутает код разравнивания. В сумматоре 12

происходит вычитание кодов, поступив- 25 Предлагаемое решение позволило

ших на его входы (т.е. из суммарного преобразованного кода вычитается код разравнивания). Резуль -ат, соответ- ствуюш 1й измеряемому напряжению, по сигналу Код готов с выхода сумматора 12 переписывается во внешнюю память. После этого преобразователь готов к следующему преобразованию.

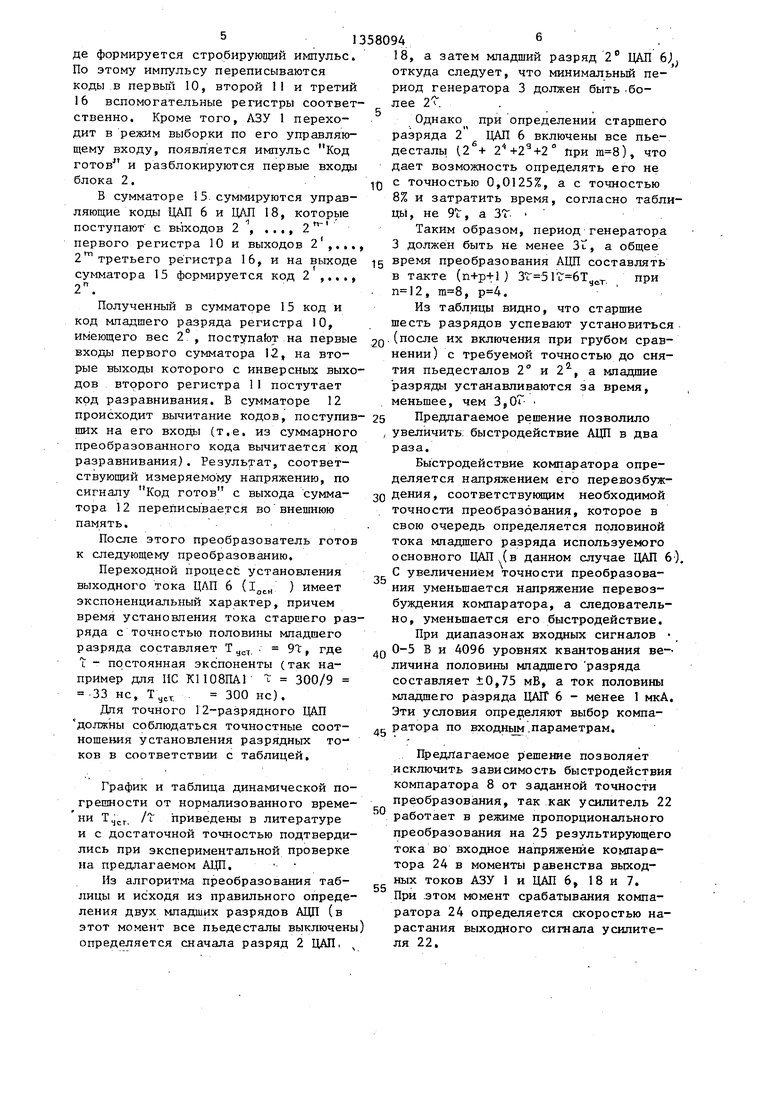

Переходной процесс установления выходного тока ЦАП 6 (. ) имеет экспоненциальный характер, причем время установления тока старшего разряда с точностью половины мпадшего

разряда составляет Т

аст.

91, где

L - постоянная экспоненты (так например для ИС К1108ПАГ Г 300/9 -33 НС, . 300 не).

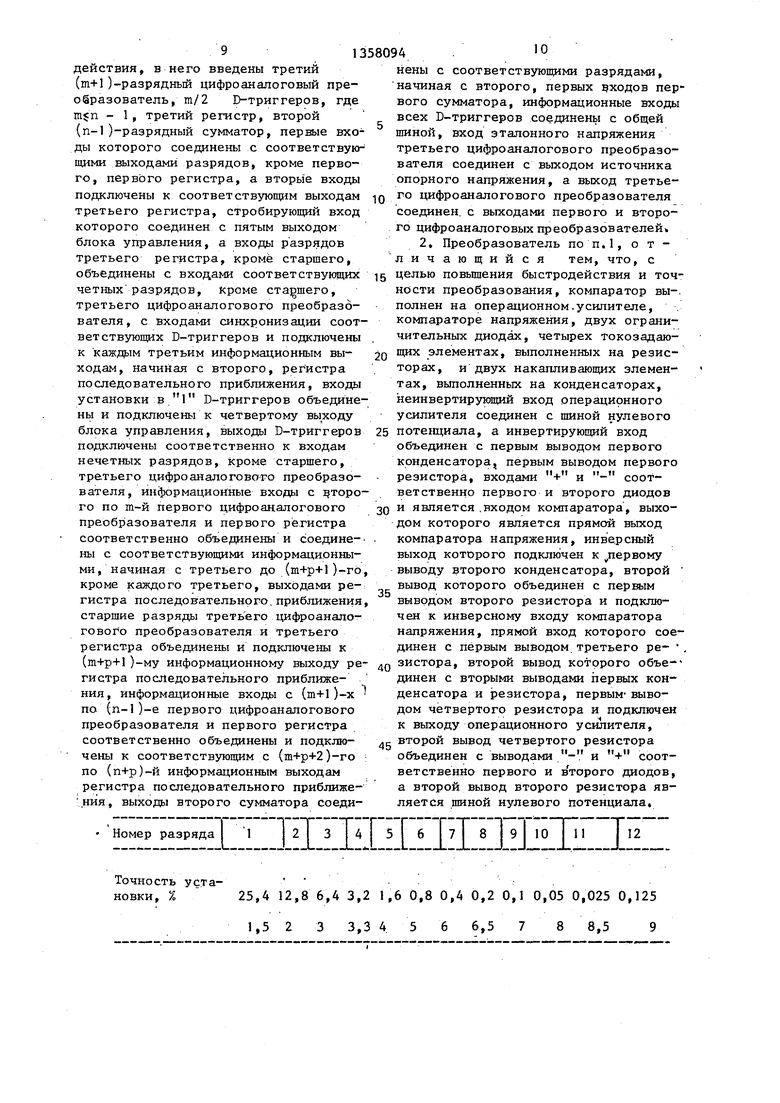

Для точного 12-разрядного ЦАП должны соблюдаться точностные соотношения установления разрядных токов в соответствии с таблицей.

График и таблица динамической погрешности от нормализованного време- ни . /t приведены в литературе и с достаточной точностью подтвердились при экспериментальной проверке на предлагаемом АЦП.

Из алгоритма преобразования таблицы и исходя из правильного определения двух младших разрядов АЦП (в этот момент все пьедесталы выключены определяется сначала разряд 2 ЦАП,

а затем младший разряд 2 ЦАП 6} откуда следует, что минимальный период генератора 3 должен быть -более 2.

Однако при определении старшего разряда 2 ЦАП 6 включены все пьедесталы ( 2 +2 +2° при ), что дает возможность определять его не с точностью 0,0125%, а с точностью 8% и затратить время, согласно таблицы , не 9t , а ЗГ-

Таким образом, период генератора 3 должен быть не менее 3t, а общее

при

ig время преобразования АЦП составлять

в такте (n+p+l ) , , .

Из таблицы видно, что старшие шесть разрядов успевают установиться 20.(поеле их включения при грубом сравнении) с требуемой точностью до снятия пьедесталов 2° и 2, а мпадшие разряды устанавливаются за время, меньшее, чем 3,0i -

5

, увеличить: быстродействие АЦП в два раза.

Быстродействие компаратора определяется напряжением его перевозбужQ дения, соответствукнцим необходимой точности преобразования, которое в свою очередь определяется половиной тока мпадшего разряда используемого основного ЦАП. (в данном случае ЦАП бО. С увеличением точности преобразования уменьшается напряжение перевозбуждения компаратора, а следовательно, уменьшается его быстродействие. При диапазонах входных сигналов

Q 0-5 В и 4096 уровнях квантований ве-- личина половины мпадшего разряда составляет ±0,75 мВ, а ток половины младшего разряда ЦАП 6 - менее 1 мкА. Эти условия определяют выбор компас ратора по входным,параметрам.

Предлагаемое решение позволяет исключить зависимость быстродействия компаратора 8 от заданной точности преобразования, так как усилитель 22 работает в режиме пропорционального преобразования на 25 результирующего тока во входное напряжение компаратора 24 в моменты равенства вьрсод- ных токов АЗУ 1 и ЦАП 6, 18 и 7. При .этом момент срабатывания компаратора 24 определяется скоростью нарастания выходного сигнала усилителя 22.

0

5

В .случае нарушения равенства токов усилитель 22 благодаря наличию цепи нелинейной-обратной связи (диоды

28 и 29 - резистор 27) будет рабо- тать в нелинейном режиме, ограничивая напряжение на входе компаратора 24. В момент сравнения с данной точностью выходных токов АЗУ 1 и ЦАП 6, 18 и 7 на прямом входе компаратора 24 устанавливается напряжение перевозбуждения, соответствующее его максимальному быстродействию.

Конденсатор 30 и резистор 31 об- разуют цепь положительной обратной связи компаратора 24, необходимую для устранения его самовозбуждения.

Конденсатор 26 обеспечивает устойчивость усилителя, сглаживание его переходной характеристики, сужение полосы пропускания и подавление избыточных резонансных шумов.

Ни токовом выходе 14 ЦАП 6 посто- янно поддерживается потенциал виртуальной земпи, выходное сопротивление ЦАП 6 (т,е.. входное сопротив- ление усилителя 22) составляет единицы ом, что уменьшает постоянную времени входной цепи усилителя 22. до величины менее 0,2 не.

Усилитель 22 должен быть широкополосным со скоростью нарастания выходного сигнала не менее 50 В/мкс (например, К574УД1, 154УД4 или гибридный микроузел КГ02-УИЗ и др,) ,

Таким образом, звено: усилитель 22 - компаратор 24 напряжения увели- чивает быстродействие и точность преобразования.

При использовании в предпоженном о устройстве усилителя КГ02-УИЗ, комг.г- паратора КР 597СА2 и ЦАП К 1108 ПА1 получены: время преобразования устройства 1,8 МКС, дифференциальная нелинейность 1% в динамическом диапазоне 200, при зтом термостабильность коэффициента преобразования составяет 0,025%/10 С, а нуля характеристики - 0,3 канала/10 С,

ормула изобретения

1, Аналого-цифровой преобразоваель, содержащий аналоговое запоминающее устройство, п-разрядный первый дифроаналоговый преобразователь и

-разрядный второй цифроаналоговый преобразователь, (п+р+1)-разрядный регистр последовательного прибли

40

10

15

20

жения, где р т/2, источник опорного напряжения, тактовый генератор, два регистра, двоичный счетчик импульсов, первый сумматор, компаратор и блок управления, первый вход которого является шиной управления, первый выход - шиной Код готов, а второй выход соединен с управляющим входом аналогового запоминающего устройства, информационный вход которого является входной шиной, а выход подключен к первому выводу токоогра- ничивающего элемента, выполненного на резисторе, второй вывод которого объединение выходами первого и второго цифроаналоговых преобразователей и подключен к входу компаратора, входы эталонного напряжения первого и второго цифроаналоговых преобразователей объединены .и подключены к выходу источника опорного напряжения, третий выход блока управления соединен с управляющим входом тактового генератора, выход которого подключен к С-входу регистра последовательного приближения, D-вход которого соединен с выходом компаратора, а S-вход объе- динен со счетным входом двоичного счетчика импульсов и подключен к четвертому выходу блока управления, втог рой вход которого соединен с выходом Конец преобразования регистра последовательного приближения, Е-вход которого является шиной нулевого потенциала, информационные входы первого и п-го разрядов первого цифроана- логового преобразователя и первого регистра соответственно объединены и подключены соответственно к первому и (п+р+1)-му разрядам регистра последовательного приближения, стро- бирующие входы первого и второго регистров объединены и подключены к

пятому выходу блока управления, ин- э

25

3035

0

5

формационные входы второго цифроана- логового преобразователя и второго регистра соответственно объединены и подключены к соответствующим выхо-. дам двоичного счетчика импульсов, выход первого разряда первого регистра соединен с входом первого разряда перилх входов первого сумматора, вы- лходы которого являются соответствую- ш;ими выходными шинами, а вторые входы подключены к инверсным выходам соответствующих разрядов второго регистра, отличающийся тем, что, с целью повышения быстродействия, в него введены третий (т+1)-разрядный цифроаналоговый преобразователь, т/2 D-триггеров, где mjn - 1, третий регистр, второй (п-1)-разрядный сумматор, первые входы которого соединены с соответствую щими выходами разрядов, кроме первого, первого регистра, а вторы е входы подключены к соответствующим выходам третьего регистра, стробирующий вход которого соединен с пятым выходом блока управления, а входы разрядов третьего регистра, кроме старшего, объединены с входами соответствующих четных разрядов, кроме ставшего, третьего цифроаналогового преобразователя, с входами синхронизации соответствующих D-триггеров и подключены к каждым третьим информационным выходам, начиная с второго, регистра последовательного приближения, входы установки в.1 D-триггеров объединены и подключены к четвертому выходу блока управления, выходы D-триггеров подключены соответственно к входам нечетных разрядов, кроме старшего, третьего цифроаналогового преобразователя, информационные входы с торо

го по т-й первого цифроаналогового преобразователя и первого регистра соответственно объединены и соединены с соответствующими информационными, начиная с третьего до (m+p+l)-rb кроме каждого третьего, выходами регистра последовательного,приближения старшие разряды треть его цифроаналогового преобразователя и третьего регистра объединены и подключены к (т+р+1)-му информационному выходу ре гистра последовательного приближения, информационные входы с (т+1)-х по (n-l)-e первого цифроаналогового преобразователя и первого регистра соответственно объединены и подключены к соответствующим с (т+р+2)-го по (п+р)-й информационным выходам регистра последовательного приближе- ния, выхо;цы второго сумматора соеди

Номер разряда

Crrj IIIi Z ll lIl JLT----I

1,5 2

3,3 4.

8094

йены

10

IQ с соответствующими разрядами, начиная с второго, первых входов первого сумматора, информационные входы всех D-триггеров соединены с общей шиной, вход эталонного напряжения третьего цифроаналогового преобразователя соединен с выходом источника опорного напряжения, а выход третьего цифроаналогового преобразователя соединен, с выходами первого и второго цифроаналоговых преобразователей. 2, Преобразователь по п.1, о т лич ающий ся

тем, что, с

целью повышения быстродействия и точности преобразования, компаратор вы-, полней на операционном.усилителе, компараторе напряжения, двух ограничительных диодах, четырех токозадаюш;их элементах, выполненных на резисторах, и двух накапливающих элементах, выполненных на конденсаторах, неинвертирующий вход операционного усилителя соединен с шиной нулевого

потенциала, а инвертирующий вход объединен с первым выводом первого конденсатора, первым выводом первого резистора, входами + и - соответственно первого и второго диодов

и является.входом компаратора, выходом которого является прямой выход компаратора напряжения, инверсный выход которого подключен к первому выводу второго конденсатора, второй вывод которого объединен с первым выводом второго резистора и подключен к инверсному входу компаратора напряжения, прямой вход которого соединен с первым выводом.третьего ре- , зистора, второй вывод которого объе- динен с вторыми выводами первых конденсатора и резистора, первым- выво Q

45

дом четвертого резистора и подключен к выходу операционного усилителя, второй вывод четвертого резистора объединен с выводами - и + соответственно первого и в торого диодов, а второй вывод второго резистора является шиной нулевого потенциала.

12

6,5

8 8,5

Редактор Л.Гратилло

Составитель К). Спиридонов

Техред М.Дидык Корректор С.Черни

Заказ 6008/56 . Тираж 900 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушскай наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Прректная,4

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1427564A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Функциональный аналого-цифровой преобразователь | 1989 |

|

SU1688411A1 |

| Генератор гармонических сигналов | 1989 |

|

SU1626379A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

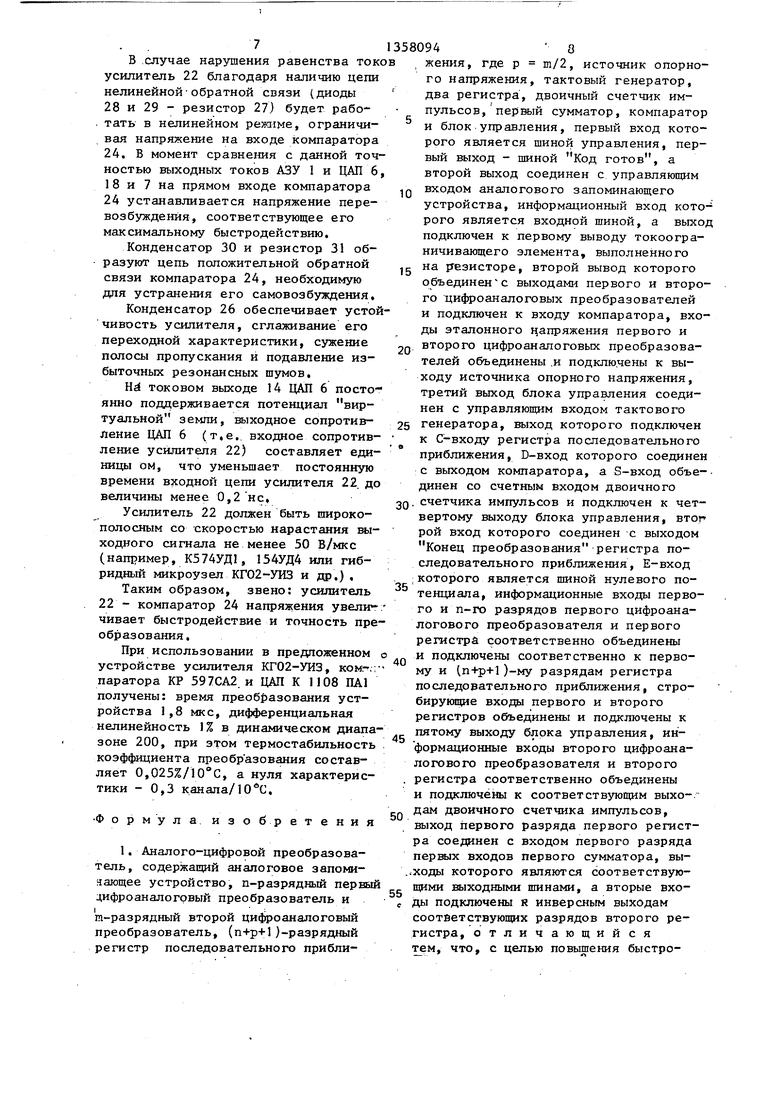

.Изобретение относится к импульсной технике и может быть использовано для построения быстродействующих и прецизионных трактов амплитудного анализа в многоканальных-спектрометрах. В устройство, содержащее аналоговое запоминающее устройство 1, основной ЦАП 6 и ЦАП 7 разравнивания, регистр 4 последовательного приближения, тактовый генератор 3, источник 5 опорного напряжения, два вспомогательных регистра 10 и 11, двоич- ньй счетчик 9 разравнивания, сумматор 12, компаратор,8 и устройство управления 2, с целью повышения быстродействия введены дополнитель-. ный ЦАП 18, т/2 D-триггеров 19-20, третий вспомогательный регистр 16, второй сумматор 15. 1 з.п. ф-лы, 2 ил., 1 табл. I (Л со ел ас :

| Антоневич А.И., Буцкий В.В., Саржевский A.M | |||

| Десятиразрядный аналого-цифровой преобразователь последовательного приближения на- интегральных схемах.-ПТЭ | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Жуков А.В., Махов В.Н., Ржендинская G.H | |||

| Быстродействующий спектрометрический аналого-цифровой преобразователь | |||

| - ПТЭ | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

Авторы

Даты

1987-12-07—Публикация

1985-04-04—Подача