Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны компараторы двоичных чисел (см., например, патент РФ 2300131, кл. G06F 7/02, 2007 г.), которые формируют признаки соотношений А>В, А=В, где А=а1а0, В=b1b0 - двухразрядные двоичные числа, задаваемые двоичными сигналами a0, a1, b0, b1 ∈{0,1}, и с учетом рис.1.35б на стр.57 в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. М.: Металлургия, 1988, а также рис.4-1 на стр.170, рис.4-4 на стр.171, рис.4-8 на стр.173 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974, содержат транзисторы и резисторы.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных компараторов двоичных чисел, относится низкое быстродействие, обусловленное тем, что максимальное время задержки распространения в них сигнала определяется выражением τ=5τT, где τТ - время задержки транзистора.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип компаратор двоичных чисел (рис.8.32а на стр.500 в книге Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. М.: Радио и связь, 1990), который формирует признаки соотношений А>В, А=В, где A=a1a0, В=b1b0 - двухразрядные двоичные числа, задаваемые двоичными сигналами a0, a1, b0, b1 ∈{0,1}, и с учетом рис.8.33а, 8.33б на стр.501 в книге Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. М.: Радио и связь, 1990, рис.1.35е на стр.57 в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. М.: Металлургия, 1988, а также рис.4-1 на стр.170, рис.4-4 на стр.171 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974, содержит 26 транзисторов и 14 резисторов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится низкое быстродействие, обусловленное тем, что максимальное время задержки распространения сигнала в прототипе определяется выражением τ=4τT, где τT - время задержки транзистора.

Техническим результатом изобретения является повышение быстродействия при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в компараторе двоичных чисел, содержащем 26 транзисторов и 14 резисторов, особенность заключается в том, что в него дополнительно введены три транзистора, причем все транзисторы подключены эмиттерами к шине нулевого потенциала и сгруппированы в девять групп так, что i-я  и первая группы содержат соответственно три и четыре транзистора, а вторая группа дополнительно содержит четвертый транзистор, объединенные коллекторы первого, второго транзисторов i-й группы соединены с базой третьего транзистора i-й группы и первым выводом i-го резистора, подключенного вторым выводом к шине единичного потенциала, во второй группе объединенные коллекторы первого, второго транзисторов дополнительно соединены с базой четвертого транзистора, а коллектор и база j-го

и первая группы содержат соответственно три и четыре транзистора, а вторая группа дополнительно содержит четвертый транзистор, объединенные коллекторы первого, второго транзисторов i-й группы соединены с базой третьего транзистора i-й группы и первым выводом i-го резистора, подключенного вторым выводом к шине единичного потенциала, во второй группе объединенные коллекторы первого, второго транзисторов дополнительно соединены с базой четвертого транзистора, а коллектор и база j-го  транзистора первой группы соединены соответственно с первым выводом (j+9)-го резистора, подключенного вторым выводом к шине единичного потенциала, и j-м входом компаратора двоичных чисел, первый и второй выходы которого образованы соответственно объединенными первым выводом первого резистора, подключенного вторым выводом к шине единичного потенциала, коллекторами третьих транзисторов второй, шестой - девятой групп и объединенными первым выводом четырнадцатого резистора, подключенного вторым выводом к шине единичного потенциала, коллектором четвертого транзистора второй группы, коллекторами третьих транзисторов третьей-пятой групп, коллектор и база первого транзистора первой группы подключены соответственно к базе первого транзистора пятой группы и объединенным базам первых транзисторов третьей, шестой, седьмой групп, коллектор и база второго транзистора первой группы подключены соответственно к базе первого транзистора четвертой группы и объединенным базе второго транзистора шестой группы, базам первых транзисторов второй, восьмой групп, база и коллектор третьего транзистора первой группы подключены соответственно к базе второго транзистора пятой группы и объединенным базе первого транзистора девятой группы, базам вторых транзисторов третьей, восьмой групп, а база и коллектор четвертого транзистора первой группы подключены соответственно к базе второго транзистора четвертой группы и объединенным базам вторых транзисторов второй, седьмой, девятой групп.

транзистора первой группы соединены соответственно с первым выводом (j+9)-го резистора, подключенного вторым выводом к шине единичного потенциала, и j-м входом компаратора двоичных чисел, первый и второй выходы которого образованы соответственно объединенными первым выводом первого резистора, подключенного вторым выводом к шине единичного потенциала, коллекторами третьих транзисторов второй, шестой - девятой групп и объединенными первым выводом четырнадцатого резистора, подключенного вторым выводом к шине единичного потенциала, коллектором четвертого транзистора второй группы, коллекторами третьих транзисторов третьей-пятой групп, коллектор и база первого транзистора первой группы подключены соответственно к базе первого транзистора пятой группы и объединенным базам первых транзисторов третьей, шестой, седьмой групп, коллектор и база второго транзистора первой группы подключены соответственно к базе первого транзистора четвертой группы и объединенным базе второго транзистора шестой группы, базам первых транзисторов второй, восьмой групп, база и коллектор третьего транзистора первой группы подключены соответственно к базе второго транзистора пятой группы и объединенным базе первого транзистора девятой группы, базам вторых транзисторов третьей, восьмой групп, а база и коллектор четвертого транзистора первой группы подключены соответственно к базе второго транзистора четвертой группы и объединенным базам вторых транзисторов второй, седьмой, девятой групп.

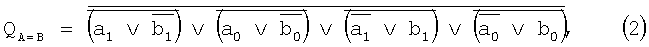

На чертеже представлена схема предлагаемого компаратора двоичных чисел.

Компаратор двоичных чисел содержит 29 транзисторов 1(1)(1), …, 1(2)(4), 1(3)(1),…, 1(9)(3) и 14 резисторов 21, …, 214, причем все транзисторы подключены эмиттерами к шине нулевого потенциала и сгруппированы в девять групп так, что i-я  и первая группы содержат соответственно транзисторы 1(i)(1), 1(i)(2), 1(i)(3) и 1(1)(1), …, 1(i)(4), а вторая группа дополнительно содержит транзистор 1(2)(4), объединенные коллекторы транзисторов 1(i)(1), 1(i)(2) соединены с базой транзистора 1(i)(3) и первым выводом резистора 2i, подключенного вторым выводом к шине единичного потенциала, объединенные коллекторы транзисторов 1(2)(1), 1(2)(2) дополнительно соединены с базой транзистора 1(2)(4), а коллектор и база транзистора 1(1)(j)

и первая группы содержат соответственно транзисторы 1(i)(1), 1(i)(2), 1(i)(3) и 1(1)(1), …, 1(i)(4), а вторая группа дополнительно содержит транзистор 1(2)(4), объединенные коллекторы транзисторов 1(i)(1), 1(i)(2) соединены с базой транзистора 1(i)(3) и первым выводом резистора 2i, подключенного вторым выводом к шине единичного потенциала, объединенные коллекторы транзисторов 1(2)(1), 1(2)(2) дополнительно соединены с базой транзистора 1(2)(4), а коллектор и база транзистора 1(1)(j)  соединены соответственно с первым выводом резистора 2j+9, подключенного вторым выводом к шине единичного потенциала, и j-м входом компаратора двоичных чисел, первый и второй выходы которого образованы соответственно объединенными первым выводом резистора 21, подключенного вторым выводом к шине единичного потенциала, коллекторами транзисторов 1(2)(3), 1(6)(3), …, 1(9)(3) и объединенными первым выводом резистора 214, подключенного вторым выводом к шине единичного потенциала, коллекторами транзисторов 1(2)(4), 1(3)(3), …, 1(5)(3), коллектор и база транзистора 1(1)(1) подключены соответственно к базе транзистора 1(5)(1) и объединенным базам транзисторов 1(3)(1), 1(6)(1), 1(7)(1), коллектор и база транзистора 1(1)(2) подключены соответственно к базе транзистора 1(4)(1) и объединенным базам транзисторов 1(2)(1), 1(6)(2), 1(8)(1), база и коллектор транзистора 1(1)(3) подключены соответственно к базе транзистора 1(5)(2) и объединенным базам транзисторов 1(3)(2), 1(8)(2), 1(9)(1), а база и коллектор транзистора 1(1)(4) подключены соответственно к базе транзистора 1(4)(2) и объединенным базам транзисторов 1(2)(2), 1(7)(2), 1(9)(2).

соединены соответственно с первым выводом резистора 2j+9, подключенного вторым выводом к шине единичного потенциала, и j-м входом компаратора двоичных чисел, первый и второй выходы которого образованы соответственно объединенными первым выводом резистора 21, подключенного вторым выводом к шине единичного потенциала, коллекторами транзисторов 1(2)(3), 1(6)(3), …, 1(9)(3) и объединенными первым выводом резистора 214, подключенного вторым выводом к шине единичного потенциала, коллекторами транзисторов 1(2)(4), 1(3)(3), …, 1(5)(3), коллектор и база транзистора 1(1)(1) подключены соответственно к базе транзистора 1(5)(1) и объединенным базам транзисторов 1(3)(1), 1(6)(1), 1(7)(1), коллектор и база транзистора 1(1)(2) подключены соответственно к базе транзистора 1(4)(1) и объединенным базам транзисторов 1(2)(1), 1(6)(2), 1(8)(1), база и коллектор транзистора 1(1)(3) подключены соответственно к базе транзистора 1(5)(2) и объединенным базам транзисторов 1(3)(2), 1(8)(2), 1(9)(1), а база и коллектор транзистора 1(1)(4) подключены соответственно к базе транзистора 1(4)(2) и объединенным базам транзисторов 1(2)(2), 1(7)(2), 1(9)(2).

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом.

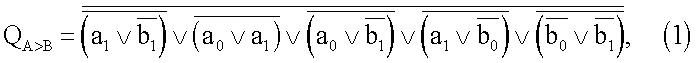

На его первый, второй и третий, четвертый входы подаются соответственно произвольные двоичные сигналы а0, а1, ∈{0,1} и b0, b1 ∈{0,1}, которые задают подлежащие сравнению двухразрядные двоичные числа А=a0a1 и В=b1b0 (а1, b1 и a0, b0 определяют значения старших и младших разрядов соответственно). Тогда сигналы на первом, втором выходах предлагаемого компаратора будут определяться выражениями

В таблице приведены значения реализуемых выражениями (1), (2) функций на всех возможных наборах значений их аргументов. С учетом таблицы имеем QA>B=1, если А>В, QA=B=1, если А=В.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый компаратор двоичных чисел формирует признаки соотношений А>В, А=В, где А=a1a0, В=b1b0 - двухразрядные двоичные числа, задаваемые двоичными сигналами a0, а1, b0, b1 ∈ {0,1}, и обладает более высоким по сравнению с прототипом быстродействием, т.к. максимальное время задержки распространения сигнала в предлагаемом компараторе определяется выражением τ=3τT, где τТ - время задержки транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2015 |

|

RU2621280C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2006 |

|

RU2300131C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2324971C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2361266C1 |

| Устройство для сравнения двоичных чисел | 1982 |

|

SU1051530A1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363036C1 |

| СИГНАЛИЗАТОР ОБЛЕДЕНЕНИЯ | 1994 |

|

RU2102791C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| Оптоэлектронный модуль | 1987 |

|

SU1444940A1 |

| Оптоэлектронный модуль | 1983 |

|

SU1119181A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом является повышение быстродействия устройства. Компаратор содержит 29 транзисторов, сгруппированных в девять групп, и 14 резисторов. 1 ил., 1 табл.

Компаратор двоичных чисел, содержащий 26 транзисторов и 14 резисторов, отличающийся тем, что в него дополнительно введены три транзистора, причем все транзисторы подключены эмиттерами к шине нулевого потенциала и сгруппированы в девять групп так, что i-я  и первая группы содержат соответственно три и четыре транзистора, а вторая группа дополнительно содержит четвертый транзистор, объединенные коллекторы первого, второго транзисторов i-й группы соединены с базой третьего транзистора i-й группы и первым выводом i-го резистора, подключенного вторым выводом к шине единичного потенциала, во второй группе объединенные коллекторы первого, второго транзисторов дополнительно соединены с базой четвертого транзистора, а коллектор и база j-го

и первая группы содержат соответственно три и четыре транзистора, а вторая группа дополнительно содержит четвертый транзистор, объединенные коллекторы первого, второго транзисторов i-й группы соединены с базой третьего транзистора i-й группы и первым выводом i-го резистора, подключенного вторым выводом к шине единичного потенциала, во второй группе объединенные коллекторы первого, второго транзисторов дополнительно соединены с базой четвертого транзистора, а коллектор и база j-го  транзистора первой группы соединены соответственно с первым выводом (j+9)-го резистора, подключенного вторым выводом к шине единичного потенциала, и j-м входом компаратора двоичных чисел, первый и второй выходы которого образованы соответственно объединенными первым выводом первого резистора, подключенного вторым выводом к шине единичного потенциала, коллекторами третьих транзисторов второй, шестой - девятой групп и объединенными первым выводом четырнадцатого резистора, подключенного вторым выводом к шине единичного потенциала, коллектором четвертого транзистора второй группы, коллекторами третьих транзисторов третьей - пятой групп, коллектор и база первого транзистора первой группы подключены соответственно к базе первого транзистора пятой группы и объединенным базам первых транзисторов третьей, шестой, седьмой групп, коллектор и база второго транзистора первой группы подключены соответственно к базе первого транзистора четвертой группы и объединенным базе второго транзистора шестой группы, базам первых транзисторов второй, восьмой групп, база и коллектор третьего транзистора первой группы подключены соответственно к базе второго транзистора пятой группы и объединенным базе первого транзистора девятой группы, базам вторых транзисторов третьей, восьмой групп, а база и коллектор четвертого транзистора первой группы подключены соответственно к базе второго транзистора четвертой группы и объединенным базам вторых транзисторов второй, седьмой, девятой групп.

транзистора первой группы соединены соответственно с первым выводом (j+9)-го резистора, подключенного вторым выводом к шине единичного потенциала, и j-м входом компаратора двоичных чисел, первый и второй выходы которого образованы соответственно объединенными первым выводом первого резистора, подключенного вторым выводом к шине единичного потенциала, коллекторами третьих транзисторов второй, шестой - девятой групп и объединенными первым выводом четырнадцатого резистора, подключенного вторым выводом к шине единичного потенциала, коллектором четвертого транзистора второй группы, коллекторами третьих транзисторов третьей - пятой групп, коллектор и база первого транзистора первой группы подключены соответственно к базе первого транзистора пятой группы и объединенным базам первых транзисторов третьей, шестой, седьмой групп, коллектор и база второго транзистора первой группы подключены соответственно к базе первого транзистора четвертой группы и объединенным базе второго транзистора шестой группы, базам первых транзисторов второй, восьмой групп, база и коллектор третьего транзистора первой группы подключены соответственно к базе второго транзистора пятой группы и объединенным базе первого транзистора девятой группы, базам вторых транзисторов третьей, восьмой групп, а база и коллектор четвертого транзистора первой группы подключены соответственно к базе второго транзистора четвертой группы и объединенным базам вторых транзисторов второй, седьмой, девятой групп.

| ШЕВКОПЛЯС Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения | |||

| - М.: Радио и связь, 1990, с.500-501 | |||

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2006 |

|

RU2300131C1 |

| ЦИФРОВОЙ КОМПАРАТОР | 0 |

|

SU303630A1 |

| Компаратор | 1978 |

|

SU790257A1 |

| JP 10079651 A, 24.03.1998 | |||

| US 4982119 A, 01.01.1991. | |||

Авторы

Даты

2010-05-10—Публикация

2008-10-28—Подача