Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в качестве широкополосного усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления (uу). Такие устройства применяются в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых перемножителях сигналов и т.д.

В настоящее время в аналоговой микросхемотехнике в составе систем электронной регулировки усиления широкое применение находит дифференциальный усилитель с управляемым статическим режимом. Данная структура стала основой для построения многих известных в настоящее время управляемых усилителей и аналоговых перемножителей сигналов на базе дифференциальных каскадов [1-17].

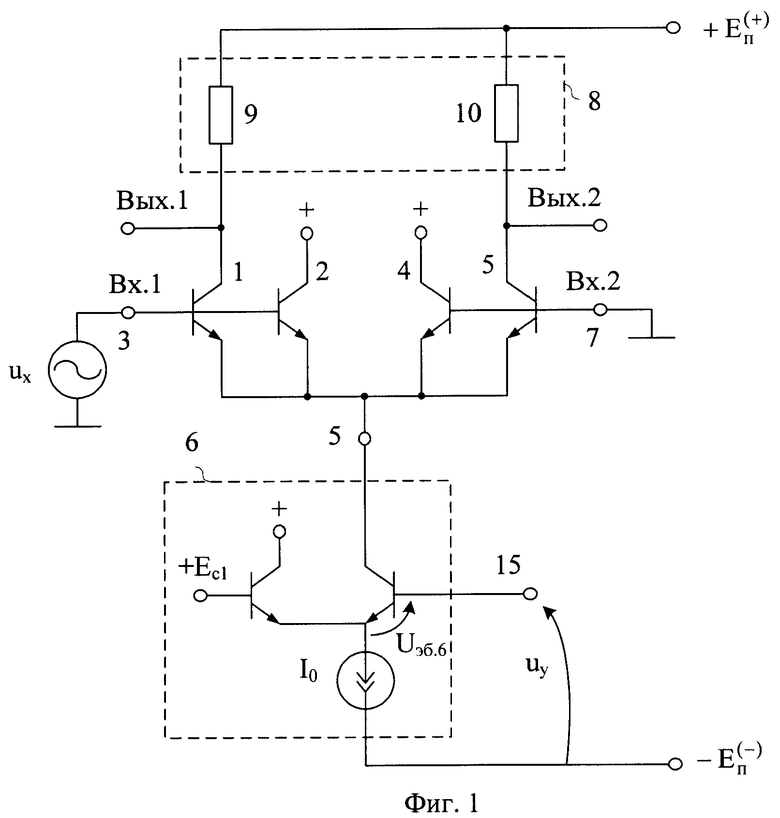

Ближайшим прототипом является дифференциальный усилитель (фиг.1), описанный в патентной заявке США №2007/0090876, содержащий первый 1 и второй 2 входные транзисторы с объединенными эмиттерами, базы которых соединены с первым 3 входом дифференциального усилителя, третий 4 и четвертый 5 входные транзисторы, эмиттеры которых соединены с эмиттерами первого 1 и второго 2 входных транзисторов и выходом 5 управляемого источника тока 6, а базы соединены со вторым 7 входом дифференциального усилителя, цепь нагрузки 8, связанную с коллекторами первого 1 и четвертого 5 входных транзисторов.

Особенность схемы известного дифференциального усилителя фиг.1 состоит в том, что уровень его выходного статического напряжения зависит от уровня сигнала управления uу, что ограничивает его применение в схемах с непосредственной связью каскадов.

В цифровых интегральных микросхемах результатом увеличения скорости обработки информации стали тенденции постоянного уменьшения напряжения питания, что является «анафемой» в аналоговом проектировании с высокими характеристиками. При технологических нормах 350 нм (3.3 В) по прежнему достаточно схемотехнических возможностей для аналоговых проектирований с высокими характеристиками, хотя наличие ±5 В питания было бы предпочтительнее. При нормах 180 нм (1.8 В) процесс усложняется и статические характеристики аналоговых устройств страдают. В этой связи необходимо развитие новых подходов к проектированию микросхем, ориентированных на снижение мощности, улучшение производительности при низковольтном питании.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы X диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако SiGe-технология накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы (Uкэ.max=1÷2,9 B). Создание схемотехники IP блоков для SiGe-технологии является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем.

Последние несколько лет источники питания с напряжением 5 В вытесняются более низковольтными. Требования к уменьшению рассеиваемой мощности и уменьшению числа батарей в таких приложениях, как беспроводные устройства связи и персональные компьютеры, привели к снижению напряжения питания в цифровых схемах до уровня 1,5 В. Эта тенденция, как отмечалось выше, реализована в современных SiGe транзисторах, которые сконструированы так, чтобы обеспечить максимальную частоту среза (f1) в компромиссе с напряжением пробоя (Uпр). Для кремниевых транзисторов существует следующее фундаментальное ограничение: f1×Uпр≈const.

Таким образом, малые размеры транзисторов, обеспечивающие высокие значения f1 (до 200 ГГц), привели к снижению напряжения питания микросхем до 1,2÷1,5 В.

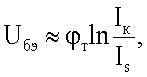

Уменьшение напряжения питания (Еп) в биполярных схемах приводит к появлению новых проблем и некоторые из них становятся трудно решаемыми при напряжении питания менее 2 В. Принципиальная сложность уменьшения напряжения Еп состоит в том, что биполярный транзистор имеет фиксированное напряжение база-эмиттер Uбэ, которое не уменьшается линейно с уменьшением технологических норм, так как

где φт=KT/q, Iк - ток коллектора, и Is - обратный ток эмиттерного р-n перехода. При этом параметры транзистора и уровни тока оказывают слабое влияние на напряжение Uбэ. На практике плотность тока в биполярном транзисторе (Iк/Is), изменяя свое значение, также слабо влияет на напряжение Uбэ. Если в используемой технологии Uбэ=0,7÷0,8 В, то использование 1,5 В источника питания приводит к тому, что между «землей» и шиной Еп не может быть включено больше, чем один переход база-эмиттер.

Учитывая вышесказанное, а также численные значения напряжения Uбэ≈700 мВ, можно сделать вывод о том, что запрещается использовать многоярусные дифференциальные пары или каскадные конфигурации (архитектуры) при напряжении питания 1,5 В. Этому условию прототип не удовлетворяет.

Таким образом, отсутствие возможности масштабирования напряжения на переходе база-эмиттер еще больше обостряет проблему дальнейшего масштабирования напряжения питания схем на биполярных транзисторах.

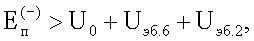

Существенный недостаток известного устройства фиг.1 состоит в том, что оно оказывается работоспособным только при сравнительно больших уровнях напряжения питания (±ЕП>2,2÷2,4 В). Это связано с особенностями архитектуры известного ДУ, которая имеет «двухъярусную» структуру. Схема фиг.1 оказывается не работоспособной при напряжениях  , меньших 1,5 В, так как здесь должно быть

, меньших 1,5 В, так как здесь должно быть

где U0 - минимальное напряжение на источнике тока I0, входящего в структуру управляемого источника тока 6;

Uэб≈0,7 В - напряжение эмиттер-база транзистора 2, а также транзистора, входящего в структуру управляемого источника тока 6.

При типовом построении двухполюсника I0 численные значения U0≈0,7 В. Таким образом, в известном ДУ  . Кроме этого, в известном ДУ достаточно трудно обеспечить высокую линейность характеристики управления в широком диапазоне изменения uу.

. Кроме этого, в известном ДУ достаточно трудно обеспечить высокую линейность характеристики управления в широком диапазоне изменения uу.

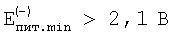

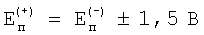

Основная цель предлагаемого изобретения состоит в уменьшении напряжения питания дифференциального усилителя с управляемым коэффициентом усиления до уровня 1,5 В.

Дополнительная цель - повышение линейности характеристики управления ДУ без потери его базового свойства - способности работать при  .

.

Поставленная цель достигается тем, что в ДУ, содержащем первый 1 и второй 2 входные транзисторы с объединенными эмиттерами, базы которых соединены с первым 3 входом дифференциального усилителя, третий 4 и четвертый 5 входные транзисторы, эмиттеры которых соединены с эмиттерами первого 1 и второго 2 входных транзисторов и выходом 5 управляемого источника тока 6, а базы соединены со вторым 7 входом дифференциального усилителя, цепь нагрузки 8, связанную с коллекторами первого 1 и четвертого 5 входных транзисторов, предусмотрены новые элементы и связи - в схему введен дополнительный двухполюсник 11, соединенный со входом 12 дополнительного усилителя тока 13 и коллекторами второго 2 и третьего 4 входных транзисторов, причем выход 14 дополнительного усилителя тока 13 подключен ко входу 15 управляемого источника тока 6, а основной выход 16 дополнительного преобразователя «напряжение-ток» 17 связан со входом 12 дополнительного усилителя тока 13.

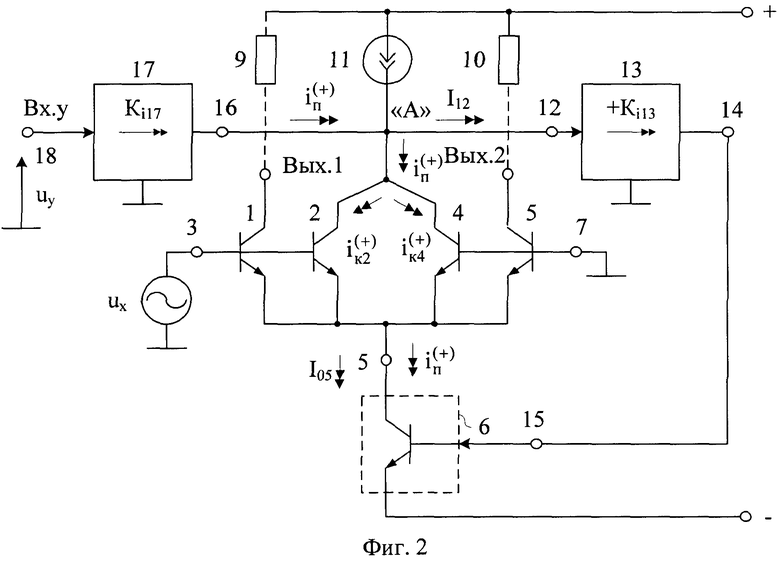

На фиг.1 показана схема ДУ-прототипа, а на фиг.2 - схема заявляемого ДУ в соответствии с п.1 формулы изобретения.

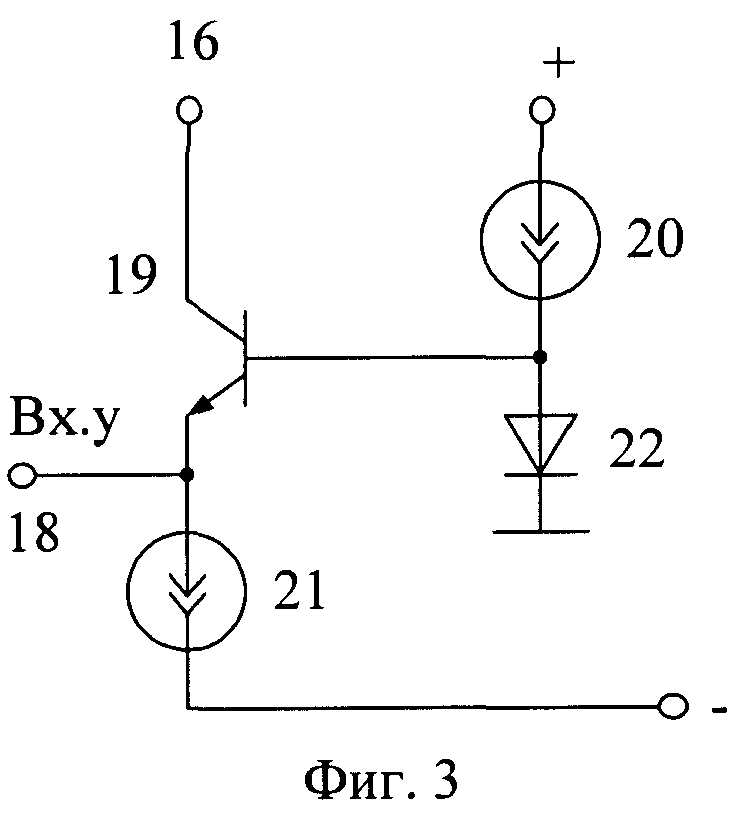

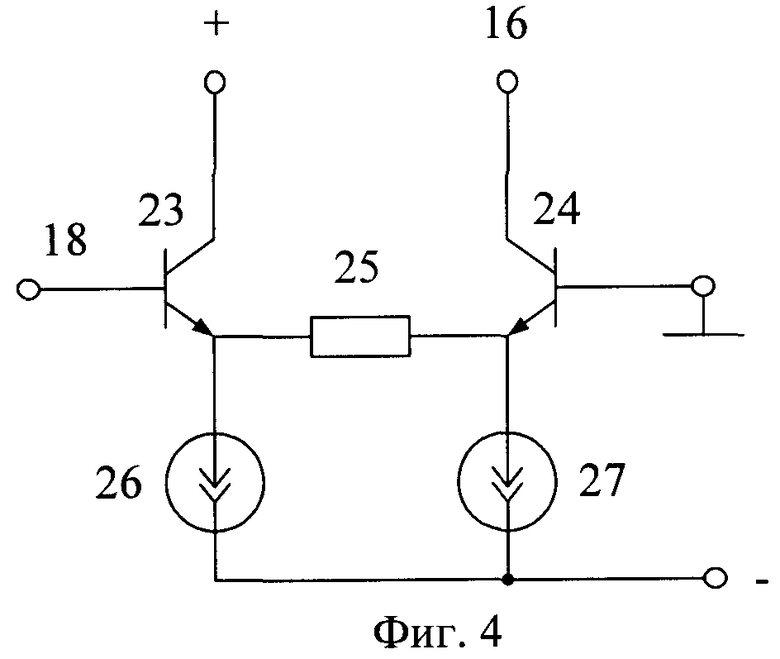

На фиг.3-4 представлены частные варианты построения преобразователя «напряжение-ток» 17.

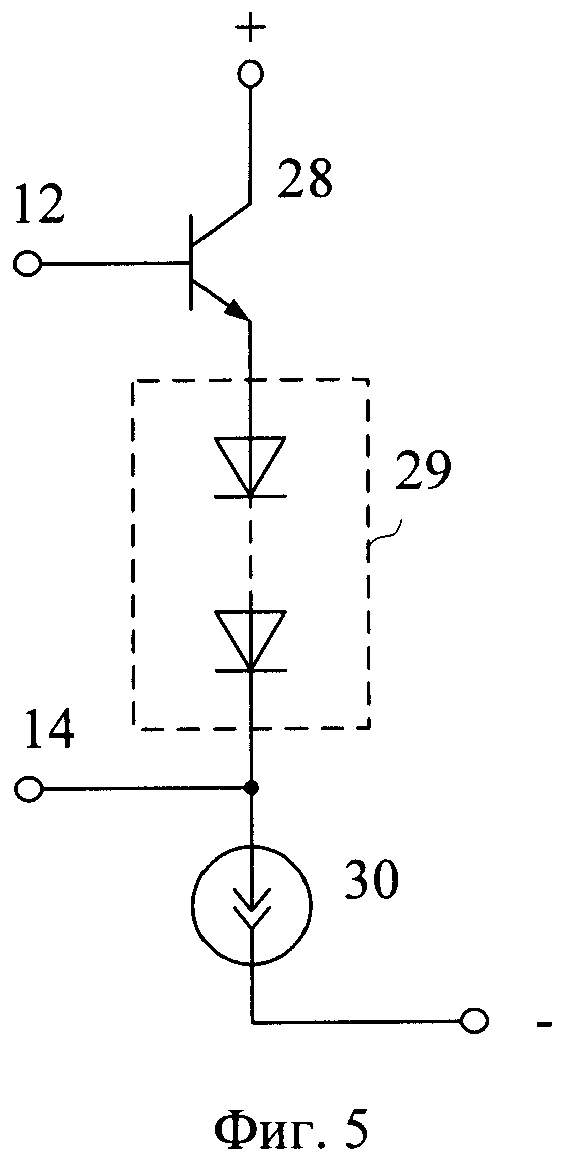

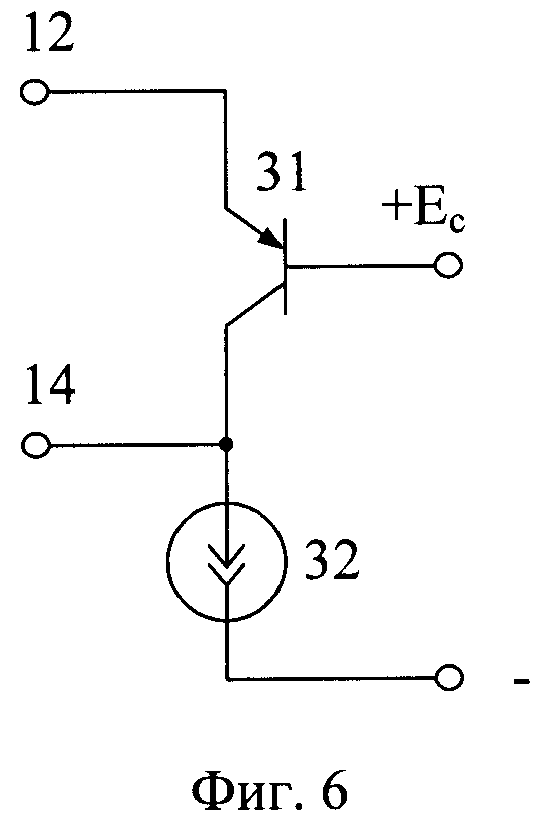

Варианты построения дополнительного усилителя тока 13 показаны на фиг.5-6.

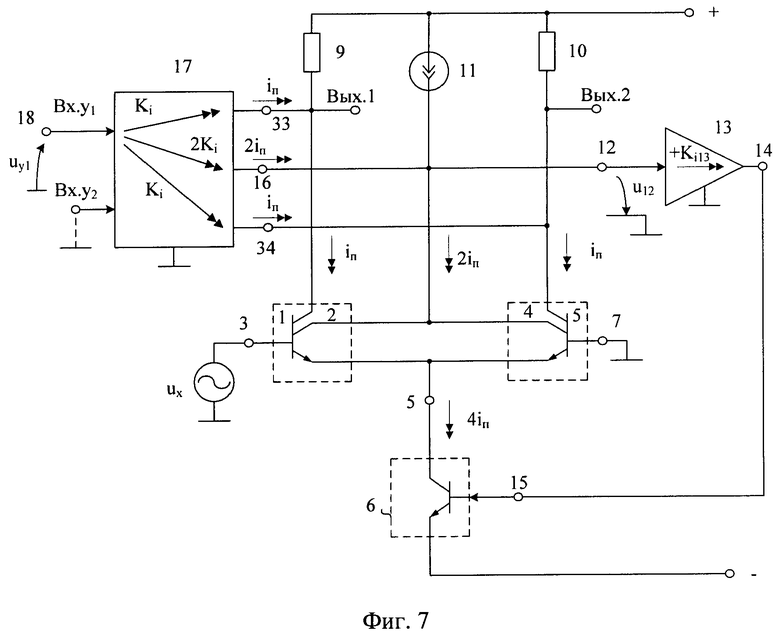

На фиг.7 приведена схема заявляемого ДУ в соответствии с п.2 формулы изобретения.

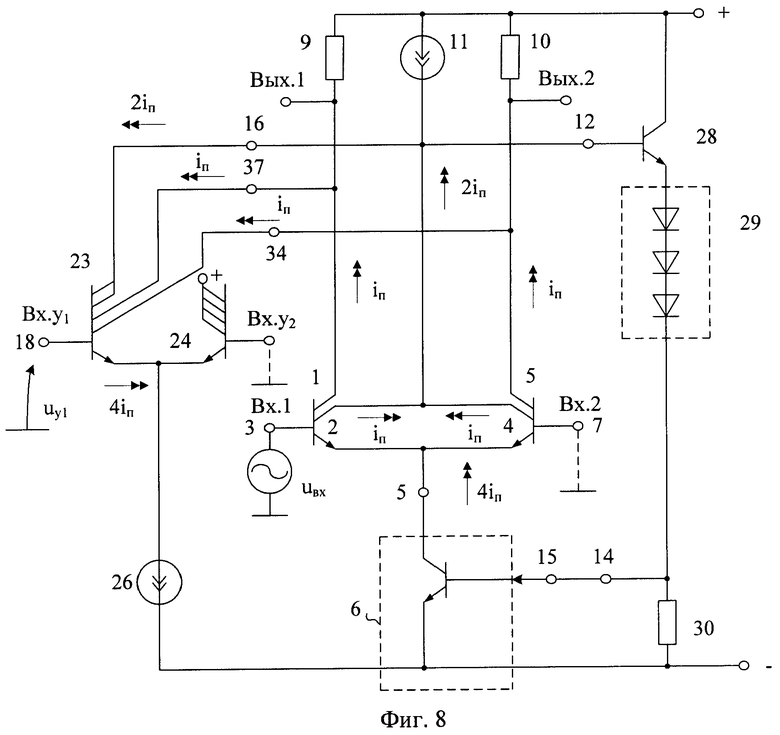

На фиг.8 представлен заявляемый ДУ, в котором преобразователь «напряжение-ток» 17 выполнен в соответствии с фиг.4 при сопротивлении резистора R25=0, а дополнительный усилитель тока реализован в соответствии с фиг.5.

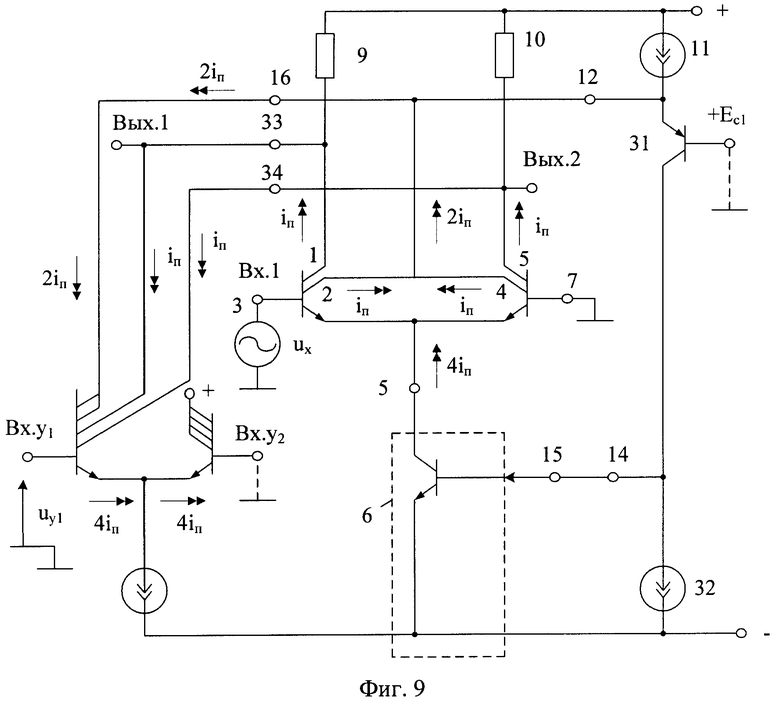

На фиг.9 представлен заявляемый ДУ, в котором преобразователь «напряжение-ток» 17 выполнен в соответствии с фиг.4 при сопротивлении резистора R25=0, а дополнительный усилитель тока реализован в соответствии с фиг.6.

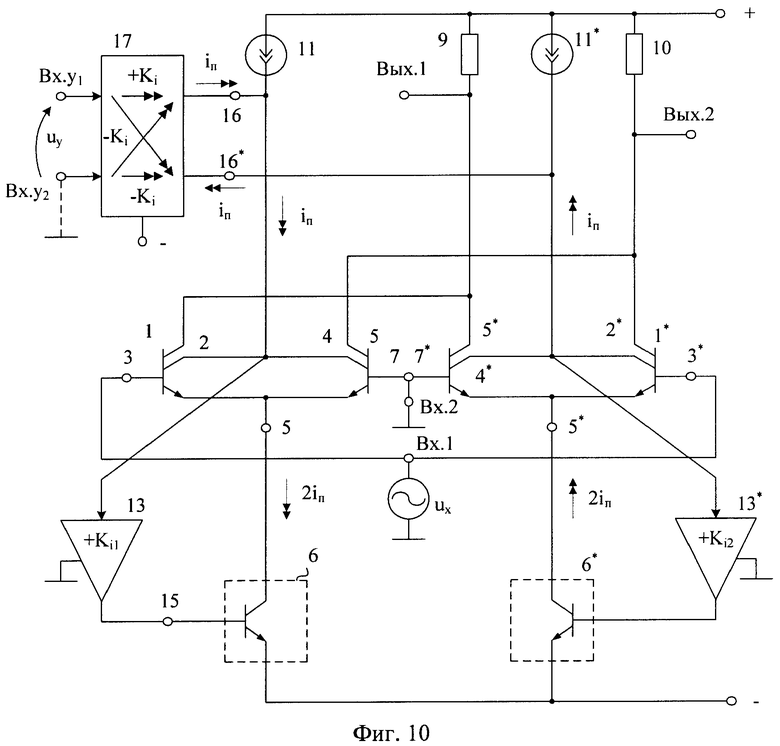

На фиг.10 показан пример построения аналогового перемножителя сигналов на базе заявляемого ДУ. Этот перемножитель содержит два идентичных ДУ фиг.2, который противофазно управляется преобразователем «напряжение-ток» 17.

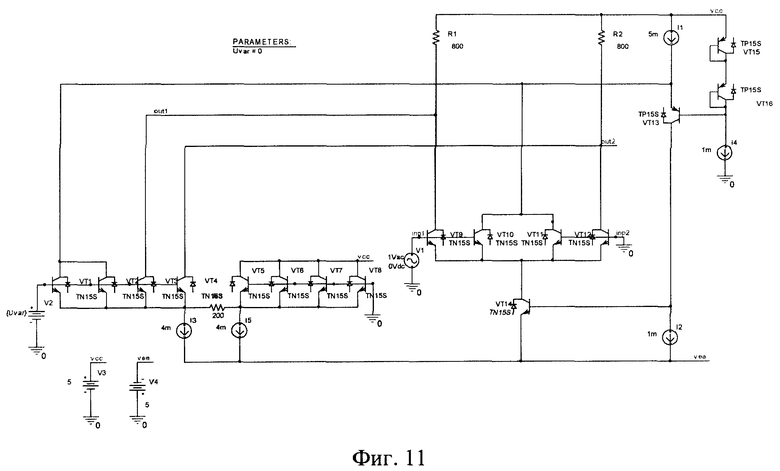

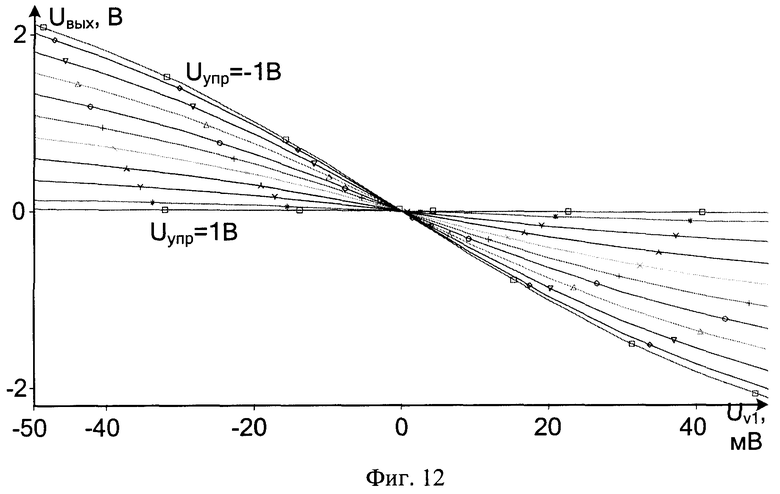

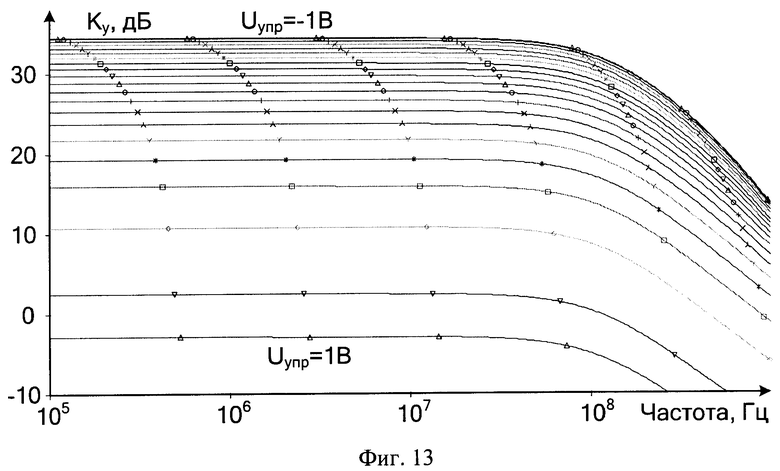

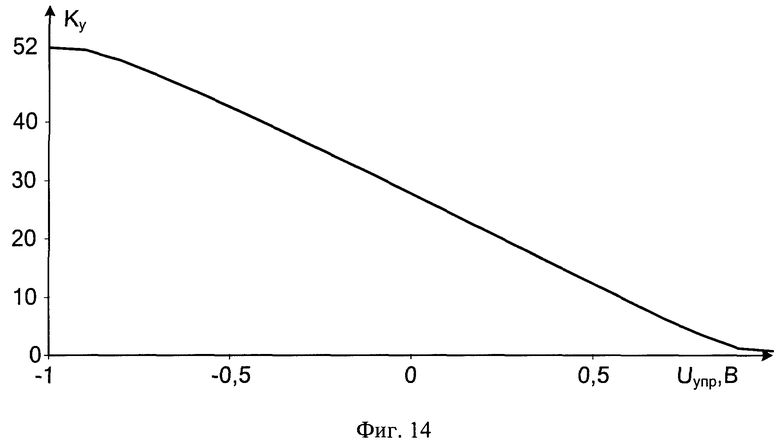

На фиг.11 представлена схема ДУ фиг.9 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Результаты ее компьютерного моделирования показаны на фиг.12-14:

- зависимость выходного напряжения Uвых от напряжения Ux=Uv1 при различных напряжениях управления (фиг.12);

- зависимость коэффициента усиления по напряжению Ку от частоты при разных напряжениях управления (фиг.13);

- зависимость коэффициента усиления по напряжению Ку от напряжения управления Uy=Uyпp..

Заявляемый дифференциальный усилитель (фиг.2) содержит первый 1 и второй 2 входные транзисторы с объединенными эмиттерами, базы которых соединены с первым 3 входом дифференциального усилителя, третий 4 и четвертый 5 входные транзисторы, эмиттеры которых соединены с эмиттерами первого 1 и второго 2 входных транзисторов и выходом 5 управляемого источника тока 6, а базы соединены со вторым 7 входом дифференциального усилителя, цепь нагрузки 8, связанную с коллекторами первого 1 и четвертого 5 входных транзисторов. В схему введен дополнительный двухполюсник 11, соединенный со входом 12 дополнительного усилителя тока 13 и коллекторами второго 2 и третьего 4 входных транзисторов, причем выход 14 дополнительного усилителя тока 13 подключен ко входу 15 управляемого источника тока 6, а основной выход 16 дополнительного преобразователя «напряжение-ток» 17 связан со входом 12 дополнительного усилителя тока 13.

В первом частном случае (фиг.3) преобразователь «напряжение-ток» 17 реализован на транзисторе 19 и двухполюсниках 20, 21, 22.

Во втором частном случае (фиг.4) преобразователь «напряжение-ток» 17 выполнен на транзисторах 23-24 и двухполюсниках 25-27. Представленный на фиг.5 вариант построения дополнительного усилителя тока 13 содержит транзистор 28, цепь согласования потенциалов 29 и двухполюсник 30. Другой вариант построения усилителя тока 13 (фиг.6) включает транзистор 31 и двухполюсник 32.

В схеме фиг.7, в соответствии с п.2 формулы изобретения, дополнительный преобразователь «напряжение-ток» 17 имеет основной выход 16, а также первый 33 и второй 34 вспомогательные выходы, причем первый 33 вспомогательный выход соединен с коллектором первого входного транзистора 1, а второй 34 вспомогательный выход подключен к коллектору четвертого 5 входного транзистора, причем коэффициент передачи по току преобразователя «напряжение-ток» 17 к основному выходу 16 в два раза больше коэффициента передачи по току к вспомогательным выходам 33 и 34.

Рассмотрим работу ДУ фиг.2.

В статическом режиме, когда uу=0, iн=0, сумма токов в узле «А» равняется нулю. Это обеспечивается отрицательной обратной связью по синфазному сигналу, которая вводится через дополнительный усилитель 13, на вход 15 управляемого источника опорного тока 6:

где I11 - ток дополнительного двухполюсника 11;

Iк2, Iк4 - коллекторные токи транзисторов 2 и 4;

Iп - выходной статический ток дополнительного преобразователя «напряжение-ток» 17;

I12 - входной ток дополнительного усилителя тока 13.

В частном случае может быть Iп=0, I12=0.

При этом дифференциальный коэффициент усиления по напряжению ДУ фиг.2 определяется отношением:

где Rн.экв - эквивалентное сопротивление, зависящее от сопротивлений нагрузки 9 и 10;

I05 - статический ток, протекающий в общей эмиттерной цепи 5;

φт≈25 мВ - температурный потенциал.

При изменении напряжения uу на выходе 16 преобразователя 17 его выходной ток получает следующее приращение

где S17 - крутизна преобразования  в выходной ток

в выходной ток  .

.

В результате в узле «А» в первый момент нарушается баланс токов (1). Однако, благодаря отрицательной обратной связи этот баланс снова устанавливается за счет изменения суммарного тока I05 в общей эмиттерной цепи 5. Так, если направления токов соответствуют фиг.2, то это приводит (для обеспечения баланса токов в узле «А») к увеличению тока i5 общей эмиттерной цепи 5 на величину  . В результате суммарный ток ДУ по эмиттерной цепи 5 увеличивается, что, в соответствии с (2), дает увеличение Ку (2).

. В результате суммарный ток ДУ по эмиттерной цепи 5 увеличивается, что, в соответствии с (2), дает увеличение Ку (2).

Если направления токов  изменяются на противоположные, то ток I05 уменьшается, что приводит к уменьшению Ку (2).

изменяются на противоположные, то ток I05 уменьшается, что приводит к уменьшению Ку (2).

Следует заметить, что благодаря новой архитектуре в ДУ фиг.2 статический потенциал точки подключения «А» преобразователя 17 оказывается выше потенциала общей 5 эмиттерной цепи ДУ. Это позволяет обеспечить работу ДУ при малых  , избежать двухъярусного включения транзисторов.

, избежать двухъярусного включения транзисторов.

В частном случае (фиг.7) возможно формирование трех синфазных токов  , пропорциональных

, пропорциональных  , что на практике (фиг.8) обеспечивается дифференциальным каскадом на транзисторах 23 и 24.

, что на практике (фиг.8) обеспечивается дифференциальным каскадом на транзисторах 23 и 24.

Другие варианты построения дополнительного усилителя 13 (фиг.6-8) практически не изменяют алгоритмы работы заявляемого ДУ, хотя и оказывают существенное влияние на параметры схемы.

Следует обратить внимание на следующие достоинства частных вариантов ДУ, показанных на фиг.8-9.

Схема фиг.8 реализована на однотипных биполярных транзисторах, что позволяет использовать для ее изготовления наиболее дешевый техпроцесс SGB25VD.

ДУ фиг.9 работоспособен при напряжениях питания ±1,5 В. Входное их и управляющее uу напряжения привязаны к общей шине питания, что также является существенным достоинством схемы.

Схема фиг.9, а также схема перемножителя на основе заявляемого ДУ фиг.10 реализуется по техпроцессу SGB25H2, а также техпроцессу SGB25VD при использовании полевых транзисторов в дополнительном усилителе 13.

Результаты компьютерного моделирования (фиг.12-14) показывают, что предлагаемый ДУ характеризуется более широким набором свойств и функций и может использоваться в различных устройствах РЭА с перестраиваемыми характеристиками.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4286226, фиг.5.

2. Патент США №6211718, фиг.3.

3. Патент AU №198065562 A1, H03F 3/45.

4. Патентная заявка США №2006/0232334, фиг.3.

5. Патент США №6229395, фиг.1.

6. Патент США №4306198, фиг.3

7. Патентная заявка США №2006/0132237, фиг.2.

8. Патент WO 2003/028210.

9. Патентная заявка США №2008/0136523, фиг.3.

10. Патент США №4331929.

11. Патент США №4227256.

12. Патент США №5256984.

13. Патент США №6753732.

14. Патентная заявка США №2005/0052239.

15. Патентная заявка США №2007/0090876.

16. Патент США №6374736 фиг.1.

17. Патент ЕР №1231709.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ СИГНАЛОВ НА ЕГО ОСНОВЕ | 2009 |

|

RU2390922C1 |

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2008 |

|

RU2384935C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388138C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2008 |

|

RU2375815C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2008 |

|

RU2390920C1 |

| ДВУХКАНАЛЬНЫЙ УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2009 |

|

RU2394364C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421883C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2008 |

|

RU2390919C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве широкополосного усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления (uу). Такие устройства применяются в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых перемножителей сигналов и т.д. Технический результат: уменьшение напряжения питания до уровня 1,5 В и повышение линейности характеристики управления. Дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входные транзисторы (Т) с объединенными эмиттерами, базы которых соединены с первым (3) входом ДУ, третий (4) и четвертый (5) входные Т, эмиттеры которых соединены с эмиттерами Т (1) и Т (2) и выходом (5) управляемого источника тока (УИТ) (6), а базы соединены со вторым (7) входом ДУ, цепь нагрузки (8), связанную с коллекторами Т (1) и Т (5). В схему введен дополнительный двухполюсник I11, соединенный со входом (12) дополнительного усилителя тока (УТ) (13) и коллекторами Т (2) и Т (4), причем выход (14) УТ (13) подключен ко входу (15) УИТ (6), а основной выход (16) дополнительного преобразователя «напряжение-ток» (17) связан со входом (12) УТ (13). 1 з.п. ф-лы, 14 ил.

1. Дифференциальный усилитель с управляемым коэффициентом усиления, содержащий первый (1) и второй (2) входные транзисторы с объединенными эмиттерами, базы которых соединены с первым (3) входом дифференциального усилителя, третий (4) и четвертый (5) входные транзисторы, эмиттеры которых соединены с эмиттерами первого (1) и второго (2) входных транзисторов и выходом (5) управляемого источника тока (6), а базы соединены со вторым (7) входом дифференциального усилителя, цепь нагрузки (8), связанную с коллекторами первого (1) и четвертого (5) входных транзисторов, отличающийся тем, что в схему введен дополнительный двухполюсник (I11), соединенный со входом (12) дополнительного усилителя тока (13) и коллекторами второго (2) и третьего (4) входных транзисторов, причем выход (14) дополнительного усилителя тока (13) подключен ко входу (15) управляемого источника тока (6), а основной выход (16) дополнительного преобразователя «напряжение-ток» (17) связан со входом (12) дополнительного усилителя тока (13).

2. Устройство по п.1, отличающееся тем, что дополнительный преобразователь «напряжение-ток» (17) имеет основной выход (16), а также первый (33) и второй (34) вспомогательные выходы, причем первый (33) вспомогательный выход соединен с коллектором первого входного транзистора (1), а второй (34) вспомогательный выход подключен к коллектору четвертого (5) входного транзистора, причем коэффициент передачи по току преобразователя «напряжение-ток» (17) к основному выходу (16) в два раза больше коэффициента передачи по току к вспомогательным выходам (33) и (34).

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| SU 1162018 A, 15.06.1985 | |||

| US 4286226 A, 25.08.1981 | |||

| WO 00/41298 A1, 13.07.2000. | |||

Авторы

Даты

2010-07-10—Публикация

2008-08-25—Подача