Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в качестве широкополосного усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления (uy). Такие устройства применяются в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых перемножителей сигналов и т.д.

В настоящее время в аналоговой микросхемотехнике в составе систем электронной регулировки усиления широкое применение находит дифференциальный усилитель с управляемым статическим режимом. Данная структура стала основой для построения многих известных в настоящее время управляемых усилителей и аналоговых перемножителей сигналов на базе дифференциальных каскадов [1-17].

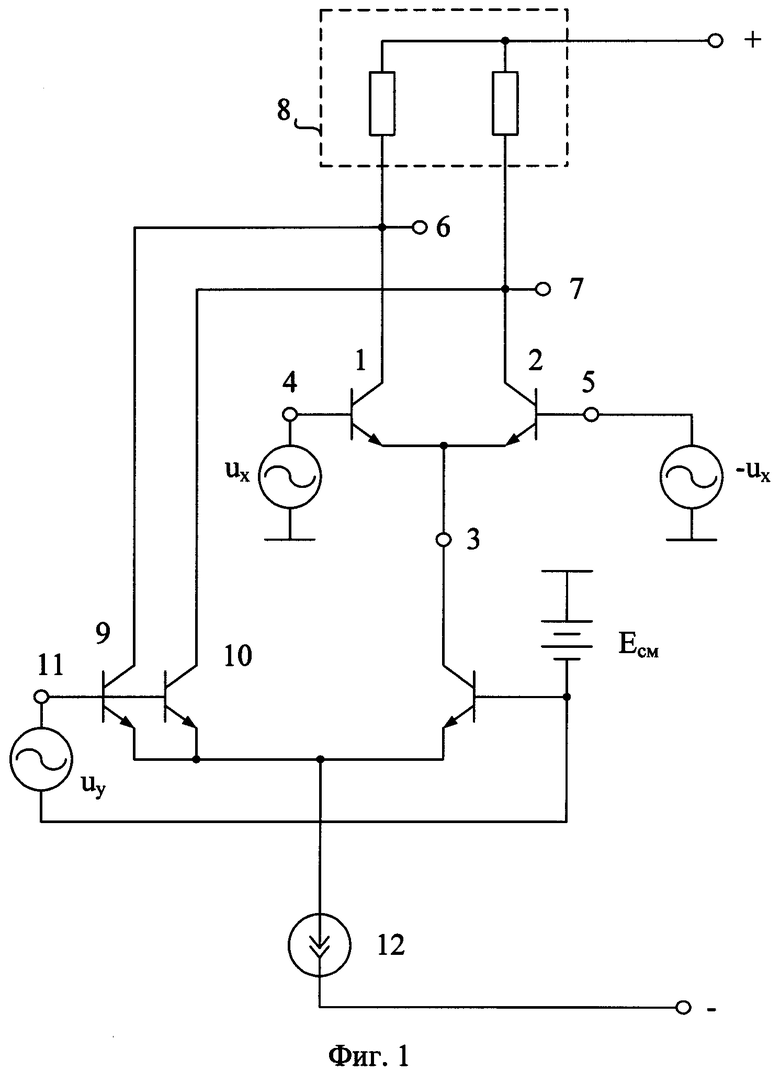

Ближайшим прототипом является дифференциальный усилитель (фиг.1), описанный в патенте США №4.286,226, фиг.5, содержащий первый 1 и второй 2 входные транзисторы параллельно-балансного каскада, эмиттеры которых соединены с токовым входом 3 параллельно-балансного каскада, базы соединены с соответствующими первым 4 и вторым 5 основными входами дифференциального усилителя, а коллекторы связаны с первым 6 и вторым 7 выходами дифференциального усилителя и цепью нагрузки 8, первый 9 и второй 10 транзисторы цепи управления усилением, базы которых подключены к управляющему входу 11 дифференциального усилителя, эмиттеры связаны с первым 12 источником опорного тока, а коллекторы связаны с первым 6 и вторым 7 выходами дифференциального усилителя.

Особенность схемы известного дифференциального усилителя фиг.1 состоит в том, что уровень его выходного статического напряжения не зависит от уровня сигнала управления uy, что делает его привлекательным для применения в схемах с непосредственной связью каскадов. Следует также отметить, что схема фиг.1 может выполнять функции перемножителей сигналов ux и uy.

В цифровых интегральных микросхемах результатом увеличения скорости обработки информации стали тенденции постоянного уменьшения напряжения питания, что является «анафемой» в аналоговом проектировании с высокими характеристиками. При технологических нормах 350 нм (3.3 В) по-прежнему достаточно схемотехнических возможностей для аналоговых проектировании с высокими характеристиками, хотя наличие 5 В питания было бы предпочтительнее. При нормах 180 нм (1.8 В) процесс усложняется и статические характеристики аналоговых устройств страдают. В этой связи необходимо развитие новых подходов к проектированию микросхем, ориентированных на снижение мощности, улучшение производительности при низковольтном питании.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии SGB25VD, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы Х диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технология SGB25VD накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы (Uкэ.max=2,9÷3,0 В).

Создание IP блоков для SiGe технологии SGB25VD является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем.

Существуют схемотехнические методы, позволяющие использовать однотипные транзисторы с относительно низким напряжением их питания в структуре не только различных узлов и устройств, но и СФ блоков систем на кристалле. Этот важнейший для указанной проблемы теоретический результат позволяет в перспективе расширить область практического использования SGB25VD SiGe технологии и, следовательно, повысить технико-экономические показатели микроэлектронных изделий. Так, например, создание новой под указанную технологию схемотехники управляемых усилителей и аналоговых перемножителей позволит не только повысить качественные показатели СВЧ фильтров, квадратурных модуляторов и демодуляторов и других устройств нового поколения, образующих СФ блоки СВЧ РЭА специального назначения, так и создать принципиально новую номенклатуру ИС более широкого функционального применения.

Последние несколько лет источники питания с напряжением 5 В вытесняются более низковольтными. Требования к уменьшению рассеиваемой мощности и уменьшению числа батарей в таких приложениях, как беспроводные устройства связи и персональные компьютеры, привели к снижению напряжения питания в цифровых схемах до уровня 1,5 В. Эта тенденция, как отмечалось выше, реализована в современных SiGe транзисторах, которые сконструированы так, чтобы обеспечить максимальную частоту среза (f1) в компромиссе с напряжением пробоя (Uпp). Для кремниевых транзисторов существует следующее фундаментальное ограничение: f1×Uпр≈const.

Таким образом, малые размеры транзисторов, обеспечивающие высокие значения f1 (до 200 ГТц), привели к снижению напряжения питания микросхем до 1,2÷1,5 В.

Уменьшение напряжения питания (Еп) в биполярных схемах приводит к появлению новых проблем и некоторые из них становятся особенно важными при напряжении питания менее 2 В. Принципиальная сложность уменьшения напряжения Еп состоит в том, что биполярный транзистор имеет фиксированное напряжение база-эмиттер Uбэ, которое не уменьшается линейно с уменьшением технологических норм, так как

где φт=kT/q, Iк - ток коллектора и Is - обратный ток эмиттерного р-n перехода. При этом параметры транзистора и уровни тока оказывают слабое влияние на напряжение Uбэ. На практике плотность тока в биполярном транзисторе (Iк/Is), изменяя свое значение, также слабо влияет на напряжение Uбэ. Если в используемой технологии Uбэ=0,7÷0,8 В, то использование 1,5 В источника питания приводит к тому, что между «землей» и шиной Еп не может быть включено больше, чем один переход база-эмиттер.

Учитывая вышесказанное, а также численные значения напряжения Uбэ≈700÷800 мВ, можно сделать вывод о том, что запрещается использовать многоярусные дифференциальные пары или каскодные конфигурации (архитектуры) при напряжении питания 1,5 В.

Таким образом, отсутствие возможности масштабирования напряжения на переходе база-эмиттер еще больше обостряет проблему дальнейшего масштабирования напряжения питания схем на биполярных транзисторах.

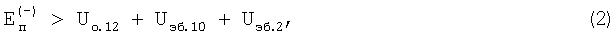

Существенный недостаток известного устройства фиг.1 состоит в том, что оно оказывается работоспособным только при сравнительно больших уровнях напряжения питания (±Еп>2,2÷2,4 В). Это связано с особенностями архитектуры известного ДУ, которая имеет «двухярусную» структуру. Схема фиг.1 оказывается неработоспособной при напряжениях  , меньших 1,5 В, так как здесь должно быть

, меньших 1,5 В, так как здесь должно быть

где Uo.12 - минимальное напряжение на источнике тока 12;

Uэб≈0,7÷0,8 В - напряжения эмиттер-база транзисторов 2 и 10 в активном режиме.

При типовом построении двухполюсника 12 численные значения

Uo.12≈0,7 В. Таким образом, в известном ДУ  . Кроме этого, в известном ДУ достаточно трудно обеспечить высокую линейность характеристики управления в широком диапазоне изменения uy.

. Кроме этого, в известном ДУ достаточно трудно обеспечить высокую линейность характеристики управления в широком диапазоне изменения uy.

Основная цель предлагаемого изобретения состоит в уменьшении напряжения питания дифференциального усилителя с управляемым коэффициентом усиления до уровня 1,5 В.

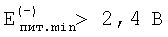

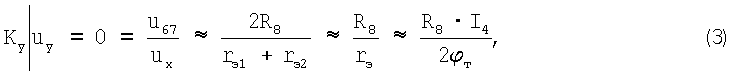

Дополнительная цель - повышение линейности характеристики управления ДУ без потери его базового свойства - способности работать при

.

.

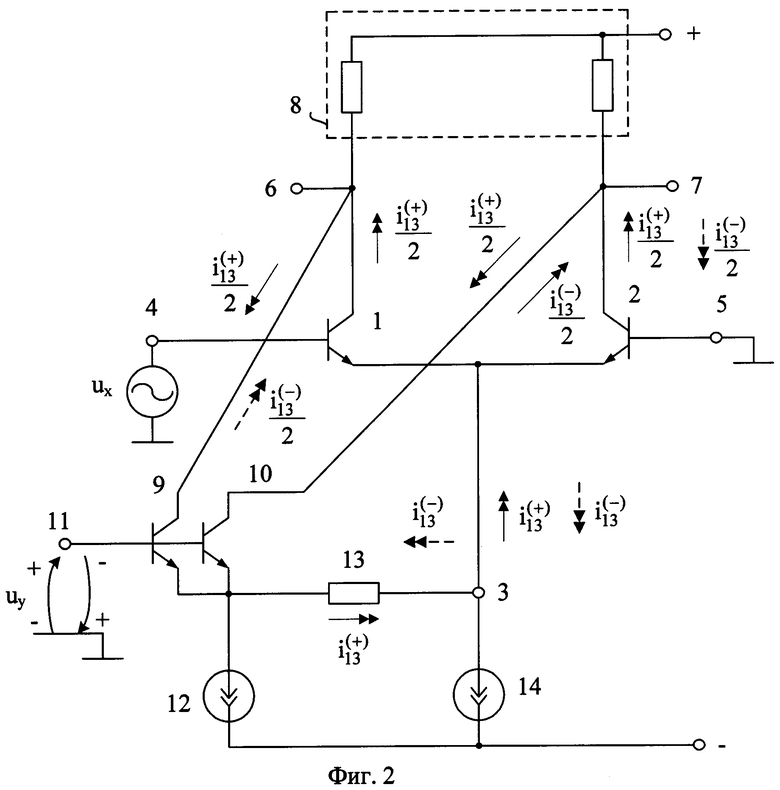

Поставленная цель достигается тем, что в ДУ, содержащем первый 1 и второй 2 входные транзисторы параллельно-балансного каскада, эмиттеры которых соединены с токовым входом 3 параллельно-балансного каскада, базы соединены с соответствующими первым 4 и вторым 5 основными входами дифференциального усилителя, а коллекторы связаны с первым 6 и вторым 7 выходами дифференциального усилителя и цепью нагрузки 8, первый 9 и второй 10 транзисторы цепи управления усилением, базы которых подключены к управляющему входу 11 дифференциального усилителя, эмиттеры связаны с первым 12 источником опорного тока, а коллекторы связаны с первым 6 и вторым 7 выходами дифференциального усилителя, предусмотрены новые элементы и связи - в схему введены дополнительный резистор 13 и дополнительный источник опорного тока 14, причем дополнительный резистор 13 включен между объединенными эмиттерами первого 9 и второго 10 транзисторов цепи управления усилением и токовым входом 3 параллельно-балансного каскада, к которому подключен дополнительный источник опорного тока 14.

На фиг.1 показана схема ДУ-прототипа, на фиг.2 - схема заявляемого ДУ в соответствии с формулой изобретения.

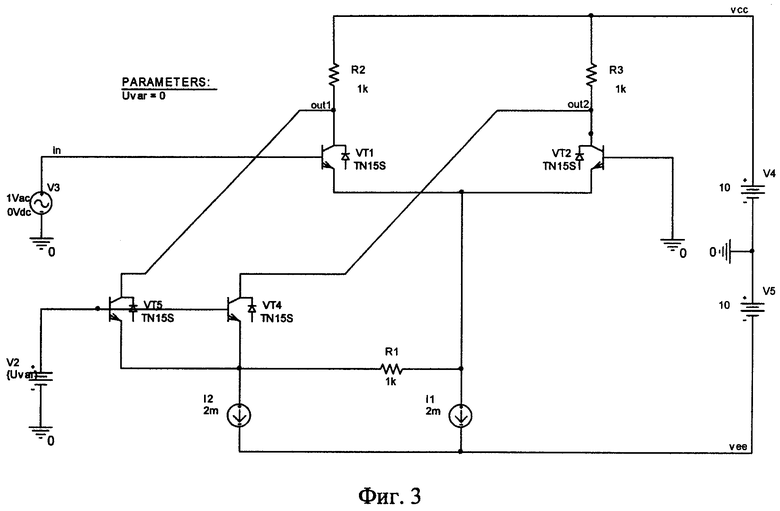

На фиг.3 представлена схема ДУ фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

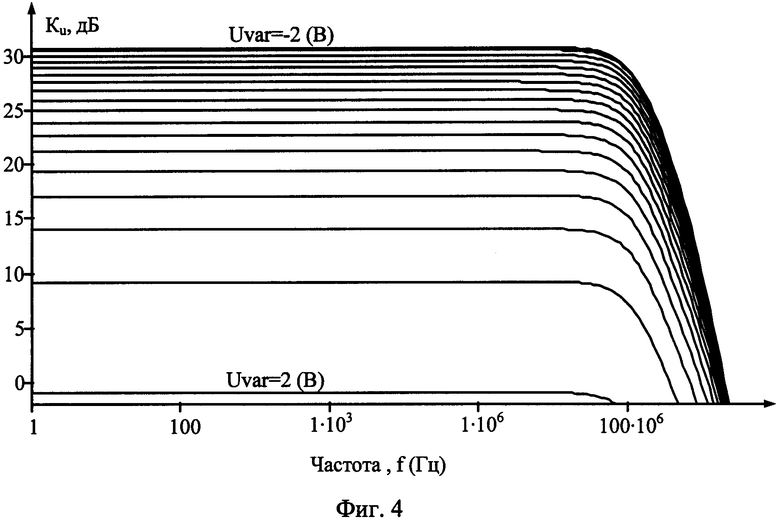

Амплитудно-частотная характеристика коэффициента усиления по напряжению Кu ДУ фиг.2 при разных значениях uY=Uvar показана на фиг.4.

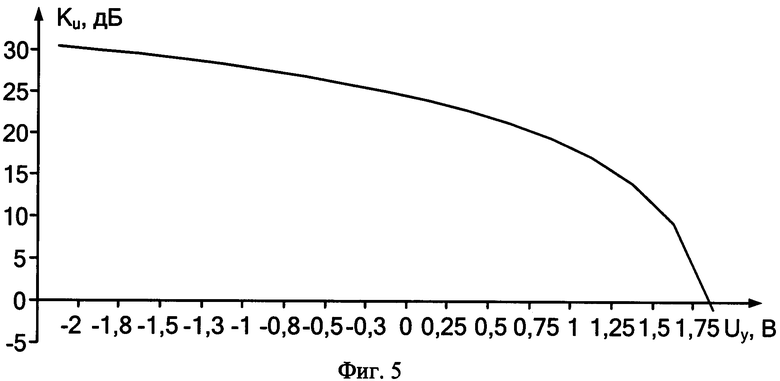

Регулированная характеристика ДУ фиг.2 представлена на фиг.5.

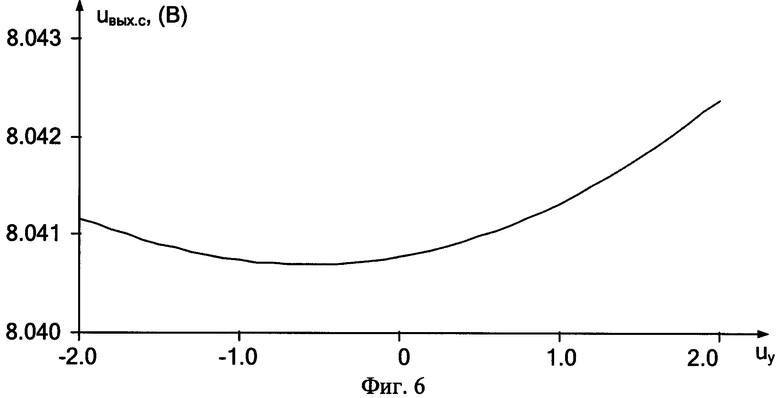

Зависимость уровня выходного синфазного статического напряжения ДУ фиг.2 (uвых.с) приведена на фиг.6.

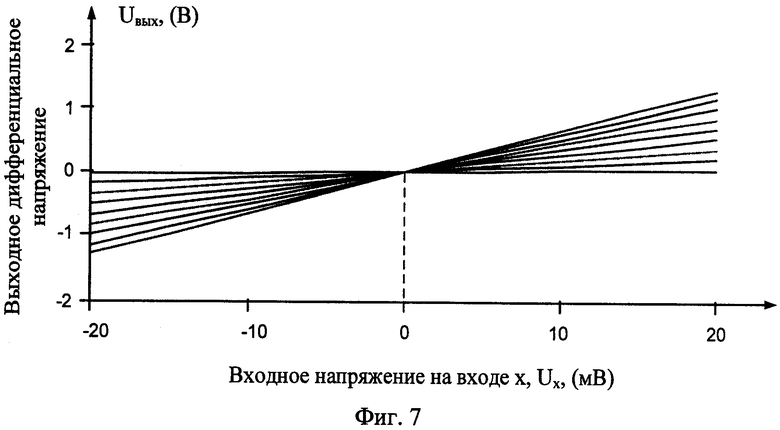

На фиг.7 показана зависимость выходного дифференциального напряжения Uвых ДУ фиг.2 от напряжения на входе канала «х» Ux при различных напряжениях uy на управляющем входе 11.

Заявляемый дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы параллельно-балансного каскада, эмиттеры которых соединены с токовым входом 3 параллельно-балансного каскада, базы соединены с соответствующими первым 4 и вторым 5 основными входами дифференциального усилителя, а коллекторы связаны с первым 6 и вторым 7 выходами дифференциального усилителя и цепью нагрузки 8, первый 9 и второй 10 транзисторы цепи управления усилением, базы которых подключены к управляющему входу 11 дифференциального усилителя, эмиттеры связаны с первым 12 источником опорного тока, а коллекторы связаны с первым 6 и вторым 7 выходами дифференциального усилителя. В схему введены дополнительный резистор 13 и дополнительный источник опорного тока 14, причем дополнительный резистор 13 включен между объединенными эмиттерами первого 9 и второго 10 транзисторов цепи управления усилением и токовым входом 3 параллельно-балансного каскада, к которому подключен дополнительный источник опорного тока 14.

Заявляемый ДУ работает следующим образом.

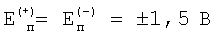

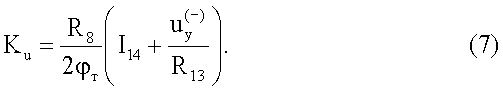

В статическом режиме при нулевом напряжении (uy=0) на управляемом входе 11 резистор 13 не влияет на работу схемы, так как напряжения на его правом и левом выводах практически одинаковы. Ток источника опорного тока 14 делится пополам между эмиттерами транзисторов 1 и 2 и определяет коэффициент усиления по напряжению со входа 4 на дифференциальный выход 6-7:

где u67 - приращение напряжения между выходными узлами 6 и 7;

ux - приращение напряжения на входе 4;

R8 - сопротивление левого (правого) резисторов цепи нагрузки 8;

φт≈25 мВ - температурный потенциал;

I14 - ток двухполюсника 14.

Если uy получает положительное приращение относительно общей шины, то это создает приращение тока через резистор 13

где R13 - сопротивление резистора 13.

Как следствие, суммарный ток I0Σ общей эмиттерной цепи ДУ уменьшается

Это приводит к уменьшению коэффициента усиления по напряжению Кu:

Если uy<0, то суммарный ток общей эмиттерной цепи ДУ увеличивается и Кu растет:

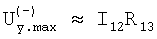

Предельное значение Кu достигает при  :

:

где I12 - ток двухполюсника 12.

С другой стороны, ток  делится пополам между эмиттерами транзисторов 9 и 10 и передается на выходы 6 и 7. При этом данное приращение тока

делится пополам между эмиттерами транзисторов 9 и 10 и передается на выходы 6 и 7. При этом данное приращение тока  компенсирует в нагрузке 8 приращение токов

компенсирует в нагрузке 8 приращение токов

коллектора транзисторов 1 и 2. Как следствие, выходное синфазное напряжение ДУ фиг.2 не зависит от уровня сигнала управления uy (фиг.6).

Фиг.4 показывает, что при R13=1 кОм коэффициент усиления Кu заявляемого ДУ изменяется более чем на 35 дБ. Если выбрать R11=100 Ом, то диапазон изменения uy, при котором Ku изменяется на 35 дБ, сужается до 200 мВ.

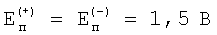

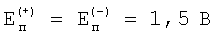

Замечательная особенность заявляемого ДУ - возможность работы при  . Действительно при типовом построении источников опорного тока 12 и 14 (на биполярных транзисторах) активный статический режим всех транзисторов ДУ фиг.2 реализуется при

. Действительно при типовом построении источников опорного тока 12 и 14 (на биполярных транзисторах) активный статический режим всех транзисторов ДУ фиг.2 реализуется при  . В ДУ-прототипе это невозможно. Таким образом, заявляемый ДУ характеризуется более высокими качественными показателями при низковольтном питании.

. В ДУ-прототипе это невозможно. Таким образом, заявляемый ДУ характеризуется более высокими качественными показателями при низковольтном питании.

Источники информации

1. Патент США №4.286.226, фиг.5.

2. Патент США №6.211.718, фиг.3.

3. Патент AU №198065562 A1, H03F 3/45.

4. Патентная заявка США №2006/0232334, фиг.3.

5. Патент США №6.229.395, фиг.1.

6. Патент США №4.306.198, фиг.3.

7. Патентная заявка США №2006/0132237, фиг.2.

8. Патент WO 2003/028210.

9. Патентная заявка США №2008/0136523, фиг.3.

10. Патент США №4.331.929.

11. Патент США №4.227.256.

12. Патент США №5.256.984.

13. Патент США №6.753.732.

14. Патентная заявка США №2005/0052239.

15. Патентная заявка США №2007/0090876.

16. Патент США №6.374.736, фиг.1.

17. Патент ЕР №1.231.709.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2383053C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388137C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2007 |

|

RU2364020C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2008 |

|

RU2368067C1 |

| УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2380824C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2008 |

|

RU2394359C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346386C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве широкополосного усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления uy, например, в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых перемножителей сигналов и т.д. Технический результат: уменьшение напряжения питания и повышение линейности характеристики управления усилением. Дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входные транзисторы (Т) параллельно-балансного каскада, эмиттеры которых соединены с токовым входом (3) параллельно-балансного каскада, базы соединены с соответствующими первым (4) и вторым (5) основными входами ДУ, а коллекторы связаны с первым (6) и вторым (7) выходами ДУ и цепью нагрузки (8), первый (9) и второй (10) Т цепи управления усилением (ЦУУ), базы которых подключены к управляющему входу (11) ДУ, эмиттеры связаны с первым (12) источником опорного тока (ИОТ), а коллекторы связаны с первым (6) и вторым (7) выходами ДУ. В схему введены дополнительный резистор (13) и дополнительный ИОТ (14), причем дополнительный резистор (13) включен между объединенными эмиттерами первого (9) и второго (10) Т ЦУУ и токовым входом (3) параллельно-балансного каскада, к которому подключен дополнительный ИОТ (14). 7 ил.

Дифференциальный усилитель с управляемым коэффициентом усиления, содержащий первый (1) и второй (2) входные транзисторы параллельно-балансного каскада, эмиттеры которых соединены с токовым входом (3) параллельно-балансного каскада, базы соединены с соответствующими первым (4) и вторым (5) основными входами дифференциального усилителя, а коллекторы связаны с первым (6) и вторым (7) выходами дифференциального усилителя и цепью нагрузки (8), первый (9) и второй (10) транзисторы цепи управления усилением, базы которых подключены к управляющему входу (11) дифференциального усилителя, эмиттеры связаны с первым (12) источником опорного тока, а коллекторы связаны с первым (6) и вторым (7) выходами дифференциального усилителя, отличающийся тем, что в схему введены дополнительный резистор (13) и дополнительный источник опорного тока (14), причем дополнительный резистор (13) включен между объединенными эмиттерами первого (9) и второго (10) транзисторов цепи управления усилением и токовым входом (3) параллельно-балансного каскада, к которому подключен дополнительный источник опорного тока (14).

| US 4286226, 25.08.1981 | |||

| Дифференциальный усилитель с регулируемым коэффициентом усиления | 1990 |

|

SU1748227A1 |

| US 4621238 A, 04.11.1986 | |||

| ЛИНЕЙНЫЙ ЭЛЕКТРОДВИГАТЕЛЬ | 1995 |

|

RU2108651C1 |

Авторы

Даты

2010-03-20—Публикация

2008-07-29—Подача