Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного усилителя мощности аналоговых микросхем различного функционального назначения (например, прецизионных повторителях сигналов, драйверов линий связи и т.п.).

В современной радиоэлектронной аппаратуре находят широкое применение буферные усилители (БУ) на основе р-n-р и n-р-n транзисторов - так называемые «бриллиантовые» транзисторы, которые выпускаются ведущими микроэлектронными фирмами как в виде самостоятельных микросхем (BUF1, BUF600, LMH6321 и др.), так и в составе мостовых входных и двухтактных выходных каскадов различных аналоговых устройств [1-46].

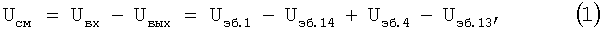

Ближайшим прототипом заявляемого устройства является классический буферный усилитель (фиг.1), представленный в патенте США фирмы Analog Devices №5.323.122, fig.2. Он содержит первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы, эмиттеры которых связаны с выходом 6 устройства, первый 7 токостабилизирующий двухполюсник, подключенный к базе первого 4 выходного транзистора, второй 8 токостабилизирующий двухполюсник, подключенный к базе второго 5 выходного транзистора.

Существенный недостаток известного БУ состоит в том, что он характеризуется сравнительно большим напряжением смещения нуля (Uсм).

Основная цель предлагаемого изобретения состоит в уменьшении напряжения смещения нуля буферного усилителя и его температурной и/или радиационной зависимости.

Поставленная цель достигается тем, что в буферном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы, эмиттеры которых связаны с выходом 6 устройства, первый 7 токостабилизирующий двухполюсник, подключенный к базе первого 4 выходного транзистора, второй 8 токостабилизирующий двухполюсник, подключенный к базе второго 5 выходного транзистора, предусмотрены новые элементы и связи - эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора через первую 9 цепь смещения потенциала и подключен к первому 10 дополнительному токостабилизирующему двухполюснику, эмиттер второго 2 входного транзистора соединен с базой второго 5 выходного транзистора через вторую 11 цепь смещения потенциала и подключен ко второму 12 дополнительному токостабилизирующему двухполюснику.

На фиг.1 показана схема БУ-прототипа.

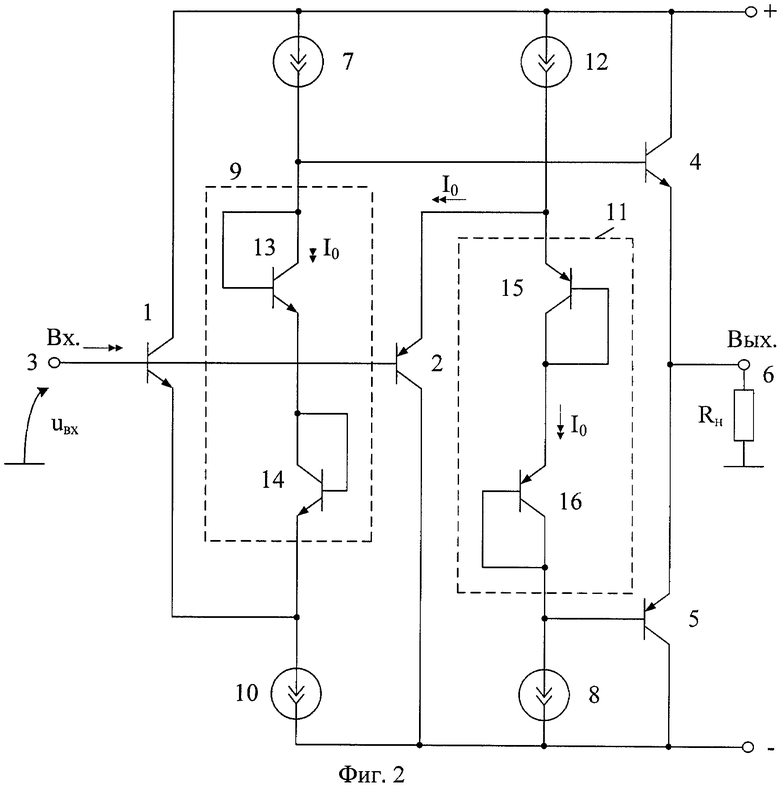

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

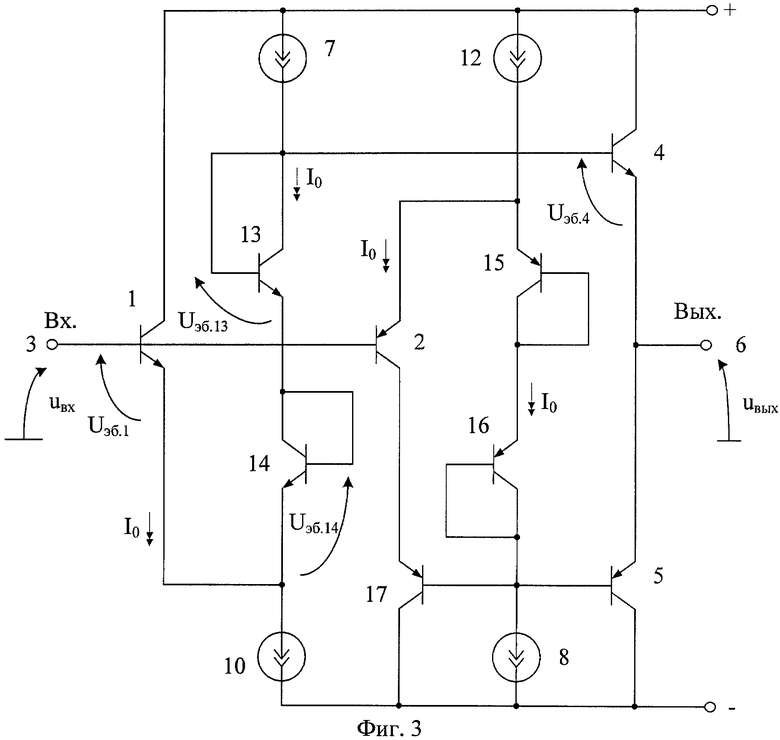

На фиг.3 приведена схема предлагаемого БУ в соответствии с п.3 формулы изобретения.

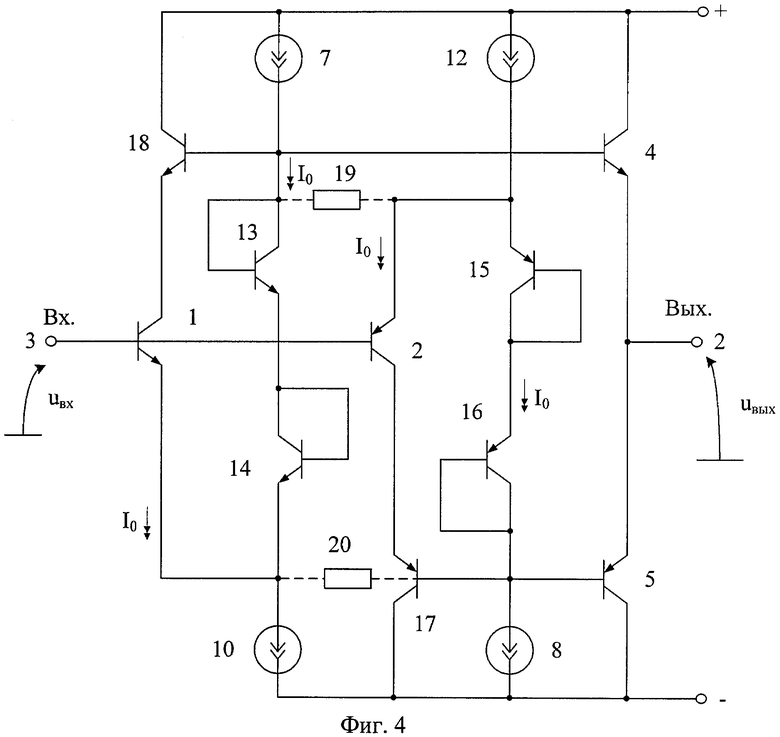

Фиг.4 соответствует п.4 и п.3 формулы изобретения.

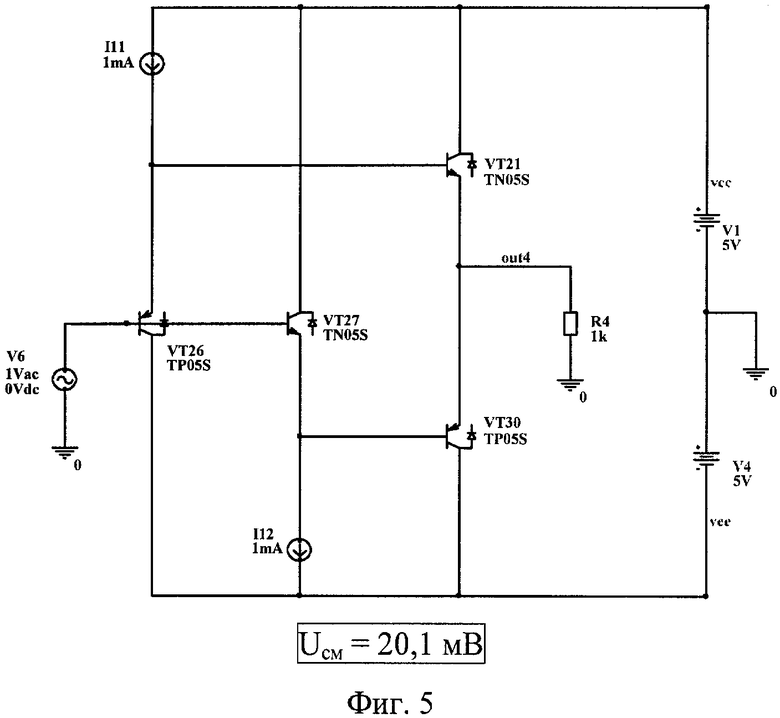

На фиг.5 приведена схема БУ-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

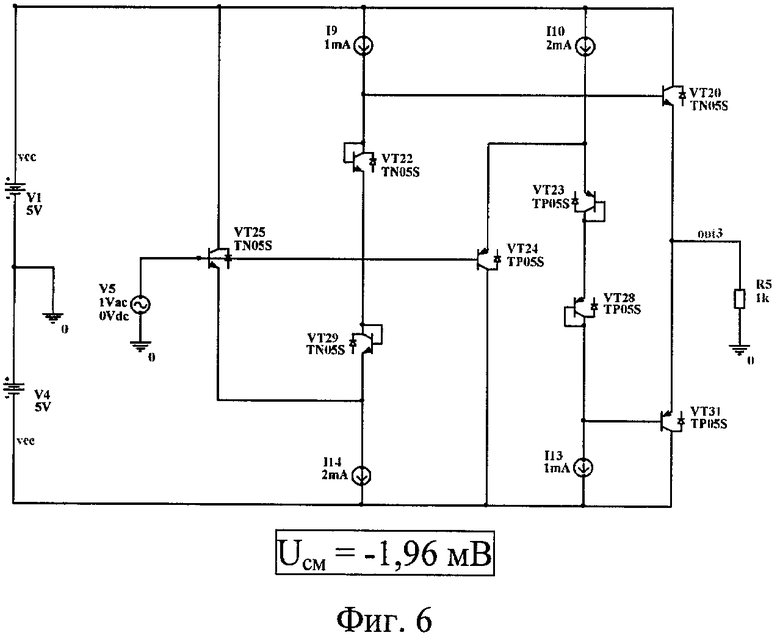

На фиг.6 приведена схема заявляемого устройства фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

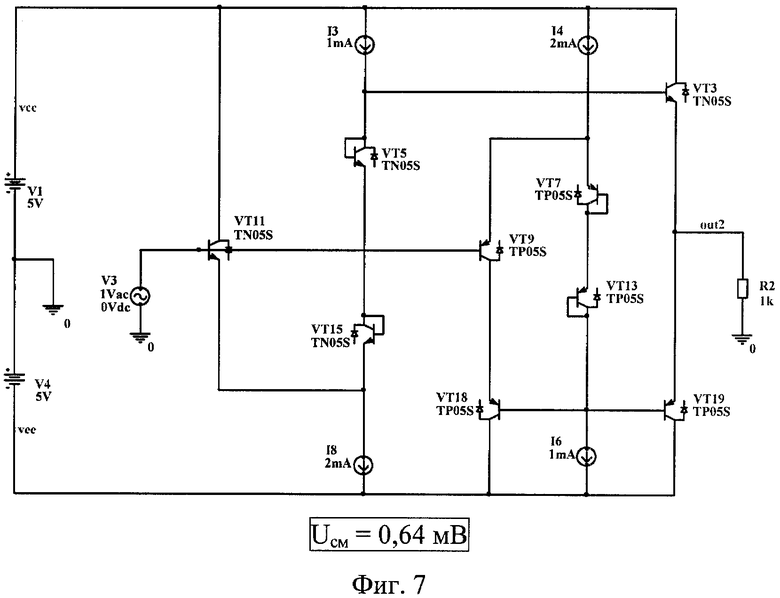

На фиг.7 приведена схема заявляемого БУ, соответствующего п.3 формулы изобретения, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

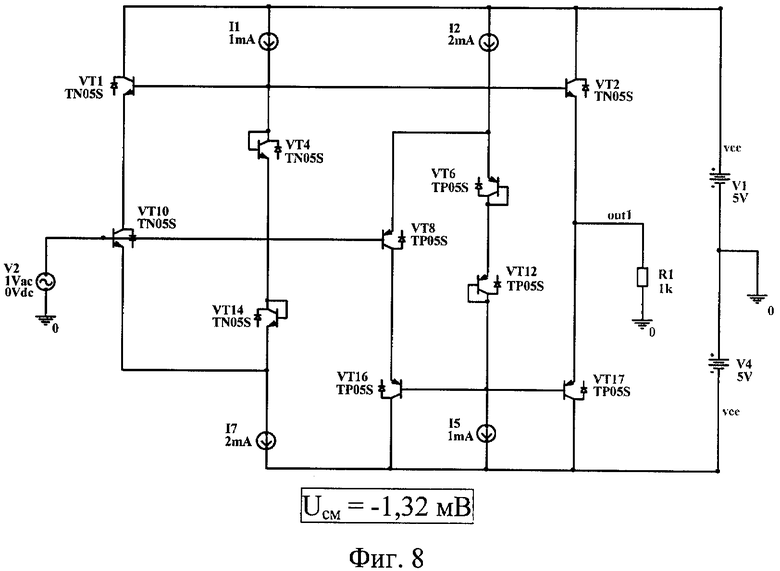

На фиг.8 приведена схема фиг.4 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

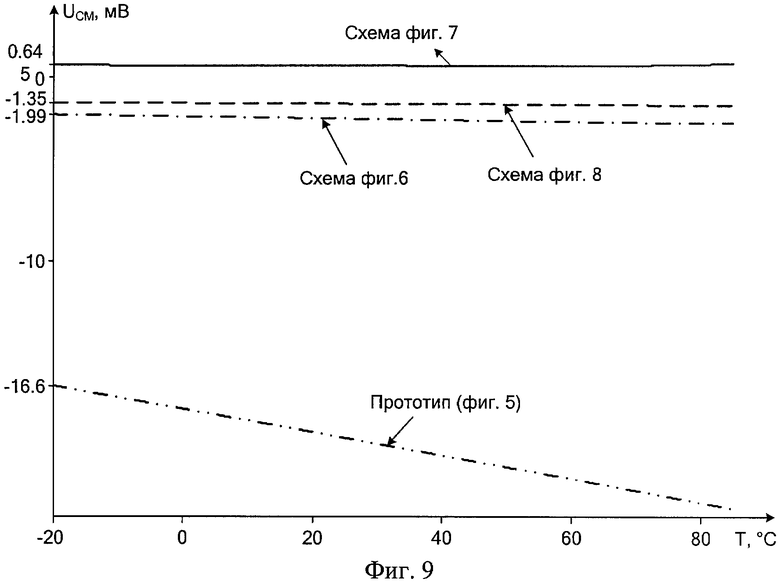

На фиг.9 показаны температурные зависимости напряжения смещения нуля буферных усилителей фиг.5, фиг.6, фиг.7 и фиг.8, которые показывают, что в сравнении с БУ-прототипом (фиг.5) предлагаемый подкласс БУ (фиг.6, фиг.7, фиг.8) характеризуется более чем на порядок меньшими абсолютными значениями напряжения смещения нуля, а также его температурного дрейфа.

Буферный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы, эмиттеры которых связаны с выходом 6 устройства, первый 7 токостабилизирующий двухполюсник, подключенный к базе первого 4 выходного транзистора, второй 8 токостабилизирующий двухполюсник, подключенный к базе второго 5 выходного транзистора. Эмиттер первого 1 входного транзистора соединен с базой первого 4 выходного транзистора через первую 9 цепь смещения потенциала и подключен к первому 10 дополнительному токостабилизирующему двухполюснику, эмиттер второго 2 входного транзистора соединен с базой второго 5 выходного транзистора через вторую 11 цепь смещения потенциала и подключен ко второму 12 дополнительному токостабилизирующему двухполюснику.

На фиг.2 в соответствии с п.2 формулы изобретения первая 9 и вторая 10 цепи смещения потенциалов выполнены в виде двух последовательно соединенных р-n переходов 13, 14 и 15, 16.

На фиг.3 в соответствии с п.3 формулы изобретения в схему введен первый 17 дополнительный транзистор, база которого подключена к базе второго 5 выходного транзистора, а эмиттер подключен к коллектору второго 2 входного транзистора.

На фиг.4 в соответствии с п.4 формулы изобретения в схему введен второй 18 дополнительный транзистор, база которого подключена к базе первого 4 выходного транзистора, а эмиттер подключен к коллектору первого 1 входного транзистора.

В частном случае для повышения быстродействия БУ, зависящего от скорости перезаряда паразитных емкостей, в предлагаемых схемах (фиг.2-4) могут вводиться двухполюсники 19 и 20 (фиг.4).

Рассмотрим работу заявляемого устройства фиг.3 на постоянном токе.

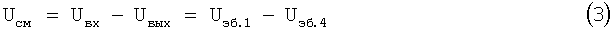

На основании второго закона Кирхгофа можно составить следующую систему уравнений, связывающую входные и выходные напряжения:

где Uсм - напряжение смещения нуля БУ;

Uэб.i - напряжение эмиттер-база i-го транзистора.

При этом без учета внутренней обратной связи в транзисторах

где φт≈26 мВ - температурный потенциал;

Iэ.i - статический ток эмиттера i-го транзистора;

Iэо.i - обратный ток эмиттерного перехода i-го транзистора.

Так как эмиттерные переходы n-р-n транзисторов одинаковы, то при одинаковых обратных токах Iэо одинаковых транзисторов 1, 4, 13 и 14 напряжение смещения нуля будет близко к нулю.

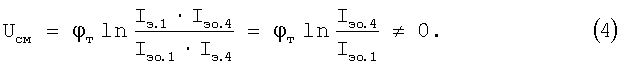

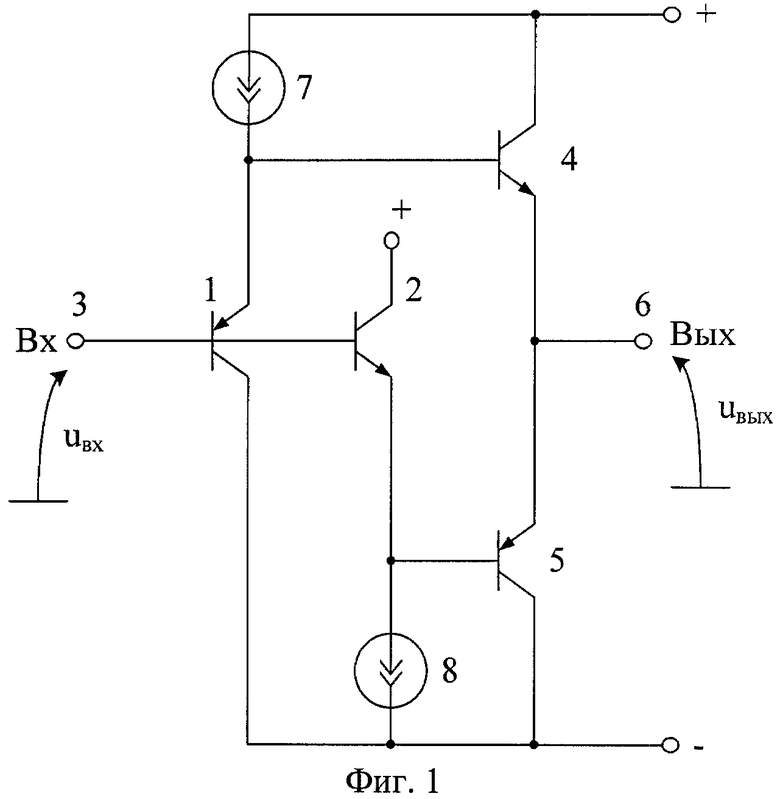

В БУ-прототипе фиг.1 напряжение смещения нуля определяется двумя n-р-n и р-n-р транзисторами, которые в силу технологических проблем имеют разные обратные токи:

или с учетом (2)

В связи с тем, что обратные токи р-n-р и n-р-n транзисторов всегда отличаются, схеме фиг.1 всегда присущи более высокие значения Uсм, на практике это 15÷20 мВ.

Данные теоретические выводы подтверждаются результатами компьютерного моделирования схем фиг.5, фиг.6 и фиг.7 - заявляемый БУ имеет более чем на порядок меньшее напряжение смещения нуля.

В схемах фиг.3, фиг.4 за счет введения транзисторов 17 и 18 уменьшается входная проводимость, а также влияние эффекта Эрли на Uсм.

Предлагаемые схемы эффективны и при радиационном воздействии на полупроводниковые элементы, которое выражается в деградации Uэб транзисторов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6.181.204 fig.2

2. Патент ЕР 0318811

3. Патентная заявка Японии JP 2000/183666

4. Патентная заявка Японии JP 2000/106508

5. Патент Японии JP 6204759

6. Патент Японии JP 6310950

7. Патент Японии JP 11167368

8. Патент Японии JP 10163763

9. Патент Японии JP 10065457

10. Патент Японии JP 10022747

11. Патент США №6.281.752

12. Патент США №6.215.357

13. Патент США №5.512.859

14. Патент США №5.515.007

15. Патент США №5.568.090

16. Патент США №5.907.262

17. Патент США №4.160.216

18. Патент США №6.710.654

19. Патент США №6.160.451

20. Патент США №6.268.769

21. Патент США №6.501.334

22. Патент США №5.144.259

23. Патент США №5.327.095

24. Патент США №5.357.211

25. Патент США №5.479.133

26. Патент США №6.492.870

27. Патент США №4.791.383

28. Патент США №4.833.424

29. Патент США №5.179.355

30. Патент США №5.323.122

31. Патент США №5.557.238

32. Патент США №5.623.230

33. Патент РФ №2193273

34. Патент Японии JP 10270954

35. Патент США №5.374.897

36. Патент США №4.837.523

37. Патент США №6.542.032

38. Патент Японии JP 11251846

39. Патент РФ №2168263

40. Патент РФ №1160530

41. Патент РФ №1506512

42. Патент РФ №1007185

43. Патент США №6.535.063

44. Патент США №5.378.938

45. Патент ЕР 0786858

46. Патент США №5.515.007

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416153C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416155C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416151C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2009 |

|

RU2416154C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412537C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412532C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416152C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412534C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве буферного усилителя аналоговых микросхем различного функционального назначения (например, прецизионных повторителях сигналов, драйверов линий связи и т.п.). Технический результат: уменьшение напряжения смещения нуля и температурной и/или радиационной зависимости. Буферный усилитель (БУ) содержит первый (1) и второй (2) входные транзисторы (Т), базы которых подключены ко входу (3) БУ, первый (4) и второй (5) выходные Т, эмиттеры которых связаны с выходом (6) БУ, первый (7) токостабилизирующий двухполюсник (ТД), подключенный к базе первого (4) выходного Т, второй (8) ТД, подключенный к базе второго (5) выходного Т. Эмиттер первого (1) входного Т соединен с базой первого (4) выходного Т через первую (9) цепь смещения потенциала и подключен к первому (10) дополнительному ТД, эмиттер второго (2) входного Т соединен с базой второго (5) выходного Т через вторую (11) цепь смещения потенциала и подключен ко второму (12) дополнительному ТД. 3 з.п. ф-лы, 9 ил.

1. Буферный усилитель с малым напряжением смещения нуля, содержащий первый n-р-n (1) и второй (2) входные транзисторы, базы которых подключены ко входу устройства (3), первый n-р-n (4) и второй (5) выходные транзисторы, эмиттеры которых связаны с выходом (6) устройства, первый (7) токостабилизирующий двухполюсник, подключенный к базе первого n-р-n (4) выходного транзистора, второй (8) токостабилизирующий двухполюсник, подключенный к базе второго (5) выходного транзистора, отличающийся тем, что эмиттер первого n-р-n (1) входного транзистора соединен с базой первого n-р-n (4) выходного транзистора через первую (9) цепь смещения потенциала и подключен к первому (10) дополнительному токостабилизирующему двухполюснику, эмиттер второго (2) входного транзистора соединен с базой второго (5) выходного транзистора через вторую (11) цепь смещения потенциала и подключен ко второму (12) дополнительному токостабилизирующему двухполюснику.

2. Буферный усилитель по п.1, отличающийся тем, что первая (9) и вторая (11) цепи смещения потенциалов выполнены в виде двух последовательно соединенных р-n переходов (13, 14) и (15, 16).

3. Буферный усилитель по п.1, отличающийся тем, что в схему введен первый (17) дополнительный транзистор, база которого подключена к базе второго (5) выходного транзистора, а эмиттер подключен к коллектору второго (2) входного транзистора.

4. Буферный усилитель по п.1, отличающийся тем, что в схему введен второй (18) дополнительный транзистор, база которого подключена к базе первого n-р-n (4) выходного транзистора, а эмиттер подключен к коллектору первого n-р-n (1) входного транзистора.

| ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2000 |

|

RU2168263C1 |

| СТЕНД ДЛЯ ПОДБОРА РАЗМЕРА ОТВЕРСТИЯ ПОД ПРОТИВОВЗРЫВНУЮ ПАНЕЛЬ | 2015 |

|

RU2646973C2 |

| US 4935704 A, 19.06.1990 | |||

| US 4827223 A, 02.05.1989. | |||

Авторы

Даты

2010-10-10—Публикация

2009-03-12—Подача