Изобретение относится к области радиотехники и может быть использовано в радиодиспетчерских пунктах мониторинга для анализа сигнальной обстановки в регионе и для автоматического поиска и обнаружения сигналов радиостанций, постоянно сменяющих рабочие частоты.

Известно устройство автоматического поиска каналов радиосвязи, содержащее блок опорных частот, приемник радиосигналов, преобразователь сигналов, регистры, формирователь управляющих сигналов, мультиплексор, демультиплексор, несколько регистров, распределитель импульсов, блок сравнения, блок начальной установки и индикатор [авторское свидетельство СССР №1515373, МПК H04B 1/10, 1989 г.].

Недостатком данного устройства является относительно большая длительность процесса поиска частоты, и при частых сменах радиостанциями рабочих частот данное устройство не обеспечивает допустимой задержки обнаружения рабочего канала связи.

Наиболее близким по технической сущности, принятым за прототип, является устройство автоматического поиска радиостанций [Архипенко А.А., Горин Д.Г. и др. Устройство автоматического поиска сигналов радиостанций. Патент РФ №2132111, МПК H04B 1/10 от 20.06.99, бюл. №17, 1999 г.]. Данное устройство содержит блок управления, кодовый выход которого подключен к кодовому входу блока индикации и через блок опорных частот соединен с гетеродинным входом приемника. К выходу демодулированного сигнала этого приемника подключен информационный вход ждущего формирователя тактовой частоты, импульсный выход которого соединен с входом блока запоминания тактовой частоты. Выход контроля наличия сигнала приемника подключен к первому входу блока управления и соединен с управляющими входами формирователя разности фаз и блока сравнения. Первый вход блока сравнения подключен к выходу формирователя разности фаз, а второй и третий входы блока сравнения соединены с двумя выходами формирователя пороговых уровней. Фиксирующий выход блока сравнения соединен с управляющим входом блока индикации и вторым входом блока управления, а командный выход блока сравнения подключен к третьему входу блока управления, установочный выход которого соединен с установочными входами ждущего формирователя тактовой частоты, формирователя разности фаз и формирователя пороговых уровней. В составе формирователя разности фаз и формирователя пороговых уровней использованы суммирующие счетчики импульсов и цифроаналоговые преобразователи, а в схеме блока сравнения применены аналоговые компараторы.

Данное устройство обеспечивает поиск сигналов радиостанций, часто сменяющих рабочие частоты, путем запоминания тактовой частоты принимаемого сигнала и последующего ее сравнения с тактовой частотой сигнала на каждой k-й частоте. Решение о принадлежности сигнала на k-й фиксированной частоте интересующей радиостанции принимается при совпадении по частоте и времени прихода фронтов импульсов сравниваемых частот, чем повышается вероятность обнаружения сигнала требуемой радиостанции.

Однако данное устройство-прототип имеет следующие недостатки.

При поиске тактовой частоты нужной радиостанции в известном устройстве выделяется разность фаз между эталонной и принимаемой последовательностями тактовых импульсов, которая сравнивается с допустимым уровнем. При ведении радиомониторинга в условиях сложной помеховой обстановки может иметь место флюктуация фронтов тактовых импульсов. В данном случае совпадения фронтов сравниваемых импульсов может не произойти, хотя в действительности они принадлежат одному и тому же сигналу, а это ведет к снижению вероятности обнаружения сигнала требуемой радиостанции. Кроме того, выделение и сравнение фаз импульсных последовательностей выполняется в аналоговой форме с помощью цифроаналоговых преобразователей и аналоговых компараторов, что усложняет структуру устройства и не позволяет его реализовать на современных перепрограммируемых цифровых микросхемах.

Техническим результатом, на достижение которого направлено изобретение, является уменьшение времени обнаружения каналов связи при частых сменах рабочих частот наблюдаемыми радиостанциями в условиях сложной помеховой обстановки и упрощение структуры устройства.

Для достижения этого технического результата в известное устройство автоматического поиска сигналов радиостанций, содержащее блок управления, кодовый выход которого подключен к кодовому входу блока индикации и через блок опорных частот соединен с гетеродинным входом приемника радиосигналов, к выходу демодулированного сигнала которого подключен информационный вход ждущего формирователя тактовой частоты, импульсный выход которого соединен с входом блока запоминания тактовой частоты, а выход контроля наличия сигнала приемника радиосигналов подключен к первому входу блока управления и к управляющим входам формирователя разности фаз и блока сравнения, первый вход которого подключен к выходу формирователя разности фаз, второй и третий входы блока сравнения соединены с двумя выходами формирователя пороговых уровней, фиксирующий выход блока сравнения соединен с управляющим входом блока индикации и вторым входом блока управления, командный выход блока сравнения подключен к счетному входу формирователя пороговых уровней и к третьему входу блока управления, установочный выход которого соединен с установочными входами ждущего формирователя тактовой частоты, формирователя разности фаз и формирователя пороговых уровней, дополнительно введен логический элемент "Исключающее ИЛИ". При этом первый и второй входы логического элемента "Исключающее ИЛИ" соединены, соответственно, с входом и выходом блока запоминания тактовой частоты, а выход логического элемента "Исключающее ИЛИ" подключен к информационному входу формирователя разности фаз, вход знака фазы которого соединен с управляющим выходом ждущего формирователя тактовой частоты. Счетный вход формирователя разности фаз соединен со стробирующим выходом ждущего формирователя тактовой частоты.

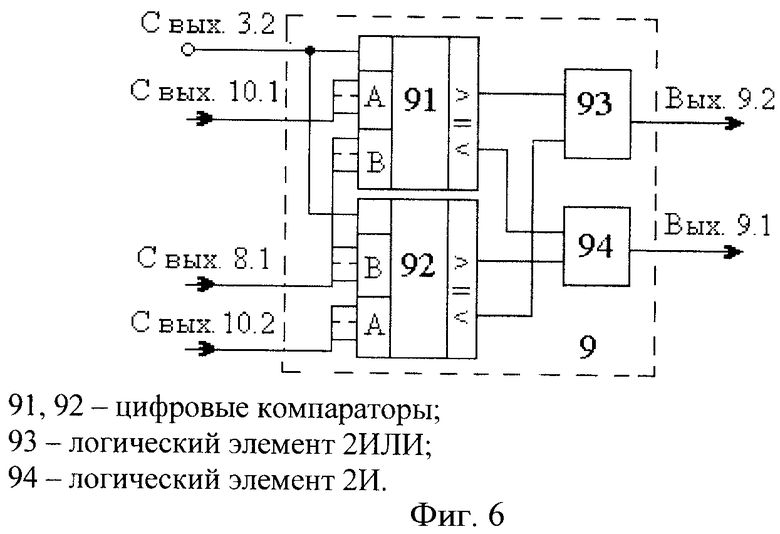

В качестве формирователя разности фаз применен реверсивный счетчик импульсов и регистр памяти, а в блоке сравнения использованы цифровые компараторы, первые выходы которых подключены в двум входам логического элемента 2И, выход которого является фиксирующим выходом блока сравнения, а вторые выходы компараторов подключены к входам элемента 2ИЛИ, выход которого является командным выходом блока сравнения.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественны всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна». Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Заявленное изобретение поясняется следующими фигурами:

фиг.1 - структурная схема устройства поиска сигналов;

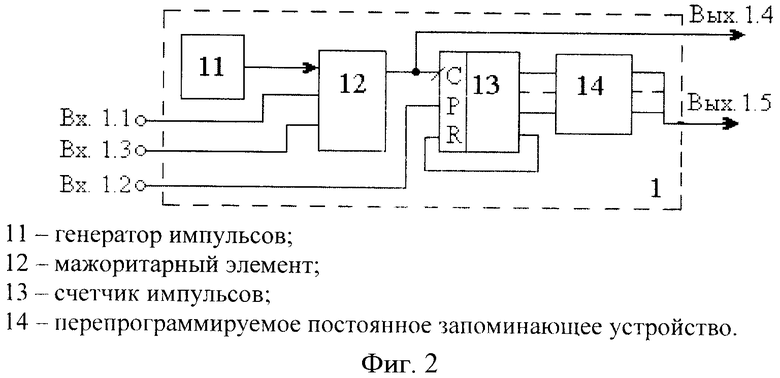

фиг.2 - структурная схема блока управления;

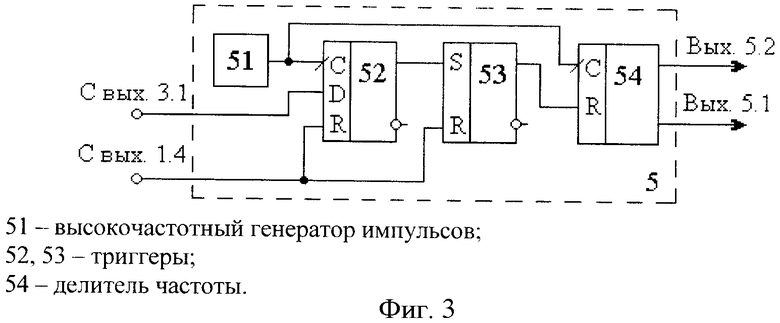

фиг.3 - структурная схема ждущего формирователя тактовой частоты;

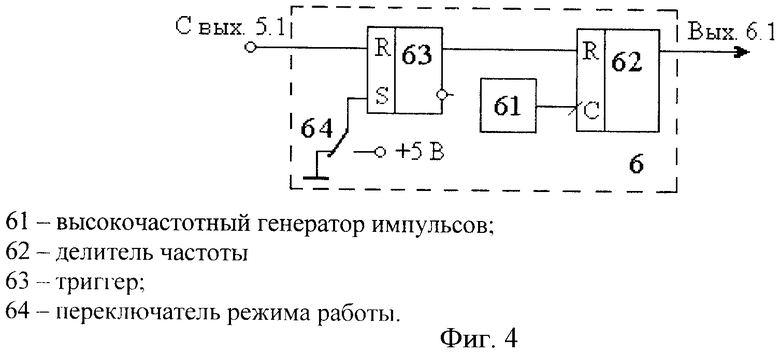

фиг.4 - структурная схема блока запоминания тактовой частоты;

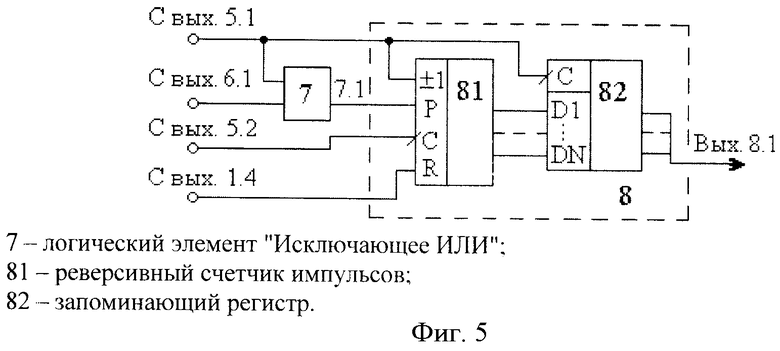

фиг.5 - структурная схема формирователя разности фаз;

фиг.6 - структурная схема блока сравнения;

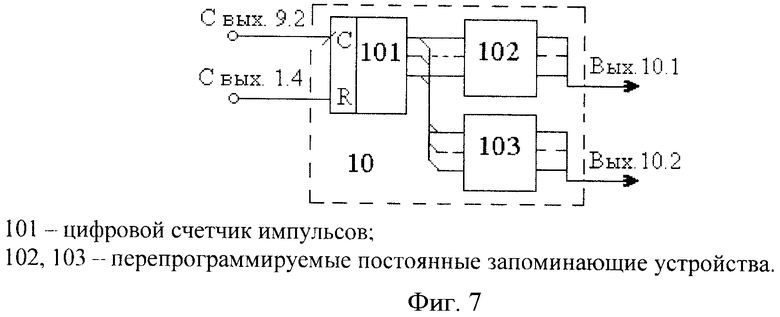

фиг.7 - структурная схема формирователя пороговых уровней.

Устройство поиска сигналов, структурная схема которого приведена на фиг.1, содержит блок управления 1, блок опорных частот 2, приемник радиосигналов 3, блок индикации 4, ждущий формирователь тактовой частоты 5, блок запоминания тактовой частоты 6, логический элемент "Исключающее ИЛИ" 7, формирователь разности фаз 8, блок сравнения 9 и формирователь пороговых уровней 10.

Кодовый выход 1.5 блока управления 1 подключен к кодовому входу блока индикации 4 и через блок опорных частот 2 - к гетеродинному входу приемника радиосигналов 3. Выход демодулированного сигнала 3.1 приемника радиосигналов 3 подключен к информационному входу ждущего формирователя тактовой частоты (ЖФТЧ) 5, импульсный выход 5.1 которого соединен с входом блока запоминания тактовой частоты (БЗТЧ) 6 и первым входом логического элемента "Исключающее ИЛИ" 7. Второй вход логического элемента "Исключающее ИЛИ" 7 соединен с выходом БЗТЧ 6. Выход 7.1 логического элемента "Исключающее ИЛИ" 7 подключен к информационному входу формирователя разности фаз 8, вход знака фазы которого соединен с управляющим выходом 5.2 ЖФТЧ 5, а счетный вход формирователя разности фаз 8 соединен с импульсным выходом 5.1 ЖФТЧ 5. Кроме того, управляющий выход 8.1 формирователя разности фаз 8 соединен с первым управляющим входом блока сравнения 9, а выход контроля наличия сигнала 3.2 приемника радиосигналов 3 соединен с первым входом 1.1 блока управления 1, управляющим входом формирователя разности фаз 8 и вторым управляющим входом блока сравнения 9. Установочные входы формирователя разности фаз 8 и ЖФТЧ 5 объединены с установочным входом формирователя пороговых уровней 10 и подключены к установочному выходу 1.4 блока управления 1. Фиксирующий выход 9.1 блока сравнения 9 соединен с управляющим входом блока индикации 4 и вторым входом 1.2 блока управления 1, третий вход 1.3 которого соединен со счетным входом формирователя пороговых уровней 10 и подключен к командному выходу 9.2 блока сравнения 9. Цифровыми кодами на выходах 10.1 и 10.2 формирователя пороговых уровней 10 задаются нижний и верхний пороговые уровни разности фаз между импульсами в блоке сравнения 9.

Устройство поиска сигналов радиостанций работает следующим образом.

Для идентификации сигнала нужного радиопередатчика при смене им рабочей частоты запоминаются значения тактовой синхронизации принимаемого сигнала в БЗТЧ 6 путем формирования импульсов начальной тактовой частоты в ЖФТЧ 5 и производится ее последующее сравнение с импульсами тактовой частоты сигнала, включившегося на новой частоте. Решение о принадлежности сигнала на новой фиксированной частоте искомому передатчику принимается при совпадении во временной области фронтов и срезов следующих подряд импульсов сравниваемых последовательностей. При ведении радиоприема в реальных условиях из-за влияния помеховой обстановки, нестабильности генераторов тактовой синхронизации на передающем и приемном конце совпадения фронтов сравниваемых импульсов может не произойти, так как возможен сдвиг во времени фронтов и срезов импульсов относительно друг друга на величину ΔtФР или ΔtСР соответственно.

В заявленном устройстве процесс принятия решения о совпадении импульсов сводится к постоянному измерению разности величин ΔtФР или ΔtСР (разности интервалов времени между фронтами и срезами сравниваемых импульсов) и последующему ее сравнению цифровыми компараторами блока сравнения 9 с пороговыми значениями кода, задаваемыми в формирователе пороговых уровней 10. По результатам этого сравнения на блок управления 1 подаются команды от блока сравнения 9 либо для фиксации частоты в блоке опорных частот (при малой разности длительностей Δt=ΔtФР-ΔtСР≤tДОП), либо для переключения частоты (при Δt=ΔtФР-ΔtСР>tДОП).

Блок опорных частот 2 обеспечивает формирование высокостабильных колебаний для приема сигналов на фиксированных частотах и имеет цифровой вход, на который с выхода 1.5 блока управления 1 поступают кодовые комбинации фиксированных частот. С выхода блока опорных частот 2 на гетеродинный вход приемника радиосигналов 3 поступают высокостабильные колебания, соответствующие k-й фиксированной радиочастоте. Приемник радиосигналов 3 обеспечивает прием сигналов на фиксированных частотах. С выхода демодулированного сигнала 3.1 приемника радиосигналов 3 последовательность информационных посылок поступает на вход ЖФТЧ 5, обеспечивающего формирование последовательности импульсов тактовой частоты и ее подстройку согласно входному сигналу. Импульсы тактовой частоты с выхода 5.1 ЖФТЧ 5 поступают на вход БЗТЧ 6, который вырабатывает аналогичную последовательность импульсов тактовой частоты синфазно с импульсами, формируемыми ЖФТЧ 5, и обеспечивает ее сохранение в случае исчезновения сигнала на выходе 3.1 приемника радиосигналов 3. Кроме того, приемник радиосигналов 3 контролирует уровень принимаемого сигнала, и в случае исчезновения радиосигнала на выходе 3.2 приемника радиосигналов 3 формируется высокий логический уровень, который подается на вход 1.1 блока управления 1. При этом на выходе 1.5 блока управления 1 формируется новый код для задания следующей фиксированной частоты в блоке опорных частот 2.

При появлении нового кода блок управления 1 формирует единичный импульс, который с выхода 1.4 поступает на входы установки ЖФТЧ 5, формирователя разности фаз 8, формирователя пороговых уровней 10 и приводит данные устройства в начальное состояние. При наличии сигнала на вновь настроенной частоте на выходе 3.2 приемника радиосигналов 3 формируется низкий логический уровень, которым разрешается работа формирователя разности фаз 8 и блока сравнения 9. При этом ЖФТЧ 5 вырабатывает импульсы тактовой частоты для новой последовательности информационных посылок, которая поступает на первый вход логического элемента "Исключающее ИЛИ" 7, и последовательность стробирующих импульсов с частотой в 32 раза больше тактовой, которая с выхода 5.2 ЖФТЧ 5 поступает на вход формирователя разности фаз 8.

На второй вход логического элемента "Исключающее ИЛИ" 7 поступают импульсы эталонной тактовой частоты с выхода 6.1 БЗТЧ 6. При этом на выходе элемента "Исключающее ИЛИ" 7 формируются импульсы с частотой вдвое больше тактовой частоты, длительность которых соответствует разности интервалов времени между фронтами ΔtФР и срезами ΔtСР каждой пары сравниваемых импульсов. В формирователе разности фаз 8 выполняется цифровое измерение длительностей ΔtФР и ΔtСР выходных импульсов элемента "Исключающее ИЛИ" 7 с помощью реверсивного счетчика, который суммирует стробирующие импульсы, поступающие с выхода 5.2 ЖФТЧ 5, в течение интервала времени ΔtФР, и выполняет вычитание стробирующих импульсов в течение интервала времени ΔtСР. Команда на изменение режима работы формирователя разности фаз 8 (выполнение суммирования или вычитания стробирующих импульсов) подается с выхода 5.1 ЖФТЧ 5. После окончания каждого импульса длительностью ΔtСР на выходе реверсивного счетчика формируется разностный код ΔN=(ΔtФР-ΔtСР)·fС, который запоминается в регистре памяти формирователя разности фаз 8 и сравнивается в блоке сравнения 9 с пороговыми значениями кода N1 и N2, которые подаются с выходов 10.1 и 10.2 формирователя пороговых уровней 10. В случае, если код N2<ΔN<N1, то блок сравнения 9 принимает решение о совпадении сравниваемых импульсов и формирует на выходе 9.1 единичный уровень, который поступает на управляющий вход блока индикации 4, отображающего номинал фиксированной частоты и сигнализирующего о ее принадлежности искомому передатчику, и на вход 1.2 блока управления 1, обеспечивая фиксацию настройки приемника на данной частоте. Если код N2>ΔN>N1, то блок сравнения 9 формирует единичный уровень сигнала на выходе 9.2, указывающий на несовпадение сравниваемых импульсов, а значит, и непринадлежность наблюдаемого сигнала искомому передатчику, который поступает на счетный вход формирователя пороговых уровней 10 и на командный вход 1.3 блока управления 1, который формирует новый код для настройки приемника радиосигналов 3 на новую фиксированную частоту.

Схема блока управления 1, приведенная на фиг.2, содержит генератор импульсов 11, мажоритарный элемент 12, счетчик импульсов 13, перепрограммируемое постоянное запоминающее устройство (ППЗУ) 14 и работает следующим образом. Генератор 11 вырабатывает импульсы с частотой у, обратной времени анализа одной фиксированной радиочастоты приемника радиосигналов 3. Выход генератора 11 через мажоритарный элемент 12 подключен к счетному входу счетчика 13, а на второй 1.1 и третий 1.3 входы мажоритарного элемента 12 поступают импульсы с выхода 3.2 приемника радиосигналов 3 и с выхода 9.2 блока сравнения 9 соответственно. При появлении единичного уровня сигнала на выходе 9.2 блока сравнения 9 или на выходе 3.2 приемника радиосигналов 3 формируется импульс на выходе мажоритарного элемента 12, который подается на счетный вход счетчика 13 и на выход 1.4 блока управления 1. Выходы счетчика 13 подключены к адресным входам ППЗУ 14, имеющего n разрядов, число которых определяется длиной кодовой комбинации фиксированных частот. ППЗУ программируется таким образом, что каждому k-му адресу соответствует кодовая комбинация k-й фиксированной частоты. Число используемых адресов в ППЗУ 14 равно числу анализируемых фиксированных частот. С выходов счетчика 13 информация в параллельном коде подается на адресные входы ППЗУ 14. На выходе ППЗУ формируется кодовая комбинация фиксированной частоты, соответствующей k-му адресу, которая в параллельном коде с выходов 1.5 подается по n-разрядной шине на входы блока опорных частот 2 и блока индикации 4. Выход m-го разряда счетчика 13 соединен с его входом сброса для установки счетчика в начальное состояние после анализа m-й частоты. На P-вход разрешения счета счетчика 13 поступает единичный уровень сигнала с выхода 9.1 при принятии решения о совпадении импульсов блоком сравнения 9, который запрещает работу счетчика 13 и тем самым фиксирует настройку приемника радиосигналов 3 на k-й фиксированной частоте.

Ждущий формирователь тактовой частоты 5 (фиг.3) содержит высокочастотный генератор импульсов 51, триггеры 52, 53, делитель частоты 54 и работает следующим образом. Генератор 51 вырабатывает импульсы с частотой, в 64 раза выше частоты манипуляции наблюдаемой передачи, которые поступают на С-вход триггера 52. Информационные посылки с выхода 3.1 приемника радиосигналов 3 подаются на D-вход этого триггера 52. При появлении единичного уровня информационной посылки триггер 52 срабатывает по фронту импульса, вырабатываемого генератором 51, и его выходной сигнал поступает на S-вход второго триггера 53. На выходе триггера 53 появляется единичный уровень сигнала, который разрешает работу делителю частоты 54. На счетный С-вход делителя частоты 54 подаются высокочастотные импульсы от генератора 51. С шестого разряда делителя частоты 54 снимается последовательность импульсов тактовой частоты, которая подается на выход 5.1 и далее поступает на блок запоминания тактовой частоты 6 и на один вход логического элемента "Исключающее ИЛИ" 7. С первого разряда делителя частоты 54 на выход 5.2 поступают стробирующие импульсы с частотой, в 32 раза больше тактовой частоты, которые затем подаются на вход формирователя разности фаз 8. При перестройке приемника радиосигналов 3 на новую фиксированную частоту с выхода 1.4 блока управления 1 поступает единичный импульс на R-входы установки нуля триггеров 52 и 53, который их обнуляет, тем самым приводя устройство в исходное состояние.

Блок запоминания тактовой частоты 6 (фиг.4) содержит высокочастотный генератор импульсов 61, делитель частоты 62, триггер 63, переключатель режима работы 64 и работает следующим образом. Высокочастотный генератор импульсов 61 вырабатывает импульсы с частотой, в 64 раза больше тактовой частоты, аналогично высокочастотному генератору импульсов 51 ЖФТЧ 5, которые поступают на счетный С-вход делителя частоты 62. С выхода 5.1 ЖФТЧ 5 импульсы тактовой частоты поступают на R-вход триггера 63, на S-вход которого подается нулевой уровень напряжения через переключатель 64. При поступлении импульса тактовой частоты на R-вход триггера 63 на его выходе формируется нулевой уровень, который подается на R-вход делителя частоты 62, разрешая его работу. Последовательность импульсов эталонной тактовой частоты снимается с шестого разряда делителя частоты 62 и подается на второй вход элемента "Исключающее ИЛИ" 7, выход которого соединен с входом формирователя разности фаз 8. Установка триггера 63 в единичное состояние происходит при подаче на его S-вход положительного импульса переключателем 64, что соответствует обучению системы начальной тактовой частоте, в частности при настройке приемника на частоту другого радиопередатчика.

Формирователь разности фаз 8 (фиг.5) содержит реверсивный счетчик импульсов 81 и запоминающий регистр 82 и работает совместно с логическим элементом "Исключающее ИЛИ" 7 следующим образом. С выхода 5.2 ЖФТЧ 5 стробирующие импульсы с частотой fC, в 32 раза больше тактовой, поступают на счетный С-вход реверсивного счетчика 81. На первый вход логического элемента "Исключающее ИЛИ" 7, на вход реверса (±1) реверсивного счетчика импульсов 81 и на С-вход запоминающего регистра 82 поступают импульсы тактовой частоты с выхода 5.1 ЖФТЧ 5. На второй вход логического элемента "Исключающее ИЛИ" 7 поступают импульсы эталонной тактовой частоты с выхода 6.1 БЗТЧ 6. При этом на выходе 7.1 логического элемента "Исключающее ИЛИ" 7 появляются импульсы, длительность которых соответствует разности интервалов времени между фронтами ΔtФР и срезами ΔtСР импульсов, поступающих с выходов 5.1 и 6.1 соответственно. Эти импульсы с выхода 7.1 логического элемента "Исключающее ИЛИ" 7 подаются на P-вход разрешения счета реверсивного счетчика импульсов 81. При наличии импульса на входе реверса ±1 реверсивного счетчика импульсов 81 работает в режиме суммирования счетных импульсов частоты fC в течение времени ΔtФР, и на выходе реверсивного счетчика импульсов 81 получается двоичный код, соответствующий количеству стробирующих импульсов между фронтами сравниваемых импульсов: NФР=ΔtФР·fC. В паузах между импульсами на входе реверса ±1 реверсивный счетчик импульсов 81 работает в режиме вычитания счетных импульсов частоты fC в течение времени ΔtСР, и в конце времени ΔtСР формирует разностный код ΔN=(ΔtФР-ΔtСР)·fС. Поэтому на выходах реверсивного счетчика 81 за два такта цифрового измерения формируется разностный код ΔN=(ΔtФР-ΔtСР)·fС который записывается в запоминающий регистр 82 по фронту каждого импульса па выходе 5.1 ЖФТЧ 5. С выходов запоминающего регистра 82 код ΔN поступает на выход 8.1 формирователя разности фаз для его последующего сравнения в блоке сравнения 9 с пороговыми значениями кодов N1 и N2, поступающих от формирователя пороговых уровней 10.

Работа реверсивного счетчика импульсов 81 разрешается при единичном уровне сигнала на выходе 7.1 логического элемента "Исключающее ИЛИ" 7. Обнуление реверсивного счетчика импульсов 81 и приведение формирователя разности фаз 8 в начальное состояние осуществляется при поступлении на R-вход реверсивного счетчика импульсов 81 единичного импульса с выхода 1.4 блока управления 1.

Блок сравнения 9 (фиг.6) содержит цифровые компараторы 91, 92, логический элемент 2ИЛИ 93, логический элемент 2И 94 и работает следующим образом. С выхода 8.1 формирователя разности фаз 8 поступает разностный код ΔN, который сравнивается цифровыми компараторами 91 и 92 с пороговыми значениями кодов N1 и N2, подаваемых с выходов 10.1 и 10.2 формирователя пороговых уровней 10. Выходы цифровых компаратора 91 и 92 подключены попарно к входам логического элемента 2ИЛИ 93 и логического элемента 2И 94. С выхода 10.1 формирователя пороговых уровней 10 на входы "А" цифрового компаратора 91 подается код нижнего порогового уровня N1. Цифровой компаратор 91 производит сравнение кодов ΔN и N1. Если выполняется неравенство ΔN>N1, то цифровой компаратор 91 вырабатывает единичный уровень сигнала, который проходит через логический элемент 93 типа 2ИЛИ и с выхода 9.2 блока сравнения 9 поступает на вход 1.3 формирователя управляющих сигналов 1, подавая команду блоку управления 1 на выработку кода новой фиксированной частоты. Если же выполняется обратное неравенство ΔN<N1, то появляется единичный уровень сигнала на втором выходе цифрового компаратора 91, который подключен к входу логического элемента 94 типа 2И. Аналогичным образом второй цифровой компаратор 92 производит сравнение кода N2, поступающего с выхода 10.2 формирователя пороговых уровней 10, с кодом ΔN. Если код ΔN будет меньше кода N1 и больше кода N2, то на обоих входах логического элемента 94 типа 2И будут высокие уровни логических сигналов. При этом на выходе 9.1 появляется единичный уровень, который поступает на управляющий вход блока индикации 4, сигнализируя о принадлежности сигнала на k-й фиксированной частоте искомому передатчику, и на вход 1.2 блока управления 1, фиксируя настройку приемника радиосигналов 3 на данную частоту. При исчезновении сигнала на входе приемника радиосигналов 3 появляется единичный уровень на выходе контроля наличия сигнала 3.2, который подается на управляющие входы цифровых компараторов 91, 92, приводя блок сравнения 9 в начальное состояние.

Формирователь пороговых уровней 10 (фиг.7) содержит цифровой счетчик импульсов 101, перепрограммируемые постоянные запоминающие устройства 102, 103 и работает следующим образом. С выхода 9.2 блока сравнения 9 импульсы поступают на С-вход цифрового счетчика импульсов 101, который производит подсчет количества этих импульсов. Число двоичных разрядов в цифровом счетчике импульсов 101 выбирается исходя из периода анализа (числа сравниваемых импульсов тактовой частоты, по которым принимается решение об их совпадении). Код с выхода цифрового счетчика импульсов 101 поступает на адресные входы ППЗУ 102 и 103. В памяти ППЗУ 102 запрограммированы нижние пороговые значения кода N1, а в ППЗУ 103 хранятся значения верхнего порогового уровня N2. Число разрядов выходного кода в обоих ППЗУ такое же, как и у запоминающего регистра 82 формирователя разности фаз 8, и определяется максимальным количеством стробирующих импульсов, соответствующих величине, по которой принимается решение о совпадении тактовых импульсов. С выходов ППЗУ 102 и 103 кодовые комбинации нижнего N1 и верхнего N2 пороговых уровней, соответствующие каждому импульсу тактовой частоты, поступают по n-разрядным шинам 10.1 и 10.2 на входы цифровых компараторов 91 и 92 блока сравнения 9. Обнуление цифрового счетчика импульсов 101 и приведение формирователя пороговых уровней 10 в начальное состояние осуществляются при поступлении на R-вход цифрового счетчика импульсов 101 единичного уровня с выхода 1.4 блока управления 1.

Практически в качестве основных функциональных узлов устройства можно использовать стандартные цифровые микросхемы серий К564, K561.

В блоке управления 1 кварцевый генератор импульсов 11 можно реализовать на микросхеме К564АГ1 [Шило В.Л. Популярные микросхемы КМОП. - М.: Ягуар, 1993. - С.62], мажоритарный элемент 12 - на микросхеме К561ЛП13, счетчик 13 - на микросхеме К561ИЕ14, ППЗУ 14 - на микросхемах серии 573 [Цифровые и аналоговые интегральные микросхемы: Справочник / Под ред. С.В.Якубовского. - М.: Радио и связь, 1990 г. с.298-314].

В качестве блока опорных частот 2 и приемника 3 можно использовать серийно выпускаемое радиоприемное устройство Р-399А "Катран", где данные блоки технически реализованы. В качестве индикатора 4 может быть использован любой серийно выпускаемый цифровой индикатор.

В ждущем формирователе тактовой частоты 5 генератор 51 аналогичен по структуре генератору 11, а в качестве триггеров 52, 53 можно использовать микросхемы типа К561ТМ2, а в качестве делителя частоты - микросхему К561ИЕ16 [Шило В.Л. Популярные микросхемы КМОП. - М.: Ягуар, 1993. - С.25, 34, 62].

В блоке запоминания тактовой частоты 6 в качестве триггера 63 можно применить микросхему К561ТМ2, а в качестве делителя частоты 62 - микросхему К561ИЕ16, в генераторе 61 - микросхему К564АГ1, а переключатель 64 реализовать на микросхеме К561КП1 [Шило В.Л. Популярные микросхемы КМОП. - М.: Ягуар, 1993. - С.25, 34, 23]. Элемент 7 "Исключающее ИЛИ" можно реализовать на микросхеме К561ЛП2 [Шило В.Л. Популярные микросхемы КМОП. - М.: Ягуар, 1993. - С.18].

В формирователе разности фаз 8 реверсивный счетчик 81 можно собрать на микросхеме К561ИЕ11, а регистр 82 - на микросхемах К561ИР9 [Шило В.Л. Популярные микросхемы КМОП. - М.: Ягуар, 1993. - С.32, 41].

В блоке сравнения 9 можно реализовать компараторы 91, 92 на микросхемах К561СА1, элемент 2И 94 - на микросхеме К561ЛА7, элемент 2ИЛИ 93 - на микросхеме К561ЛЕ5 [Шило В.Л. Популярные микросхемы КМОП. - М.: Ягуар, 1993. - С.18-21]. В формирователе пороговых уровней 10 можно сделать счетчик импульсов 101 на микросхеме К561ИЕ11 и реализовать ППЗУ 102 и 103 на микросхемах 537 серии. Кроме того, все перечисленные блоки 5-10 устройства можно реализовать программным способом на зарубежных электрически программируемых логических матрицах фирмы Analog Devises.

Положительный эффект в предлагаемом устройстве можно обосновать следующим образом.

Показателем эффективности систем с автоматическим поиском каналов радиосвязи является вероятность обнаружения сигналов при поиске новой рабочей частоты (канала связи) наблюдаемой радиостанции, если в результате воздействия помех система связи вынуждена часто производить смену рабочих частот для достижения требуемого качества связи.

Задача состоит в том, чтобы повысить вероятность обнаружения сигнала при минимально возможном времени анализа радиочастот.

При дискретной перестройке радиопередатчика по N фиксированным частотам вероятность его обнаружения зависит от частотно-временного совпадения частоты настройки приемника с текущей частотой искомого сигнала. При постоянной длительности опроса каждого канала tK=const период перестройки по фиксированным частотам T=N·tK зависит от интервала времени опроса tK каждой фиксированной частоты и общего числа N таких частот.

Время распознавания можно уменьшить и повысить вероятность обнаружения путем сравнения импульсов начальной тактовой частоты принимаемого сигнала с последовательностями импульсов тактовых частот сигналов на каждой фиксированной частоте. При наличии частотно-временного совпадения частоты настройки приемника с рабочей частотой передатчика вероятность правильного обнаружения канала связи зависит от периода анализа, числа сравниваемых импульсов и заданных значений длительности импульсов и длительности их перекрытия. В предложенном устройстве выполняется контроль длительностей не только между фронтами ΔtФР сравниваемых импульсов (как в прототипе), но и между срезами ΔtСР этих импульсов, что при одинаковой вероятности обнаружения нужного канала радиосвязи позволяет вдвое сократить время поиска нужной частоты.

Можно повысить вероятность обнаружения до уровня РОБН≈0,99 при времени анализа, равном двум периодам следования импульсов тактовой частоты (в течение времени передачи двух элементарных посылок), но при условии обеспечения качественного приема сигнала, когда его временные искажения не превышают 10% от длительности элементарной посылки. При плохом качестве приема в устройстве-прототипе нужно увеличивать период анализа до 7 элементарных посылок, чтобы обеспечивается вероятность обнаружения нужного канала связи до уровня РОБН>0,95 при оценке длительностей временных интервалов между фронтами сравниваемых импульсов.

В предложенном устройстве аналогичная вероятность обнаружения нужного канала связи обеспечивается максимум за 4 элементарных посылки даже в условиях сложной помеховой обстановки в канале связи.

Следовательно, заявляемое устройство позволяет обеспечить своевременный поиск сигналов радиостанций, часто сменяющих рабочие частоты, с довольно высокой вероятностью обнаружения за короткое время анализа. В зависимости от решаемых задач время распознавания может выбираться исходя из приоритетности максимальной вероятности обнаружения над временем распознавания или наоборот. Этим подтверждается существенный положительный эффект от использования предлагаемого устройства.

Кроме того, реализация основных функциональных узлов устройства только на цифровых микросхемах позволяет упростить его сложность, например, за счет использования современных электрически перепрограммируемых логических матриц, что дает дополнительную возможность повысить надежность, уменьшить габаритные размеры и энергопотребление устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИИ | 2005 |

|

RU2292641C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1995 |

|

RU2097908C1 |

| СПОСОБ СВЯЗИ СВЕРХШИРОКОПОЛОСНЫМИ СИГНАЛАМИ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ СИНХРОНИЗАЦИИ | 2010 |

|

RU2433532C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| СИСТЕМА СВЯЗИ СВЕРХШИРОКОПОЛОСНЫМИ СИГНАЛАМИ С ПОВЫШЕННОЙ ТОЧНОСТЬЮ И СТАБИЛЬНОСТЬЮ СИНХРОНИЗАЦИИ | 2010 |

|

RU2441320C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ МНОГОЛУЧЕВЫХ РАДИОСИГНАЛОВ | 1992 |

|

RU2042195C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ, СМЕНЯЮЩИХ РАБОЧИЕ ЧАСТОТЫ | 2005 |

|

RU2308151C1 |

| ЦЕНТРАЛЬНАЯ СТАНЦИЯ СИСТЕМЫ РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2022 |

|

RU2780810C1 |

Изобретение относится к области радиотехники и может быть использовано для автоматического поиска сигналов радиостанций, постоянно сменяющих рабочие частоты. Технический результат заключается в уменьшении времени обнаружения каналов связи при частых сменах рабочих частот наблюдаемыми радиостанциями в условиях сложной помеховой обстановки. Устройство поиска сигналов содержит блок управления, блок опорных частот, приемник радиосигналов, блок индикации, ждущий формирователь тактовой частоты, блок запоминания тактовой частоты, логический элемент "Исключающее ИЛИ", формирователь разности фаз, блок сравнения и формирователь пороговых уровней. 2 з.п. ф-лы, 7 ил.

1. Устройство поиска сигналов, содержащее блок управления, кодовый выход которого подключен к кодовому входу блока индикации и через блок опорных частот соединен с гетеродинным входом приемника радиосигналов, к выходу демодулированного сигнала которого подключен информационный вход ждущего формирователя тактовой частоты, импульсный выход которого соединен с входом блока запоминания тактовой частоты, а выход контроля наличия сигнала приемника подключен к первому входу блока управления и к управляющим входам формирователя разности фаз и блока сравнения, первый вход которого подключен к выходу формирователя разности фаз, второй и третий входы блока сравнения соединены с двумя выходами формирователя пороговых уровней, фиксирующий выход блока сравнения соединен с управляющим входом блока индикации и вторым входом блока управления, командный выход блока сравнения подключен к счетному входу формирователя пороговых уровней и третьему входу блока управления, установочный выход которого соединен с установочными входами ждущего формирователя тактовой частоты, формирователя разности фаз и формирователя пороговых уровней, отличающееся тем, что в него дополнительно введен логический элемент "Исключающее ИЛИ", первый вход которого соединен с входом знака фазы формирователя разности фаз и подключен к входу блока запоминания тактовой частоты, выход которого соединен с вторым входом элемента "Исключающее ИЛИ", выход которого соединен с информационным входом формирователя разности фаз, а счетный вход формирователя разности фаз соединен со стробирующим выходом ждущего формирователя тактовой частоты.

2. Устройство поиска сигналов по п.1, отличающееся тем, что в качестве формирователя разности фаз применен реверсивный счетчик импульсов с запоминающим регистром.

3. Устройство поиска сигналов по п.1, отличающееся тем, что в блоке сравнения использованы цифровые компараторы, первые выходы которых подключены в двум входам логического элемента 2И, выход которого является фиксирующим выходом блока сравнения, а вторые выходы компараторов подключены к входам элемента 2ИЛИ, выход которого является командным выходом блока сравнения.

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИИ | 2005 |

|

RU2292641C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| Устройство автоматического поиска каналов радиосвязи | 1987 |

|

SU1515373A1 |

| US 5355527 А, 11.10.1994 | |||

| Способ хроматографического определения окиси углерода в газовой среде | 1961 |

|

SU150297A1 |

Авторы

Даты

2011-06-27—Публикация

2009-06-29—Подача