Изобретение относится к электронной полупроводниковой технике, в частности к методам изготовления СВЧ мощных кремниевых полевых LDMOS (Lateral Diffused Metal Oxide Semiconductor) транзисторов, и может быть использовано для создания на их основе радиоэлектронной аппаратуры нового поколения.

Известен способ изготовления СВЧ LDMOS транзисторов, выбранный в качестве аналога (патент США № US 6707102 В2 «Semiconductor device including an insulated gate type field effect transistor and method for fabricating the same», опубликован 16.03.2004 г.), включающий выращивание толстого полевого диэлектрика на поверхности высокоомного эпитаксиального р--слоя исходной кремниевой р-р+-подложки на периферии транзисторных структур, создание истоковых р+-перемычек транзисторных ячеек в объеме эпитаксиального р--слоя подложки не покрытом полевым диэлектриком, выращивание подзатворного диэлектрика на поверхности эпитаксиального слоя подложки, формирование из предварительно нанесенного на подзатворный диэлектрик слоя поликремния и силицида вольфрама (полицида) электродов затвора транзисторных ячеек в виде узких продольных зубцов прямоугольного сечения, создание р-канальной (р-кармана), высоколегированных n+-областей стока, истока и слаболегированной n-области стока транзисторных ячеек посредством последовательного внедрения в подложку акцепторной и донорной примеси с использованием электродов затвора в качестве защитной маски и последующего диффузионного перераспределения внедренных примесей, формирование металлических экранов, электродов стока и истока транзисторных ячеек на лицевой стороне подложки и общего металлического электрода истока на ее тыльной стороне.

Одним из основных недостатков, ограничивающих диапазон рабочих частот изготовленных таким способом LDMOS транзисторов, является постоянная времени цепи затвора, обусловленная достаточно высоким сопротивлением силицидов вольфрама, титана, кобальта и других тугоплавких металлов (1÷2 Ом/□), используемых для шунтирования поликремния.

Известен другой способ изготовления СВЧ мощных кремниевых LDMOS транзисторов («Philips BLF2022-90 power MOSFET structural analysis». 3685 Richmond Road, Suite 500, Ottawa, ONK2H587, Canada, 17.06.2004 г.), в соответствии с которым слаболегированная n-область стока транзисторных ячеек вместо однородной выполнена многоступенчатой, а узкие (0,82 мкм) полицидные (WSi/Si∗) затворные зубцы толщиной 0,44 мкм и протяженностью 330 мкм через вскрытые в толстом (~1 мкм) межслойном диэлектрике контактные окна размером 0,35 мкм × 330 мкм для уменьшения постоянной времени цепи затвора по всей длине дополнительно прошунтированы трехслойным металлическим покрытием: Ti (0,08 мкм) / TiW (0,14 мкм) / Au (1,24 мкм). Это позволило реализовать приборы с диапазоном рабочих частот до 2,0÷2,2 ГГц и пробивными напряжениями стока Uс проб=65 В. Однако реализация второго способа-аналога в промышленном производстве существенно ограничено из-за необходимости иметь дорогостоящее прецизионное технологическое оборудование и «эксклюзивные» технологические операции для формирования затворного узла транзисторных ячеек с приемлемым для организации рентабельного выпуска изделий процентом выхода годных структур на пластине, что является основным его недостатком.

В качестве прототипа выбран способ изготовления СВЧ LDMOS транзисторов (Isao Yoshida, «2-GHz Si power MOSFET technology» - International Electron Devices Meeting, 1997, Washington, Technical Digest, 7-10 Dec. 1997), включающий формирование истоковых р+-перемычек и р-карманов транзисторных ячеек в высокоомном эпитаксиальном р--слое исходной кремниевой р-р+-подложки, выращивание подзатворного диэлектрика на поверхности эпитаксиального слоя, формирование полицидных (WSi/Si∗) электродов затвора транзисторных ячеек в виде узких продольных зубцов прямоугольного сечения с рядом прилегающих к ним со стороны истока ответвленных контактных площадок над р-карманами, формирование слаболегированной n-области стока транзисторных ячеек посредством перекомпенсации акцепторной примеси в выходящей за пределы полицидного электрода затвора периферийной части р-кармана внедренной в подложку донорной примесью, создание высоколегированных n+-областей стока и истока транзисторных ячеек посредством внедрения в подложку донорной примеси при использовании полицидных электродов затвора и слоев фоторезиста в качестве защитной маски и последующего диффузионного перераспределения внедренной примеси, формирование металлических электродов стока, истока и шин, шунтирующих полицидные затворные зубцы транзисторных ячеек через примыкающие к ним со стороны истока ответвленные контактные площадки на лицевой стороне подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне. Подобным образом были изготовлены образцы кремниевых СВЧ LDMOS транзисторов, которые имели пороговые напряжения Узи пор≤0,5 В, пробивные напряжения стока Uс проб=16 В и на частоте f=2,0 ГГц при напряжении питания по стоку Uс пит=3,6 В отдавали в нагрузку мощность Рвых=1 Вт при коэффициенте усиления по мощности Кур=6,5 дБ и коэффициенте полезного действия стоковой цепи ηс=34% [3].

Основными недостатками способа-прототипа являются:

- невозможность реализации значений Uзи пор, Uc проб, Uc пит, характерных для мощных кремниевых СВЧ LDMOS транзисторов;

- невозможность реализации оптимальной для мощных СВЧ LDMOS транзисторов многоступенчатой конфигурации слаболегированной n-области стока транзисторных ячеек;

- невозможность реализации одинаковой длины индуцированного n-канала по всей протяженности затворных зубцов транзисторных ячеек (в районе дислокации примыкающих к затворным зубцам ответвленных контактных площадок канал получается длиннее);

- низкая стойкость изготовленных по способу-прототипу приборов к воздействию ионизирующих излучений.

Технический результат настоящего изобретения - создание мощных кремниевых СВЧ LDMOS транзисторов с улучшенными электрическими параметрами, повышенной стойкостью к воздействию ионизирующих излучений и более высоким процентом выхода годных структур.

Технический результат достигается тем, что в известном способе изготовления СВЧ LDMOS транзисторов, включающем выращивание толстого полевого диэлектрика на поверхности высокоомного эпитаксиального р--слоя исходной кремниевой р-р+-подложки на периферии транзисторных структур, формирование истоковых р+-перемычек и р-карманов транзисторных ячеек в эпитаксиальном р--слое подложки, не покрытом полевым диэлектриком, выращивание подзатворного диэлектрика и формирование поликремниевых электродов затвора транзисторных ячеек в виде узких продольных зубцов прямоугольного сечения с рядом прилегающих к ним со стороны истока ответвленных контактных площадок над р-карманами, создание высоколегированных n+-областей стока, истока и слаболегированной n-области стока транзисторных ячеек посредством внедрения в подложку и последующего диффузионного перераспределения донорной примеси с использованием электродов затвора в качестве защитной маски, формирование металлических электродов стока, истока, экранов и шин, шунтирующих электроды затвора транзисторных ячеек через ответвленные контактные площадки на лицевой стороне подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне, первую ступень слаболегированной многоступенчатой n-области стока транзисторных ячеек формируют после образования истоковых р+-перемычек посредством внедрения донорной примеси в эпитаксиальный р--слой подложки без использования защитных масок, р-карманы, стоковые и истоковые области транзисторных ячеек создают с помощью дополнительной диэлектрической защитной маски, идентичной по конфигурации и местоположению продольным зубцам поликремниевого электрода затвора без примыкающих к ним ответвленных контактных площадок, одновременно с р-карманами формируют аналогичные им области на торцах слаболегированной n-области стока транзисторных ячеек, примыкающих к толстому полевому диэлектрику транзисторной структуры, а электроды затвора транзисторных ячеек с прилегающими к зубцам ответвленными контактными площадками формируют после удаления дополнительной диэлектрической защитной маски и последующего выращивания подзатворного диэлектрика, при этом ширину зубцов поликремниевого электрода затвора выбирают такой, чтобы она на величину погрешности совмещения превышала длину индуцированного канала транзисторных ячеек.

Сопоставительный анализ с прототипом показывает, что заявляемый способ отличается наличием новой совокупности и последовательности выполнения технологических операций: использование дополнительной диэлектрической защитной маски заданной конфигурации, сформированной на определенном этапе технологического маршрута в конкретном месте создаваемой транзисторной LDMOS-структуры для формирования р-кармана, истоковой и стоковых областей транзисторных ячеек; формирование поликремниевого электрода затвора с регламентированной шириной продольных затворных зубцов над индуцированным n-каналом после создания канальной, истоковой, стоковых областей транзисторных ячеек и последующего удаления дополнительной диэлектрической защитной маски и выращивания подзатворного диэлектрика на поверхности эпитаксиального слоя кремниевой р-р+-подложки; формирование 1-ой ступени многоступенчатой слаболегированной n-области стока транзисторных ячеек до создания р-карманов посредством перекомпенсации акцепторной примеси внедряемой донорной примесью в эпитаксиальном р--слое подложки, а не в р-кармане; одновременное формирование с р-карманами аналогичных областей на торцах слаболегированных n-областей стока транзисторных ячеек, примыкающих к толстому полевому диэлектрику транзисторной структуры. Таким образом, заявляемый способ отвечает критерию изобретения «новизна».

Создание канальной, истоковой и стоковых областей транзисторных ячеек с помощью дополнительной диэлектрической защитной маски, сформированной на месте будущей дислокации в транзисторной LDMOS-структуре затворных зубцов поликремниевого электрода затвора без примыкающих к ним ответвленных контактных площадок и имеющей идентичную затворным зубцам конфигурацию и сопоставимые топологические размеры, позволяет в отличие от способа-прототипа реализовать одинаковую длину индуцированного n-канала по всей протяженности затворных зубцов, в том числе и в районе дислокации примыкающих к ним ответвленных контактных площадок.

Формирование в заявляемом способе вначале 1-ой ступени слаболегированной многоступенчатой n-области стока транзисторных ячеек посредством внедрения донорной примеси в эпитаксиальный р--слой подложки без использования защитных масок, а затем р-карманов и одновременно с ними аналогичных областей на торцах слаболегированных n-областей стока транзисторных ячеек, примыкающих к толстому полевому диэлектрику транзисторной структуры посредством перекомпенсации донорной примеси внедряемой в подложку акцепторной примесью, позволяет обеспечить независимо друг от друга оптимальный уровень легирования р-кармана и слаболегированной многоступенчатой стоковой n-области транзисторных ячеек, требуемый для реализации типичных для мощных СВЧ LDMOS транзисторов значений Узи пор, Uc проб, Uc пит, а также значительно упростить по сравнению с прототипом и способами-аналогами технологический процесс изготовления транзисторных структур.

Формирование подзатворного диэлектрика и поликремниевых электродов затвора транзисторных ячеек в заявляемом способе после создания канальной (кармана), стоковой и истоковой областей позволяет:

- использовать в качестве электрода затвора не только поликремний и полициды, но и тугоплавкие металлы (Мо и др.) и их силициды;

- улучшить качество подзатворного диэлектрика и повысить по сравнению с прототипом и способами-аналогами процент выхода годных структур на пластине и стойкость к воздействию ионизирующих излучений.

При изготовлении транзисторных структур по заявляемому способу ширина продольных зубцов поликремниевого или полицидного электрода затвора транзисторных ячеек должна на величину погрешности совмещения превышать длину индуцированного канала, что гарантирует образование индуцированного n-канала под затворными зубцами на всем их протяжении при приложении положительного напряжения к электроду затвора транзисторной структуры.

В предлагаемом изобретении новая совокупность и последовательность технологических операций позволяет в отличие от способа-прототипа обеспечить пробивные напряжения стока Uc проб=40…120 В, пороговые напряжения Uзи пор=2…6 В, напряжения питания по стоку Uc пит=12,5…50 В и отдаваемые в нагрузку мощности Рвых=5…200 Вт, присущие мощным СВЧ LDMOS транзисторам с диапазонам рабочих частот до 2,0…3,5 ГГц, то есть проявляет новое техническое свойство. Следовательно, заявляемый способ соответствует критерию «изобретательский уровень».

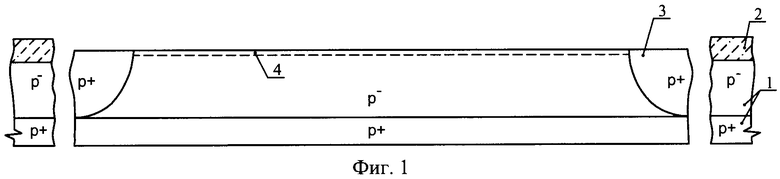

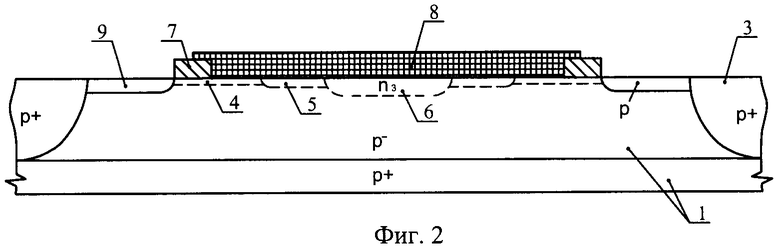

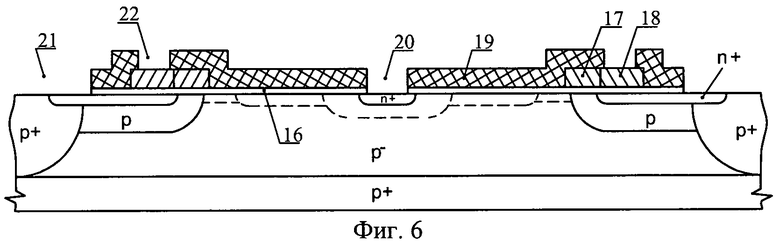

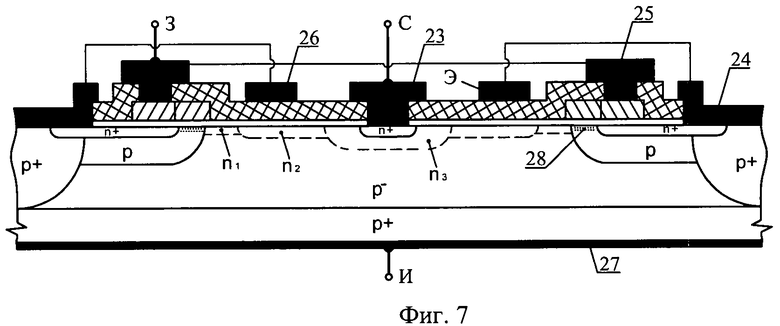

На фигурах 1…7 изображены основные этапы изготовления СВЧ LDMOS транзисторных структур согласно изобретению, где введены следующие обозначения:

1 - исходная кремниевая р-р+-подложка;

2 - толстый полевой диэлектрик на периферии транзисторных структур;

3 - диффузионные истоковые р+-перемычки транзисторных ячеек в высокоомном р--слое подложки;

4, 5, 6 - первая, вторая и третья ступени слаболегированной n-области стока транзисторных ячеек соответственно;

7 - дополнительная диэлектрическая защитная маска, сформированная на поверхности эпитаксиального р--слоя подложки;

8 - защитный слой фоторезиста над слаболегированной n-областью стока транзисторных ячеек;

9, 9′ - р-карманы транзисторных ячеек после внедрения в высокоомный р--слой подложки ионов акцепторной примеси и соответственно после диффузионной разгонки внедренной примеси;

10 - аналогичные р-карманам области, сформированные одновременно с ними на торцах слаболегированной n-области стока транзисторных ячеек, контактирующих с толстым полевым диэлектриком транзисторной структуры;

11 - защитный слой фоторезиста;

12, 13 - контактные окна стока и истока, вскрытые в защитном слое фоторезиста (11);

14, 15 - высоколегированные n+-области стока и истока транзисторных ячеек соответственно;

16 - подзатворный диэлектрик;

17 - продольные зубцы поликремниевого или полицидного электрода затвора транзисторных ячеек;

18 - примыкающие к продольным затворным зубцам со стороны истока ответвленные контактные площадки;

19 - межслойный диэлектрик;

20, 21, 22 - контактные окна, вскрытые в межслойном диэлектрике, соответственно над высоколегированными n+-областями стока, истока и ответвленными площадками поликремниевого или полицидного электрода затвора транзисторных ячеек;

23, 24 - металлические электроды стока и истока транзисторных ячеек;

25 - металлические шины, шунтирующие продольные зубцы поликремниевого или полицидного электрода затвора транзисторных ячеек через примыкающие к ним со стороны истока ответвленные контактные площадки;

26 - металлические экранирующие электроды транзисторных ячеек;

27 - общий металлический электрод истока транзисторной структуры на тыльной стороне подложки;

28 - индуцированный n-канал.

Пример

Используя специально разработанный комплект фотошаблонов, были изготовлены образцы транзисторных структур по заявляемому способу размером 1,0 мм × 4,2 мм с индуцированным n-каналом и слаболегированной трехступенчатой n-областыо стока транзисторных ячеек длиной Lк=0,75 мкм и Ln--=4,5 мкм соответственно и суммарной протяженностью (шириной) канала Wк=78,7 мм, положенных в основу мощных кремниевых СВЧ LDMOS транзисторов, рассчитанных на диапазон рабочих частот до 2,0 ГГц.

Способ осуществляют следующим образом:

1. Ha поверхности высокоомного эпитаксиального р--слоя (ρρ-=8…12 Ом·см, hρ-=6…8 мкм) исходной кремниевой р-р+-подложки (1) локальным термическим окислением кремния формируют толстый полевой диэлектрик (2) на периферии транзисторных структур, имплантацией ионов бора и последующим диффузионным перераспределением внедренной примеси создают сквозные истоковые р+-перемычки (3) транзисторных ячеек в объеме эпитаксиального р--слоя подложки, не покрытом толстым полевым диэлектриком (2), и последующим внедрением ионов фосфора в эпитаксиальный слой подложки без использования защитных масок формируют первую ступень слаболегированной n-области стока (4) транзисторных ячеек - фиг.1.

2. Внедрением ионов фосфора в подложку с последовательно возрастающей дозой при использовании слоев фоторезиста в качестве защитной маски создают вторую (5) и третью (6) ступени слаболегированной n-области стока транзисторных ячеек, термическим окислением кремния выращивают диоксид кремния на поверхности эпитаксиального слоя, формируют из выращенного диоксида кремния методом фотолитографии на месте будущей дислокации продольных зубцов поликремниевого или полицидного электрода затвора транзисторных ячеек дополнительную диэлектрическую защитную маску (7), покрывают слаболегированную n-область стока транзисторных ячеек защитным слоем фоторезиста (8), имплантацией ионов бора в подложку формируют р-карманы транзисторных ячеек (9) и одновременно с ними аналогичные р-области (10) на торцах слаболегированной n-области стока транзисторных ячеек, примыкающих к толстому полевому диэлектрику (2) транзисторной структуры - фиг.2, 3.

3. После удаления защитного слоя фоторезиста (8) с лицевой поверхности подложки проводят диффузионную разгонку акцепторной примеси в р-карманах (9′) - фиг.4, наносят новый слой фоторезиста (11) на лицевую сторону подложки, методом фотолитографии вскрывают в нем контактные окна (12) и (13) и имплантацией донорной примеси (Р, As,) в подложку через контактные окна создают высоколегированные n+-области стока (14) и истока (15) транзисторных ячеек - фиг.5.

4. Удаляют фоторезист (11) и дополнительную диэлектрическую защитную маску (7) с лицевой поверхности подложки, термическим окислением кремния выращивают подзатворный диэлектрик (16) на поверхности эпитаксиального слоя подложки, покрывают подзатворный диэлектрик слоем поликремния, легированного фосфором, формируют из него методом фотолитографии над торцами р-карманов (9′) продольные затворные зубцы транзисторных ячеек (17) совместно с примыкающими к затворным зубцам со стороны истока ответвленными контактными площадками (18), осаждают на лицевую сторону подложки межслойный диэлектрик (19), методом фотолитографии вскрывают в межслойном диэлектрике контактные окна (20), (21), (22) соответственно над высоколегированными n+-областями стока, истока и ответвленными контактными площадками (18) поликремниевого электрода затвора транзисторных ячеек - фиг.6.

5. Наносят на межслойный диэлектрик (19) однослойное или многослойное металлическое покрытие и методом фотолитографии формируют из него электроды стока (23), истока (24), шунтирующие шины поликремниевого электрода затвора (25) и экраны (26) транзисторных ячеек. Общий электрод истока транзисторной структуры (27) на тыльной стороне подложки создавался при напайке кристалла на теплоотводящую поверхность металлокерамического корпуса с помощью золотой прокладки, а индуцированный n-канал (28) образовывался на торцах р-карманов (9′), прилегающих к подзатворному диэлектрику (16) при приложении положительного напряжения к электроду затвора транзисторной структуры.

Выход годных транзисторных структур (кристаллов) на пластине, изготовленных по заявляемому способу, составил около 40%. Годные кристаллы, смонтированные в металлокерамическом корпусе типа КТ-25, имели следующие параметры: пробивное напряжение стока Uc пpoб=80 B (Uзи=0, Iс=2 мА); ток стока Iс=8,0 А (Uзи=15 В, Ucи=10 В); пороговое напряжение Uзи пор=2,8…5,0 В (Uси=10 В, Iс=20 мА); проходная емкость C12=1,82 пФ (f=1 МГц, Uзи=0, Uси=30 В); энергетические параметры, измеренные на частоте 2000 МГц, в режиме класса АВ при напряжении питания по стоку Uc пит=40 В - выходная мощность Рвых=38 Вт, коэффициент усиления по мощности Кур=9,5 дБ, коэффициент полезного действия стоковой цепи ηс=39%; сдвиг порогового напряжения при воздействии гамма-излучения дозой Dγ=105 рад - ΔUзи пор≤0,4 В.

Сопоставляя приведенные параметры с аналогичными параметрами известных СВЧ LDMOS транзисторов, имеющих приблизительно такие же конструктивные и электрофизические параметры базового кристалла и рассчитанного на тот же диапазон рабочих частот и отдаваемых в нагрузку мощностей, можно сделать следующие выводы:

1. Заявляемый способ позволяет создавать мощные кремниевые СВЧ LDMOS транзисторы, сопоставимые с современными зарубежными аналогами по основным электрическим параметрам, но с более высокими по сравнению с ними пробивными напряжениями стока и более высокой стойкостью к воздействию ионизирующих излучений.

2. Формирование в заявляемом способе одновременно с р-карманами аналогичных областей на торцах слаболегированных n-областей стока транзисторных ячеек, примыкающих к толстому полевому диэлектрику транзисторной структуры, позволяет при прочих равных условиях на 14÷15 В увеличить пробивное напряжение стока СВЧ LDMOS транзисторов, а следовательно, и обеспечить возможность их работы при напряжениях питания по стоку Uc пит=40 В и выше.

3. Заявляемый способ позволяет существенно упростить технологический процесс изготовления мощных кремниевых СВЧ LDMOS транзисторов и на более доступном технологическом оборудовании обеспечить высокий процент выход годных структур на пластине.

Технико-экономическая эффективность предлагаемого способа состоит в возможности улучшения электрических параметров, повышения пробивных напряжений стока, увеличения напряжения питания по стоку, радиационной стойкости и процента выхода годных транзисторных структур на пластине серийно выпускаемых мощных кремниевых СВЧ LDMOS транзисторов и создания на их основе радиоэлектронной аппаратуры нового поколения с более высокими технико-экономическими характеристиками.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ | 2013 |

|

RU2535283C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ С МОДЕРНИЗИРОВАННЫМ ЗАТВОРНЫМ УЗЛОМ ЭЛЕМЕНТАРНЫХ ЯЧЕЕК | 2016 |

|

RU2639579C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ | 2012 |

|

RU2515124C1 |

| МОЩНЫЙ СВЧ LDMOS ТРАНЗИСТОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2011 |

|

RU2473150C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS ТРАНЗИСТОРОВ | 2012 |

|

RU2498448C1 |

| СВЧ LDMOS-ТРАНЗИСТОР | 2007 |

|

RU2338297C1 |

| КОНСТРУКЦИЯ ДИСКРЕТНОГО СВЧ LDMOS-ТРАНЗИСТОРНОГО КРИСТАЛЛА С УСОВЕРШЕНСТВОВАННОЙ ЭКРАНИРУЮЩЕЙ ШИНОЙ ИСТОКА | 2024 |

|

RU2819579C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ МОЩНЫХ ПОЛЕВЫХ LDMOS ТРАНЗИСТОРОВ | 2008 |

|

RU2364984C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS-ТРАНЗИСТОРНЫХ КРИСТАЛЛОВ С МНОГОСЛОЙНОЙ ДРЕЙФОВОЙ ОБЛАСТЬЮ СТОКА | 2024 |

|

RU2819581C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2006 |

|

RU2361318C2 |

Изобретение относится к электронной полупроводниковой технике и направлено на улучшение электрических параметров СВЧ мощных кремниевых генераторных LDMOS транзисторов, повышение их стойкости к воздействию ионизирующих излучений и повышение процента выхода годных изделий. Сущность изобретения: в способе изготовления СВЧ LDMOS транзисторов, включающем выращивание толстого полевого диэлектрика на поверхности высокоомного эпитаксиального р--слоя исходной кремниевой р-p+-подложки на периферии транзисторных структур, формирование истоковых р+-перемычек и р-карманов транзисторных ячеек в эпитаксиальном p--слое подложки, не покрытом полевым диэлектриком, выращивание подзатворного диэлектрика и формирование поликремниевых электродов затвора транзисторных ячеек в виде узких продольных зубцов прямоугольного сечения с рядом прилегающих к ним со стороны истока ответвленных контактных площадок над р-карманами, создание высоколегированных n+-областей стока, истока и слаболегированной n-области стока транзисторных ячеек посредством внедрения в подложку и последующего диффузионного перераспределения донорной примеси с использованием электродов затвора в качестве защитной маски, формирование металлических электродов стока, истока, экранов и шин, шунтирующих электроды затвора транзисторных ячеек через ответвленные контактные площадки на лицевой стороне подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне, первую ступень слаболегированной многоступенчатой n-области стока транзисторных ячеек формируют после образования истоковых р+-перемычек посредством внедрения донорной примеси в эпитаксиальный р--слой подложки без использования защитных масок, р-карманы, стоковые и истоковые области транзисторных ячеек создают с помощью дополнительной диэлектрической защитной маски, идентичной по конфигурации и местоположению продольным зубцам поликремниевого электрода затвора без примыкающих к ним ответвленных контактных площадок, одновременно с р-карманами формируют аналогичные им области на торцах слаболегированной n-области стока транзисторных ячеек, а электроды затвора с прилегающими к зубцам ответвленными контактными площадками формируют после удаления дополнительной диэлектрической защитной маски и последующего выращивания подзатворного диэлектрика, при этом ширину зубцов поликремниевого электрода затвора выбирают такой, чтобы она на величину погрешности совмещения превышала длину индуцированного канала транзисторных ячеек. 7 ил.

Способ изготовления СВЧ LDMOS транзисторов, включающий выращивание толстого полевого диэлектрика на поверхности высокоомного эпитаксиального p--слоя исходной кремниевой p-p+-подложки на периферии транзисторных структур, формирование истоковых р+-перемычек и р-карманов транзисторных ячеек в эпитаксиальном p--слое подложки непокрытым полевым диэлектриком, выращивание подзатворного диэлектрика и формирование поликремниевых электродов затвора транзисторных ячеек в виде узких продольных зубцов прямоугольного сечения с рядом прилегающих к ним со стороны истока ответвленных контактных площадок над р-карманами, создание высоколегированных n+-областей стока, истока слаболегированной n-области стока транзисторных ячеек посредством внедрения в подложку и последующего диффузионного перераспределения донорной примеси с использованием электродов затвора в качестве защитной маски, формирование металлических электродов стока, истока, экранов и шин, шунтирующих электроды затвора транзисторных ячеек через ответвленные контактные площадки на лицевой стороне подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне, отличающийся тем, что первую ступень слаболегированной многоступенчатой n-области стока транзисторных ячеек формируют после образования истоковых р+-перемычек посредством внедрения донорной примеси в эпитаксиальный р--слой подложки без использования защитных масок, р-карманы, стоковые и истоковые области транзисторных ячеек создают с помощью дополнительной диэлектрической защитной маски, идентичной по конфигурации и местоположению продольным зубцам поликремниевого электрода затвора без примыкающих к ним ответвленных контактных площадок, одновременно с р-карманами формируют аналогичные им области на торцах слаболегированной n-области стока транзисторных ячеек, примыкающих к толстому полевому диэлектрику транзисторной структуры, а электроды затвора транзисторных ячеек с прилегающими к зубцам ответвленными контактными площадками формируют после удаления дополнительной диэлектрической защитной маски и последующего выращивания подзатворного диэлектрика, при этом ширину зубцов поликремниевого электрода затвора выбирают такой, чтобы она на величину погрешности совмещения превышала длину индуцированного канала транзисторных ячеек.

| Isao Yoshida | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Электрическое сопротивление для нагревательных приборов и нагревательный элемент для этих приборов | 1922 |

|

SU1997A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ МОЩНЫХ ПОЛЕВЫХ LDMOS ТРАНЗИСТОРОВ | 2008 |

|

RU2364984C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПЛАНАРНОГО СИЛОВОГО МОП ТРАНЗИСТОРА | 2002 |

|

RU2239912C2 |

| US 6707102 B2, 16.03.2004 | |||

| US 7282765 B2, 16.10.2007 | |||

| US 6800528 B2, 05.10.2004. | |||

Авторы

Даты

2012-01-10—Публикация

2010-07-22—Подача