Изобретение относится к электронной полупроводниковой технике, в частности к конструкциям мощных кремниевых генераторных СВЧ LDMOS (Lateral Diffused Metal Oxide Semiconductor) транзисторов.

Известна конструкция мощного кремниевого n-канального СВЧ LDMOS-транзистора, выбранная в качестве аналога (LDMOS Family. New RF 1GHz LDMOS. - Информационное сообщение фирмы «STMicroelectronics», 2000 г - http://www.st.com/ST/Products Presentation/Discrete/RF/LDMOS), включающая в свой состав: кремниевую p-p+- подложку с верхним высокоомным (р-) и нижним высоколегированным (р+) слоями; элементарные транзисторные ячейки с р-канальной, высоколегированной n+- истоковой, высоколегированной n+-стоковой и слаболегированной n-стоковой областями в высокоомном слое подложки; идентичный по толщине слой термической двуокиси кремния над р-канальными (подзатворный диэлектрик) и слаболегированными стоковыми n-областями транзисторных ячеек; электроды затвора в виде узких прямоугольных поликремниевых полос, зашунтированных сверху силицидом кобальта (CoSi2) над подзатворным диэлектриком и р-канальными областями транзисторных ячеек; межслойный диэлектрик из фосфорносиликатного или борофосфорносиликатного стекла над электродами затвора и термической двуокисью кремния, покрывающей слаболегированные стоковые n-области транзисторных ячеек; металлические электроды стока и истока транзисторных ячеек на лицевой стороне подложки; экранирующие электроды на межслойном диэлектрике, простирающиеся над электродами затвора и частично над слаболегированными стоковыми n-областями, конструктивно выполненные как продолжение электродов истока транзисторных ячеек; сквозные диффузионные р+-перемычки в высокоомном p--слое подложки под электродом истока транзисторных ячеек; общий электрод истока транзисторной структуры на тыльной стороне подложки. Введенный в транзисторные ячейки дополнительный полевой экранирующий электрод предназначен для повышения пробивных напряжений стока за счет выравнивания потенциала и снижения максимальной напряженности поля в области отсечки слаболегированного стокового n-слоя и одновременно для уменьшения проходной (сток-затвор) емкости. Однако при этом резко возрастает вероятность появления дополнительных закороток и токов утечки между экранирующим и затворным электродами транзисторных ячеек, что является существенным недостатком данной конструкции.

Известна другая конструкция мощного кремниевого СВЧ LDMOS-транзистора (второй аналог), в которой указанный выше недостаток в значительной степени преодолен за счет того, что полевые экранирующие электроды контактируют только с одним торцом электродов истока за пределами электродов затвора и перекрывают лишь периферийную часть затворных полос (O.Ishikawa, H.Yamada, H.Ecaki. «A 2,45 GHz power LD-MOSFET with reduced source inductance by V-groove connections» - сборник статей «International Electron Devices Meeting», Washington, 1985, December 1-4, p.167-169).

В качестве прототипа выбран мощный кремниевый СВЧ LDMOS-транзистор (Richmond Road «Philips BLF 2022-90 Power MOSFET Structural Analysis» - Suite 500, Ottawa, ONK2H5B7, Canada, June 17, 2004) с идентичным аналогам набором основных конструктивных элементов, в котором поликремниевые электроды затвора транзисторных ячеек зашунтированы сверху металлизационным покрытием на основе золота (материал электродов стока и истока), а полевые экранирующие электроды выполнены из того же металлизационного покрытия и размещены на межслойном диэлектрике из борофосфорно-силикатного стекла над слаболегированной областью стока приблизительно на одинаковом расстоянии от электродов стока и истока. То есть в прототипе экранирующие и затворные электроды полностью не перекрываются друг с другом на всем их протяжении, и поэтому он лишен вышеупомянутого недостатка аналогов. Однако для прототипа и аналогов наиболее серьезной технической проблемой является сложность обеспечения стабильности параметров, обусловленная вероятностью дрейфа ионов щелочных металлов или других нежелательных примесей вдоль границы раздела термическая двуокись кремния - межслойный диэлектрик над слаболегированной областью стока транзисторных ячеек. Для избежания возможности проявления этого негативного эффекта при использовании данных приборов в радиоэлектронной аппаратуре приходится ограничивать их предельно-допустимые значения электрических параметров и режимов эксплуатации (температуры структуры, рассеиваемой мощности, выходной мощности, напряжения питания и т.д.). Этот эффект приводит также к снижению процента выхода годных структур на пластине и годных пластин в партии, повышению себестоимости продукции и, как результат, препятствует организации рентабельного промышленного выпуска данных изделий.

Технический результат настоящего изобретения - повышение предельно-допустимых значений электрических параметров и режимов эксплуатации СВЧ LDMOS-транзисторов и обеспечение условий для организации рентабельного промышленного выпуска данных изделий.

Технический результат достигается тем, что в известной конструкции СВЧ LDMOS-транзистора, содержащей полупроводниковую подложку с высокоомным и высоколегированным слоями первого типа проводимости, элементарные транзисторные ячейки в высокоомном слое подложки с канальной областью первого типа проводимости, высоколегированной истоковой, высоколегированной и слаболегированной стоковой областями второго типа проводимости, подзатворный диэлектрик из термической двуокиси кремния и электрод затвора над канальной областью транзисторных ячеек, термическую двуокись кремния и межслойный диэлектрик над слаболегированной стоковой областью транзисторных ячеек, электроды стока и истока транзисторных ячеек на лицевой стороне подложки, полевые экранирующие электроды в промежутке между электродами стока и затвора, соединенные с одним из торцов истока транзисторных ячеек за пределами электродов затвора, общий электрод истока транзисторной структуры на тыльной стороне подложки, полевые экранирующие электроды транзисторных ячеек выполнены из материала электрода затвора и размещены на границе раздела термическая двуокись кремния - межслойный диэлектрик, причем толщина термической двуокиси кремния над слаболегированной областью стока составляет (1,0...3,5) толщины подзатворного диэлектрика, а граница сопряжения подзатворного диэлектрика и слоя термической двуокиси кремния над слаболегированной стоковой областью расположена под электродом затвора.

Сопоставительный анализ с прототипом показывает, что заявляемая конструкция отличается: новым материалом, из которого изготовлены полевые экранирующие электроды транзисторных ячеек; новым местоположением полевых экранирующих электродов в активной области транзисторной структуры; новым, строго регламентируемым соотношением между толщинами подзатворного диэлектрика и термической двуокиси кремния над слаболегированной областью стока транзисторных ячеек; наличием дополнительной границы сопряжения между подзатворным диэлектриком и слоем термической двуокиси кремния над слаболегированной стоковой областью транзисторных ячеек и ее строго регламентированным расположением в активной области транзисторной структуры. Таким образом, заявляемая конструкция соответствует критерию изобретения «новизна».

Выполнение полевых экранирующих электродов из материала электродов затвора (в прототипе и аналогах - из материала электродов стока и истока) позволяет разместить экранирующие электроды не на межслойном диэлектрике (как в прототипе и аналогах), а на границе раздела термическая двуокись кремния - межслойный диэлектрик над слаболегированной областью стока транзисторных ячеек.

Выполнение экранирующих и затворных электродов из одного и того же материала, размещение экранирующих электродов на границе раздела термическая двуокись кремния - межслойный диэлектрик, в совокупности с пассивацией термической двуокиси кремния над слаболегированной стоковой областью фосфорносиликатным стеклом и возможной дополнительной стабилизацией термической двуокиси кремния посредством внедрения в нее низкоэнергетических ионов фосфора или мышьяка, позволяют свести к нулю вероятность дрейфа ионов щелочных металлов или других нежелательных примесей между электродами стока и затвора транзисторных ячеек вдоль границы раздела термическая двуокись кремния - межслойный диэлектрик и избавиться таким образом от основного недостатка прототипа и конструкций-аналогов.

Регламентируемый формулой изобретения диапазон соотношений между толщинами позатворного диэлектрика и термической двуокиси кремния над слаболегированной областью стока транзисторных ячеек, во-первых, обеспечивает возможность проведения эффективной стабилизации указанных слоев термической двуокиси кремния фосфорносиликатным стеклом в едином технологическом процессе и, во-вторых, при частичном выходе электродов затвора на более толстый (в предельном случае до 3,5 раз) по сравнению с подзатворным диэлектриком слой термической двуокиси кремния над слаболегированной стоковой областью транзисторных ячеек позволяет избежать обрывов затворных электродов на ступеньках окисла на границе сопряжения тонкого и толстого диэлектриков. Минимальная толщина термической двуокиси кремния над слаболегированной стоковой областью зависит от ее диэлектрической прочности (106...107 В/см) и должна исключать возможность пробоя диэлектрика под экранирующими электродами при подаче на стоковый переход максимально-допустимого для транзисторной структуры напряжения сток-исток Uси макс. Так, при диэлектрической прочности двуокиси кремния ЕSiO2=3·106 В/см и Uси макс=80 В минимальная толщина термической двуокиси кремния над слаболегированной стоковой областью dSiO2 мин должна быть на менее 0,27 мкм. При ESiO2=8·106 В/см и Uси макс=80 В dSiO2 мин≅0,1 мкм и в этом случае термическая двуокись кремния над канальной и слаболегированной стоковой областями транзисторных ячеек может быть сформирована одинаковой по толщине в едином технологическом процессе.

Регламентированное формулой изобретения местоположение границы сопряжения подзатворного диэлектрика со слоем термической двуокиси кремния над слаболегированной областью стока транзисторных ячеек продиктовано тем, чтобы свести к минимуму емкость затвор-сток транзисторной структуры и не ухудшить тем самым ее коэффициент усиления по мощности.

В предлагаемом изобретении новый материал, из которого изготовлены полевые экранирующие электроды транзисторных ячеек, новое местоположение экранирующих электродов в активной области транзисторной структуры, новое соотношение между толщинами подзатворного диэлектрика и термической двуокиси кремния над слаболегированной стоковой областью транзисторных ячеек, строго регламентированное расположение границы сопряжения между подзатворным диэлектриком и слоем термической двуокиси кремния над слаболегированной стоковой областью транзисторных ячеек, обеспечивают возможность создания мощных кремниевых СВЧ LDMOS-транзисторов с идентичными прототипу и аналогам частотными свойствами и энергетическими параметрами (отдаваемой в нагрузку мощностью Рвых, коэффициентом усиления по мощности Кур, коэффициентом полезного действия стоковой цепи ηc), но обладающих по сравнению с ними более высокой эксплуатационной надежностью и более высокими предельно-допустимыми значениями электрических параметров и режимов эксплуатации, то есть проявляет новое техническое свойство. Следовательно, заявляемая конструкция соответствует критерию «изобретательский уровень».

Данное изобретение также существенно, так как оно обеспечивает значительный технический эффект, заключающийся в возможности организации устойчивого рентабельного промышленного выпуска мощных кремниевых СВЧ LDMOS-транзисторов с рабочими частотами до 2,0...2,5 ГГц и уровнем отдаваемых в нагрузку мощностей до 100...200 Вт, открывающих новые перспективы в решении важнейших задач комплексной микроминиатюризации радиоэлектронной аппаратуры, улучшении ее технико-экономических и массогабаритных характеристик.

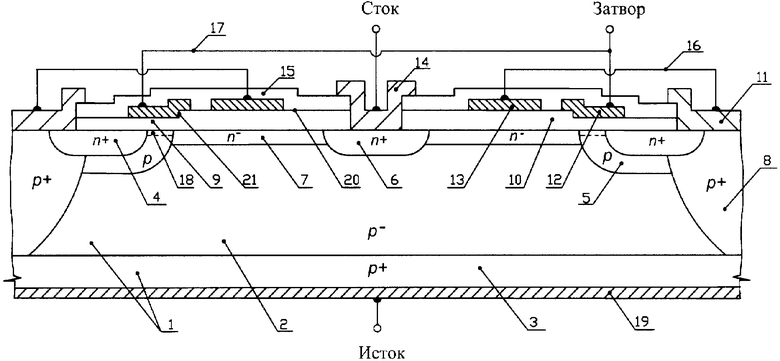

На чертеже изображено поперечное сечение структуры заявляемого СВЧ LDMOS-транзистора согласно изобретению, где введены следующие обозначения:

1 - полупроводниковая подложка;

2 - высокоомный слой подложки;

3 - высоколегированный слой подложки;

4 - высоколегированные истоковые области транзисторных ячеек;

5 - канальные области транзисторных ячеек;

6 - высоколегированные стоковые области транзисторных ячеек;

7 - слаболегированные стоковые области транзисторных ячеек;

8 - сквозные высоколегированные диффузионные перемычки в высокоомном слое подложки;

9 - подзатворный диэлектрик из термической двуокиси кремния;

10 - слой термической двуокиси кремния над слаболегированной областью стока транзисторных ячеек;

11 - электрод истока транзисторных ячеек;

12 - электрод затвора транзисторных ячеек;

13 - полевой экранирующий электрод транзисторных ячеек;

14 - электрод стока транзисторных ячеек;

15 - межслойный диэлектрик из фосфорносиликатного или борофосфорносиликатного стекла;

16 - металлические шины, соединяющие торцевые части экранирующих и истоковых электродов транзисторных ячеек за пределами электродов затвора;

17 - металлические шины, соединяющие электроды затвора транзисторных ячеек в единую систему;

18 - индуцированный канал;

19 - общий электрод истока транзисторной структуры;

20 - граница раздела термическая двуокись кремния - межслойный диэлектрик над слаболегированной областью стока транзисторных ячеек;

21 - граница сопряжения позатворного диэлектрика со слоем термической двуокиси кремния над слаболегированной областью стока транзисторных ячеек.

Пример

Для реализации заявляемой конструкции и прототипа в конкретных изделиях был спроектирован комплект фотошаблонов A3926 и на его основе изготовлены образцы мощных кремниевых генераторных n-канальных СВЧ LDMOS-транзисторов с шагом структуры 38 мкм (в данном случае под шагом структуры подразумевается расстояние между центрами высоколегированных n+-истоковых или n+-стоковых областей транзисторных ячеек) и длиной индуцированного n-канала Lкан=0,85...0,9 мкм, рассчитанных на работу в диапазоне частот до 2,0...2,5 ГГц в режиме класса АВ в схеме с общим истоком при напряжении питания по стоку Uc пит=28...40 В. Те и другие приборы изготавливались одновременно в едином технологическом процессе с использованием в качестве исходного материала кремниевых р-p+-подложек ориентации (100) с верхним высокоомным эпитаксиальным р--слоем (2) толщиной hp-=6,5...7,0 мкм и удельным сопротивлением ρp-=15...17 Ом·см и нижним высоколегированным p+-слоем с hp+=380...400 мкм и ρр+=0,03 Ом·см. Высоколегированные истоковые (4) и стоковые (6) n+-области транзисторных ячеек толщиной 0,25...0,4 мкм и 0,8...1,0 мкм создавались внедрением в подложку ионов мышьяка и фосфора, р-канальные области (5) - имплантацией ионов бора, слаболегированные стоковые n--области (7) толщиной 0,25...0,5 мкм - имплантацией ионов мышьяка и фосфора, высоколегированные сквозные истоковые p+-перемычки (8) в высокоомном р--слое подложки (2) - загонкой бора из твердого источника (нитрида бора) с последующей диффузионной разгонкой примеси в среде азота и кислорода при температуре 1100°С. Подзатворный диэлектрик (9) из термической двуокиси кремния толщиной 0,08...0,15 мкм и слой двуокиси кремния (10) над слаболегированной n--областью стока элементарных ячеек (7) толщиной 0,15...0,4 мкм (в заявляемом СВЧ LDMOS-транзисторе) формировались посредством термического окисления кремния в среде сухого кислорода и паров воды при Т=975°С с последующей одновременной пассивацией диэлектриков (9) и (10) фосфорносиликатным стеклом (диффузией фосфора из метафосфата алюминия при Т=970°С в среде азота). В прототипе слой двуокиси кремния (10) формировался одновременно с подзатворным диэлектриком (9) и являлся его естественным продолжением. Электроды затвора (12) транзисторных ячеек и экранирующие электроды (13) [в заявляемой конструкции LDMOS-транзистора] в виде узких продольных полос шириной 2,7...3,0 мкм, толщиной 0,2...0,25 мкм и длиной 74 мкм создавались одновременно из предварительно нанесенного на лицевую сторону подложки магнетронного молибдена методом фотолитографии. Электроды затвора (12) в заявляемом LDMOS-транзисторе частично (на 0,4...0,8 мкм) выходили на слой термической двуокиси кремния (10), а граница сопряжения последнего с подзатворным диэлектриком (21) располагалась под электродами затвора (12) и на 0,1...0,3 мкм отстояла от р-канальной области (5) транзисторных ячеек. Экранирующие электроды (13) в заявляемой конструкции размещались на границе раздела (20) термическая двуокись кремния (10) - межслойный диэлектрик (15), причем межслойный диэлектрик (15) толщиной 0,5...0,6 мкм состоял из пиролитической двуокиси кремния и фосфорносиликатного стекла. Электроды истока (11) и стока (14) транзисторных ячеек, шины (16), соединяющие торцы истоковых и экранирующих электродов, соединительные затворные шины (17), соединительные стоковые шины, контактные площадки стока и затвора (на чертеже не показаны), а также экранирующие электроды (13) в прототипе изготавливались одновременно из предварительно нанесенного на лицевую сторону подложки однослойного алюминиевого или трехслойного Ti-Pt-Au покрытия толщиной 1,0...1,5 мкм методом фотолитографии. Экранирующие электроды (13) в прототипе размещались не на границе раздела (20), а на межслойном диэлектрике (15) под верхним защитным диэлектрическим покрытием (на чертеже не показанным). Общий электрод истока транзисторной структуры (19) формировался после утонения кристалла до толщины 120...150 мкм и его напайке на теплоотводящую поверхность металлокерамического корпуса КТ-25 с помощью золотой прокладки толщиной 20 мкм при температуре 400...430°С в среде инертного газа. Канал n-типа проводимости (18) индуцировался на торцах р-канальных областей (5), примыкающих к лицевой поверхности транзисторной структуры, при подаче положительного напряжения на электрод затвора. В заявляемой конструкции и прототипе транзисторная структура размером 1,6 мм × 4,2 мм включала в свой состав 40 пакетов элементарных транзисторных ячеек, разделенных друг от друга толстым (2,0...2,5 мкм) слоем термической двуокиси кремния, 11 стоковых и 10 затворных площадок, размещенных на толстом диэлектрическом покрытии в промежутках между пакетами транзисторных ячеек и предназначенных для присоединения к кристаллу внешних проволочных выводов. Каждый пакет транзисторных ячеек содержал 24 электрода затвора (12), суммарная протяженность которых составляла ˜1780 мкм. Суммарная протяженность электродов затвора всего кристалла (ширина канала) составляла ˜7,2 см.

Электрические параметры изготовленных LDMOS-структур (заявляемая конструкция, прототип) с различным сочетанием толщин термической двуокиси кремния над р-канальными [dSiO2(p)] и слаболегированными п--стоковыми [dSiO2(п-)] областями элементарных транзисторных ячеек, измеренные непосредственно на пластинах, представлены в таблице 1. На LDMOS - структурах до и после воздействия вначале 1-ой (Uси=40 В, Uзи=0, температура окружающей среды Токр=150°С, время выдержки t=3 мин), а затем 2-ой (Uси=80 В, Uзи=0, Токр=150°С, t=3 мин) ступеней нагрузки, измерялись: пробивное напряжение стокового рп--перехода (Uс проб) при напряжении затвор-исток Uзи=0 по уровню тока стока Iс=3 мА; начальный ток стока (1 с нач) при напряжении сток-исток Uси=40 В и Uзи=0; пороговое напряжение (Uзи пор) при напряжении Uси=20 В и Iс=3 мА; остаточное напряжение сток-исток (Uc ост) при Uси=20 В и Ic=1 А. Предварительно на пластинах забраковывались все LDMOS - структуры с токами утечки затвора Iз ут>10-8 А, нестабильным затворным узлом (нестабильность оценивалась по сдвигу порогового напряжения при воздействии на структуру тепловых и электрических нагрузок) и значениями параметров Uc проб, I с нач, Uзи пор, Uc ост, отличными от указанных в таблице 1. В процессе испытаний выявлено:

1. При регламентированных формулой изобретения соотношениях толщин dSiO2(п-)/dSiO2(p)=1,0...3,5 тестируемые параметры Uc проб, Ic нач, Uзи пор, Uc ост заявляемых LDMOS - структур после воздействия двух ступеней нагрузки оставались неизменными.

2. Соотношение толщин dSiO2(п-)/dSiO2(p)>3,5 в заявляемой конструкции LDMOS - транзистора не является оптимальным (из-за сложности одновременной пассивации подзатворного диэлектрика и термической двуокиси кремния над слаболегированной стоковой п--областью транзисторных ячеек фосфорносиликатным стеклом), так как в этом случае после воздействия 1-ой и 2-ой ступеней нагрузки у 8,0...15% тестируемых структур (в таблице 1 помечены *) проявлялась тенденция к 10...15% росту величины Uc ост по отношению к исходному значению данного параметра. При этом на некоторых структурах наблюдался обрыв металлизации электродов затвора на ступеньках окисла на границе сопряжения тонкого и толстого слоев термической двуокиси кремния.

3. После воздействия нагрузки у всех тестируемых LDMOS - структур прототипа величина остаточного напряжения сток-исток возрастала минимум на 10...15% по отношению к исходному значению Uс ост, а у 15-ти процентов структур после 1-ой ступени нагрузки и 35-ти процентов структур после 2-ой ступени нагрузки (в таблице 1 помечены *) Uс ост возросло соответственно в 1,47 и 1,65 раза.

Для проведения дальнейших исследований были отобраны и смонтированы в малогабаритном металлокерамическом корпусе с полосковыми выводами и плоским фланцем типа КТ-25 шестьдесят образцов LDMOS-структур заявляемой конструкции с соотношением толщин термической двуокиси кремния dSiO2(п-)/dSiO2(p)=1,0; 2,5; 3,5 (по 20 штук каждого типономинала) и 40 образцов LDMOS-структур прототипа с dSiO2(p)=dSiO2(п-)=1000 Å (20 штук) и с dSiO2(p)=dSiO(п-)=1500 Å (20 штук), у которых уход величины остаточного напряжения сток-исток после 2-ой ступени нагрузки относительно исходного значения Uс ост составил не более 15%. Собранные приборы подвергались воздействию 4-х ступеней нагрузки и непосредственно после каждой из них на приборах измерялись: ток стока Iс при напряжениях Uси=15 В и Uзи=20 В; сопротивление сток-исток в открытом состоянии (Rси отк) при напряжениях Uзи=20 В и Uси=1 В; энергетические параметры - выходная мощность Рвых, коэффициент усиления по мощности Кур (дБ), коэффициент полезного действия стоковой цепи ηс (%) на частоте f=1000 МГц при напряжении питания Uс пит=40 Вт в режиме класса АВ в схеме с общим истоком. Предварительно на приборах измерялось тепловое сопротивление переход - корпус (Rтпк), которое в данном случае равнялось ˜2,3°С/Вт. На каждой ступени нагрузки LDMOS - транзисторы выдерживались в течении t=10 минут при напряжении сток-исток Uси=40 В, температуре корпуса Ткорп=20°С, а ток нагрузки Iсн или эквивалентная ему величина рассеиваемой транзистором мощности Ррасс=Uси·Iсн выбирались такими, чтобы исходя из известного соотношения Iсн=(Тстр-Ткорп)/Uси·Rтпк температура структуры (кристалла) Тстр достигала 150°С, 170°С, 190°С и 210°С соответственно на 1-ой, 2-ой, 3-ей и 4-ой ступенях нагрузки.

Из представленных в таблице 2 результатов испытаний можно сделать следующие выводы:

1. В LDMOS-транзисторах заявляемой конструкции тестируемые параметры - Iс, Rси отк, Рвых остаются неизменными после воздействия всех 4-х ступеней нагрузки и поэтому для них в качестве максимально-допустимой вполне может быть принята температура структуры Тстр макс=200°С.

2. В LDMOS-транзисторах прототипа тестируемые параметры - Рвых, Iс, Rси отк начинают деградировать при температуре структуры Тстр=170°С, а после воздействия 4-ой ступени нагрузки (Тстр=210°С) эти параметры изменяются относительно своих значений при Тстр=150°С приблизительно в 1,26...1,31 раза. Поэтому для прототипа в качестве максимально-допустимой может быть принята температура структуры Тстр макс≤150°С.

Коэффициент усиления по мощности (Кур) и коэффициент полезного действия стоковой цепи (ηс) у тестируемых образцов прототипа и LDMOS - транзисторов заявляемой конструкции были сопоставимыми - Кур=13...14 дБ, ηс=43...44% (в таблице 2 не указаны).

Технико-экономическая эффективность предложенной конструкции по сравнению с прототипом состоит:

- в возможности повышения предельно-допустимых значений электрических параметров и режимов эксплуатации (температуры структуры, мощности рассеяния, выходной мощности) мощных СВЧ LDMOS-транзисторов;

- в возможности снижения себестоимости и повышения процента выхода годных LDMOS-структур на пластине и, как результат, в обеспечении условий для организации рентабельного промышленного выпуска СВЧ мощных кремниевых LDMOS-транзисторов нового поколения с повышенной эксплуатационной надежностью.

Å

Å

Å

Å

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS ТРАНЗИСТОРОВ | 2010 |

|

RU2439744C1 |

| МОЩНЫЙ СВЧ LDMOS ТРАНЗИСТОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2011 |

|

RU2473150C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ МОЩНЫХ ПОЛЕВЫХ LDMOS ТРАНЗИСТОРОВ | 2008 |

|

RU2364984C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ | 2012 |

|

RU2515124C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2006 |

|

RU2361318C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ | 2013 |

|

RU2535283C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS ТРАНЗИСТОРОВ | 2012 |

|

RU2498448C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ С МОДЕРНИЗИРОВАННЫМ ЗАТВОРНЫМ УЗЛОМ ЭЛЕМЕНТАРНЫХ ЯЧЕЕК | 2016 |

|

RU2639579C2 |

| Способ изготовления латерального ДМОП - транзистора с увеличенным значением напряжения пробоя | 2023 |

|

RU2803252C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНОГО ДМОП-ТРАНЗИСТОРА | 2000 |

|

RU2189089C2 |

Изобретение относится к электронной полупроводниковой технике. Техническим результатом изобретения является повышение предельно-допустимых значений электрических параметров и режимов эксплуатации СВЧ LDMOS - транзисторов и обеспечение условий для организации рентабельного промышленного выпуска данных изделий. Сущность изобретения: в СВЧ LDMOS - транзисторе, содержащем полупроводниковую подложку с высокоомным и высоколегированным слоями первого типа проводимости, элементарные транзисторные ячейки в высокоомном слое подложки с канальной областью первого типа проводимости, высоколегированной истоковой, высоколегированной и слаболегированной стоковой областями второго типа проводимости, подзатворный диэлектрик из термической двуокиси кремния и электрод затвора над канальной областью транзисторных ячеек, термическую двуокись кремния и межслойный диэлектрик над слаболегированной стоковой областью транзисторных ячеек, электроды истока и стока транзисторных ячеек на лицевой стороне подложки, полевые экранирующие электроды в промежутке между электродами стока и затвора, соединенные с одним из торцов электрода истока транзисторных ячеек за пределами электродов затвора, общий электрод истока транзисторной структуры на тыльной стороне подложки, полевые экранирующие электроды транзисторных ячеек выполнены из материала электрода затвора и размещены на границе раздела термическая двуокись кремния - межслойный диэлектрик, причем толщина термической двуокиси кремния над слаболегированной областью стока составляет (1,0-3,5) толщины подзатворного диэлектрика, а граница сопряжения подзатворного диэлектрика и слоя термической двуокиси кремния над слаболегированной стоковой областью расположена под электродом затвора. 1 ил., 2 табл.

СВЧ LDMOS-транзистор, содержащий полупроводниковую подложку с высокоомным и высоколегированным слоями первого типа проводимости, элементарные транзисторные ячейки в высокоомном слое подложки с канальной областью первого типа проводимости, высоколегированной истоковой, высоколегированной и слаболегированной стоковой областями второго типа проводимости, подзатворный диэлектрик из термической двуокиси кремния и электрод затвора над канальной областью транзисторных ячеек, термическую двуокись кремния и межслойный диэлектрик над слаболегированной стоковой областью транзисторных ячеек, электроды истока и стока транзисторных ячеек на лицевой стороне подложки, полевые экранирующие электроды в промежутке между электродами стока и затвора, соединенные с одним из торцов электрода истока транзисторных ячеек за пределами электродов затвора, общий электрод истока транзисторной структуры на тыльной стороне подложки, отличающийся тем, что полевые экранирующие электроды транзисторных ячеек выполнены из материала электрода затвора и размещены на границе раздела термическая двуокись кремния - межслойный диэлектрик, причем толщина термической двуокиси кремния над слаболегированной областью стока составляет 1,0-3,5 толщины подзатворного диэлектрика, а граница сопряжения подзатворного диэлектрика и слоя термической двуокиси кремния над слаболегированной стоковой областью расположена под электродом затвора.

| Способ получения продуктов конденсации фенолов с формальдегидом | 1924 |

|

SU2022A1 |

| US 7095080 B2, 22.08.2006 | |||

| US 6744117 B2, 01.06.2004 | |||

| US 5369045 A, 29.11.1994 | |||

| US 7033891 B2, 25.04.2006 | |||

| US 6870222 B2, 22.03.2005 | |||

| WO 00/14791 A1, 16.03.2000 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ ПЛАНАРНОГО СИЛОВОГО МОП ТРАНЗИСТОРА | 2002 |

|

RU2239912C2 |

| ПЛАНАРНЫЙ СИЛОВОЙ МОП ТРАНЗИСТОР С БЛОКИРУЮЩИМ ЕМКОСТЬ СТОКА БАРЬЕРОМ ШОТТКИ | 2002 |

|

RU2229758C1 |

Авторы

Даты

2008-11-10—Публикация

2007-01-16—Подача