ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к сигналу синхронизации, используемому для операции отображения в устройстве отображения (дисплейном устройстве).

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство отображения, которое включает в себя запоминающую схему (в дальнейшем называемую памятью пикселя) в каждом пикселе и хранит данные изображения в памяти пикселя, чтобы отображать неподвижное изображение с низким энергопотреблением без постоянной доставки извне данных изображения. Энергопотребление уменьшается, например, на (i) величину энергии для загрузки и разгрузки данными изображения сигнальных линий данных для доставки данных изображения к пикселям и (ii) величину энергии для передачи данных изображения снаружи панели к устройству управления. Величина (i) уменьшается, так как такая загрузка или разгрузка уже не нужна, если данные изображения записываются в память пикселя, и величина (ii) уменьшается, так как такая передача уже не нужна, если данные изображения записываются в память пикселя.

Разработана память пикселя на основе SRAM и DRAM. Напряжение пикселя в устройстве отображения, имеющем память пикселя на основе SRAM или DRAM, является цифровым. Поэтому такое устройство отображения вряд ли вызовет перекрестные помехи и обладает отличным качеством отображения.

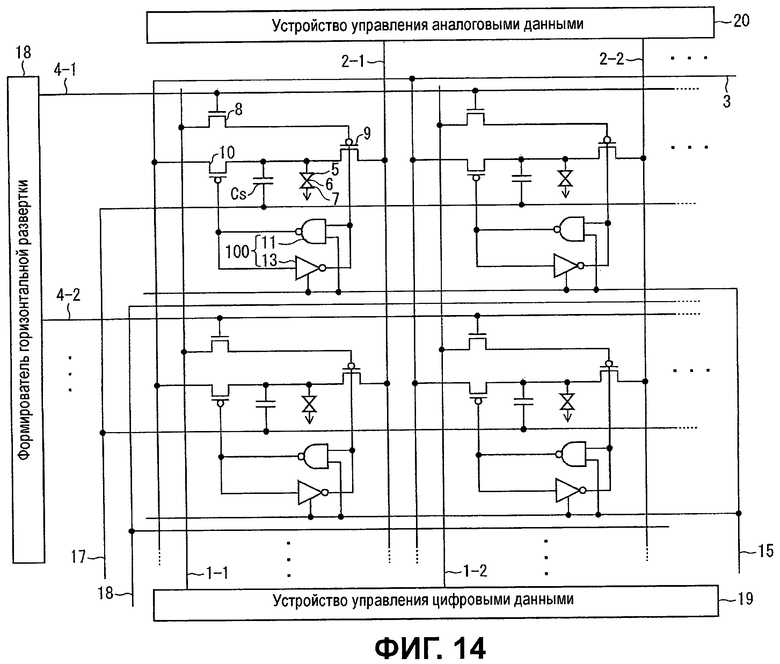

Фиг.14 показывает конфигурацию устройства отображения, включающего такую память пикселя, описанную в патентной литературе 1.

Устройство отображения включает в себя формирователь 18 горизонтальной развертки, устройство управления 19 цифровыми данными и устройство управления 20 аналоговыми данными, и может работать отдельно в режиме показа цифровых изображений и режиме показа аналоговых изображений.

Нижеследующее будет описывать режим показа цифровых изображений. Выбирается сигнальная линия 4-n строчной развертки (n - положительное целое число), соединенная с пикселем, куда должны записываться данные изображения. Затем из его соответствующей первой линии 1-n управления отображением цифровой сигнал данных записывается в цифровой запоминающий элемент 100, включающий схему 11 И-НЕ (NAND) и тактируемый инвертирующий элемент 13, через первый переключающий элемент 8 в пикселе. В то же время цифровой запоминающий элемент 100 делается активным через линию 15 управления режимом отображения.

Вход цифрового запоминающего элемента 100 подключается ко второму переключающему элементу 9, а выход цифрового запоминающего элемента 100 подключается к третьему переключающему элементу 10. Поэтому, в зависимости от верхнего или нижнего уровня цифрового сигнала данных проводящим становится либо второй переключающий элемент 9, либо третий переключающий элемент 10. Опорное напряжение отображения белого подается на одну из второй линии 2-n управления отображением и третьей линии 3 управления отображением, и опорное напряжение отображения черного подается на другую из второй линии 2-n управления отображением и третьей линии 3 управления отображением. В зависимости от переключающего элемента, который стал проводящим (второй переключающий элемент 9 или третий переключающий элемент 10), выбирается напряжение отображения белого или напряжение отображения черного, и затем подводится к жидкокристаллической ячейке 6. Жидкокристаллическая ячейка 6 поддерживает состояние отображения, вызванное цифровым сигналом данных, сохраненным в цифровом запоминающем элементе 100, до тех пор, пока первый переключающий элемент 8 снова не становится проводящим, и другой цифровой сигнал данных записывается в цифровой запоминающий элемент 100.

Патентная литература 1

Публикация заявки на патент Японии Tokukai № 2003-177717 A (дата публикации: 27 июня 2003 г.)

Патентная литература 2

Публикация заявки на патент Японии Tokukaisho № 58-23091 А (дата публикации: 10 февраля 1983 г.)

Патентная литература 3

Публикация заявки на патент Японии Tokukai № 2007-286237 А (дата публикации: 1 ноября 2007 г.)

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В последнее время все больше и больше интерфейсов для передачи отображаемых данных для использования в жидкокристаллических устройствах отображения применяют способ высокоскоростной последовательной передачи, использующий меньше сигнальных линий, вместо способа цифрового RGB (RGB-интерфейса) в способе параллельной передачи, использующем много сигнальных линий. Методика в способе последовательной передачи особенно важна для мобильного устройства, например мобильного телефона, поскольку мобильному устройству нужно сократить пространство для размещения проводки и предотвратить отсоединение провода. Более того, выполнение дифференциальной передачи делает возможным высокоскоростную передачу с низким энергопотреблением. В такой последовательной передаче отображаемые данные и управляющая команда передаются по одной и той же шине.

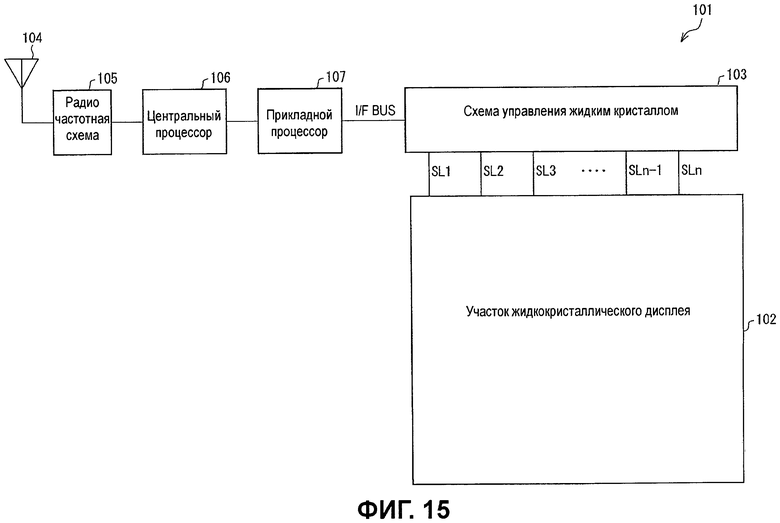

Например, в соответствии со стандартами MIPI (Интерфейс процессора для мобильных устройств), которые устанавливают общие спецификации для так называемого интерфейса CPU, который является интерфейсом между прикладным процессором и периферийным устройством мобильного устройства, прикладной процессор функционирует в качестве ведущего узла для управления работой периферийного устройства. Устройство запуска дисплея, которое использует управляющий сигнал, обычно начинает операцию отображения, которая задана командным управлением. Такое устройство запуска дисплея запускает экранный дисплей в ответ на команду пуска, переданную устройству запуска дисплея от ведущего узла после того, как включается источник питания. Фиг.15 - изображение, схематически показывающее конфигурацию схемного соединения в мобильном телефоне, включающую участок жидкокристаллического дисплея, снабженный таким интерфейсом CPU.

Мобильный телефон 101 включает в себя участок 102 жидкокристаллического дисплея, схему 103 управления жидким кристаллом, антенну 104, радиочастотную схему 105, центральный процессор 106 и прикладной процессор 107.

Участок 102 жидкокристаллического дисплея имеет пиксели, расположенные в матрице. Сигналы данных соответствующим образом записываются в пиксели через их соответствующие шины SL1-SLn истоков. Сигналы данных поступают в шины SL1-SLn истоков от схемы 103 управления жидким кристаллом. Дополнительно сигналы развертки, выбирающие строку, включающую множество пикселей, поступают в шины затворов от схемы 103 управления жидким кристаллом для того, чтобы сигналы данных записывались в пиксели (эта операция не показана).

Схема 103 управления жидким кристаллом является схемой, которая управляет отображением участка 102 жидкокристаллического дисплея, включающей одну или несколько микросхем. Дополнительно схема 103 управления жидким кристаллом включает в себя участки схем, такие как тактовый генератор, схема управления истоком, схема управления затвором, силовая цепь и запоминающее устройство, каждый из которых относится к операции отображения. Кроме того, схема 103 управления жидким кристаллом управляется прикладным процессором 107, служащим в качестве ведущего узла, через последовательную шину I/F BUS, и включает в себя ее интерфейс.

Антенна 104 является антенной, которую мобильный телефон 101 использует для передачи и приема. Радиочастотная схема 105 обрабатывает радиочастотный сигнал при передаче и приеме. Центральный процессор 106 обрабатывает исходный сигнал, демодулированный радиочастотной схемой 105, и управляет работой схемы обработки речевых сигналов (не показана) и схемой обработки передачи данных (не показана). Прикладной процессор 107 управляет схемой 103 управления жидким кристаллом и периферийным устройством (не показано), которое обрабатывает движущееся изображение, музыку, видеоигру и/или т.п.

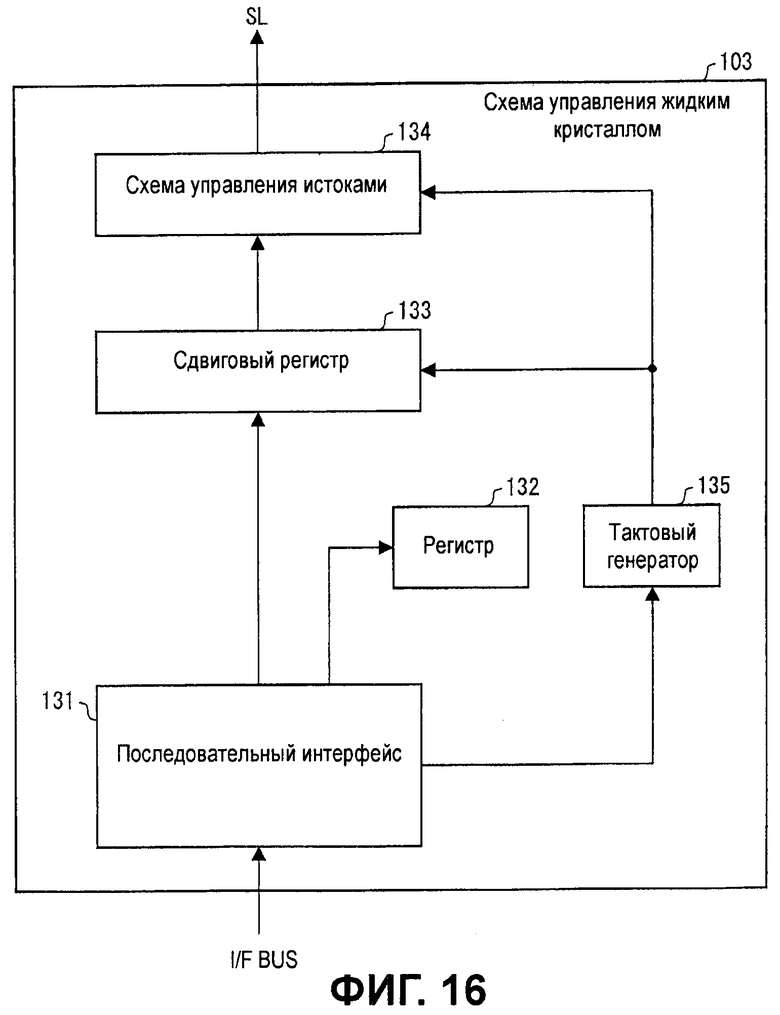

Фиг.16 показывает пример структуры схемы 103 управления жидким кристаллом.

В схеме 103 управления жидким кристаллом последовательный интерфейс 131 принимает управляющую команду и отображаемые данные, поступившие из шины последовательного интерфейса I/F BUS, и управляющая команда записывается в регистр 132. В соответствии с синхронизацией, с которой принимаются управляющая команда и отображаемые данные, тактовый генератор 135 формирует сигнал синхронизации с использованием генератора, включенного в тактовый генератор 135. В соответствии с сигналом синхронизации отображаемые данные передаются из последовательного интерфейса 131 в сдвиговый регистр 133, а затем в схему 134 управления истоками в этом порядке, чтобы сигнал данных поступал в шину SL истока.

Чтобы приводить в действие каждую часть схемы управления и участка жидкокристаллического дисплея в случае RGB-интерфейса, сигнал кадровой синхронизации и сигнал строчной синхронизации поступают снаружи; однако в случае схемы управления жидким кристаллом, включающей вышеописанный интерфейс CPU, вместо сигнала кадровой синхронизации или сигнала строчной синхронизации тактовый генератор все время формирует сигнал синхронизации с использованием несинхронизируемого генератора в соответствии с управляющей командой и отображаемыми данными, которые поступают с помощью последовательной передачи. В случае пикселя, включающего вышеописанную память пикселя, отображение неподвижного изображения выполняется следующим образом. После того, как отображаемые данные записываются в запоминающую схему, поступление данных от прикладного процессора прекращается, чтобы уменьшалось энергопотребление. Поэтому формирование сигнала синхронизации в схеме управления жидким кристаллом является важным. То есть хотя схема управления жидким кристаллом, включающая вышеописанный интерфейс CPU, применяет последовательную передачу, которая обладает преимуществами возможности сокращения размера, высокоскоростной передачи и низкого энергопотребления, сигнал синхронизации для записи данных изображения в пиксель следует формировать в соответствии с синхросигналом, сформированным тактовым генератором.

Таким образом, при традиционном способе с интерфейсом CPU необходимо все время формировать, в схеме формирователя, сигнал синхронизации для записи данных изображения в пиксели с использованием генератора или т.п. в соответствии с сигналом, поступившим от CPU. Это мешает сокращению размера схемы управления жидким кристаллом.

Настоящее изобретение создавалось в связи с вышеупомянутой проблемой, и цель настоящего изобретения - реализовать устройство отображения, выполненное с возможностью без труда формировать, в схеме формирователя, сигнал синхронизации для записи данных изображения в пиксели, и мобильный терминал, включающий в себя это устройство отображения.

Устройство отображения из настоящего изобретения для достижения упомянутой цели является устройством отображения активноматричного типа и включает в себя устройство управления дисплеем, в которое с помощью последовательной передачи поступают данные изображения, включенные в последовательные данные, причем последовательные данные содержат добавленный к ним первый флаг для указания начала одного периода кадровой развертки, при этом устройство управления дисплеем извлекает первый флаг и данные изображения из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, переданного по шине, используемой для последовательной передачи, но отличной от шины для последовательных данных, в соответствии с синхронизацией последовательного тактового сигнала, при этом устройство управления дисплеем формирует сигнал синхронизации, служащий в качестве синхросигнала для функционирования сдвигового регистра в формирователе сигнальной линии данных, включенном в устройство управления дисплеем, в соответствии с первым флагом и сигналом синхронизации, служащим в качестве синхросигнала для функционирования сдвигового регистра, причем устройство управления дисплеем формирует сигнал синхронизации для начального периода строчной развертки в одном периоде кадровой развертки, и вводит сигнал синхронизации для начального периода строчной развертки в сдвиговый регистр формирователя сигнальной линии данных, в случае, где существует следующий период строчной развертки, устройство управления дисплеем формирует сигнал синхронизации для следующего периода строчной развертки в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, и вводит сигнал синхронизации для следующего периода строчной развертки в сдвиговый регистр в формирователе сигнальной линии данных, в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, устройство управления дисплеем формирует сигнал синхронизации, который нужно ввести в сдвиговый регистр в формирователе сигнальной линии развертки, включенном в устройство управления дисплеем, и в соответствии с сигналами синхронизации для начального периода строчной развертки и последующего периода строчной развертки, и сигналом развертки, доставленным формирователем сигнальной линии развертки, устройство управления дисплеем записывает данные изображения в пиксели.

В соответствии с вышеупомянутым изобретением устройство управления дисплеем извлекает, в соответствии с синхронизацией последовательного тактового сигнала, первый флаг и данные изображения из последовательных данных, поступивших с помощью последовательной передачи. Затем устройство управления дисплеем формирует сигнал синхронизации для начального периода строчной развертки в одном периоде кадровой развертки в соответствии с первым флагом, и вводит сигнал синхронизации в сдвиговый регистр в формирователе сигнальной линии данных. Устройство управления дисплеем последовательно формирует сигналы синхронизации для второго периода строчной развертки и последующего периода строчной развертки в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных.

Таким образом, устройство управления дисплеем с помощью непосредственного контроля последовательной передачи может формировать сигнал синхронизации для записи данных изображения в пиксель. То есть устройство управления дисплеем без труда может сформировать сигнал синхронизации без постоянного использования генератора и т.п.

Вышеприведенная конфигурация позволяет без труда формировать, в схеме формирователя, сигнал синхронизации для записи данных изображения в пиксель.

В устройстве отображения из настоящего изобретения для достижения упомянутой цели каждый из пикселей включает в себя память пикселя для хранения данных изображения, поступивших от устройства управления дисплеем; в случае, где память пикселя хранит данные изображения, последовательные данные включают в себя данные изображения для сохранения в памяти пикселя, и последовательные данные содержат добавленный в них первый флаг; а в случае, где отображаются данные изображения, сохраненные в памяти пикселя, последовательные данные включают в себя, вместо данных изображения для сохранения в памяти пикселя, фиктивные данные не для передачи в пиксели, и последовательные данные содержат добавленный в них первый флаг.

В соответствии с вышеупомянутым изобретением в случае, где отображаются данные изображения, сохраненные в памяти пикселя, первый флаг добавляется к фиктивным данным не для передачи в пиксели вместо данных изображения для сохранения в памяти пикселя. Этот первый флаг позволяет формировать сигнал синхронизации для переменного общего напряжения, пока энергия не потребляется для поступления данных изображения в каждый из пикселей.

В устройстве отображения из настоящего изобретения для достижения упомянутой цели сигнал развертки является сигналом, который дает возможность данным изображения записываться в память пикселя после того, как все данные изображения выводятся в сигнальную линию данных в каждом строчном периоде отображения.

В соответствии с вышеупомянутым изобретением, в каждом строчном периоде отображения данные изображения записываются в память пикселя после того, как все данные изображения выводятся в сигнальную линию данных. Поэтому, даже если колебание в электрическом потенциале сигнальной линии данных возникает в период, в котором данные изображения по порядку выводятся в сигнальную линию данных, это оказывает меньшее влияние на память пикселя при сохранении данных изображения.

В устройстве отображения из настоящего изобретения для достижения вышеупомянутой цели последовательные данные содержат добавленный в них второй флаг, указывающий, включают ли последовательные данные данные изображения для сохранения в памяти пикселя, и устройство управления дисплеем извлекает второй флаг из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, и в случае, где второй флаг указывает, что последовательные данные включают в себя данные изображения для сохранения в памяти пикселя, устройство управления дисплеем извлекает данные изображения из последовательных данных и сохраняет данные изображения в памяти пикселя.

В соответствии с вышеупомянутым изобретением из второго флага можно узнать, что последовательные данные включают в себя данные изображения для сохранения в памяти пикселя. При этом, только когда последовательные данные включают в себя данные изображения, разрешается энергопотребление для поступления данных изображения в каждый из пикселей.

В устройстве отображения из настоящего изобретения для достижения упомянутой цели последовательные данные содержат добавленный в них третий флаг, дающий указание в отношении того, инициализировать ли отображение всех пикселей; и устройство управления дисплеем извлекает третий флаг из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, и в случае, где указание в третьем флаге означает инициализацию отображения всех пикселей, устройство управления дисплеем инициализирует отображение всех пикселей.

В соответствии с вышеупомянутым изобретением из третьего флага можно узнать, что нужно инициализировать отображение всех пикселей. При этом можно выполнить инициализацию без включения данных изображения для инициализации в последовательные данные. Это устраняет необходимость в поступлении данных изображения в пиксели по отдельности, посредством этого приводя к сокращению энергопотребления на величину энергии для поступления данных изображения в пиксели по отдельности.

Устройство отображения из настоящего изобретения является устройством отображения по п.1 или 2, в котором первый флаг, добавленный в последовательные данные, служит в качестве флага для дополнительного указания полярности напряжения общего электрода.

Вышеупомянутое изобретение позволяет инвертировать полярность напряжения общего электрода в каждом кадре. В устройстве отображения из настоящего изобретения для достижения вышеупомянутой цели в последовательной передаче сигнал последовательного выбора кристалла, указывающий, выполнять ли отображение, то есть приводить ли в действие устройство управления дисплеем, передается по шине, отличной от шин для последовательных данных и последовательного тактового сигнала.

В соответствии с вышеупомянутым изобретением, путем распознавания периода, в котором устройство управления дисплеем не функционирует, из сигнала последовательного выбора кристалла, устройство управления дисплеем может избежать загрузки последовательных данных. Поэтому можно прекратить последовательную передачу в этом периоде, посредством этого приводя к сокращению энергопотребления на величину энергии для последовательной передачи.

В устройстве отображения из настоящего изобретения для достижения вышеупомянутой цели пиксели включают в себя аналоговый ключ, выполненный из схемы CMOS.

В соответствии с вышеупомянутым изобретением аналоговый ключ в пикселе выполнен из схемы CMOS. Это позволяет управлять с помощью низкого напряжения даже устройством (например, TFT), имеющим высокое Vth (пороговое напряжение), и устанавливать одинаковое напряжение для управляющего сигнала и сигнала данных. При этом можно снизить амплитуду напряжения у источника питания, используемого в задающей схеме для дисплея, посредством этого уменьшая энергопотребление.

В устройстве отображения из настоящего изобретения для достижения упомянутой цели устройство управления дисплеем составляет единое целое с панелью дисплея.

В соответствии с вышеупомянутым изобретением устройство управления дисплеем, выполненное из схемы CMOS, формируется монолитно на панели дисплея. Это позволяет уменьшить размер устройства отображения и упростить процесс.

В устройстве отображения из настоящего изобретения для достижения указанной цели каждый из пикселей включает в себя элемент отображения, использующий жидкий кристалл с диспергированным полимером.

В соответствии с вышеупомянутым изобретением жидкий кристалл с диспергированным полимером используется для элемента отображения. При этом можно реализовать жидкокристаллическое устройство отображения с высокой яркостью, не включающее пластину поляризации и/или т.п., и дополнительно управлять таким жидкокристаллическим устройством отображения с помощью низкого напряжения. Это значительно снижает энергопотребление, особенно в устройстве отображения с низким энергопотреблением, включающем память пикселя в пикселе.

В устройстве отображения из настоящего изобретения для достижения вышеуказанной цели каждый из пикселей включает в себя элемент отображения, использующий стабилизированный полимерной сеткой жидкий кристалл.

В соответствии с вышеупомянутым изобретением стабилизированный полимерной сеткой жидкий кристалл используется для элемента отображения. При этом можно реализовать жидкокристаллическое устройство отображения с высокой яркостью, не включающее пластину поляризации и/или т.п., и дополнительно управлять таким жидкокристаллическим устройством отображения с помощью низкого напряжения. Это значительно снижает энергопотребление, особенно в устройстве отображения с низким энергопотреблением, включающем память пикселя в пикселе.

В устройстве отображения из настоящего изобретения для достижения упомянутой цели сигнал, сдвинутый на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, сдвигается на заранее установленное количество ступеней (разрядов) с использованием фиктивного сдвигового регистра, так что формируется первый конечный разряд, и первый конечный разряд дополнительно сдвигается на одну ступень посредством фиктивного сдвигового регистра, так что формируется второй конечный разряд, причем второй конечный разряд используется для формирования сигнала синхронизации для следующего периода строчной развертки для формирователя сигнальной линии данных, и первый конечный разряд и второй конечный разряд используются для формирования сигнала синхронизации, который нужно ввести в сдвиговый регистр формирователя сигнальной линии развертки.

Мобильный терминал из настоящего изобретения для достижения вышеупомянутой цели включает в себя устройство отображения, служащее в качестве модуля отображения.

С помощью вышеупомянутого изобретения можно без труда удовлетворить потребность в мобильных терминалах с меньшим энергопотреблением.

Для более полного понимания сущности и преимуществ изобретения следует обратиться к следующему подробному описанию изобретения в сочетании с прилагаемыми чертежами.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

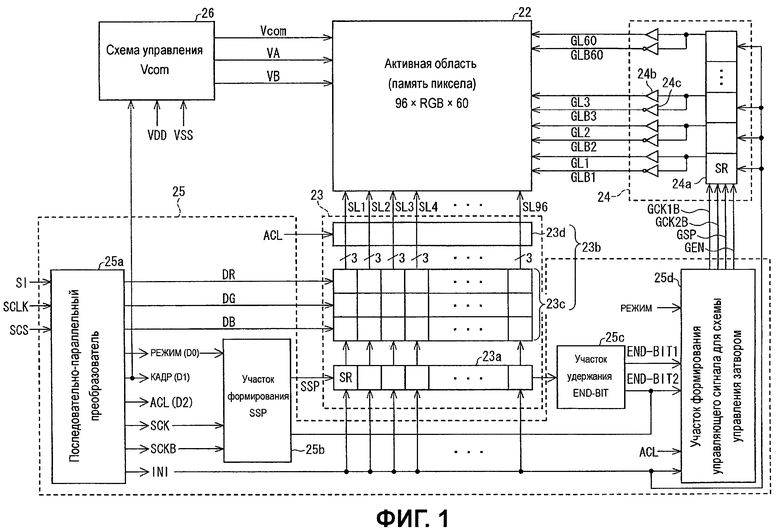

Фиг.1, имеющая отношение к варианту осуществления настоящего изобретения, является принципиальной схемой, показывающей, как основные части в устройстве отображения соединяются друг с другом.

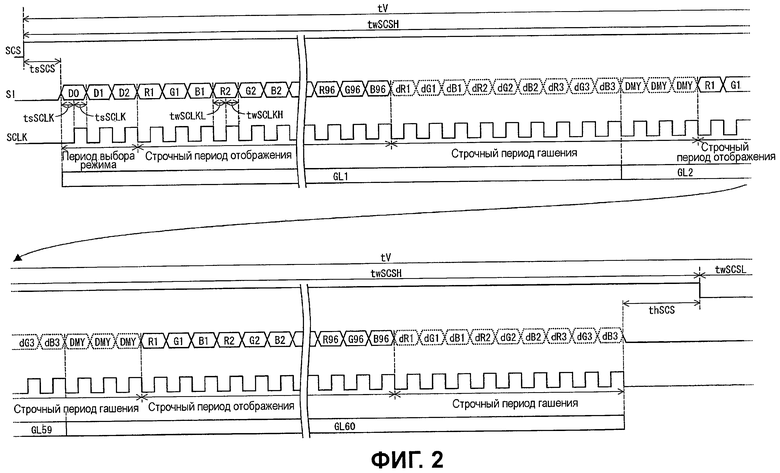

Фиг.2 - временная диаграмма, показывающая форму сигнала у каждого сигнала для последовательной передачи в режиме обновления данных.

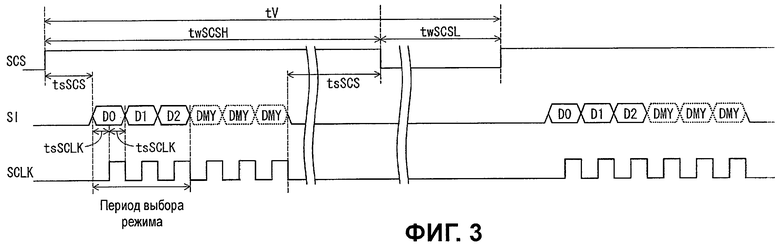

Фиг.3 - временная диаграмма, показывающая форму сигнала у каждого сигнала для последовательной передачи в режиме отображения.

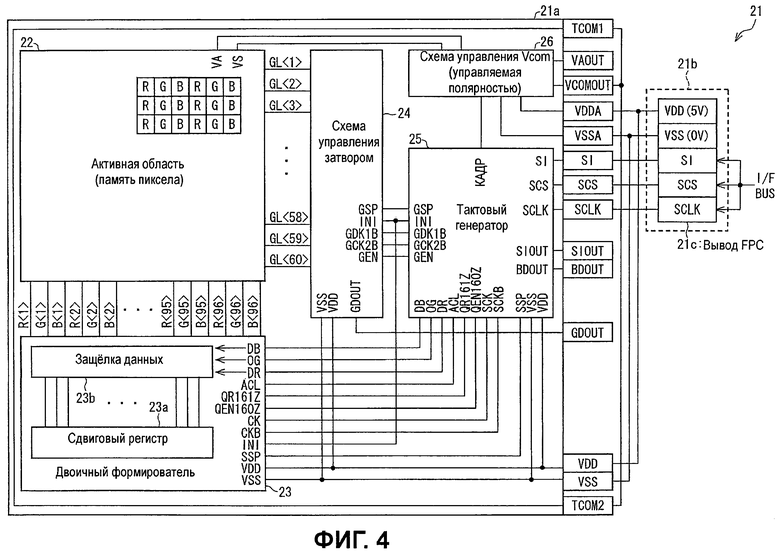

Фиг.4 - блок-схема, показывающая всю структуру устройства отображения.

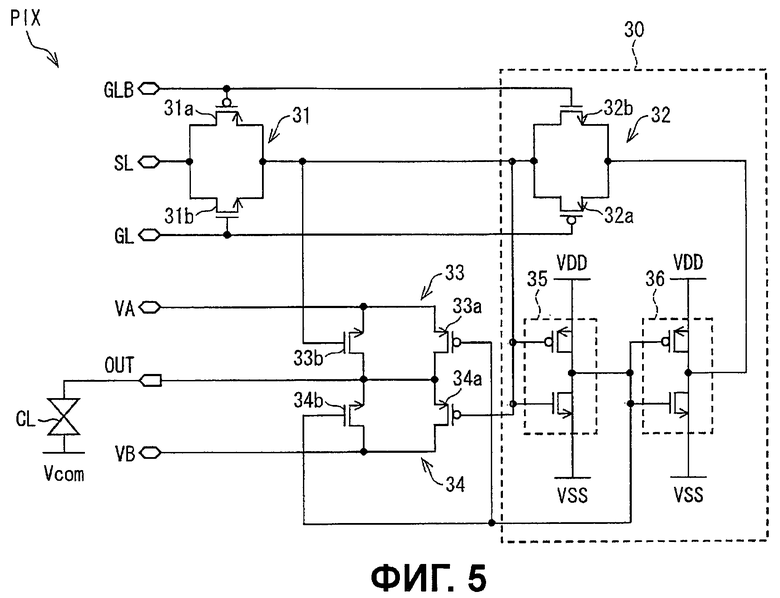

Фиг.5 - принципиальная схема, показывающая структуру пикселя и памяти пикселя.

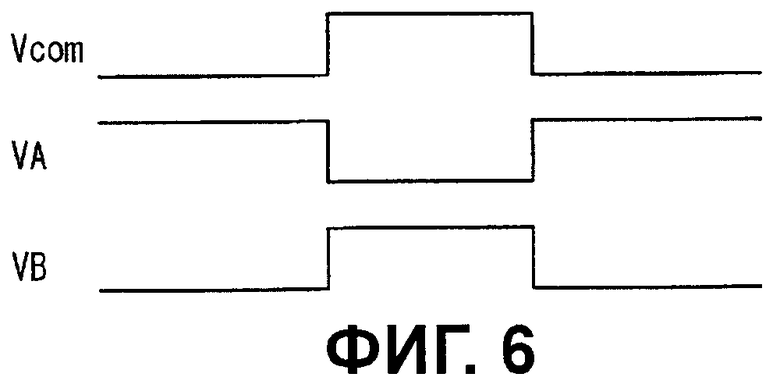

Фиг.6 - временная диаграмма, показывающая выходную форму сигнала схемы управления Vcom.

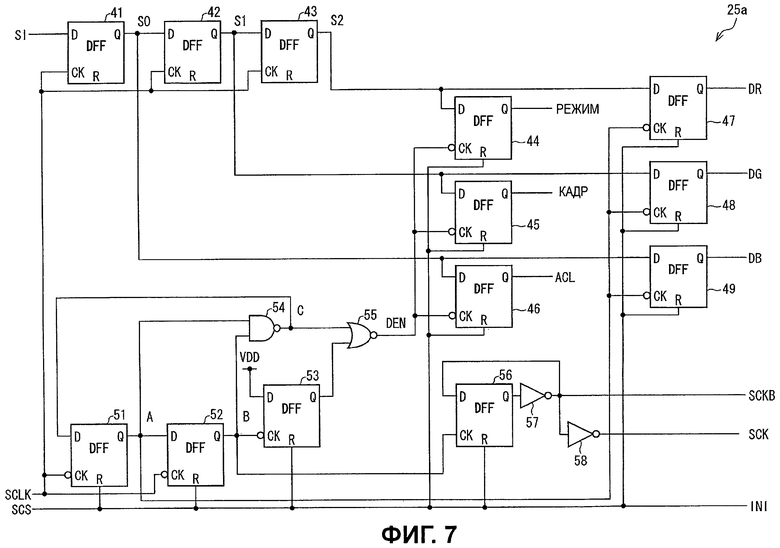

Фиг.7 - принципиальная схема, показывающая структуру последовательно-параллельного преобразователя.

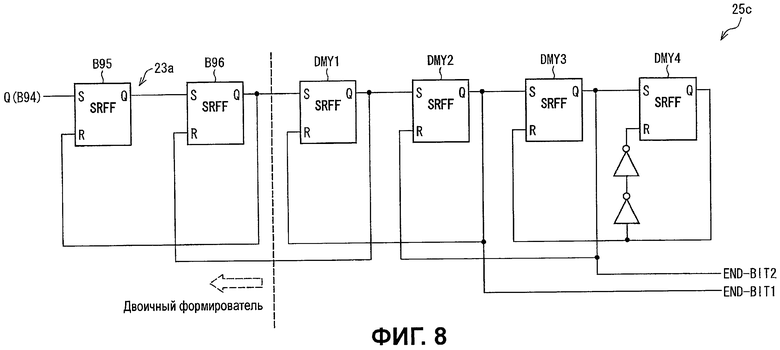

Фиг.8 - принципиальная схема, показывающая структуру участка удержания END-BIT.

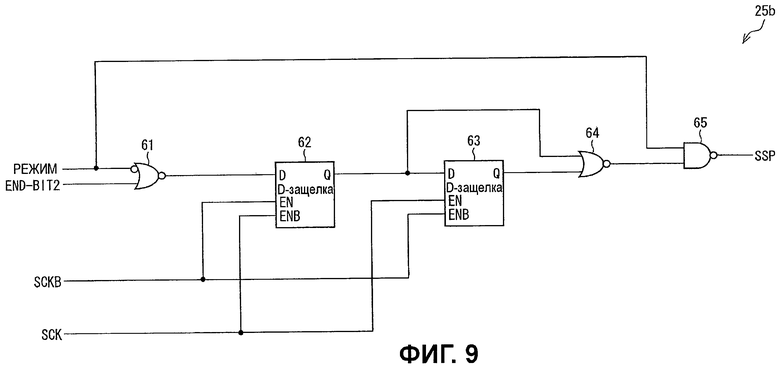

Фиг.9 - принципиальная схема, показывающая структуру участка формирования пускового импульса для истока.

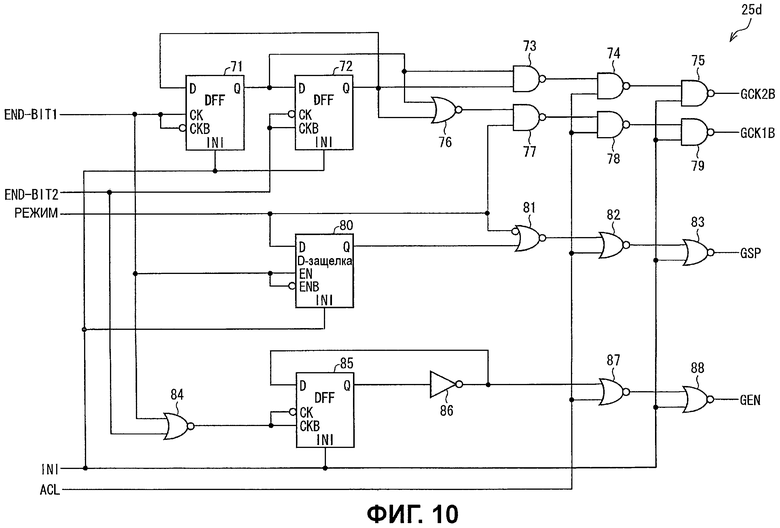

Фиг.10 - принципиальная схема, показывающая структуру участка формирования управляющего сигнала для схемы управления затвором.

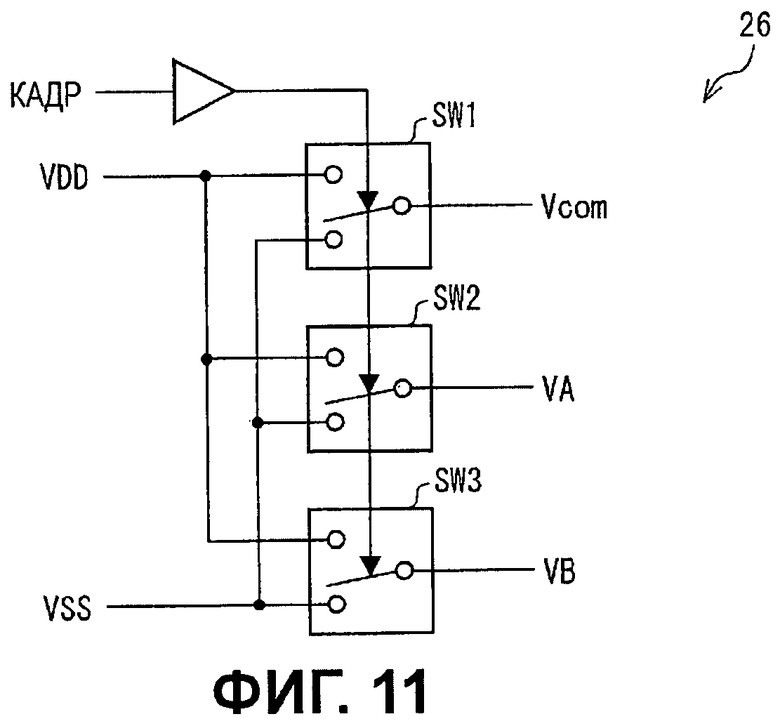

Фиг.11 - принципиальная схема, показывающая структуру схемы управления Vcom.

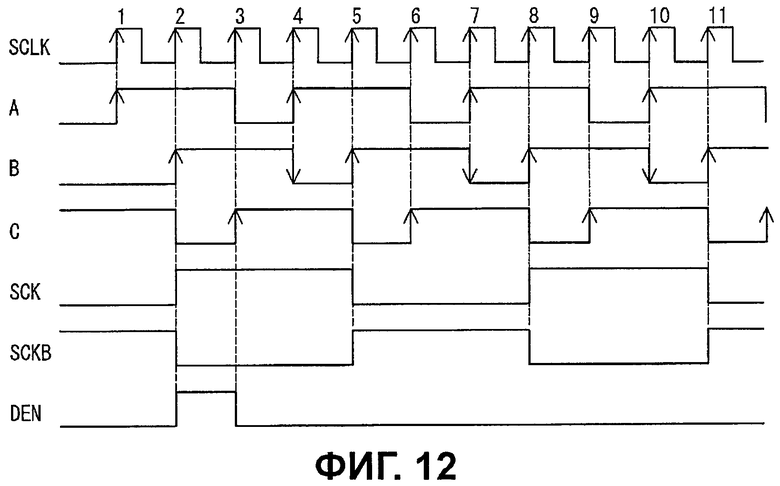

Фиг.12 - временная диаграмма, показывающая форму сигнала у каждого сигнала в последовательно-параллельном преобразователе.

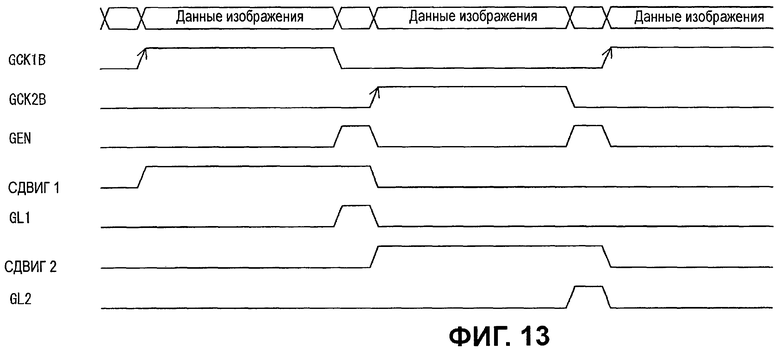

Фиг.13 - временная диаграмма, показывающая форму сигнала у каждого сигнала в участке формирования управляющего сигнала для схемы управления затвором.

Фиг.14 - принципиальная схема, показывающая структуру устройства отображения по традиционной методике.

Фиг.15 - блок-схема, показывающая структуру мобильного телефона по традиционной методике.

Фиг.16 - блок-схема, показывающая структуру устройства управления дисплеем по традиционной методике.

СПИСОК ССЫЛОК

21: Жидкокристаллическое устройство отображения (Устройство отображения)

23: Двоичный формирователь

23a: Сдвиговый регистр (Сдвиговый регистр в формирователе сигнальной линии данных)

23b: Защелка данных

24: Схема управления затвором

24a: Сдвиговый регистр (Сдвиговый регистр в формирователе сигнальной линии развертки)

25: Тактовый генератор

26: Схема управления Vcom

30: Память пикселя

D0: Флаг (Второй флаг)

D1: Флаг (Первый флаг)

D2: Флаг (Третий флаг)

GCK1B и GCKB2: Тактовые сигналы затвора (Сигналы синхронизации, введенные в сдвиговый регистр в формирователе сигнальной линии затвора)

GEN: Разрешающий сигнал затвора (Сигнал синхронизации, введенный в сдвиговый регистр в формирователе сигнальной линии затвора)

SCK и SCKB: Тактовые сигналы истока (Сигналы синхронизации в виде синхросигналов для функционирования сдвигового регистра в формирователе сигнальной линии данных)

SSP: Пусковой импульс истока (Сигнал синхронизации для периода строчной развертки)

I/F BUS: Шина последовательного интерфейса

SI: Последовательные данные

SCLK: Последовательный тактовый сигнал

SCS: Сигнал выбора кристалла

SL: Шина истока (Сигнальная линия данных)

Vcom: Общий выход (Напряжение общего электрода)

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Нижеследующее описывает вариант осуществления настоящего изобретения со ссылкой на фиг. с 1 по 13.

Фиг.4 показывает структуру жидкокристаллического устройства 21 отображения (устройства отображения) из настоящего варианта осуществления.

Жидкокристаллическое устройство 21 отображения является модулем отображения, включенным в мобильный терминал, например мобильный телефон, и включает в себя панель 21a дисплея и гибкую печатную плату 21b (FPC). Панель 21a дисплея содержит различные монолитно включенные в нее схемы. Гибкая печатная плата 21b принимает последовательные данные SI, сигнал последовательного выбора кристалла SCS и последовательный тактовый сигнал SCLK, переданные путем последовательной передачи по трехканальной шине последовательного интерфейса I/F BUS, которая управляется CPU, например прикладным процессором, и передает последовательные данные SI, сигнал последовательного выбора кристалла SCS и последовательный тактовый сигнал SCLK к панели 21a дисплея через вывод 21c FPC. Последовательная передача может управляться другим средством управления, например микроконтроллером. Дополнительно гибкая печатная плата 21b подает 5В от источника питания VDD и 0В от источника питания VSS, которые поступают извне, на панель 21a дисплея через вывод 21c FPC.

Панель 21a дисплея включает в себя активную область 22, двоичный формирователь 23 (формирователь сигнальной линии данных), схему 24 управления затвором (формирователь сигнальной линии развертки), тактовый генератор 25 и схему 26 управления Vcom. Двоичный формирователь 23, схема 24 управления затвором, тактовый генератор 25 и схема 26 управления Vcom образуют устройство управления дисплеем.

Активная область 22 является, например, областью, где пиксели RGB располагаются в матрице 96xRGBx60, и каждый из пикселей включает в себя память пикселя. Двоичный формирователь 23 является схемой для доставки данных изображения в активную область 22 через шину истока, и включает в себя сдвиговый регистр 23a и защелку 23b данных. Схема 24 управления затвором через шину затворов выбирает пиксель, к которому должны поступить данные изображения, среди пикселей в активной области 22. Тактовый генератор 25 формирует сигнал для передачи двоичному формирователю 23, схеме 24 управления затвором и схеме 26 управления Vcom в соответствии с сигналом, поступившим от гибкой печатной платы 21b.

Фиг.5 показывает структуру каждого из пикселей PIX, расположенных в активной области 22, наряду с подробным показом схемы памяти пикселя.

Пиксель PIX включает в себя жидкокристаллическое емкостное сопротивление CL, память 30 пикселя и аналоговые ключи 31, 33 и 34. Память 30 пикселя дополнительно включает в себя аналоговый ключ 32 и инверторы 35 и 36.

Жидкокристаллическое емкостное сопротивление CL здесь образуется между выходом полярности OUT и общим выходом Vcom (который является напряжением общего электрода) с использованием жидкого кристалла светорассеивающего типа, например PDLC (жидкий кристалл с диспергированным полимером) или PNLC (стабилизированный полимерной сеткой жидкий кристалл). Аналоговые ключи 31-34 и инверторы 35 и 36 представлены схемой CMOS.

Аналоговый ключ 31 располагается между выходом шины истока SL и памятью 30 пикселя и включает в себя (i) PMOS-транзистор 31а, чей затвор подключается к инверсионному выходу шины затворов GLB, и (ii) NMOS-транзистор 31b, чей затвор подключается к выходу шины затворов GL. Аналоговый ключ 32 в памяти 30 пикселя располагается между входом инвертора 35 и выходом инвертора 36, и включает в себя (i) PMOS-транзистор 32а, чей затвор подключается к выходу шины затворов GL, и (ii) NMOS-транзистор 32b, чей затвор подключается к инверсионному выходу шины затворов GLB. Вход инвертора 35 подключается к клемме аналогового ключа 31, и эта клемма находится на стороне, противоположной стороне, на которой подключается выход шины истока SL. Выход инвертора 35 подключается ко входу инвертора 36. Каждый из инверторов 35 и 36 использует источник питания VDD в качестве источника питания "High" и источник питания VSS в качестве источника питания "Low".

Аналоговый ключ 33 располагается между выходом полярности черного VA и выходом полярности OUT, и включает в себя (i) PMOS-транзистор 33а, чей затвор подключается к выходу инвертора 35, и (ii) NMOS-транзистор 33b, чей затвор подключается ко входу инвертора 35. Аналоговый ключ 34 располагается между выходом полярности белого VB и выходом полярности OUT, и включает в себя (i) PMOS-транзистор 34а, чей затвор подключается ко входу инвертора 35, и (ii) NMOS-транзистор 34b, чей затвор подключается к выходу инвертора 35.

Фиг.6 показывает соответствующие формы сигналов у общего выхода Vcom, выхода полярности черного VA и выхода полярности белого VB. Эти сигналы формируются схемой 26 управления Vcom. Общий выход Vcom дает форму импульса 5Vp-p, в которой переключение между положительной полярностью и отрицательной полярностью происходит в каждом кадре. При желании можно задать цикл для переключения полярности. Например, такое переключение может происходить в каждом заранее установленном периоде строчной развертки. Выход полярности черного VA имеет форму импульса 5Vp-p в противофазе с формой импульса у общего выхода Vcom. Выход полярности белого VB (в случае обычного белого) имеет форму импульса 5Vp-p в фазе с формой импульса у общего выхода Vcom.

На фиг.5 в случае, где верхний уровень (5В) выводится в качестве выхода шины истока SL из двоичного формирователя 23, пиксель PIX выбирается с помощью верхнего уровня (5В) выхода шины затворов GL и нижнего уровня (0В) инверсионного выхода шины затворов GLB, чтобы аналоговый ключ 31 выбранного пикселя PIX стал проводящим. При этом аналоговый ключ 33 становится проводящим, а аналоговый ключ 34 блокируется. Следовательно, выход полярности черного VA выводится в выход полярности OUT, и в жидкокристаллическое емкостное сопротивление CL подается 5В, что является разностью напряжения между выходом полярности черного VA и общим выходом Vcom. В результате пиксель PIX приводится в состояние отображения черного.

Впоследствии, когда выход шины затворов GL становится нижним уровнем (0В), а инверсионный выход шины затворов GLB становится верхним уровнем (5В), аналоговый ключ 31 блокируется, а аналоговый ключ 32 становится проводящим. Следовательно, верхний уровень сохраняется в памяти 30 пикселя. Сохраненные данные хранятся, пока этот пиксель PIX не выбирается снова и аналоговый ключ 31 становится проводящим.

Между тем на фиг.5 в случае, где нижний уровень (0В) выводится в качестве выхода шины истока SL из двоичного формирователя 23, пиксель PIX выбирается с помощью верхнего уровня (5В) выхода шины затворов GL и нижнего уровня (0В) инверсионного выхода шины затворов GLB, чтобы аналоговый ключ 31 выбранного пикселя PIX стал проводящим. При этом аналоговый ключ 33 блокируется, а аналоговый ключ 34 становится проводящим. Следовательно, выход полярности белого VB выводится в выход полярности OUT, и в жидкокристаллическое емкостное сопротивление CL подается 0В, что является разностью напряжения между выходом полярности белого VB и общим выходом Vcom. В результате пиксель PIX приводится в состояние отображения белого.

Впоследствии, когда выход шины затворов GL становится нижним уровнем (0В), а инверсионный выход шины затворов GLB становится верхним уровнем (5В), аналоговый ключ 31 блокируется, а аналоговый ключ 32 становится проводящим. Следовательно, нижний уровень сохраняется в памяти 30 пикселя. Сохраненные данные хранятся, пока этот пиксель PIX не выбирается снова и аналоговый ключ 31 становится проводящим.

Фиг.1 показывает то, как тактовый генератор 25, двоичный формирователь 23, схема 24 управления затвором и схема 26 управления Vcom соединяются друг с другом.

Тактовый генератор 25 включает в себя последовательно-параллельный преобразователь 25а, участок 25b формирования пускового импульса для истока, участок 25c удержания END-BIT и участок 25d формирования управляющего сигнала для схемы управления затвором. Тактовый генератор 25 формирует сигнал режима MODE, сигнал кадра FRAME, сигнал общей очистки ACL, тактовые сигналы истока SCK и SCKB (сигналы синхронизации, служащие в качестве синхросигнала для функционирования сдвигового регистра в формирователе сигнальной линии данных), пусковой импульс истока SSP (сигнал синхронизации для периода строчной развертки), тактовые сигналы затвора GCK1B и GCK2B (сигналы синхронизации, вводимые в сдвиговый регистр в формирователе сигнальной линии затвора), пусковой импульс затвора GSP, разрешающий сигнал затвора GEN (сигнал синхронизации, введенный в сдвиговый регистр в формирователе сигнальной линии затвора), и начальный сигнал INI в соответствии с последовательными данными SI, последовательным тактовым сигналом SCLK и сигналом последовательного выбора кристалла SCS, которые поступают снаружи панели. Тактовый генератор 25 передает пусковой импульс истока SSP и начальный сигнал INI в двоичный формирователь 23. Тактовый генератор 25 передает тактовые сигналы затвора GCK1B и GCK2B, пусковой импульс затвора GSP, разрешающий сигнал затвора GEN и начальный сигнал INI в схему 24 управления затвором. Тактовый генератор 25 передает сигнал кадра FRAME в схему 26 управления Vcom. Тактовые сигналы истока SCK и SCKB здесь используются в тактовом генераторе 25. Однако, как описано позже, тактовые сигналы истока SCK и SCKB используются для формирования пускового импульса истока SSP в каждом периоде строчной развертки, и являются синхросигналами для функционирования сдвигового регистра 23a в двоичном формирователе 23.

Последовательно-параллельный преобразователь 25а снабжается последовательными данными SI, последовательным тактовым сигналом SCLK и сигналом последовательного выбора кристалла SCS от гибкой печатной платы 21b. Как описано выше, шина последовательного интерфейса I/F BUS принадлежит к трехканальному типу. Поэтому последовательные данные SI, последовательный тактовый сигнал SCLK и сигнал последовательного выбора кристалла SCS передаются по разным шинам. Фиг.2 и 3 показывают эти сигналы.

Последовательные данные SI являются сигналом, сконфигурированным следующим образом. Флаги D0, D1 и D2, которые помещаются в периоде выбора режима, предусмотренном в заголовке каждого кадра, добавляются к цифровым данным двоичного RGB-изображения, упорядоченным последовательно.

В режиме обновления данных, который показан на фиг.2, для записи данных изображения в память 30 пикселя наборы данных изображения, в каждом из которых во временном ряду размещаются RGB-данные для одного строчного периода отображения, размещаются в порядке строчного периода отображения. Более того, строчный период отображения и последующий период имеют строчный период гашения между ними, и этот строчный период гашения включает в себя (i) фиктивные данные dR1, dG1 и dB1, расположенные в нем, и (ii) трое фиктивных данных DMY, DMY и DMY, расположенные в периоде, соответствующем таковому у флагов D0, D1 и D2 в начальном строчном периоде отображения. Эти фиктивные данные могут быть High или Low.

В режиме отображения, который показан на фиг.3, для удержания данных изображения, сохраненных в памяти 30 пикселя, все данные изображения и фиктивные данные в режиме обновления данных, показанном на фиг.2, заменяются фиктивными данными DMY.

Флаг (второй флаг) D0 является флагом режима. В случае, где флаг D0 равен High, флаг D0 указывает тактовому генератору 25 работать в режиме обновления данных для записи данных изображения в память 30 пикселя. В случае, где флаг D0 равен Low, флаг D0 указывает тактовому генератору 25 работать в режиме отображения для удержания данных изображения, сохраненных в памяти 30 пикселя. Флаг (первый флаг) D1 является флагом инверсии кадра. В случае, где флаг D1 равен High, флаг D1 указывает тактовому генератору 25 выставить общий выход Vcom на High. В случае, где флаг D1 равен Low, флаг D1 указывает тактовому генератору 25 выставить общий выход Vcom на Low. То есть флаг D1 является флагом для указания полярности общего выхода Vcom, которая инвертируется в каждом кадре. Флаг (третий флаг) D2 является флагом общей очистки. В случае, где флаг D2 равен High, флаг D2 указывает тактовому генератору 25 записать данные отображения белого во все пиксели PIX в текущем кадре. В случае, где флаг D2 равен Low, флаг D2 указывает тактовому генератору 25 записать во все пиксели PIX данные изображения, которые нужно передать, в текущем кадре. То есть в случае, где флаг D2 равен High, флаг D2 отдает указание для инициализации отображения всех пикселей PIX. Флаг D2 обычно равен Low.

Последовательный тактовый сигнал SCLK является синхроимпульсами для извлечения различных данных, включающих флаги последовательных данных SI. Нижеследующее описывает пример моментов нарастания и спада в последовательном тактовом сигнале SCLK. Для каждого из флагов с D0 по D2 момент нарастания последовательного тактового сигнала SCLK является моментом времени, когда прошел период времени tsSCLK от момента начала передачи флага; для каждых из данных изображения R, G и B момент нарастания последовательного тактового сигнала SCLK является моментом времени, когда прошел период времени twSCLKL от момента начала передачи данных изображения. Период времени tsSCLK равен периоду времени twSCLKL, и каждый из периода времени tsSCLK и периода времени twSCLKL равен периоду, в котором последовательный тактовый сигнал SCLK равен Low. Для каждого из флагов с D0 по D2 момент спада последовательного тактового сигнала SCLK является моментом времени, когда прошел период времени tsSCLK от момента нарастания последовательного тактового сигнала SCLK, и является моментом окончания передачи флага (то есть моментом, в котором происходит переключение на следующий флаг или следующие данные); для каждых из данных изображения R, G и B момент спада является моментом времени, когда прошел период времени twSCLKH от момента нарастания последовательного тактового сигнала SCLK, и является моментом окончания передачи данных изображения (то есть моментом, в котором происходит переключение на следующий флаг или следующие данные). Период времени tsSCLK равен периоду времени twSCLKH, и каждый из периода времени tsSCLK и периода времени twSCLKH равен периоду, в котором последовательный тактовый сигнал SCLK равен High. Рабочий цикл последовательного тактового сигнала SCLK здесь равен 50%.

Сигнал последовательного выбора кристалла SCS является сигналом, который становится High в течение периода времени twSCSH в случае, где последовательные данные SI и последовательный тактовый сигнал SCLK передаются тактовому генератору 25 от CPU по шине последовательного интерфейса I/F BUS. В кадре для передачи последовательных данных SI и последовательного тактового сигнала SLCK сигнал последовательного выбора кристалла SCS становится High в периоде времени tsSCS до момента начала передачи последовательных данных SI, и становится Low в периоде времени thSCS после момента окончания передачи последовательных данных SI. Дополнительно сигнал последовательного выбора кристалла SCS становится Low в течение периода времени twSCSL после периода High. Период времени twSCSH и период времени twSCSL составляют один период кадровой развертки tV, который включает в себя кадровый период гашения.

Данные изображения, записанные в память 30 пикселя в режиме обновления данных из фиг.2, удерживаются в режиме отображения из фиг.3. Как в режиме обновления данных, так и в режиме отображения, последовательные данные SI содержат добавленные в них флаги D0, D1 и D2, и флаг D1 переключается между High и Low в каждом кадре. Таким образом, флаг D1 также является флагом, который задает начало одного кадра.

Из поступивших таким образом последовательных данных SI, последовательного тактового сигнала SCLK и сигнала последовательного выбора кристалла SCS последовательно-параллельный преобразователь 25a извлекает (i) флаги D0, D1 и D2 и (ii) данные DR в R, данные DG в G и данные DB в B. Флаг D0 используется в качестве сигнала режима MODE, флаг D1 используется в качестве сигнала кадра D1, а флаг D2 используется в качестве сигнала общей очистки ACL для формирования сигнала в других схемах. Данные DR, DG и DB поступают в защелку 23b данных в двоичном формирователе 23.

Дополнительно в соответствии с последовательными данными SI, последовательным тактовым сигналом SCLK и сигналом последовательного выбора кристалла SCS последовательно-параллельный преобразователь 25a формирует тактовые сигналы истока SCK и SCKB и начальный сигнал INI. Тактовые сигналы истока SCK и SCKB поступают в двоичный формирователь 23, а начальный сигнал INI используется для формирования сигнала в другой схеме.

Впоследствии, в соответствии с сигналом режима MODE и тактовыми сигналами истока SCK и SCKB, поступившими от последовательно-параллельного преобразователя 25a, участок 25b формирования пускового импульса для истока формирует пусковой импульс истока SSP для начального строчного периода отображения и передает пусковой импульс истока SSP в сдвиговый регистр 23a двоичного формирователя 23. Пусковой импульс истока SSP для начального строчного периода отображения может формироваться с использованием момента нарастания, в котором сигнал режима MODE становится High. Пусковые импульсы истока SSP для второго строчного периода отображения и последующего строчного периода отображения могут формироваться с использованием второго конечного разряда END-BIT2, сформированного участком 25c удержания END-BIT (описанного позже).

В соответствии с выходом оконечного каскада сдвигового регистра 23a в двоичном формирователе 23 участок 25c удержания END-BIT формирует первый конечный разряд END-BIT 1 и второй конечный разряд END-BIT 2, и передает первый конечный разряд END-BIT 1 и второй конечный разряд END-BIT 2 в участок 25d формирования управляющего сигнала для схемы управления затвором. Первый конечный разряд END-BIT 1 формируется путем дополнительного сдвига выхода оконечного каскада сдвигового регистра 23a на заранее установленное количество разрядов с использованием фиктивного сдвигового регистра. Второй конечный разряд END-BIT 2 формируется путем дополнительного сдвига первого конечного разряда END-BIT 1 на один разряд с использованием фиктивного сдвигового регистра.

В соответствии с первым конечным разрядом END-BIT 1, вторым конечным разрядом END-BIT 2, сигналом режима MODE и сигналом общей очистки ACL участок 25d формирования управляющего сигнала для схемы управления затвором формирует тактовые сигналы затвора GCK1B и GCK2B, пусковой импульс затвора GSP и разрешающий сигнал затвора GEN, и передает тактовые сигналы затвора GCK1B и GCK2B, пусковой импульс затвора GSP и разрешающий сигнал затвора GEN в схему 24 управления затвором.

Впоследствии, в соответствии с (i) пусковым импульсом истока SSP, поступившим от участка 25b формирования пускового импульса для истока в тактовом генераторе 25, и (ii) начальным сигналом INI, поступившим от последовательно-параллельного преобразователя 25a в тактовом генераторе 25, сдвиговый регистр 23a в двоичном формирователе 23 формирует выходы SR на соответствующих каскадах. Защелка 23b данных включает в себя первую схему-защелку 23c и схему 23d общей очистки. В выходные моменты у SR на соответствующих каскадах в сдвиговом регистре 23a первая схема-защелка 23c последовательно фиксирует данные DR, DG, и DB, поступившие от последовательно-параллельного преобразователя 25a в тактовом генераторе 25, и выводит зафиксированные данные DR, DG и DB в их соответствующие шины истоков SL (SL1-SL96 для каждого из R, G и B). В случае, где флаг D2 в последовательных данных SI равен High, при приеме активного сигнала общей очистки ACL, поступившего от последовательно-параллельного преобразователя 25a в тактовом генераторе 25, схема 23d общей очистки выводит данные отображения белого во все шины истоков SL.

Схема 24 управления затвором включает в себя сдвиговый регистр 24a, множество буферов 24b и множество инверсионных буферов 24c. В соответствии с (i) тактовыми сигналами затвора GCK1B и GCK2B, пусковым импульсом затвора GSP и разрешающим сигналом затвора GEN, каждый из которых поступил из участка 25d формирования управляющего сигнала для схемы управления затвором в тактовом генераторе 25, и (ii) начальным сигналом INI, поступившим от последовательно-параллельного преобразователя 25a, сдвиговый регистр 24a формирует выходы SR на соответствующих каскадах. Один из буферов 24b и соответствующий буфер из инверсионных буферов 24c образуют пару, и такая пара предоставляется для каждой строки пикселей. Входы буфера 24b и инверсионного буфера 24c, которые образуют пару, подключаются к выходу SR на соответствующем каскаде в сдвиговом регистре 24a. Выход буфера 24b подключается к соответствующей шине затворов GL (соответствующей из GL1-GL60), а выход инверсионного буфера 24c подключается к соответствующей шине затворов GLB (соответствующей из GLB1-GLB60).

В соответствии с (i) сигналом кадра FRAME, поступившим от последовательно-параллельного преобразователя 25a в тактовом генераторе 25, и (ii) источниками питания VDD и VSS схема 26 управления Vcom формирует общий выход Vcom, выход полярности черного VA и выход полярности белого VB, и передает общий выход Vcom, выход полярности черного VA и выход полярности белого VB в активную область 22.

Фиг.7 показывает пример подробной конфигурации последовательно-параллельного преобразователя 25a.

Последовательные данные SI проходят через D-триггеры 41, 42 и 43 по порядку, и эти D-триггеры 41, 42 и 43 соединены каскадом. В случае, где выход S2 D-триггера 43 на третьем каскаде проходит через D-триггер 44, извлекается сигнал режима MODE. В случае, где выход S1 D-триггера 42 на втором каскаде проходит через D-триггер 45, извлекается сигнал кадра FRAME. В случае, где выход S0 D-триггера 41 на первом каскаде проходит через D-триггер 46, извлекается сигнал общей очистки ACL. Предположим, что данные изображения организуются в порядке R, G и B во временном ряду. В этом случае в случае, где выход S2 проходит через D-триггер 47, извлекаются данные DR; в случае, где выход S1 проходит через D-триггер 48, извлекаются данные DG; и в случае, где выход S0 проходит через D-триггер 49, извлекаются данные DB.

Последовательный тактовый сигнал SCLK вводится в высокоактивные входы синхронизации CK в D-триггерах 41, 42 и 43. Выход DEN вентиля 55 ИЛИ-НЕ, имеющего два входа, вводится в низкоактивные входы синхронизации CK в D-триггерах 44, 45 и 46. Выход A у D-триггера 51 вводится в низкоактивные входы синхронизации CK в D-триггерах 47, 48 и 49.

Один из входов вентиля 55 ИЛИ-НЕ (NOR) подключается к выходу D-триггера 53, а другой из входов подключается к выходу C вентиля 54 И-НЕ, имеющего два входа. Вход D-триггера 53 подключается к источнику питания VDD, а низкоактивный вход синхронизации CK у D-триггера 53 подключается к выходу B в D-триггере 52. Один из входов вентиля 54 И-НЕ подключается к выходу B, и другой из входов подключается к выходу A. Вход D-триггера 51 подключается к выходу C. Вход D-триггера 52 подключается к выходу A. Последовательный тактовый сигнал SCLK вводится в низкоактивные входы синхронизации CK в D-триггерах 51 и 52.

Тактовый сигнал истока SCKB получается путем пропускания выхода D-триггера 56 через инвертор 57. Тактовый сигнал истока SCK получается путем пропускания выхода инвертора 57 через инвертор 58. Вход D-триггера 56 подключается к выходу инвертора 57, а высокоактивный вход синхронизации CK у D-триггера 56 подключается к выходу B.

В каждом из D-триггеров сигнал запуска с положительным фронтом возникает на высокоактивном входе синхронизации CK, тогда как сигнал запуска с отрицательным фронтом возникает на низкоактивном входе синхронизации CK.

Сигнал последовательного выбора кристалла SCS вводится во вход сброса R в каждом из D-триггеров с 44 по 53 и 56. Начальный сигнал INI сам по себе является сигналом последовательного выбора кристалла SCS.

Фиг.12 показывает временную диаграмму, иллюстрирующую соответствующие формы сигналов у последовательного тактового сигнала SCLK, выходов A, B и C, тактовых сигналов истока SCK и SCKB и выхода DEN.

Фиг.8 показывает пример подробной конфигурации участка 25c удержания END-BIT.

Сдвиговый регистр 23a в двоичном формирователе 23 включает в себя RS-триггеры, которые соединены каскадом. Фиг.8 показывает RS-триггеры B95 и B96, которые являются двумя последними (95ым и 96ым) каскадами RS-триггеров. Выход Q (B94) RS-триггера B94, предшествующего RS-триггеру B95, поступает на вход установки в состояние у RS-триггера B95. Участок 25c удержания END-BIT включает в себя фиктивные RS-триггеры DMY1, DMY2, DMY3 и DMY4, которые аналогичным образом соединены по порядку каскадом, где DMY1 подключается к оконечному каскаду сдвигового регистра 23a. В этих RS-триггерах на RS-триггер поступает выход следующего каскада в качестве сигнала сброса. Однако в RS-триггер DMY4 в качестве сигнала сброса поступает сигнал, который выводится им самим и задерживается двумя инверторами.

Выход RS-триггера DMY2 получается в виде первого конечного разряда END-BIT 1, а выход RS-триггера DMY3 получается в виде второго конечного разряда END-BIT 2.

Фиг.9 показывает пример подробной конфигурации участка 25b формирования пускового импульса для истока.

Сигнал режима MODE вводится в один (низкоактивный) из двух входов вентиля 61 ИЛИ-НЕ, а второй конечный разряд END-BIT 2 вводится в другой (высокоактивный) из входов. Выход вентиля 61 ИЛИ-НЕ вводится в D-защелку 62, а выход D-защелки 62 вводится в D-защелку 63. Тактовый сигнал истока SCKB, сформированный последовательно-параллельным преобразователем 25a, вводится в разрешающий вход EN D-защелки 62 и разрешающий вход ENB D-защелки 63. Тактовый сигнал истока SCK, сформированный последовательно-параллельным преобразователем 25a, вводится в разрешающий вход ENB D-защелки 62 и разрешающий вход EN D-защелки 63. Выходы D-защелок 62 и 63 вводятся в вентиль 64 ИЛИ-НЕ, имеющий два входа. Выход вентиля 64 ИЛИ-НЕ и сигнал режима MODE вводятся в вентиль 65 И-НЕ, имеющий два входа, и выход вентиля 65 И-НЕ служит в качестве пускового импульса истока SSP.

Фиг.10 показывает пример подробной конфигурации участка 25d формирования управляющего сигнала для схемы управления затвором.

Первый конечный разряд END-BIT 1 вводится в высокоактивный вход синхронизации CK и низкоактивный вход синхронизации CKB у D-триггера 71. Выход D-триггера 71 вводится в D-триггер 72. Второй конечный разряд END-BIT 2 вводится в низкоактивный вход синхронизации CK и высокоактивный вход синхронизации CKB у D-триггера 72. Выход D-триггера 72 вводится в D-триггер 71. Выходы D-триггеров 71 и 72 вводятся в два входа вентиля 73 И-НЕ и два входа вентиля 76 ИЛИ-НЕ. Выход вентиля 73 И-НЕ и сигнал общей очистки ACL вводятся в вентиль 74 И-НЕ, имеющий два входа. Выход вентиля 74 И-НЕ и начальный сигнал INI вводятся в вентиль 75 И-НЕ, имеющий два входа. Выход вентиля 75 И-НЕ служит в качестве тактового сигнала затвора GCK2B.

Выход вентиля 76 ИЛИ-НЕ и сигнал режима MODE вводятся в вентиль 77 И-НЕ, имеющий два входа. Выход вентиля 77 И-НЕ и сигнал общей очистки ACL вводятся в вентиль 78 И-НЕ, имеющий два входа. Выход вентиля 78 И-НЕ и начальный сигнал INI вводятся в вентиль 79 И-НЕ, имеющий два входа. Выход вентиля 79 И-НЕ служит в качестве тактового сигнала затвора GCK1B.

Сигнал режима MODE также вводится в D-защелку 80. Первый конечный разряд END-BIT 1 вводится в разрешающие входы EN и ENB в D-защелке 80. Выход D-защелки 80 является входным сигналом высокоактивного входа вентиля 81 ИЛИ-НЕ, имеющего два входа, и сигнал режима MODE является входным сигналом низкоактивного входа вентиля 81 ИЛИ-НЕ. Выход вентиля 81 ИЛИ-НЕ и сигнал общей очистки ACL вводятся в вентиль 82 ИЛИ-НЕ, имеющий два входа. Выход вентиля 82 ИЛИ-НЕ и начальный сигнал INI вводятся в вентиль 83 ИЛИ-НЕ, имеющий два входа. Выход вентиля 83 ИЛИ-НЕ служит в качестве пускового импульса затвора GSP.

Первый конечный разряд END-BIT 1 и второй конечный разряд END-BIT 2 также вводятся в вентиль 84 ИЛИ-НЕ, имеющий два входа. Выход вентиля 84 ИЛИ-НЕ вводится в низкоактивный вход синхронизации CK и высокоактивный вход синхронизации CKB у D-триггера 85. Выход D-триггера 85 вводится в инвертор 86, а вход D-триггера 85 подключается к выходу инвертора 86. Выход инвертора 86 и сигнал общей очистки ACL вводятся в вентиль 87 ИЛИ-НЕ, имеющий два входа. Выход вентиля 87 ИЛИ-НЕ и начальный сигнал INI вводятся в вентиль 88 ИЛИ-НЕ. Выход вентиля 88 ИЛИ-НЕ служит в качестве разрешающего сигнала затвора GEN.

Начальный сигнал INI вводится в соответствующие начальные входы INI D-триггеров 71, 72 и 85 и D-защелки 80. D-триггер 71 относится к типу со срабатыванием по положительному фронту, а D-триггеры 72 и 85 относятся к типу со срабатыванием по отрицательному фронту.

Временная диаграмма по фиг.13 показывает соответствующие формы сигналов у тактовых сигналов затвора GCK1B и GCK2B, разрешающего сигнала затвора GEN и выходов шины затворов GL (GL1 и GL2). Сдвиг 1 указывает период, в котором данные DR, DG и DB для первого выхода шины затворов GL1 выводятся в шину истока SL. Сдвиг 2 указывает период, в котором данные DR, DG и DB для второго выхода шины затворов GL2 выводятся в шину истока SL. Данные изображения записываются в память 30 пикселя за один раз с использованием разрешающего сигнала затвора GEN в конце строчного периода отображения. Поэтому, даже если колебание в электрическом потенциале шины истока SL происходит в период, в котором данные DR, DG и DB выводятся в шину истока SL по порядку, это оказывает меньшее влияние на память 30 пикселя, хранящую данные изображения.

Фиг.11 показывает подробную конфигурацию схемы управления Vcom.

Сигнал кадра FRAME вводится через буфер в качестве управляющего сигнала для ключей SW1, SW2 и SW3, каждый из которых соответствует переключающему контакту. Ключ SW1 является ключом для вывода напряжения для общего выхода Vcom; ключ SW2 является ключом для вывода напряжения для выхода полярности черного VA; и ключ SW3 является ключом для вывода напряжения для выхода полярности белого VB. Каждый раз, когда сигнал кадра FRAME переключается между High и Low, ключи SW1, SW2 и SW3 выбирают источник питания, чтобы (i) сочетание источников питания VDD, VSS и VDD и (ii) сочетание источников питания VSS, VDD и VSS переключались по очереди.

Как описано выше, устройство отображения из настоящего варианта осуществления является устройством отображения активноматричного типа, и включает в себя устройство управления дисплеем, в которое с помощью последовательной передачи поступают данные изображения, включенные в последовательные данные, причем последовательные данные содержат добавленный в них первый флаг для указания начала одного периода кадровой развертки, устройство управления дисплеем извлекает первый флаг и данные изображения из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, переданного по шине, используемой для последовательной передачи, но отличной от шины для последовательных данных, в соответствии с синхронизацией последовательного тактового сигнала, устройство управления дисплеем формирует сигнал синхронизации, служащий в качестве синхросигнала для функционирования сдвигового регистра в формирователе сигнальной линии данных, включенном в устройство управления дисплеем, в соответствии с первым флагом и сигналом синхронизации, служащим в качестве синхросигнала для функционирования сдвигового регистра, устройство управления дисплеем формирует сигнал синхронизации для начального периода строчной развертки в одном периоде кадровой развертки, и вводит сигнал синхронизации для начального периода строчной развертки в сдвиговый регистр формирователя сигнальной линии данных в случае, где существует следующий период строчной развертки, устройство управления дисплеем формирует сигнал синхронизации для следующего периода строчной развертки в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, и вводит сигнал синхронизации для следующего периода строчной развертки в сдвиговый регистр в формирователе сигнальной линии данных, в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, устройство управления дисплеем формирует сигнал синхронизации, который нужно ввести в сдвиговый регистр в формирователе сигнальной линии развертки, включенном в устройство управления дисплеем, и в соответствии с сигналами синхронизации для начального периода строчной развертки и последующего периода строчной развертки, и сигналом развертки, доставленным формирователем сигнальной линии развертки, устройство управления дисплеем записывает данные изображения в пиксели.

В соответствии с предшествующей конфигурацией устройство управления дисплеем извлекает, в соответствии с синхронизацией последовательного тактового сигнала, первый флаг и данные изображения из последовательных данных, поступивших с помощью последовательной передачи. Затем устройство управления дисплеем формирует сигнал синхронизации для начального периода строчной развертки в одном периоде кадровой развертки в соответствии с первым флагом, и вводит сигнал синхронизации в сдвиговый регистр в формирователе сигнальной линии данных. Устройство управления дисплеем последовательно формирует сигналы синхронизации для второго периода строчной развертки и последующего периода строчной развертки в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных.

Таким образом, устройство управления дисплеем с помощью непосредственного контроля последовательной передачи может формировать сигнал синхронизации для записи данных изображения в пиксель. То есть устройство управления дисплеем без труда может сформировать сигнал синхронизации без постоянного использования генератора и т.п.

Вышеприведенная конфигурация позволяет без труда формировать, в схеме формирователя, сигнал синхронизации для записи данных изображения в пиксель.

Как описано выше, устройство отображения из настоящего варианта осуществления является устройством отображения активноматричного типа, и включает в себя устройство управления дисплеем, в которое данные изображения, включенные в последовательные данные, поступают с помощью последовательной передачи, причем последовательные данные содержат добавленный в них первый флаг для задания полярности напряжения общего электрода, устройство управления дисплеем извлекает первый флаг из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, переданного по шине, используемой для последовательной передачи, но отличной от шины для последовательных данных, и устройство управления дисплеем выполняет отображение в соответствии с последовательными данными, подавая напряжение общего электрода, каковое напряжение обладает полярностью, заданной извлеченным первым флагом.

В соответствии с вышеприведенной конфигурацией устройство управления дисплеем извлекает, в соответствии с синхронизацией последовательного тактового сигнала, первый флаг из последовательных данных, поступивших с помощью последовательной передачи, определяет полярность напряжения общего электрода в соответствии с первым флагом и выполняет отображение. Поэтому устройство управления дисплеем может формировать сигнал синхронизации для переменного общего напряжения путем непосредственного контроля последовательной передачи. Это устраняет необходимость в генераторе или специальном управляющем терминале для внешнего управления формированием сигнала синхронизации для переменного общего напряжения, посредством этого позволяя сокращение размера схемы в устройстве управления дисплеем.

Вышеприведенная конфигурация позволяет реализовать устройство отображения, допускающее формирование сигнала синхронизации для переменного общего напряжения, имея небольшую схему.

В настоящем варианте осуществления флаги D0, D1 и D2 помещаются в заголовок кадра. Однако настоящее изобретение этим не ограничивается. В качестве альтернативы флаги могут помещаться в нужный момент, в который нужно дать указание тактовому генератору 25. Например, чтобы переключать флаг D1 между High и Low в каждом периоде, кратном периоду строчной развертки, флаги могут помещаться в начало каждого периода строчной развертки.

Дополнительно в настоящем варианте осуществления сигнал последовательного выбора кристалла SCS используется для формирования различных сигналов синхронизации, но сигнал последовательного выбора кристалла SCS необходим не всегда. Например, вместо использования сигнала последовательного выбора кристалла SCS последовательно-параллельный преобразователь 25a может быть всегда установлен в состояние разрешенного приема для последовательных данных.

Кроме того, описанное в настоящем варианте осуществления является конфигурацией, в которой активная область 22 включает в себя память 30 пикселя. Однако настоящее изобретение этим не ограничивается. Настоящее изобретение также применимо к устройству отображения, имеющему активную область, не оборудованную памятью пикселя, при условии, что устройство отображения имеет конфигурацию, в которой флаг D0 не отличает режим обновления данных от режима отображения.

К тому же настоящий вариант осуществления имеет конфигурацию, в которой сдвиговый регистр 23a в двоичном формирователе 23 может выполнять операцию сдвига просто в ответ на пусковой импульс истока SSP, поступивший в качестве входного сигнала установки в состояние для первого каскада. Поэтому тактовые сигналы истока SCK и SCKB, сформированные последовательно-параллельным преобразователем 25a, используются для формирования пускового импульса истока SSP в участке 25b формирования пускового импульса для истока, чтобы тактовые сигналы истока SCK и SCKB функционировали в качестве синхросигналов для работы сдвигового регистра в формирователе сигнальной линии данных. Однако настоящее изобретение этим не ограничивается. Настоящее изобретение также может иметь конфигурацию, в которой (i) сдвиговый регистр в формирователе сигнальной линии данных выполняет операцию сдвига в ответ на синхросигнал, поступивший на каждый каскад, и (ii) сформированные тактовые сигналы истока SCK и SCKB используются для формирования пускового импульса истока SSP и вводятся в каждый каскад сдвигового регистра в формирователе сигнальной линии данных, чтобы вызвать работу каждого каскада в сдвиговом регистре, чтобы тактовые сигналы истока SCK и SCKB функционировали в качестве синхросигналов для работы сдвигового регистра в формирователе сигнальной линии данных.

Настоящее изобретение не ограничивается описанием вариантов осуществления выше, а может изменяться специалистом в рамках объема формулы изобретения. Вариант осуществления на основе надлежащего сочетания технических средств, раскрытых в разных вариантах осуществления, включается в технический объем настоящего изобретения. Например, настоящее изобретение применимо к электролюминесцентному устройству отображения.

ПРОМЫШЛЕННАЯ ПРИМЕНИМОСТЬ

Настоящее изобретение соответствующим образом применимо, в частности, к мобильному терминалу.

Изобретение относится к сигналу синхронизации, используемому для операции отображения в устройстве отображения (дисплейном устройстве). Тенический результат заключается в реализации устройства отображения, выполненное с возможностью формировать в схеме формирователя сигнал синхронизации для записи данных изображения в пиксели. Такой технический результат достигается за счет того, что устройство отображения по настоящему изобретению является устройством отображения активноматричного типа и включает в себя устройство управления дисплеем, в которое с помощью последовательной передачи поступают данные изображения (DR, DG и DB), включенные в последовательные данные (SI). Последовательные данные (SI) содержат добавленный в них первый флаг (D1) для задания полярности напряжения (Vcom) у общего электрода. Устройство управления дисплеем в соответствии с синхронизацией последовательного тактового сигнала (SCLK) формирует сигнал синхронизации (SSP) для периода строчной развертки для формирователя сигнальной линии данных (23) и сигнал синхронизации (GEN) для формирователя сигнальной линии затвора (24). 2 н. и 11 з.п. ф-лы, 16 ил.

1. Устройство отображения активноматричного типа, содержащее:

устройство управления дисплеем, в которое с помощью последовательной передачи поступают данные изображения, включенные в последовательные данные,

причем последовательные данные содержат добавленный в них первый флаг для указания начала одного периода кадровой развертки,

при этом устройство управления дисплеем извлекает первый флаг и данные изображения из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, переданного по шине, используемой для последовательной передачи, но отличной от шины для последовательных данных,

при этом устройство управления дисплеем в соответствии с синхронизацией последовательного тактового сигнала формирует сигнал синхронизации, служащий в качестве синхросигнала для функционирования сдвигового регистра в формирователе сигнальной линии данных, включенном в устройство управления дисплеем,

при этом устройство управления дисплеем в соответствии с первым флагом и сигналом синхронизации, служащим в качестве синхросигнала для функционирования сдвигового регистра, формирует сигнал синхронизации для начального периода строчной развертки в одном периоде кадровой развертки и вводит сигнал синхронизации для начального периода строчной развертки в сдвиговый регистр формирователя сигнальной линии данных,

при этом устройство управления дисплеем в случае, когда существует следующий период строчной развертки, формирует сигнал синхронизации для следующего периода строчной развертки в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, и вводит сигнал синхронизации для следующего периода строчной развертки в сдвиговый регистр формирователя сигнальной линии данных,

при этом устройство управления дисплеем в соответствии с сигналом, сдвинутым на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, формирует сигнал синхронизации, который нужно ввести в сдвиговый регистр формирователя сигнальной линии развертки, включенного в устройство управления дисплеем, и

при этом устройство управления дисплеем записывает данные изображения в пиксели в соответствии с сигналами синхронизации для начального периода строчной развертки и следующего периода строчной развертки и сигналом развертки, поступившим от формирователя сигнальной линии развертки.

2. Устройство отображения по п.1, в котором:

каждый из пикселей включает в себя память пикселя для хранения данных изображения, переданных устройством управления дисплеем;

в случае, когда память пикселя хранит данные изображения, последовательные данные включают в себя данные изображения для сохранения в памяти пикселя, и последовательные данные содержат добавленный в них первый флаг; и

в случае, когда отображаются данные изображения, сохраненные в памяти пикселя, последовательные данные включают в себя, вместо данных изображения для сохранения в памяти пикселя, фиктивные данные не для передачи в пиксели, и последовательные данные содержат добавленный в них первый флаг.

3. Устройство отображения по п.2, в котором:

сигнал развертки является сигналом, который дает возможность данным изображения записываться в память пикселя после того, как все данные изображения выводятся в сигнальную линию данных в каждом строчном периоде отображения.

4. Устройство отображения по п.2, в котором:

последовательные данные содержат добавленный в них второй флаг, указывающий, включают ли в себя последовательные данные данные изображения для сохранения в памяти пикселя; и

устройство управления дисплеем извлекает второй флаг из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, и в случае, когда второй флаг указывает, что последовательные данные включают в себя данные изображения для сохранения в памяти пикселя, устройство управления дисплеем извлекает данные изображения из последовательных данных и сохраняет данные изображения в памяти пикселя.

5. Устройство отображения по п.2, в котором:

последовательные данные содержат добавленный в них третий флаг, дающий указание в отношении того, инициализировать ли отображение всех пикселей; и

устройство управления дисплеем извлекает третий флаг из последовательных данных в соответствии с синхронизацией последовательного тактового сигнала, и в случае, когда указание в третьем флаге означает инициализацию отображения всех пикселей, устройство управления дисплеем инициализирует отображение всех пикселей.

6. Устройство отображения по п.1, в котором:

первый флаг, добавленный в последовательные данные, служит в качестве флага для дополнительного задания полярности напряжения у общего электрода.

7. Устройство отображения по п.1, в котором:

в последовательной передаче сигнал последовательного выбора кристалла, указывающий, выполнять ли отображение, передается по шине, отличной от шин для последовательных данных и последовательного тактового сигнала.

8. Устройство отображения по п.1, в котором:

каждый из пикселей включает в себя аналоговый ключ, выполненный из схемы CMOS.

9. Устройство отображения по п.8, в котором:

устройство управления дисплеем составляет единое целое с панелью дисплея.

10. Устройство отображения по п.1, в котором:

каждый из пикселей включает в себя элемент отображения, использующий жидкий кристалл с диспергированным полимером.

11. Устройство отображения по п.1, в котором:

каждый из пикселей включает в себя элемент отображения, использующий стабилизированный полимерной сеткой жидкий кристалл.

12. Устройство отображения по п.1, в котором:

сигнал, сдвинутый на один строчный период отображения посредством сдвигового регистра в формирователе сигнальной линии данных, сдвигается на заранее установленное количество ступеней с использованием фиктивного сдвигового регистра, так что формируется первый конечный разряд, и первый конечный разряд дополнительно сдвигается на одну ступень посредством фиктивного сдвигового регистра, так что формируется второй конечный разряд;

второй конечный разряд используется для формирования сигнала синхронизации для следующего периода строчной развертки для формирователя сигнальной линии данных; и

первый конечный разряд и второй конечный разряд используются для формирования сигнала синхронизации, который нужно ввести в сдвиговый регистр формирователя сигнальной линии развертки.

13. Мобильный терминал, содержащий устройство отображения по п.1, причем устройство отображения служит в качестве модуля отображения.

| АППАРАТНОЕ УСКОРЕНИЕ ГРАФИЧЕСКИХ ОПЕРАЦИЙ ПРИ ПОСТРОЕНИИ ИЗОБРАЖЕНИЙ НА ОСНОВЕ ПИКСЕЛЬНЫХ ПОДКОМПОНЕНТОВ | 2003 |

|

RU2312404C2 |

| JP 2007133263 A, 31.05.2007 | |||

| JP 2006119409 A, 11.05.2006 | |||

| RU 2003131333 A, 10.04.2005 | |||

| Устройство для закрывания,клеймения и фиксации клапанов картонных коробок | 1985 |

|

SU1306827A1 |

Авторы

Даты

2012-04-10—Публикация

2009-01-29—Подача