Изобретение относится к электронной технике СВЧ, а именно к гибридным интегральным схемам СВЧ-диапазона, и может быть использовано в твердотельных модулях СВЧ различного назначения.

Известна гибридная интегральная схема СВЧ-диапазона (далее гибридная интегральная схема), содержащая диэлектрическую подложку, на лицевой стороне которой расположен топологический рисунок металлизационного покрытия, а на обратной - экранное заземляющее металлизационное покрытие, конденсаторы, под которыми расположены металлизированные отверстия, при этом нижние обкладки конденсаторов соединены через металлизированные отверстия с экранным заземляющим металлизационным покрытием. На лицевой стороне диэлектрической подложки выполнено углубление, в котором расположен кристалл полупроводникового прибора в одной плоскости с лицевой стороной диэлектрической подложки и соединен с ним связующим веществом. Выводы кристалла полупроводникового прибора соединены с верхними обкладками конденсаторов и топологическим рисунком металлизационного покрытия. При этом диэлектрическая подложка расположена обратной стороной на металлическом теплоотводящем основании и соединена с ним связующим электро- и теплопроводящим веществом.

В которой с целью улучшения отвода тепла от кристалла полупроводникового прибора и тем самым повышения надежности и улучшения электрических характеристик гибридной интегральной схемы, металлизированные отверстия выполнены глухими с лицевой стороны диэлектрической подложки с толщиной дна, равной не более 0,5 мм.

Это позволило:

- использовать металлизационное покрытие дна глухих отверстий в качестве нижних обкладок конденсаторов;

- использовать остаточную толщину диэлектрической подложки в металлизированных глухих отверстиях в качестве слоя диэлектрика конденсаторов;

- формировать верхние обкладки конденсаторов в составе топологического рисунка металлизации.

Все это в свою очередь позволило исключить часть паянных электрических соединений из гибридной интегральной схемы и тем самым повысить ее надежность и улучшить электрические характеристики.

Однако данная гибридная интегральная схема СВЧ-диапазона отличается:

- низкими массогабаритными характеристиками вследствие практически невозможности получения тонкого слоя диэлектрика конденсатора, толщиной менее 0,05 мм, и что тем самым и определяет значительные его геометрические размеры и соответственно низкие массогабаритные характеристики гибридной интегральной схемы,

- высокой трудоемкостью и низкой технологичностью изготовления вследствие использования достаточно сложных и трудоемких технологических операций, прежде всего при выполнении углублений с обеих сторон диэлектрической подложки.

Известна гибридная интегральная схема СВЧ-диапазона, содержащая диэлектрическую подложку, на лицевой стороне которой расположен топологический рисунок металлизационного покрытия, а на обратной стороне - экранное заземляющее металлизационное покрытие, при этом диэлектрическая подложка расположена обратной стороной на металлическом теплоотводящем основании и соединена с ним электро- и теплопроводящим веществом, по меньшей мере, одну металлизированную посадочную площадку, электрически соединенную с экранным заземляющим металлизационным покрытием, по меньшей мере, один транзистор с выводами (электродами), по меньшей мере, два конденсатора, расположенные с разных сторон транзистора [2 - прототип].

При этом один из выводов транзистора электрически соединен с верхними обкладками конденсаторов, два другие его вывода электрически соединены с топологическим рисунком металлизационного покрытия, нижние обкладки конденсаторов электрически соединены с металлизированной посадочной площадкой и через нее с экранным заземляющим металлизационным покрытием.

При этом каждые - транзистор с выводами, оба конденсатора и электрические соединения одного из выводов транзистора с верхними обкладками конденсаторов - выполнены в виде, по меньшей мере, одного единого кристалла монолитной интегральной схемы на полуизолирующей полупроводниковой структуре с заданными активными слоями, упомянутый единый кристалл расположен на металлизированной посадочной площадке.

При этом оба конденсатора выполнены пленочными.

Верхние обкладки конденсаторов, выводы транзистора и электрические соединения, по меньшей мере, одного из выводов транзистора с верхними обкладками конденсаторов выполнены в одном слое металлизационного покрытия единого кристалла монолитной интегральной схемы.

В едином кристалле монолитной интегральной схемы непосредственно под нижними обкладками конденсаторов выполнены сквозные металлизированные отверстия для электрического соединения нижних обкладок конденсаторов с металлизированной посадочной площадкой.

Недостатки данной гибридной интегральной схемы СВЧ-диапазона заключаются в сложности, а иногда невозможности подключения дополнительных схемных элементов и особенно в часть схемы, выполненной в составе единого кристалла монолитной интегральной схемы, что ограничивает функциональные возможности, например реализацию режима однополярного питания (так называемый режим автосмещения), и тем самым ограничивает возможности дальнейшего улучшения электрических и массогабаритных характеристик.

Техническим результатом изобретения является улучшение электрических и массогабаритных характеристик и их воспроизводимости, за счет расширения функциональных возможностей гибридной интегральной схемы СВЧ-диапазона, повышение технологичности и надежности.

Указанный технический результат достигается гибридной интегральной схемой СВЧ-диапазона, содержащей

- диэлектрическую подложку, на лицевой стороне которой расположен топологический рисунок металлизационного покрытия, а на обратной стороне - экранное заземляющее металлизационное покрытие, при этом диэлектрическая подложка расположена обратной стороной на металлическом теплоотводящем основании и соединена с ним электро- и теплопроводящим веществом,

- по меньшей мере, одну металлизированную посадочную площадку, электрически соединенную с экранным заземляющим металлизационным покрытием,

- по меньшей мере, один транзистор с выводами (электродами),

- по меньшей мере, два конденсатора, расположенные с разных сторон транзистора,

- при этом один из выводов транзистора электрически соединен с верхними обкладками конденсаторов, два другие его вывода электрически соединены с топологическим рисунком металлизационного покрытия, нижние обкладки конденсаторов электрически соединены с металлизированной посадочной площадкой и через нее с экранным заземляющим металлизационным покрытием,

- при этом каждые - транзистор с выводами, два конденсатора и упомянутые электрические соединения одного из выводов транзистора - выполнены в виде, по меньшей мере, одного единого кристалла монолитной интегральной схемы на полуизолирующей полупроводниковой структуре с заданными легированными слоями,

- упомянутый единый кристалл расположен на металлизированной посадочной площадке,

- оба конденсатора выполнены пленочными,

- верхние обкладки конденсаторов, выводы транзистора и упомянутые электрические соединения одного из выводов транзистора выполнены в одном слое металлизационного покрытия упомянутого единого кристалла,

- в последнем выполнены сквозные металлизированные отверстия для электрического соединения нижних обкладок конденсаторов с металлизированной посадочной площадкой.

В которой

- транзистор выполнен в виде полевого транзистора с барьером Шотки (ПТШ) с шириной вывода - электрода затвора не более 500 мкм, с заданными величинами тока насыщения, не превышающего 150 мА, и напряжения отсечки,

- каждый единый кристалл монолитной интегральной схемы дополнительно содержит, по меньшей мере, один резистивный элемент с заданным электрическим сопротивлением,

- резистивный элемент выполнен пленочным на лицевой поверхности упомянутого единого кристалла или в виде легированного слоя в составе упомянутой полупроводниковой структуры,

- резистивный элемент расположен вне области канала полевого транзистора с барьером Шотки на расстоянии не менее 20 мкм от электрода истока,

- при этом один из концов резистивного элемента электрически соединен с верхней обкладкой одного из конденсаторов, а другой - с нижней обкладкой этого конденсатора, электрическое соединение одного из концов резистивного элемента с верхней обкладкой конденсатора выполнено в упомянутом одном слое металлизационного покрытия единого кристалла, а электрическое соединение другого конца резистивного элемента и нижние обкладки конденсаторов - в другом слое этого металлизационного покрытия,

- сквозные металлизированные отверстия в упомянутом едином кристалле выполнены вне площади расположения конденсаторов,

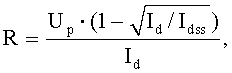

- при этом электрическое сопротивление резистивного элемента задано исходя из соотношения

,

,

где

Up - заданное напряжение отсечки полевого транзистора с барьером Шотки,

Id - рабочий ток полевого транзистора с барьером Шотки,

Idss - заданный максимальный ток насыщения при нулевом напряжении на затворе полевого транзистора с барьером Шотки (далее ток насыщения),

а рабочий ток выбран из соотношения

Id=(0,15…0,5)×Idss.

Полевой транзистор с барьером Шотки может быть выполнен, по меньшей мере, с двумя электродами истока, при этом последние электрически соединены между собой.

Резистивный элемент выполнен в составе упомянутой полупроводниковой структуры в виде того же легированного слоя, в котором выполнен и канал полевого транзистора с барьером Шотки, при этом с длиной, равной длине канала и шириной - 0,15-0,5 от его ширины.

Раскрытие сущности изобретения.

Заявленная гибридная интегральная схема СВЧ-диапазона, совокупность ее существенных признаков, а именно когда:

- транзистор выполнен в виде полевого транзистора с барьером Шотки с шириной вывода - затвора не более 500 мкм, с заданными величинами тока насыщения, не превышающего 150 мА, и напряжения отсечки;

- гибридная интегральная схема дополнительно содержит, по меньшей мере, один резистивный элемент с заданным электрическим сопротивлением, который выполнен в составе каждого единого кристалла монолитной интегральной схемы;

- один из концов резистивного элемента электрически соединен с верхней обкладкой одного из конденсаторов, а другой - с нижней обкладкой этого конденсатора,

- электрическое соединение одного из концов резистивного элемента с верхней обкладкой конденсатора выполнено в упомянутом одном слое металлизационного покрытия единого кристалла,

- электрическое соединение другого конца резистивного элемента и нижние обкладки конденсаторов - в другом слое этого металлизационного покрытия.

Это обеспечивает включение полевого транзистора с барьером Шотки в гибридной интегральной схеме по схеме с однополярным питанием (такая схема питания транзистора называется схемой с автосмещением - режим автосмещения), и тем самым обеспечивается:

- возможность установления рабочего режима работы полевого транзистора с барьером Шотки по постоянному току,

- и более того - в автоматическом режиме.

И как следствие -

во-первых, благодаря возможности использования небольших рабочих токов и тем самым обеспечения низкой рабочей температуры полевого транзистора с барьером Шотки и, соответственно, единого кристалла монолитной интегральной схемы - улучшение электрических характеристик и, прежде всего, стабильности коэффициента усиления,

во-вторых, благодаря сокращению в гибридной интегральной схеме количества сварных соединений, а именно исключению:

а) разварки электрических проволочных соединений между верхними обкладками конденсаторов и электродом истока полевого транзистора с барьером Шотки,

б) разварки электрических проволочных соединений между верхними обкладками конденсаторов и резистивным элементом.

И, как следствие этого (а и б), повышение технологичности и надежности.

Кроме того, исключается необходимость использования для гибридной интегральной схемы второго внешнего источника питания - источника питания отрицательной полярности.

Выполнение транзистора в виде полевого транзистора с барьером Шотки с шириной вывода - электрода затвора не более 500 мкм, с заданными величинами тока насыщения, не превышающего 150 мА, и напряжения отсечки в совокупности с указанным расположением резистивного элемента, а именно вне области канала полевого транзистора с барьером Шотки на расстоянии, равном не менее 20 мкм от электрода истока, обеспечивает значительное снижение, вплоть до полного исключения, нагрева единого кристалла монолитной интегральной схемы вследствие рассеивания значительной тепловой мощности на резистивном элементе и, как указано выше, тем самым обеспечение низкой рабочей температуры полевого транзистора с барьером Шотки и соответственно единого кристалла монолитной интегральной схемы и, как следствие - улучшение электрических характеристик.

Экспериментально установлено, что при рабочих токах больше 75 мА (что соответствует току насыщения, примерно 150 мА) на резистивном элементе рассеиваться значительная мощность, что отрицательно сказывается на тепловом режиме работы полевого транзистора с барьером Шотки и соответственно единого кристалла монолитной интегральной схемы.

Так, для полевого транзистора с барьером Шотки 3П612 с током насыщения 240 мА и напряжением отсечки минус 4 В, рабочий ток должен быть 15-50 процентов от тока насыщения, то есть порядка 36-120 мА.

Таким образом, напряжение на электроде истока полевого транзистора с барьером Шотки должно быть 2-3,5 В и, соответственно, рассеиваемая мощность резистивного элемента равна

Ррас.=I×U=(2-3,5 В)×(120-36 мА)=126-240 мВт.

Эта дополнительная мощность приведет к повышению температуры полевого транзистора с барьером Шотки и соответственно единого кристалла монолитной интегральной схемы и тем самым - к ухудшению электрических характеристик гибридной интегральной схемы и, прежде всего коэффициента шума и коэффициента усиления.

Выполнение сквозных металлизированных отверстий в едином кристалле монолитной интегральной схемы для электрического соединения нижних обкладок конденсаторов с металлизированной посадочной площадкой вне площади расположения этих конденсаторов обеспечивает исключение возможных нарушений целостности всех слоев пленочных конденсаторов (нижних и верхних обкладок и слоя диэлектрика) в отличие от случая их выполнения над сквозными металлизированными отверстиями и, как следствие - повышение надежности гибридной интегральной схемы СВЧ.

Частные случаи выполнения резистивного элемента, а именно пленочным на лицевой поверхности кристалла монолитной интегральной схемы, равно как и в виде легированного слоя в составе полуизолирующей полупроводниковой структуры с заданными легированными слоями обеспечивают исключение внутрисхемных достаточно длинных соединительных проводников, имеющих значительные паразитные индуктивности и емкости.

И как следствие этого -

- улучшение электрических и массогабаритных характеристик,

- повышение технологичности и надежности гибридной интегральной схемы СВЧ-диапазона.

Кроме того, технологические процессы, посредством которых выполняют резистивный элемент, являются на сегодня наиболее технологичными и оптимизированными и тем самым дополнительно обеспечивают улучшение электрических и массогабаритных характеристик и повышение их воспроизводимости.

Указанные математические соотношения в совокупности с другими признаками обеспечивают оптимизацию работы гибридной интегральной схемы с точки зрения улучшения электрических характеристик и повышения их воспроизводимости.

Итак, совокупность существенных признаков заявленной гибридной интегральной схемы СВЧ-диапазона позволит в полной мере реализовать технический результат, а именно - улучшение электрических и массогабаритных характеристик и повышение их воспроизводимости, повышение технологичности и надежности.

Изобретение поясняется чертежами.

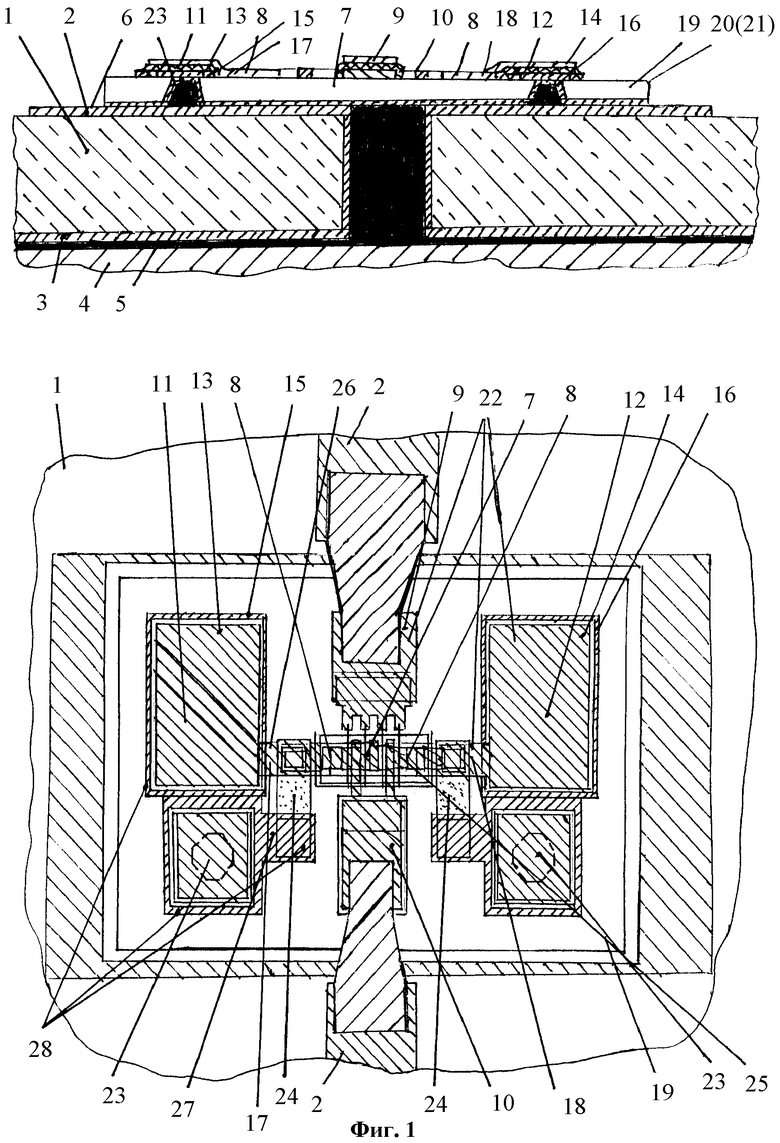

На Фиг.1 (а и б) представлен фрагмент заявленной гибридной интегральной схемы СВЧ-диапазона, частный случай ее выполнения, в котором резистивный элемент выполнен пленочным на лицевой поверхности единого кристалла монолитной интегральной схемы, где:

- диэлектрическая подложка - 1,

- топологический рисунок металлизационного покрытия - 2,

- экранное заземляющее металлизационное покрытие - 3,

- металлическое теплоотводящее основание - 4,

- электро- и теплопроводящее вещество - 5,

- металлизированная посадочная площадка - 6,

- транзистор - 7 в виде полевого транзистора с барьером Шотки,

- выводы - электроды транзистора (исток-затвор-сток) - 8, 9, 10 соответственно,

- два конденсатора - 11, 12 соответственно,

- верхние обкладки - 13, 14 и нижние обкладки - 15, 16 конденсаторов соответственно,

- электрические соединения - 17, 18 одного из выводов транзистора (электрода истока) с верхними обкладками 13, 14 конденсаторов,

- единый кристалл монолитной интегральной схемы - 19,

- полуизолирующая полупроводниковая структура 20 с заданными активными - легированными слоями - 21,

- один слой металлизационного покрытия - 22 единого кристалла монолитной интегральной схемы,

- сквозные металлизированные отверстия - 23 в едином кристалле монолитной интегральной схемы,

- резистивный элемент - 24,

- канал полевого транзистора с барьером Шотки - 25,

- электрическое соединение одного из концов резистивного элемента с верхней обкладкой одного из конденсаторов - 26,

- электрическое соединение другого конца резистивного элемента с нижней обкладкой этого конденсатора - 27,

- другой слой металлизационного покрытия - 28 единого кристалла монолитной интегральной схемы.

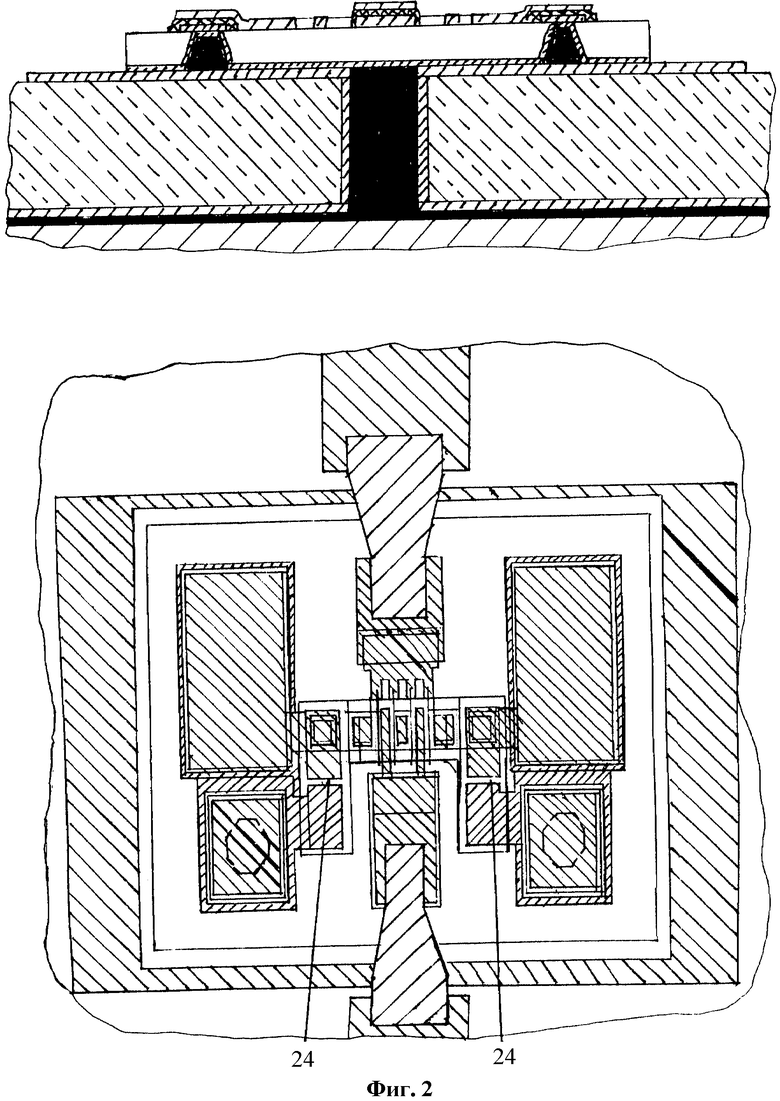

На Фиг.2 (а и б) представлен фрагмент заявленной гибридной интегральной схемы СВЧ-диапазона, частный случай ее выполнения, в котором резистивный элемент 24 выполнен в виде легированного слоя в составе полупроводниковой эпитаксиальной структуры 20 с заданными легированными слоями 21, при этом того же, в котором выполнен канал 25 полевого транзистора с барьером Шотки.

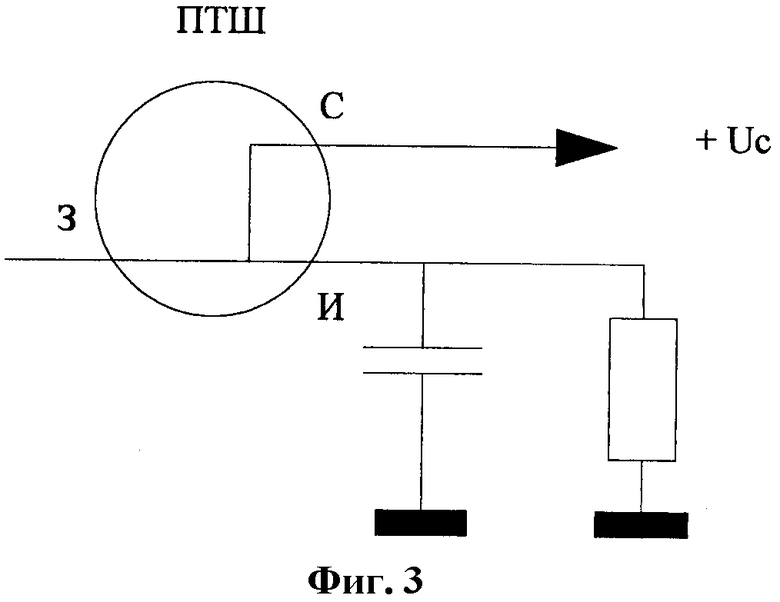

На фиг.3 представлена электрическая схема заявленной гибридной интегральной схемы СВЧ-диапазона.

Примеры конкретного выполнения заявленной гибридной интегральной схемы СВЧ-диапазона.

Пример 1

Рассмотрен частный случай ее выполнения, в котором резистивный элемент 24 выполнен пленочным на лицевой поверхности единого кристалла монолитной интегральной схемы 19.

Прежде осуществляют выполнение единого кристалла монолитной интегральной схемы 19 в едином технологическом цикле посредством классической тонкопленочной технологии (размер кристалла 0,5×0,4×0,1 мм) на полуизолирующей полупроводниковой структуре 20, например на полуизолирующей подложке из арсенида галлия с заданными легированными слоями 21, например, n-типа проводимости толщиной 0,15 мкм и концентрацией 5×1017-5×1018 см-3, содержащий:

- полевой транзистор с барьером Шотки 7, с выводами - электродами (далее электродами) 8, 9, 10 соответственно исток - затвор - сток со структурой металлизационного покрытия: титан - золото толщиной, равной 0,0001 и 0,0007 мм соответственно посредством напыления в вакууме, с последующем гальваническим осаждением золота толщиной, равной 3 мкм. Полевой транзистор с барьером Шотки выполнен с заданными величинами тока насыщения и напряжения отсечки, например 50 мА и 1,25 В соответственно;

- два конденсатора 11, 12, например, одинаковой емкостью 5 пФ, расположены, например, с противоположных сторон полевого транзистора с барьером Шотки 7, при этом оба конденсатора 11, 12 выполнены пленочными, верхние 13, 14 и нижние 15, 16 обкладки конденсаторов выполнены со структурой металлизационного покрытия титан - золото толщиной, равной 0,0001 и 0,0007 мм соответственно посредством напыления в вакууме, с последующим гальваническим осаждением золота толщиной, равной 3 мкм, слой диэлектрика конденсаторов - из двуокиси кремния толщиной, равной 0,0005 мм;

- электрические соединения 17 электрода истока 8 полевого транзистора с барьером Шотки 7 с верхними обкладками 13 одного из конденсаторов, например 11, выполнены из металлизационного покрытия титан - золото толщиной, равной 0,0001 и 0,0007 мм соответственно посредством напыления в вакууме, с последующим гальваническим осаждением золота толщиной, равной 3 мкм;

- резистивный элемент 24 выполнен на лицевой поверхности единого кристалла монолитной интегральной схемы 19 пленочным посредством напыления тантала с толщиной слоя, равной 0,05 мкм (что соответствует электрическому сопротивлению примерно 40 Ом/мм2) с последующей фотолитографией,

при этом

- электрическое соединение 26 одного из концов резистивного элемента 24 с верхней обкладкой 13 одного из конденсаторов, например 11, выполнены в одном слое металлизационного покрытия 22 единого кристалла 19, также с верхними обкладками 13, 14 конденсаторов 11 и 12, электродами полевого транзистора с барьером Шотки 7 (исток-затвор-сток) 8, 9, 10 соответственно и электрическими соединениями - 17, 18 одного из электродов (истока) полевого транзистора с барьером Шотки с верхними обкладками 13, 14 конденсаторов 11, 12, а электрическое соединение 27 другого конца резистивного элемента 24 и нижние обкладки 15, 16 конденсаторов 11, 12 выполнены в другом слое 28 этого металлизационного покрытия единого кристалла;

- в едином кристалле монолитной интегральной схемы 19 выполнены вне площади конденсаторов 11, 12 соответственно два сквозных металлизированных отверстия 23 для электрического соединения нижних обкладок 15, 16 конденсаторов 11, 12 с металлизированной посадочной площадкой 6.

Далее на диэлектрической подложке 1, например, поликоровой (керамика ВК-100), посредством классической тонкопленочной технологии выполнены:

- на лицевой ее стороне - топологический рисунок металлизационного покрытия 2,

- на обратной стороне - экранное заземляющее металлизационное покрытие 3.

При этом с одинаковой структурой металлизационного покрытия хром - медь - никель - золото (Сr 100 Ом/мм2, Сu 1 мкм, напыленные в вакууме, Сu 3 мкм, Ni 0,6 мкм и Аu 3 мкм, осажденные гальванически;

- металлизированная посадочная площадка 6.

Диэлектрическая подложка 1 расположена обратной стороной на металлическом теплоотводящем основании 4 и соединена с ним электро- и теплопроводящим веществом 5, например припоем золото-кремний эвтектического состава.

При этом металлизированная посадочная площадка 6 электрически соединена через сквозные металлизированные отверстия 23, заполненные припоем золото-кремний эвтектического состава с экранным заземляющим металлизационным покрытием 3.

Пример 2

Частный случай выполнения, в котором резистивный элемент 24 выполнен в виде легированного слоя в составе полупроводниковой эпитаксиальной структуры 20 в одном из заданных легированных слоев 21, при этом том же, в котором выполнен канал 25 полевого транзистора с барьером Шотки.

Работа заявленной гибридной интегральной схемы СВЧ-диапазона.

Как видно из фиг.3, положительный полюс внешнего источника питания через фильтр питания присоединен к электроду стока ПТШ гибридной интегральной схемы. Электрод затвора ПТШ через фильтр питания присоединен к отрицательнму полюсу этого источника питания. Электрод истока ПТШ соединен через резистивный элемент с отрицательным полюсом этого источника питания.

При подаче на электрод стока ПТШ положительного напряжения от внешнего источника питания по цепи - внешний источник питания - сток ПТШ - исток ПТШ - резистивный элемент - потечет ток.

Этот ток, проходя через резистивный элемент, создает напряжение смещения между электродами затвора и истока ПТШ. Последнее автоматически обеспечивает выбранную согласно указанному в формуле изобретения соотношению величину рабочего тока.

СВЧ сигнал поступает на электрод затвора ПТШ и усиленный, снимается с электрода стока ПТШ гибридной интегральной схемы СВЧ-диапазона.

На экспериментальных образцах гибридной интегральной схемы СВЧ-диапазона (примеры 1, 2) были измерены:

- коэффициент усиления (дБ),

- коэффициент шума (дБ),

- верхняя предельная рабочая частота (ГГц).

Как показали измерения:

- коэффициент усиления составляет 10 дБ на образцах как примера 1, так и примера 2;

- коэффициент шума составляет 2 дБ на образцах как примера 1, так и примера 2;

- верхняя предельная рабочая частота составляет 19,4 ГГц.

Прототип имеет соответственно:

- коэффициент усиления 8,5 дБ,

- коэффициент шума 2 дБ,

- верхняя предельная рабочая частота 18 ГГц.

Как видно, по сравнению с прототипом:

- коэффициент усиления увеличен на 1,5 дБ,

- при сохранении величины коэффициент шума 2 дБ,

- верхняя предельная рабочая частота увеличена на 1,4 ГГц.

Следует отметить, что для класса малошумящих балансных усилителей, в которых применяется режим автосмещения, это достаточно высокие характеристики.

Таким образом, заявленная гибридная интегральная схема СВЧ-диапазона по сравнению с прототипом обеспечит:

во-первых, улучшение электрических и массогабаритных характеристик и повышение их воспроизводимости;

во-вторых, повышение технологичности и надежности.

Данная гибридная интегральная схема может найти широкое применение в электронных модулях СВЧ различного назначения и, прежде всего, в балансных малошумящих усилителях СВЧ, где требуется высокий коэффициент усиления и низкий коэффициент шума.

Источники информации

1. Патент РФ №2227345, МПК H01L 27/13, Н05 1/16, приоритет 26.02.2002, опубл. 20.04.04, бюл. №11.

2. Патент РФ №2390877, МПК H01L 25/16, Н05К 1/02, приоритет изобретения 08.04.2009, опубл. 27.05.10 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2009 |

|

RU2390877C1 |

| СПОСОБ МЕТАЛЛИЗАЦИИ ЭЛЕМЕНТОВ ИЗДЕЛИЙ ЭЛЕКТРОННОЙ ТЕХНИКИ | 2010 |

|

RU2436183C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СВЧ | 2013 |

|

RU2556271C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СВЧ | 2011 |

|

RU2474921C1 |

| Интегральная схема СВЧ | 2017 |

|

RU2654970C1 |

| ЭЛЕКТРОННЫЙ ПРИБОР СВЧ | 2010 |

|

RU2442241C1 |

| ГЕНЕРАТОР СВЧ НА ТРАНЗИСТОРЕ | 2007 |

|

RU2353048C1 |

| Интегральная схема СВЧ | 2021 |

|

RU2782184C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ ПОЛЕВОГО ТРАНЗИСТОРА С БАРЬЕРОМ ШОТКИ | 2011 |

|

RU2465682C1 |

| СМЕСИТЕЛЬ СВЧ | 2011 |

|

RU2473166C1 |

Изобретение относится к электронной технике. Сущность изобретения: гибридная интегральная схема СВЧ-диапазона содержит диэлектрическую подложку, на лицевой стороне которой расположен топологический рисунок металлизационного покрытия, а на обратной стороне - экранное заземляющее металлизационное покрытие, при этом диэлектрическая подложка расположена обратной стороной на металлическом теплоотводящем основании и соединена с ним электро- и теплопроводящим веществом, по меньшей мере, одну металлизированную посадочную площадку, электрически соединенную с экранным заземляющим металлизационным покрытием, по меньшей мере, один транзистор с выводами, по меньшей мере, два конденсатора, расположенные с разных сторон транзистора, при этом один из выводов транзистора электрически соединен с верхними обкладками конденсаторов, два другие его вывода - с топологическим рисунком металлизационного покрытия, нижние обкладки конденсаторов - с металлизированной посадочной площадкой и через нее с экранным заземляющим металлизационным покрытием, при этом каждые - транзистор с выводами, два конденсатора и упомянутые электрические соединения одного из выводов транзистора - выполнены в виде, по меньшей мере, одного единого кристалла монолитной интегральной схемы на полуизолирующей полупроводниковой структуре с заданными легированными слоями, упомянутый единый кристалл расположен на металлизированной посадочной площадке, оба конденсатора выполнены пленочными, верхние обкладки конденсаторов, выводы транзистора и упомянутые электрические соединения одного из выводов транзистора выполнены в одном слое металлизационного покрытия упомянутого единого кристалла, в последнем выполнены сквозные металлизированные отверстия для электрического соединения нижних обкладок конденсаторов с металлизированной посадочной площадкой. Транзистор выполнен в виде полевого транзистора с барьером Шотки с шириной вывода - электрода затвора не более 500 мкм, с заданными величинами тока насыщения, не превышающего 150 мА, и напряжения отсечки, каждый единый кристалл монолитной интегральной схемы дополнительно содержит резистивный элемент с заданным электрическим сопротивлением, резистивный элемент выполнен пленочным на лицевой поверхности упомянутого единого кристалла или в виде легированного слоя в составе упомянутой полупроводниковой структуры, резистивный элемент расположен вне области канала полевого транзистора с барьером Шотки на расстоянии не менее 20 мкм от вывода - электрода истока, при этом один из концов резистивного элемента электрически соединен с верхней обкладкой одного из конденсаторов, а другой - с нижней обкладкой этого конденсатора, электрическое соединение одного из концов резистивного элемента с верхней обкладкой конденсатора выполнено в упомянутом одном слое металлизационного покрытия единого кристалла, а электрическое соединение другого конца резистивного элемента и нижние обкладки конденсаторов - в другом слое этого металлизационного покрытия, а сквозные металлизированные отверстия в упомянутом едином кристалле выполнены вне площади расположения конденсаторов. Техническим результатом изобретения является улучшение электрических и массогабаритных характеристик и их воспроизводимости, за счет расширения функциональных возможностей гибридной интегральной схемы СВЧ-диапазона, повышение технологичности и надежности. 2 з.п. ф-лы, 3 ил.

1. Гибридная интегральная схема СВЧ-диапазона, содержащая диэлектрическую подложку, на лицевой стороне которой расположен топологический рисунок металлизационного покрытия, а на обратной стороне - экранное заземляющее металлизационное покрытие, при этом диэлектрическая подложка расположена обратной стороной на металлическом теплоотводящем основании и соединена с ним электро- и теплопроводящим веществом, по меньшей мере, одну металлизированную посадочную площадку, электрически соединенную с экранным заземляющим металлизационным покрытием, по меньшей мере, один транзистор с выводами, по меньшей мере, два конденсатора, расположенные с разных сторон транзистора, при этом один из выводов транзистора электрически соединен с верхними обкладками конденсаторов, два другие его вывода - с топологическим рисунком металлизационного покрытия, нижние обкладки конденсаторов - с металлизированной посадочной площадкой и через нее - с экранным заземляющим металлизационным покрытием, при этом каждые - транзистор с выводами, два конденсатора и упомянутые электрические соединения одного из выводов транзистора выполнены в виде, по меньшей мере, одного единого кристалла монолитной интегральной схемы на полуизолирующей полупроводниковой структуре с заданными легированными слоями, упомянутый единый кристалл расположен на металлизированной посадочной площадке, оба конденсатора выполнены пленочными, верхние обкладки конденсаторов, выводы транзистора и упомянутые электрические соединения одного из выводов транзистора выполнены в одном слое металлизационного покрытия упомянутого единого кристалла, в последнем выполнены сквозные металлизированные отверстия для электрического соединения нижних обкладок конденсаторов с металлизированной посадочной площадкой, отличающаяся тем, что транзистор выполнен в виде полевого транзистора с барьером Шотки с шириной вывода - электрода затвора не более 500 мкм, с заданными величинами тока насыщения, не превышающего 150 мА, и напряжения отсечки, каждый единый кристалл монолитной интегральной схемы дополнительно содержит, по меньшей мере, один резистивный элемент с заданным электрическим сопротивлением, резистивный элемент выполнен пленочным на лицевой поверхности упомянутого единого кристалла или в виде легированного слоя в составе упомянутой полупроводниковой структуры, резистивный элемент расположен вне области канала полевого транзистора с барьером Шотки на расстоянии не менее 20 мкм от вывода - электрода истока, при этом один из концов резистивного элемента электрически соединен с верхней обкладкой одного из конденсаторов, а другой - с нижней обкладкой этого конденсатора, электрическое соединение одного из концов резистивного элемента с верхней обкладкой конденсатора выполнено в упомянутом одном слое металлизационного покрытия единого кристалла, а электрическое соединение другого конца резистивного элемента и нижние обкладки конденсаторов - в другом слое этого металлизационного покрытия, а сквозные металлизированные отверстия в упомянутом едином кристалле выполнены вне площади расположения конденсаторов, при этом электрическое сопротивление резистивного элемента задано, исходя из соотношения:

где Up - заданное напряжение отсечки полевого транзистора с барьером Шотки;

Id - рабочий ток полевого транзистора с барьером Шотки;

Idss - заданный максимальный ток насыщения при нулевом напряжении на затворе полевого транзистора с барьером Шотки, а рабочий ток выбран из соотношения:

Id=(0,15…0,5)·Idss.

2. Гибридная интегральная схема СВЧ-диапазона по п.1, отличающаяся тем, что полевой транзистор с барьером Шотки может быть выполнен, по меньшей мере, с двумя электродами истока, при этом последние электрически соединены между собой.

3. Гибридная интегральная схема СВЧ-диапазона по п.1, отличающаяся тем, что резистивный элемент выполнен в составе упомянутой полупроводниковой структуры в виде того же легированного слоя, что и канал полевого транзистора с барьером Шотки, с длиной, равной длине канала и шириной - 0,15-0,5 от его ширины.

| ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2009 |

|

RU2390877C1 |

| МОЩНАЯ ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2009 |

|

RU2390071C1 |

| МОЩНАЯ ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2005 |

|

RU2298255C1 |

| ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2002 |

|

RU2227345C2 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Полупроводниковый регулятор напряжения для электрического генератора постоянного тока | 1975 |

|

SU592002A1 |

Авторы

Даты

2012-04-27—Публикация

2010-12-29—Подача