Предлагаемое изобретение относится к области увеличения частоты и числа строк телевизионных изображений и, в том числе, преобразования чересстрочной структуры последовательных во времени сигналов телевизионных кадров в прогрессивную (построчную) структуру и может быть использовано при сжатии спектра сигналов телевизионных изображений, при преобразованиях телевизионного сигнала вещательного телевидения в сигнал телевидения высокой четкости и при воспроизведении телевизионных изображений.

Недостатком используемого в настоящее время в системах телевидения чересстрочного растра являются специфические искажения, которые в технической литературе обычно определяют как эффекты «гребенчатости», «жалюзи» и различные, по отношению к указанным, промежуточные варианты пространственно-временных искажений, характерные для телевизионных изображений объектов, перемещающихся с относительно большой скоростью по различным направлениям в пределах контролируемого пространства. Возникновение искажений связано в таком случае с пространственно-временными изменениями сигналов изображений движущегося объекта в структуре строк смежных полукадров текущего телевизионного сигнала и с последовательным их отображением изображениями четных и нечетных полукадров с уменьшенным вдвое числом строк в пространстве чересстрочного растра. При этом рассмотренные искажения в максимальной степени проявляются на изображениях границ подвижных объектов, ортогональных направлению движения, и отражаются уменьшениями степени сжатия спектра сигналов изображений, качества и четкости воспроизведения изображений указанных границ.

Известен способ преобразования чересстрочной развертки в построчную, заключающийся в запоминании, на время одного телевизионного кадра, сигналов изображений двух смежных во времени (нечетного и четного) сигналов полей и поочередном воспроизведении сигналов их строк [Смирнов А.В., Пескин А.Е. Цифровое телевидение: от теории к практике. М.: Горячая линия - Телеком, 2005. - 348 с., стр.275-279]. При этом воспроизведение осуществляют в порядке расположения в пространстве телевизионного растра всей совокупности четных и нечетных строк: 1с, 2с, 3с…. Однако полной совокупностью этих строк в кадре представлены два отличающихся на время поля (TП=0,02 сек) положения изображений одного и того же движущегося объекта. Такое зависящее от скорости движения объекта относительное перемещение в пространстве изображений объекта, представленных четными и нечетными строками, приводит, как указывалось ранее, к заметным искажениям изображения (расслоениям структуры смежных в пространстве строк типа «расческа» и «жалюзи») на границах движущихся объектов, ортогональных направлению движения.

Более эффективным, в смысле устранения рассмотренных пространственно-временных искажений, является способ [Пат. 2287909 Российская федерация, МПК7 H04N 7/48. Способ преобразования цифрового сигнала изображения и устройство для его реализации / Безруков В.Н., Рабинович А.В., Комаров П.Ю.; заявитель и патентообладатель Московский технический университет связи и информатики. - №2004136445/09; заявлено 15.12.2004; опубл. 20.11.2006, Бюл. №32. - 34 с.; ил.], основанный на том, что перед сжимающим спектр цифрового сигнала изображения блочного формата кодированием из цифрового сигнала блочного формата полукадров яркостной составляющей телевизионного сигнала изображения выделяют интервалы сигналов строк, в пределах которых значение сигналов межстрочной разности превышает заранее заданное пороговое значение, формируют соответствующие этим интервалам сигналы управления фиксированного уровня, совмещают во времени и вычитают сигналы смежных полей кадров изображения, полученные сигналы межполевой разности приводят к нулевому уровню в интервалах, совпадающих с наличием сформированных сигналов управления, а полученные в результате этого преобразованные сигналы межполевой разности совмещают во времени и суммируют с сигналами смежных полей изображения.

Основой данного способа, следовательно, является разделение сигнала разности смежных полей на пространственную и временную составляющие. С этой целью сигнал текущего поля дифференцируют в межстрочном направлении, что обеспечивает возможность выделения (по превышениям заданного порогового значения уровнем сигнала, отражающего результат дифференцирования) интервалов в сигнале изображения, в пределах которых возникают изменения его уровня в сигналах смежных строк. Последнее осуществляется детектированием, интегрированием и ограничением по уровню сигнала составляющей, отражающей результат дифференцирования сигнала текущего поля в межстрочном направлении.

Недостатком данного способа является снижение эффективности действия реализуемой коррекции при наличии в исходной структуре сигналов изображений составляющих относительно низкого уровня, отражающих, в том числе, во внутрикадровом пространстве и горизонтально ориентированные границы. По существу в таком случае следует существенно снижать задаваемое пороговое значение при формировании сигнала управления, а этому в реальных случаях препятствует нежелательное проникновение в структуру последнего уже и шумовых составляющих, присутствующих в исходном сигнале изображений.

Устройство преобразования цифрового сигнала изображения [Пат. 2287909 Российская федерация, МПК7 H04N 7/48. Способ преобразования цифрового сигнала изображения и устройство для его реализации / Безруков В.Н., Рабинович А.В., Комаров П.Ю.; заявитель и патентообладатель Московский технический университет связи и информатики. - №2004136445/09; заявлено 15.12.2004; опубл. 20.11.2006, Бюл. №32. - 34 с.; ил.], реализующее указанный выше способ с преобразованием сигнала межполевой разности, содержит матрицу преобразования, первый выход которой через первый фильтр нижних частот подключен к сигнальном входу первого аналогово-цифрового преобразователя, второй выход через второй фильтр нижних частот - к сигнальному входу второго аналогово-цифрового преобразователя, а третий выход через третий фильтр нижних частот - к сигнальному входу третьего аналогово-цифрового преобразователя, а каждый из трех входов матрицы преобразования подключен соответственно к одному из сигналов трех основных цветов; блок коррекции, первую и вторую линии задержки, генератор тактовых импульсов, причем выход первого аналогово-цифрового преобразователя через блок коррекции соединен с первым входом сжимающего кодера, выход второго аналогово-цифрового преобразователя через первую линию задержки соединен со вторым входом сжимающего кодера, выход третьего аналогово-цифрового преобразователя через вторую линию задержки соединен с третьим входом сжимающего кодера, а первый выход генератора тактовых импульсов подключен ко входу синхронизации первого аналогово-цифрового преобразователя, второй выход генератора тактовых импульсов подключен ко входам синхронизации второго и третьего аналогово-цифровых преобразователей, третий выход генератора тактовых импульсов подключен ко входу синхронизации блока коррекции и к первому входу синхронизации сжимающего кодера, второй вход синхронизации которого подключен к четвертому выходу генератора тактовых импульсов.

В матрице преобразования данного устройства из сигналов трех основных цветов R, G, В с применением весового суммирования и вычитания формируются яркостной EY и два цветоразностных сигналов EB-Y и ER-Y. Цветоразностные сигналы поступают здесь также на входы первого и второго умножителей, где умножаются на коэффициент 0,493 и 0,877 соответственно (Телевидение. под ред. В.Е.Джаконии, М. 2002, стр.248). Умножители чаще всего выполняются на основе аналоговых перемножителей [Цифровые и аналоговые интегральные микросхемы: Справочник. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.373], имеющих фиксированный коэффициент умножения и поэтому один сигнальный вход. На выходе блоков умножения формируются сигналы U и V соответственно.

Сигналы EY, U и V через соответствующие фильтры нижних частот (ФНЧ) поступают на входы первого, второго и третьего аналогово-цифровых преобразователей. Далее сигнал EY в цифровой форме поступает в блок коррекции, а сигналы U и V в цифровой форме через первую и вторую линии задержки, соответственно, выравнивающие задержку сигнала, вносимую блоком коррекции, поступают на второй и третий входы сжимающего кодера соответственно.

Блок коррекции, который предназначен для устранения специфических искажений границ движущихся объектов, вызванных, как указывалось выше, различным положением движущихся объектов в двух полях одного кадра изображения, включает в себя две линии задержки на длительность строки, три вычитателя, два детектора, два фильтра нижних частот, два амплитудных ограничителя (по максимуму и минимуму), логический элемент "ИЛИ", формирующий сигнал управления, линию задержки на длительность поля, линию задержки на длительность половины строки, блок выделения сигналов временной разности, ключ и сумматор. При этом с помощью указанных двух линий задержки на длительность строки в блоке коррекции телевизионный сигнал текущего поля задерживают на время одной и двух строк. Из входного телевизионного сигнала вычитают задержанный на время одной строки сигнал (опорный телевизионный сигнал), а из последнего вычитают сигнал, задержанный на время двух строк. Полученные разностные сигналы определяют наличие изменений (линий или границ) в структуре (в каждом сигнале поля) соответствующего телевизионного изображения по межстрочному, т.е. по вертикальному во внутрикадровом пространстве направлению. Эти оба сигнала разности раздельно детектируют, подвергают цифровой низкочастотной фильтрации и ограничивают по максимуму и по минимуму. Сформированные таким образом сигналы поступают в блоке коррекции на элемент "ИЛИ", в котором формируют сигнал управления, определяющий местоположение во внутрикадровом пространстве границ (линий) в структуре изображений неподвижных объектов, направление которых (границ, линий) в пределах указанного пространства отличается от вертикального. Сформированный в элементе "ИЛИ" сигнал управления поступает на вход управления блоком выделения сигналов временной разности.

Формирование сигнала межполевой пространственно-временной разности реализуют в блоке коррекции за счет параллельной задержки опорного телевизионного сигнала на время длительности поля и на время длительности половины строки. При этом обеспечивается совмещение во времени сигналов смежных (текущего и предшествующего) полей опорного телевизионного сигнала. Совмещенные с применением указанных задержек сигналы смежных полей (полей четных и нечетных строк) раздельно подают на входы третьего вычитателя. На его выходе получают сигнал пространственно-временной разности, который поступает на второй (сигнальный) вход блока выделения сигналов временной разности.

В блоке выделения сигналов временной разности реализуется, в моментах поступления сформированного сигнала управления, приведение в структуре сигнала межполевой разности составляющих пространственной разности к уровню, равному нулю. Этим, собственно, и обеспечивается результат выделения сигнала, соответствующего только составляющим временной разности. Полученный сигнал временной разности поступает в блоке коррекции на сигнальный вход ключа. На управляющий вход этого ключа поступает сигнал синхронизации с частотой 25 Гц с выхода генератора тактовых импульсов. В соответствии с сигналом управления к выходу ключа подключаются (с частотой Гц) лишь четные (нечетные) сигналы полей временной разности. Преобразованный таким образом сигнал временной разности, имеющий заданную полярность, суммируют с опорным телевизионным сигналом. При этом обеспечивается устранение сигнала временной разности в полях заданной четности (четных или нечетных) в каждом из кадров подвергаемых последующему сжатию, например, по стандарту MPEG-2 (MPEG-4). Соответственно имеет место подавление специфических искажений (типа «гребенчатости», «жалюзи») в пределах границ телевизионных изображений движущихся объектов, ортогональных направлению движения. Преобразованные кадры телевизионного сигнала с выхода блока коррекции поступают на вход сжимающего кодера, в котором спектр соответствующих телевизионных изображений подвергается сжатию и кодированию.

Недостатком данного устройства является то, что подавление искажений в данном случае имеет место только для фиксированного порядка формирования кадров из смежных (четных и нечетных) сигналов полей телевизионного сигнала. К тому же во внутрикадровом пространстве могут сохраняться остаточные искажения в пределах границ в телевизионных изображениях движущихся объектов, обусловленные, неточностями формирования в блоке коррекции управляющего сигнала, что определяет сопутствующее снижение эффективности выделения в структуре сигнала межполевой разности временной составляющей.

Наиболее близким по технической сущности к предлагаемому изобретению является схема преобразования [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.], предназначенная для обеспечения вывода видеосигнала, строка развертки которого является удвоенной, путем интерполяции видеосигнала интерполируемой (отсутствующей) строки развертки по входным сигналам соседних, внутри поля, с интерполируемым сигналам строк развертки, расположенных сверху и снизу, и содержащая блок обнаружения направления во внутрикадровом пространстве для осуществления интерполяции пикселов (отсчетов, элементов) видеосигнала в межстрочном интервале сигнала поля как направления, имеющего наибольшую корреляцию, из (2n+1) направлений (n является целым числом, которое равно или больше 1), центрированных вокруг точки реализации интерполяции каждого пиксела упомянутой интерполируемой строки, включая вертикальное направление, направление, имеющее наклон влево, и направление, имеющее наклон вправо, на основе использования множества точек выборки входных видеосигналов на упомянутой строке развертки, расположенной сверху, и упомянутой строке развертки, расположенной снизу, и блок вычисления среднего значения для вычисления среднего значения видеосигналов двух точек выборки, соответствующих направлению, обнаруженному упомянутым блоком обнаружения направления, из множества точек выборки на упомянутой строке развертки, расположенной сверху, и упомянутой строке развертки, расположенной снизу, для получения, таким образом, видеосигнала интерполируемой строки развертки.

Согласно разработанной авторами схеме преобразования, в тех случаях, когда за счет применения блока обнаружения направления выявляется то, что в изображении движущегося объекта в межстрочном пространстве наибольшая корреляция соответствует значениям видеосигнала по направлению, имеющему наклон, то в блоке вычисления среднего значения определяют из множества пикселов выборки на строке развертки, расположенной по отношению к положению интерполируемого пикселя сверху, и на строке развертки, расположенной по отношению к положению интерполируемого пикселя снизу, среднее значение видеосигналов для двух точек выборки пикселей видеосигнала, соответствующих (во внутрикадровом пространстве) направлению, имеющему наклон, которое и используют в качестве составляющей видеосигнала интерполируемой строки развертки.

Когда же выявляется то, что наибольшую корреляцию имеет вертикальное направление, тогда из множества точек выборки пикселей в телевизионном сигнале строки развертки, расположенной (в пределах внутрикадрового пространства) по отношению к положению интерполируемого пикселя сверху, и строки развертки, расположенной по отношению к положению интерполируемого пикселя снизу, вычисляется среднее значение пикселей двух точек выборки, соответствующих вертикальному направлению, которое и используется в качестве пикселя в составе видеосигнала интерполируемой строки развертки.

В тех же случаях, когда с применением блока обнаружения направления не выявлено во множестве точек выборки на строке развертки, расположенной сверху, и строке развертки, расположенной снизу, направления, имеющего наибольшую корреляцию, вычисляется и используется в качестве пикселя видеосигнала интерполируемой строки развертки среднее значение пикселей видеосигналов двух точек выборки, соответствующих вертикальному направлению.

Разработанная схема преобразования развертки [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.] обеспечивает обнаружение движения в сигнале изображения с использованием входного видеосигнала для чересстрочной развертки. В участках с наличием движений пиксели видеосигнала в точках интерполяции получают комбинированием пикселей видеосигнала, соответствующих предшествующему полям, с пикселями видеосигнала, соответствующими интерполяционной обработке внутри поля, чтобы получить пиксели видеосигнала точек интерполяции, а вывод видеосигнала для последовательной строчной развертки осуществляют посредством двухскоростного преобразования пикселей видеосигнала в точках интерполяции и пикселей входного видеосигнала.

Соответственно изложенному выше в способе преобразования сигнала телевизионного изображения, соответствующем [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.], исходный видеосигнал, состоящий из последовательных во времени сигналов кадров, содержащих соответствующие сигналы полей четных и нечетных строк, преобразовывают в совокупность совмещенных во времени видеосигналов полей текущего и предшествующего кадров, которые одновременно и независимо отражают соответствующие данному сигналу поля группы по (2n+1) пикселя, одинаковых по порядку следования в сигналах смежных строк и симметрично распределенных вокруг n+1 пикселя каждой из групп, и отражают по порядку следования n+1 пиксель сигнала строки предшествующего поля, положение которого во внутрикадровом пространстве совпадает с центром межстрочного промежутка в указанных смежных строках данного поля, сравнением сигналов текущего и предшествующего кадров обнаруживают участки видеосигнала данного поля, отражающие отсутствие и наличие движений объектов, подвергнутых видеоконтролю, получают интерполяцией в пределах указанных групп (2n+1) пикселей в сигналах смежных строк пиксели дополнительных сигналов строк развертки, при этом предшествующие n+1 пикселю и n+1 пиксель из интерполируемых пикселей группы первой из смежных строк попарно распределяют и соответственно независимо сравнивают с последующими, по отношению к n+1 пикселю, и n+1 пикселем группы второй из смежных строк и предшествующие n+1 пикселю из интерполируемых пикселей группы второй из смежных строк попарно распределяют и соответственно сравнивают с последующими, по отношению к n+1 пикселю, пикселями первой из смежных строк, получают абсолютные значения сигналов сравнения уровней пикселей групп по (2n+1) пикселей в сигналах смежных строк, с использованием которых устанавливают в совокупности сравниваемых пикселей пару пикселей, имеющих с максимальную корреляцию по уровню, вычисляют с использованием этих двух пикселей смежных строк среднее значение соответствующего интерполированного пикселя дополнительной строки или вычисляют среднее значение соответствующего интерполированного пикселя дополнительной строки с использованием (n+1)-x пикселей в группах пикселей первой и второй смежных строк, интерполированный сигнал пикселя в сигналах дополнительных строк заменяют пикселем предшествующего поля в участках видеосигнала данного поля, отражающих отсутствие движения объектов, сигналы строк данного поля и полученные в результате выполнения интерполяции и замены пикселей сигналы дополнительных строк преобразовывают в видеосигнал с прогрессивной разверткой, частота и число строк развертки в кадрах которого соответственно удваивают.

Недостатком способа по схеме преобразования развертки [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.] является низкое качество преобразования и соответственно воспроизведения с увеличенными частотой и числом строк малоконтрастных вертикальных, наклонных линий и границ, а также воспроизведения горизонтальных линий и границ, соответствующих, в пределах внутрикадрового пространства, движущимся деталям телевизионных изображений.

Основной вариант реализации устройства в соответствии со схемой преобразования развертки [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.]. содержит блок обнаружения движения, последовательно включенные блоки совмещения во времени смежных сигналов кадров, полей, строк и групп пикселей сигнала поля в структуре телевизионного сигнала, выполненные на основе использования блоков задержки на необходимые интервалы времени: первого блока задержки на время, меньшее длительности телевизионного сигнала поля на половину длительности одной строки, блока задержки на время одной строки, второго блок задержки на время, меньшее длительности телевизионного сигнала поля на половину длительности одной строки (в описании указанного Пат. 2257684 соответственно блоки (262Н), (1Н), (262Н)), блоков задержки на время, равное одному периоду следования отсчетов (пикселей, элементов) в пределах строк телевизионного сигнала (в описании указанного Пат. 2257684 соответственно блоки (D)), блок обнаружения направления (через точку интерполяции) наибольшей корреляции пикселей телевизионного сигнала строки, расположенной по отношению к точке интерполяции, в пределах внутрикадрового пространства, сверху, и пикселей телевизионного сигнала строки, расположенной по отношению к точке интерполяции, в пределах внутрикадрового пространства, снизу, выходы которого подключены ко входам управления блока вычисления среднего значения пикселей по направлению наибольшей корреляции, состоящего из первого и второго блоков выбора направления усреднения пикселей входного телевизионного сигнала строки, расположенной по отношению к точке интерполяции, в пределах внутрикадрового пространства, сверху, и пикселей телевизионного сигнала строки, расположенной по отношению к точке интерполяции, в пределах внутрикадрового пространства, снизу, из первого блока суммирования, и блока умножения с фиксированным (K=0,5) коэффициентом, два блока умножения соответственно с регулируемыми (K и 1-K) коэффициентами, определяющими вес межполевой и внутриполевой интерполяционных составляющих при их усреднении, второй блок суммирования и блок двухскоростного преобразования.

Сигнал телевизионных изображений с прогрессивным порядком следования сигналов строк (с удвоением их числа в каждом поле по сравнению с исходным телевизионным сигналом) поступает на выход основного варианта устройства.

При этом в блоке обнаружения движения осуществляют оценку наличия движения в пределах межкадрового направления. Для этого ко входам данного блока подключают исходный телевизионный сигнал и сигнал, полученный после последовательной задержки в блоках задержки (262Н), (1Н), (262Н) на время, равное длительности соответственно кадра (525Н периодов (Н) следования строк). Указанная задержка позволяет обеспечить совмещение во времени и осуществить сравнительную оценку уровней пикселей в текущих и предшествующих (текущим) кадрах телевизионного сигнала. При сравнении осуществляют выявление участков с наличием изменений уровней телевизионных сигналов в текущих, по отношению к предшествующим, кадрах, что обычно связано с наличием в данных участках телевизионных сигналов составляющих сигналов изображений движущихся объектов. В блоке обнаружения движения формируют соответствующие сигналы, обеспечивающие управление разделением телевизионных сигналов в пределах строк (полей) на участки с наличием и отсутствием движущихся объектов. Сформированные сигналы управления (соответственно K и 1-K) поступают на выходы блока обнаружения движения и определяют изменения регулируемых коэффициентов двух блоков умножения. В случаях отсутствия движения в качестве пиксела точки интерполяции используют пиксель сигнала предшествующего поля (после задержки в соответствующих блоках), координаты местоположения которого во внутрикадровом пространстве совпадают с координатами точки интерполяции.

Телевизионный сигнал с выхода блока задержки (262Н) смещен во времени по отношению к сигналу на входе основного варианта устройства на 262 периода следования строк. Данный сигнал дополнительно задерживают на один период следования строк. Телевизионные сигналы смежных строк сигналов полей одновременно со входа и с выхода блока задержки на строку поступают на входы А, В, С и D, Е, F блока обнаружения направления интерполяции. При этом телевизионные сигналы нижней и верхней (дополнительно задержанной на период строки) строк (в сигналах полей) со входа и с выхода блока задержки на строку непосредственно поступают соответственно на входы F и С. Эти же сигналы поступают на входы блока обнаружения направления Е и В, а также D и А соответственно с задержкой (через блоки реализации задержки (D)) на время, равное одному периоду следования отсчетов (пикселов, элементов) в пределах строк телевизионного сигнала, и с задержкой (через блоки задержки (D)) на время, равное двум периодам следования отсчетов (пикселов, элементов) в пределах строк телевизионного сигнала. Параллельно телевизионные сигналы строк, поступающие на входы С, В, А и F, Е, D блока обнаружения направления, соединены с сигнальными входами блока вычисления среднего значения, а выходы блока обнаружения направления соединены со входами управления блока вычисления среднего значения. При этом выход блоков задержки на время, равное длительности строки, непосредственно, через блок задержки (D) на время, равное одному периоду (D) следования отсчетов (пикселов, элементов) в пределах строк телевизионного сигнала, и через два таких блока подключен в блоке вычисления среднего значения к трем сигнальным входам первого блока, а вход блока задержки на время, равное длительности строки, аналогичным образом, непосредственно и через блоки задержки, подключен здесь к сигнальным входам второго блока выбора вариантов усреднения пикселов телевизионного сигнала смежных строк, расположенных по отношению к точке интерполяции, во внутрикадровом пространстве, сверху и снизу.

На управляющие входы указанных блоков выбора вариантов усреднения пикселов телевизионного сигнала смежных строк поступают от блока обнаружения направления сигналы управления, обеспечивающие выбор сочетания на выходах блоков выбора пикселов смежных строк для последующего их усреднения в первом блоке суммирования. В блоке умножения соответственно с фиксированным (K=0,5) коэффициентом устраняется увеличение амплитуды результирующего пикселя, возникающее как результат суммирования двух пикселей в первом блоке суммирования.

В блоке обнаружения движения формируют соответствующие сигналы управления (по схеме соответственно K и 1-K), обеспечивающие разделение сигналов в пределах строк (полей) на участки с наличием и отсутствием движущихся объектов. Сформированные сигналы управления (K=1 в случае, когда движение в точке интерполяции не обнаружено) должны быть совмещены во времени с пикселями телевизионного сигнала, полученными при межстрочной интерполяции. Аналогичное совмещение должно быть осуществлено по отношению к используемым пикселам телевизионных сигналов, полученных после последовательной задержки (262Н), (1Н) и после последовательной задержки в блоках (262Н), (1Н), (262Н) на время, равное длительности соответственно кадра. Необходимое совмещение во времени указанных выше сигналов реализуют в схеме за счет использования соответствующих независимых блоков задержки (D) на время, равное одному периоду следования отсчетов (пикселей, элементов) в пределах строк телевизионного сигнала.

Телевизионные сигнала пикселей, полученные в результате осуществления межстрочной интерполяции и пикселей предшествующего поля поступают на сигнальные входы блоков умножения соответственно с регулируемыми (на основе использования упомянутых сигналов управления К и 1-K) коэффициентами, определяющими вес пикселей от предшествующего поля телевизионных сигналов и пикселей внутриполевой интерполяции при их последующем суммировании. Соответственно на выходе второго блока суммирования получают пиксели телевизионных сигналов строк, соответствующих по своему положению во внутрикадровом пространстве межстрочному интервалу в телевизионном сигнале, который предварительно задерживают в блоке (262Н). Телевизионный сигнал с выхода первого блока (262Н), после задержки в блоках (1Н) и (D) соответственно на время, равное длительности строки и одному периоду следования отсчетов (пикселей, элементов) в пределах строк телевизионного сигнала, поступает на первый вход блока двухскоростного преобразования, на второй вход которого поступает телевизионный сигнал с выхода второго блока суммирования. Указанные сигналы и используются в блоке двухскоростного преобразования для получения на выходе устройства в соответствии со схемой преобразования развертки [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.] телевизионного сигнала с удвоением, по отношению к сигналу на входе, числа и частоты строк.

Преобразованный сигнал телевизионных изображений соответственно с прогрессивным порядком следования сигналов строк (с удвоением их числа в каждом поле по сравнению с исходным телевизионным сигналом) поступает на выход основного варианта устройства.

На сигнальные входы блока обнаружения направления, использованного в основном варианте устройства, одновременно поступают пиксели телевизионного сигнала верхней и нижней строк поля (обозначены соответственно буквами A, B, C и D, E, F), с применением которых осуществляют интерполяционную реставрацию, во внутрикадровом пространстве, пикселей в пределах соответствующего межстрочного интервала. В своей входной части структура данного блока является трехканальной. Каждый из каналов содержит последовательно включенные блоки вычитания входных сигналов, вычисления абсолютного значения, умножения на постоянный коэффициент, обнаружения заданного соотношения вычисленных и умноженных абсолютных значений сигналов разности. К выходам трех блоков обнаружения заданного соотношения вычисленных и нормированных абсолютных значений сигналов разности подключены две схемы логического стробирования.

В частности, в первый блок вычитания входят независимые каскады вычитания (по пикселям) трех пикселей верхней и нижней строк, обозначенных соответственно буквами А и F, В и Е, С и D, во второй - каскады вычитания пикселей нижней строки D и Е, Е и F, в третий - каскады вычитания пикселей верхней строки А и В, В и С. Аналогичным образом в первый, второй и третий блоки вычисления абсолютного значения полученных на выходах указанных каскадов вычитания сигналов входят соответственно семь каскадов вычисления абсолютного значения сигналов разности, а в первый, второй и третий блоки умножения на постоянные коэффициенты входят соответственно семь каскадов умножения на числа, каждое из которых может быть представлено как 1/2 в целочисленной степени. Соответственно имеет место уменьшение разрядности чисел определяющих абсолютные значения сигналов разности, что, в конечном итоге, нелинейно снижает воздействие шумов на результат интерполяции.

Для идентификации приоритетности вертикального направления интерполяции из абсолютного значения разности входных пикселей В и Е вычитают заданное значение S в соответствующем каскаде вычитания. Таким образом снижается оценка уровня данного сигнала разности.

После умножения абсолютные значения разности входных А и F пикселей и разности входных С и D пикселей поступают на соответствующие входы a и c первого блока обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности, на вход b которого поступает, после указанных умножения и вычитания, абсолютное значение разности входных В и Е сигналов.

Аналогичным образом, после умножения абсолютные значения разности входных D и Е, А и В сигналов и разности входных Е и F, В и С сигналов поступают на соответствующие входы d, f и e, g второго и третьего блоков обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности. В указанных блоках обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности осуществляют сравнение значений входных сигналов.

Согласно заданным, логического типа, условиям сравнения текущих соотношений между значениями указанных выше входных сигналов a, b, c, d, e, f, g, на выходах первого, второго и третьего блоков обнаружения (заданного соотношения между вычисленными абсолютными значениями сигналов разности) формируют одиннадцать (соответственно пять, три и три) стробирующих сигналов управления. При этом в состав первой схемы стробирования включены три логических элемента "И", к трем входам первого из которых подключены соответственно пятый выход первого, первый выход второго и второй выход третьего блоков обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности. К трем входам второго из указанных логических элементов подключены соответственно пятый выход первого блока, второй выход второго и первый выход третьего блоков обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности. И, наконец, к трем входам третьего из указанных логических элементов подключены соответственно пятый выход первого блока, третий выход второго и третий выход третьего блоков обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности. Выходы первого, второго и третьего логических элементов, входящих в состав первой схемы стробирования, подключены соответственно ко вторым входам первого, третьего и к третьему входу второго из трех логических элементов, которые входят в состав второй схемы стробирования. Первые же их (трех логических элементов второй схемы стробирования) входы подключены к первому, второму и третьему выходам первого блока обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности, к четвертому выходу которого подключен второй вход второго логического элемента второй схемы стробирования. На выходах второй схемы стробирования получают сигналы управления. Эти сигналы поступают на входы управления блока вычисления среднего значения интерполируемых пикселей и параллельно поступают на управляющие входы первого и второго блоков выбора направления усреднения пикселей телевизионного сигнала смежных строк, расположенных во внутрикадровом пространстве, по отношению к точке интерполяции, сверху и снизу. При этом осуществляется выбор из (подключение к выходам блоков выбора) трех возможных вариантов: усреднение пикселей сигналов смежных строк под +90° (по вертикали), усреднение пикселей сигналов смежных строк под углом плюс 45° и усреднение пикселей сигналов смежных строк под углом минус 45°.

Кроме рассмотренной схемы преобразования развертки в описании к изобретению [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.] предложен вариант осуществления схемы, отличающийся по структуре за счет изменения позиции включения и конфигурации блока вычисления среднего значения, который подключен к выходам блока совмещения строк и групп пикселей сигнала второго поля и к трем сигнальным входам которого независимо и последовательно подключены блоки суммирования и блоки умножения с фиксированным (K=0,5) коэффициентом, выходы которых соединены с сигнальными входами блока выбора направления усреднения пикселей телевизионного сигнала смежных строк, расположенных во внутрикадровом пространстве, по отношению к точке интерполяции, сверху и снизу, причем управляющие входы блока выбора направления соединены с соответствующими выходами управления блока обнаружения направления (через точку интерполяции) наибольшей корреляции пикселей телевизионного сигнала строки, расположенной по отношению к точке интерполяции, в пределах внутрикадрового пространства, сверху, и пикселей телевизионного сигнала строки, расположенной по отношению к точке интерполяции, в пределах внутрикадрового пространства, снизу, а его выход соединен с сигнальным входом блока умножения с регулируемым (на основе подключения сигнала управления 1-K от блока обнаружения движения) коэффициентом.

Кроме рассмотренной схемы преобразования развертки, представленной на фиг.4, в описании к изобретению [Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки /Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.] предложен также вариант осуществления схемы, отличающийся тем, что ко входу устройства подключен вход блока задержки на интервал, равный длительности одного периода следования строк (1 Н) телевизионного сигнала данного поля, состоящего из блока задержки телевизионного сигнала на время, равное длительности строки, а выход блока умножения с фиксированным (K=0,5) коэффициентом непосредственно подключают ко второму входу блока двухскоростного преобразования развертки.

Соответственно ко входу устройства в данном случае подключен блок совмещения групп пикселей смежных в сигнале поля строк, содержащий блок задержки на интервал времени, равный периоду следования строк телевизионного сигнала, и блоки задержки (D) на время, равное одному периоду следования пикселей в пределах строк телевизионного сигнала, при этом вход блока задержки на время строки соединен со входом первых двух последовательно включенных блоков задержки (D) на время, равное одному периоду следования пикселей в пределах строк телевизионного сигнала, и выход блока задержки на время строки соединен со входом вторых двух последовательно включенных блоков задержки (D) на время, равное одному периоду следования пикселей в пределах строк телевизионного сигнала, входы и выходы каждого из последовательно включенных блоков задержки (D) соединены с шестью входами блока обнаружения направления и соединены соответственно с тремя сигнальными входами первого и тремя сигнальными входами второго блоков выбора направления усреднения пикселей телевизионного сигнала, выходы блока обнаружения направления параллельно соединены с первым, вторым и третьим входами управления каждого из блоков выбора направления усреднения, выходы которых подключены к первому и второму входам блока суммирования выбранных пикселей, выход блока суммирования через блок умножения с фиксированным (K=0,5) коэффициентом подключен ко второму входу блока двухскоростного преобразования, с первым входом которого через блок задержки (D) на интервал времени, равный одному периоду следования пикселей в пределах строк телевизионного сигнала, соединен выход блока задержки на интервал времени, равный периоду следования строк, к выходу устройства подключен выход блока двухскоростного преобразования.

Здесь блок задержки на время, равное длительности строки обеспечивает совпадение во времени сигналов текущей и предшествующей строк телевизионного сигнала и по существу является соответствующим блоком совмещения пикселей сигналов строк. С применением блоков задержки (D) на время, равное одному периоду следования отсчетов (пикселей, элементов) в пределах строк телевизионного сигнала, в данном устройстве обеспечено также совмещение во времени групп пикселей текущей и предшествующей во времени сигналов строк данного телевизионного сигнала поля. Назначение остальных блоков в данном варианте схемы не имеет отличий по сравнению с предшествующими версиями.

Недостатком данного варианта являются потери четкости преобразованных изображений в вертикальном (во внутрикадровом пространстве) направлении.

Недостатком же общего варианта устройства по схеме преобразования развертки [рис.4 в Пат. 2257684 Российская федерация, МПК7 H04N 7/01. Схема преобразования развертки / Мацунага Сеидзи, Онодера Дзикеда, Икеда Макото; заявитель и патентообладатель Фудзитсу дженерал лимитед. - №2002123061/09; заявлено 22.09.2000; опубл. 27.07.2005, Бюл. №21. - 32 с.; ил.] является существенное снижение качества преобразования и соответственно воспроизведения телевизионных изображений с увеличенными частотой и числом строк в условиях, когда преобразованию подвергается телевизионный сигнал изображений, содержащий, с некоторым приближением, горизонтально ориентированные линии, границы и детали, с относительно невысоким отношением сигнал/шум, что обусловливает увеличение ошибок обнаружения направления (через точку интерполяции) наибольшей корреляции пикселей телевизионных сигналов интерполируемых строк и реализации, собственно, интерполяции.

Задачей, решаемой в предлагаемом изобретении, является улучшение качества воспроизведения изображений сигналов изображений за счет увеличения в преобразуемых последовательных сигналах полей числа и частоты строк и устранения сопутствующих используемому в исходном телевизионном сигнале чересстрочному растру геометрических искажений и искажений интерполяции, которые возникают из-за действия составляющих шума в структуре преобразованных сигналов кадров, при передаче изменений формы и на границах телевизионных изображений движущихся объектов, угол φ0 ориентации которых изменяется во внутрикадровом пространстве.

Для решения поставленной задачи в способе преобразования сигнала изображения исходный видеосигнал, состоящий из последовательных во времени и модулированных по амплитуде пикселей сигналов телевизионных кадров, отражающих последовательное распределение, во времени и соответственно во внутрикадровом пространстве, пикселей сигналов полей четных и нечетных строк, преобразовывают в группу совмещенных во времени сигналов трех смежных полей, первого текущего во времени, второго, предшествующего текущему и используемого при межстрочной интерполяции, третьего, предшествующего второму, совмещают во времени сигналы строк и предшествующих, смежных во внутриполевом пространстве, строк сигнала второго поля, совмещают во времени в сигналах строк и предшествующих смежных строк этого поля эквивалентные, по порядку следования, группы пикселей, симметрично распределенные в смежной окрестности каждого n+1 пикселя с периодом, равным периоду следования пикселей в сигналах указанных строк, с n+1, по порядку следования, пикселем сигнала строки третьего поля, положение n+1 пикселя в котором совпадает с центром межстрочного промежутка в указанных смежных строках второго поля и общим центром симметрии совмещенных групп пикселей, получают межстрочной интерполяцией в пределах указанных групп пикселей смежных строк второго поля пиксели дополнительных сигналов строк развертки, соответствующие, по положению во внутрикадровом пространстве, центру межстрочного промежутка и общему центру симметрии групп по 2n+1 пикселей в сигналах смежных строк, при этом вычитают симметрично расположенные, по отношению к центру межстрочного промежутка, пиксели групп первой и второй строки и получают пиксели соответствующих независимых сигналов разности амплитуд пикселей групп в сигналах смежных строк, с использованием которых устанавливают в совокупности сравниваемых по амплитуде пикселей второго поля пару (пары) интерполируемых пикселей, имеющих амплитуду сигналов разности, которая не превышает заданное пороговое значение, вычисляют с использованием соответствующих пар совмещенных пикселей сигналов смежных строк среднее значение амплитуды соответствующего интерполирующего по межстрочному направлению n+1 пикселя дополнительной строки, используют для интерполирования пикселя дополнительной строки пиксель, полученный усреднением соответствующих пикселей первой и второй смежных строк, для которых характерна минимальная разность в амплитуде сравниваемых пикселей, преобразовывают пиксели сигналов строк второго поля и сигналов дополнительных строк в видеосигнал с прогрессивной разверткой, частоту и число строк развертки в кадрах которого соответственно удваивают, перед вычислением амплитуды интерполированного пикселя увеличивают число совмещенных во времени и симметрично распределенных по отношению к центру межстрочного промежутка и общему центру симметрии сигналов смежных строк и соответствующих групп совмещенных пикселей в сигналах строк второго поля с получением соответствующей матрицы совмещенных пикселей, совмещают во времени полученные сигналы строк и групп пикселей в сигналах строк второго поля с матрицами совмещенных пикселей первого и третьего полей, положение центрального пикселя строк которых, во внутрикадровом пространстве, совпадает с общим межстрочным центром симметрии матрицы совмещенных пикселей второго поля, ограничивают протяженность спектра огибающей последовательностей пикселей в матрицах пикселей второго поля в горизонтальном, во внутрикадровом пространстве, направлении, при этом ограничение полосы частот реализуют на основе весовых суммирований двух и более смежных и вычитания удаленных по положению в строках пикселей и нормировании полученных результатов, которые и используют для получения сигналов разности пар пикселей смежных строк второго поля, раздельно получают сигналы межстрочных разностей в пределах матриц совмещенных пикселей во внутрикадровом пространстве до и после центра межстрочного промежутка указанных двух смежных строк второго поля, попарно вычитают в каждом из сигналов первого и третьего полей симметрично распределенные, по отношению к центральному пикселю, пиксели матриц, получают среднее значение пар пикселей, разность которых не превышает первый заданный порог, вычитают из каждого полученного среднего значения пикселя отдельной пары значение центрального пикселя, суммируют с центральным пикселем в каждом из сигналов первого и третьего полей лишь пиксели всех тех из пар, разность средних значений и значения центрального пикселя которых не превышает заданное, по максимальной амплитуде, второе пороговое, значение, нормируют, при наличии суммируемых пикселей, полученные результаты независимых, в первом и втором полях, суммирований по амплитудам и полученные центральные пиксели первого и третьего полей вычитают с последующей оценкой наличия превышения заданным третьим пороговым значением амплитуды полученного пикселя разности, при наличии которого суммируют и нормируют уже указанные полученные центральные пиксели первого и третьего полей с определением значения пикселя интерполяции по межкадровому направлению, которое устанавливают результатом интерполяции при превышениях амплитудой всех сигналов разности ограниченных по протяженности спектра огибающей последовательностей пикселей первой и второй смежных строк второго поля заданного четвертого порогового значения, суммируют и нормируют результаты суммирования пикселей межстрочной и межкадровой интерполяций при отсутствии превышений соответствующими сигналами разности соответственно третьего и четвертого пороговых значений, устанавливают результатом интерполяции полученное при этом значение пикселя, получают значение интерполируемого пикселя интерполяцией пикселей смежных строк второго поля по вертикальному направлении при превышении соответствующих заданных пороговых значений сигналами разности и по межкадровому и по межстрочному направлениям, при этом устанавливают в процессе усреднения вес пикселей до и после центра межстрочного промежутка смежных строк второго поля, обратно пропорциональным величинам амплитуд сигналов межстрочных разностей в пределах соответствующей матрицы совмещенных пикселей.

Для устранения указанных искажений в устройство по прототипу, содержащее вход устройства, блок совмещения строк и групп пикселей телевизионного сигнала второго поля, блок вычисления среднего значения уровня пикселей в сигнале второго поля, информационные входы которого соединены с выходами блока совмещения строк и групп пикселей телевизионного сигнала второго поля, блок выбора пикселей, блок обнаружения направления интерполяции пикселей сигналов смежных строк второго поля с первыми управляющими выходами, подключенными ко входам управления соответствующего блока выбора пикселей, входы информационных сигналов которого соединены с выходами блока вычисления среднего значения уровня пикселей в сигнале второго поля, блок двухскоростного преобразования числа и частоты сигналов строк, независимый информационный вход которого соединен с выходом блока совмещения групп пикселей сигнала второго поля и выход которого подключен к выходу устройства, введены первый блок формирования результирующего пикселя сигнала первого поля, второй блок формирования результирующего пикселя сигнала третьего поля, блок совмещения во времени строк и групп пикселей телевизионного сигнала первого поля, который включен между входом устройства и входом блока совмещения строк и групп пикселей телевизионного сигнала второго поля и выходы которого соединены с информационными входами первого блока формирования результирующего пикселя сигнала первого поля, блок совмещения строк и групп пикселей телевизионного сигнала третьего поля, который подключен к выходу блока совмещения строк и групп пикселей телевизионного сигнала второго поля и выходы которого соединены с информационными входами второго блока формирования результирующего пикселя сигнала третьего поля, первый блок вычисления результирующего пикселя сигналов первого и третьего полей, первый информационный вход которого соединен с выходом первого блока формирования результирующего пикселя сигнала первого поля и второй информационный вход которого соединен с выходом второго блока формирования результирующего пикселя третьего поля, второй блок вычисления результирующего пикселя сигнала второго поля, информационные входы которого соединены с выходами блока выбора пикселей, и третий блок вычисления результирующего пикселя сигналов первого, второго и третьего полей, блок горизонтальной низкочастотной фильтрации пикселей сигналов строк второго поля, входы которого соединены с выходами блока совмещения строк и групп пикселей телевизионного сигнала второго поля, блок формирования экстраполированного пикселя сигнала второго поля, первые входы которого также соединены с информационными выходами блока совмещения строк и групп пикселей телевизионного сигнала второго поля, вторые информационные входы блока формирования экстраполированного пикселя сигнала второго поля соединены с выходами блока горизонтальной низкочастотной фильтрации пикселей сигналов строк второго поля, выходы которого соединены со входами блока обнаружения направления интерполяции пикселей сигналов смежных строк второго поля, вторые и третьи управляющие выходы блока обнаружения направления интерполяции пикселей сигналов смежных строк второго поля подключены ко входам управления второго блока вычисления результирующего пикселя сигнала второго поля и ко входам управления третьего блока вычисления результирующего пикселя сигналов первого, второго и третьего полей, другой вход управления которого соединен с управляющим выходом первого блока вычисления результирующего пикселя сигнала первого поля, информационный выход блока формирования экстраполированного пикселя сигнала второго поля подключен к первому соответствующему входу блока вычисления результирующего пикселя сигналов первого, второго и третьего полей, второй и третий информационные входы которого соединены с ответствующими выходами первого блока вычисления результирующего пикселя сигналов первого и третьего полей и с выходами второго блока вычисления результирующего пикселя второго поля, информационный выход второго блока вычисления результирующего пикселя сигналов первого, второго и третьего полей соединен с другим информационным входом блока двухскоростного преобразования числа и частоты сигналов строк.

Причем блоки формирования результирующих пикселей сигналов первого и третьего полей являются идентичными и содержат вход пикселя сигнала первого (третьего) поля, совпадающего по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, заданное количество m пар входов пикселей сигналов смежных строк первого (третьего) поля, симметрично распределенных по отношению к пикселю, совпадающему по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, вход сигнала фиксированного уровня, вход сигнала "логической единицы", блоки суммирования с двумя входами, независимые входы каждого из которых соединены с указанными парами входов пикселей, блоки умножения на фиксированный коэффициент, входы каждого из которых соединены с выходами блоков суммирования, блоки электронного ключа и блоки вычитания, первый из входов каждого блока вычитания параллельно соединен со входом пикселя сигнала первого поля, совпадающего по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, и второй из входов каждого блока вычитания параллельно соединен с выходом одного из блоков умножения на фиксированный коэффициент и с информационным входом одного из блоков электронного ключа, блоки вычисления абсолютного значения, вход каждого из которых соединен с выходом одного из блоков вычитания, компараторы, один из входов каждого из которых соединен с выходом одного блоков вычисления абсолютного значения и второй из входов соединен со входом сигнала фиксированного уровня, логические элементы "ME", вход каждого из которых соединен с выходом одного из компараторов, первый и второй блоки суммирования с m+1 входами, m+1 вход первого из которых соединен со входом сигнала "логической единицы" и каждый из других m входов первого из которых параллельно соединен с выходом одного из логических элементов "НЕ" и со входом управления одного из блоков электронного ключа, выход каждого из блоков электронного ключа подключен к одному из m входов второго блока суммирования с m+1 входами, m+1 вход которого подключен к параллельно соединенным первым из входов каждого блока вычитания и входом пикселя сигнала первого поля, совпадающего по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, блок делителя с переменным коэффициентом деления, вход управления которого подключен к выходу первого блока суммирования с m+1 входами и информационный вход которого подключен к выходу второго блока суммирования с m+1 входами, выход каждого из блоков формирования результирующих пикселей сигналов первого и третьего полей подключен к выходу блока делителя с переменным коэффициентом деления.

Блок горизонтальной низкочастотной фильтрации пикселей сигналов строк второго поля содержит распределенные входы совмещенных, первой и второй, групп пикселей смежных, верхней и нижней, по отношению к интерполируемому пикселю, сигналов строк второго поля, 3k блоков умножения на фиксированный коэффициент, k блоков суммирования с тремя входами, один вход отдельного из которых непосредственно подключен ко входу центрального, из каждых трех рядом расположенных в пределах первой и второй из групп пикселей распределенным входам пикселей сигналов смежных строк второго поля и два других из которых через первый и второй блоки умножения на фиксированный коэффициент подключены к другим двум из каждых трех, рядом расположенных в пределах каждой из групп по отношению к центральному, распределенным входам пикселей, при этом выход отдельного из k блоков суммирования подключен к независимому из k выходов блока горизонтальной низкочастотной фильтрации пикселей сигналов строк второго поля через третий блок умножения на фиксированный коэффициент.

Блок формирования экстраполированного пикселя сигнала второго поля содержит попарно распределенные входы совмещенных во времени пикселей, совпадающих в сигналах соответствующих совокупностей пикселей смежных, трех и более, предшествующих строк второго поля по положению с интерполируемым пикселем, и попарно распределенные входы совмещенных во времени пикселей, совпадающих в сигналах смежных, трех и более, последующих строк второго поля по положению с интерполируемым пикселем, вход пикселя, совпадающего по положению в сигнале первой из смежных, трех и более, предшествующих строк с интерполируемым пикселем, вход пикселя, совпадающего по положению с интерполируемым пикселем в сигнале первой из смежных, трех и более, последующих строк, блоки вычитания, два входа каждого из которых соединены с попарно распределенными входами блока формирования экстраполированного пикселя сигнала второго поля, при этом один из двух входов первого блока вычитания соединен в блоке формирования экстраполированного пикселя сигнала второго поля со входом указанного пикселя сигнала первой предшествующей строки и второй из входов соединен со входом указанного пикселя сигнала второй предшествующей строки, один из двух входов второго блока вычитания соединен в блоке формирования экстраполированного пикселя сигнала второго поля со входом указанного пикселя сигнала первой последующей строки и второй из входов соединен со входом указанного пикселя сигнала второй последующей строки, один из двух входов третьего блока вычитания соединен в блоке формирования экстраполированного пикселя сигнала второго поля со входом указанного пикселя сигнала первой предшествующей строки и второй из входов соединен со входом указанного пикселя сигнала третьей предшествующей строки, один из двух входов четвертого блока вычитания соединен в блоке формирования экстраполированного пикселя сигнала второго поля со входом указанного пикселя сигнала первой последующей строки и второй из входов соединен со входом указанного пикселя сигнала третьей последующей строки, первый второй, третий и четвертый блоки вычисления абсолютного значения, вход каждого из которых соединен с выходом соответствующего по порядку блоков вычитания, первый блок обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности, входы которого соединены с выходами первого и второго блоков вычисления абсолютного значения, второй блок обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности, входы которого соединены с выходами третьего и четвертого блоков вычисления абсолютного значения, блок суммирования с двумя входами, к первому из которых подключен вход пикселя, совпадающего по положению в сигнале первой из смежных, трех и более, предшествующих строк с интерполируемым пикселем и ко второму из которых подключен вход пикселя, совпадающего по положению с интерполируемым пикселем в сигнале первой из смежных, трех и более, последующих строк, блок умножения на фиксированный коэффициент, вход которого подключен к выходу блока суммирования, три логических элемента "И", первые входы первого, второго и третьего из которых параллельно соединены с третьим выходом первого блока обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности и вторые входы первого, второго и третьего из которых подключены соответственно к первому, второму и третьему выходам второго блока обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности, пять блоков электронного ключа, при этом с первым выходом первого блока обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности соединен вход управления первого из блоков электронного ключа, информационный вход которого параллельно подключен ко входу пикселя, совпадающего по положению с интерполируемым пикселем в сигнале первой из смежных, трех и более, предшествующих строк, и к первому входу блока суммирования, со вторым выходом первого блока обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности соединен вход управления второго из блоков электронного ключа, информационный вход которого параллельно подключен ко входу пикселя, совпадающего по положению с интерполируемым пикселем в сигнале первой из смежных, трех и более, последующих строк, и ко второму входу блока суммирования, с выходом первого логического элемента "И" соединен вход управления третьего блока электронного ключа, информационный вход которого параллельно подключен ко входу пикселя, совпадающего по положению с интерполируемым пикселем в сигнале первой из смежных, трех и более, предшествующих строк, к первому входу блока суммирования и к информационному входу первого блока электронного ключа, с выходом второго логического элемента "И" соединен вход управления четвертого блока электронного ключа, информационный вход которого параллельно подключен ко входу пикселя, совпадающего по положению с интерполируемым пикселем в сигнале первой из смежных, трех и более, последующих строк, ко второму входу блока суммирования и к информационному входу второго блока электронного ключа, с выходом третьего логического элемента "И" соединен вход управления пятого блока электронного ключа, информационный вход которого подключен к выходу блока умножения на фиксированный коэффициент, выходы блоков электронного ключа параллельно подключены к выходу блока формирования экстраполированного пикселя сигнала второго поля.

Причем в блок обнаружения направления интерполяции, содержащий в каждом из трех независимых каналов схемы попарно распределенные входы симметрично расположенных по отношению к интерполируемому пикселю, пикселей совмещенных, первой и второй, групп смежных, верхней и нижней, сигналов строк второго поля, блоки вычитания, входы каждого из которых подключены к попарно распределенным входам симметрично расположенных по отношению к интерполируемому пикселю пикселей, и выходы каждого из которых подключены ко входу блока вычисления абсолютного значения, первые выходы сигналов управления, введены в каждый из независимых каналов схем вторые из выходов сигналов управления, входы сигнала фиксированного уровня, компараторы, первый вход каждого из которых соединен со входом сигнала фиксированного уровня и второй вход каждого из которых подключен к выходу блока вычисления абсолютного значения, логические элементы "НЕ", вход каждого из которых параллельно подключен к выходу компаратора и к отдельному из трех первых выходов сигналов управления и выход каждого из которых подключен к отдельному из трех вторых выходов сигнала управления блока обнаружения направления интерполяции.

Первый блок вычисления результирующего пикселя сигналов первого и третьего полей содержит вход результирующего пикселя сигнала первого поля, вход результирующего пикселя сигнала третьего поля, вход сигнала фиксированного уровня, первый и второй выходы сигналов управления, информационный выход результирующего пикселя первого и третьего полей, выходы сигналов управления, блок вычитания с двумя входами и блок суммирования с двумя входами, первый из входов которого параллельно соединен со входом результирующего пикселя сигнала первого поля и первым входом блока вычитания и второй из входов которого параллельно соединен со входом результирующего пикселя сигнала третьего поля и вторым входом блока вычитания, блок вычисления абсолютного значения, вход которого соединен с выходом блока вычитания, блок умножения на фиксированный коэффициент, вход которого подключен к выходу блока суммирования, компаратор, первый вход которого соединен со входом сигнала фиксированного уровня и второй вход которого подключен к выходу блока вычисления абсолютного значения, логический элемент "НЕ", вход которого параллельно подключен к первому выходу сигнала управления и к выходу компаратора, блок электронного ключа, вход управления которого параллельно подключен ко второму выходу сигнала управления и к выходу логического элемента "НЕ", информационный вход которого соединен с выходом блока умножения на фиксированный коэффициент и выход которого подключен к информационному выходу результирующего пикселя первого и третьего полей.

Третий блок вычисления результирующего пикселя сигналов первого второго и третьего полей содержит информационный вход результирующего пикселя от первого блока вычисления результирующего пикселя сигналов первого и третьего полей, информационный вход результирующего пикселя от второго блока вычисления результирующего пикселя сигнала второго поля, вход экстраполированного пикселя от блока формирования экстраполированного пикселя сигнала второго поля, вход сигнала фиксированного уровня, первый и второй входы сигналов управления от первого блока вычисления результирующего пикселя сигналов первого и третьего полей, первые три входа сигналов управления от блока обнаружения направления интерполяции и вторые три входа сигналов управления от блока обнаружения направления интерполяции, первый логический элемент "И" с четырьмя входами, первые три из которых подключены к первым трем входам сигналов управления от блока обнаружения направления интерполяции и четвертый из которых подключен к первому выходу сигнала управления от первого блока вычисления результирующего пикселя сигналов первого и третьего полей, логический элемент "ИЛИ" с тремя входами, которые подключены ко вторым трем входам сигналов управления от блока обнаружения направления интерполяции, второй логический элемент "И" с двумя входами, первый из входов которого подключен к выходу логического элемента "ИЛИ", блок вычитания с двумя входами, первый из которых подключен к информационному входу результирующего пикселя от первого блока вычисления результирующего пикселя сигналов первого и третьего полей и второй вход которого подключен к информационному входу результирующего пикселя от второго блока вычисления результирующего пикселя сигнала второго поля, первый блок суммирования с двумя входами, первый из которых параллельно подключен к информационному входу результирующего пикселя от первого блока вычисления результирующего пикселя сигналов первого и третьего полей и к первому входу блока вычитания, блок вычисления абсолютного значения, вход которого соединен с выходом блока вычитания, блок умножения на фиксированный коэффициент, вход которого подключен к выходу первого блока суммирования с двумя входами, компаратор, первый вход которого соединен со входом сигнала фиксированного уровня и второй вход которого подключен к выходу блока вычисления абсолютного значения, первый логический элемент "НЕ", вход которого параллельно подключен ко второму входу второго логического элемента "И" и к выходу компаратора, третий логический элемент "И" с двумя входами, первый из входов которого подключен к выходу первого логического элемента "НЕ" и второй из входов которого подключен к первому входу сигнала управления от первого блока вычисления результирующего пикселя сигналов первого и третьего полей, второй логический элемент "НЕ", вход которого подключен к выходу третьего логического элемент "И", третий логический элемент "НЕ", вход которого подключен к выходу второго логического элемента "И" с двумя входами, четвертый логический элемент "И" с тремя входами, первый из которых подключен к выходу второго логического элемента "НЕ", второй из которых подключен к выходу третьего логического элемента "НЕ" и третий из которых параллельно подключен ко второму входу третьего логического элемента "И" и ко второму входу сигнала управления от первого блока вычисления результирующего пикселя сигналов первого и третьего полей, первый, второй, третий и четвертый блоки электронного ключа, информационный вход первого из которых параллельно соединен с информационным входом результирующего пикселя от второго блока вычисления результирующего пикселя сигнала второго поля и со вторыми входами первого блока суммирования и блока вычитания, информационный вход второго из блоков электронного ключа соединен с выходом блока умножения на фиксированный коэффициент, информационный вход третьего из блоков электронного ключа параллельно соединен с информационным входом результирующего пикселя от первого блока вычисления результирующего пикселя сигналов первого и третьего полей и с первыми входами блока вычитания и первого блока суммирования с двумя входами, информационный вход четвертого из блоков электронного ключа соединен со входом экстраполированного пикселя от блока формирования экстраполированного пикселя сигнала второго поля, при этом вход сигнала управления первого блока электронного ключа параллельно соединен с выходом второго логического элемента "И" и входом третьего логического элемента "НЕ", вход сигнала управления второго блока электронного ключа параллельно соединен с выходом третьего логического элемента "И" и входом второго логического элемента "НЕ", вход сигнала управления третьего блока электронного ключа подключен к выходу четвертого логического элемента "И" и вход сигнала управления четвертого блока электронного ключа подключен к выходу первого логического элемента "И", второй блок суммирования с четырьмя входами, выход которого подключен к выходу блока вычисления результирующего пикселя первого второго и третьего полей и каждый из четырех входов которого соединен с выходом отдельного из четырех блоков электронного ключа.

Полученное на выходе устройства телевизионное изображение отражается во внутрикадровом пространстве построчным растром и не имеет искажений в передаче структуры границ движущихся объектов, ортогональных направлению движения.

Предложенное устройство, обеспечивающее эффективное преобразование чересстрочного варианта развертки в построчный, показано на фиг.1., где 1 - вход устройства, 2 - блок совмещения во времени строк и групп пикселей сигналов первого, второго и третьего полей, 3 - первый блок формирования результирующего пикселя сигнала первого поля, 4 - второй блок формирования результирующего пикселя сигнала третьего поля, 5 - блок горизонтальной низкочастотной фильтрации пикселей сигналов строк второго поля, 6 - блок формирования экстраполированного пикселя сигнала второго поля, 7 - блок вычисления среднего значения уровня пикселей в сигнале второго поля, 8 - третий блок формирования результирующего пикселя второго поля, 9 - блок обнаружения направления интерполяции пикселей сигналов смежных строк второго поля, 10 - блок выбора пикселей, 11 - второй блок вычисления результирующего пикселя сигнала второго поля, 12 - третий блок вычисления результирующего пикселя сигналов первого, второго и третьего полей, 13 - первый блок вычисления результирующего пикселя сигналов первого и третьего полей, 14 - блок двухскоростного преобразования числа и частоты сигналов строк, 15 - выход устройства;

на фиг.2 - Формирование изображений движущегося в горизонтальном направлении по растру объекта в последовательности четных и нечетных полей

а. Исходное изображение объекта;

б. Сформированные сигналы изображений объекта в последовательности полукадров;

в. Кадры изображения при совмещении смежных, четного и нечетного, полукадров;

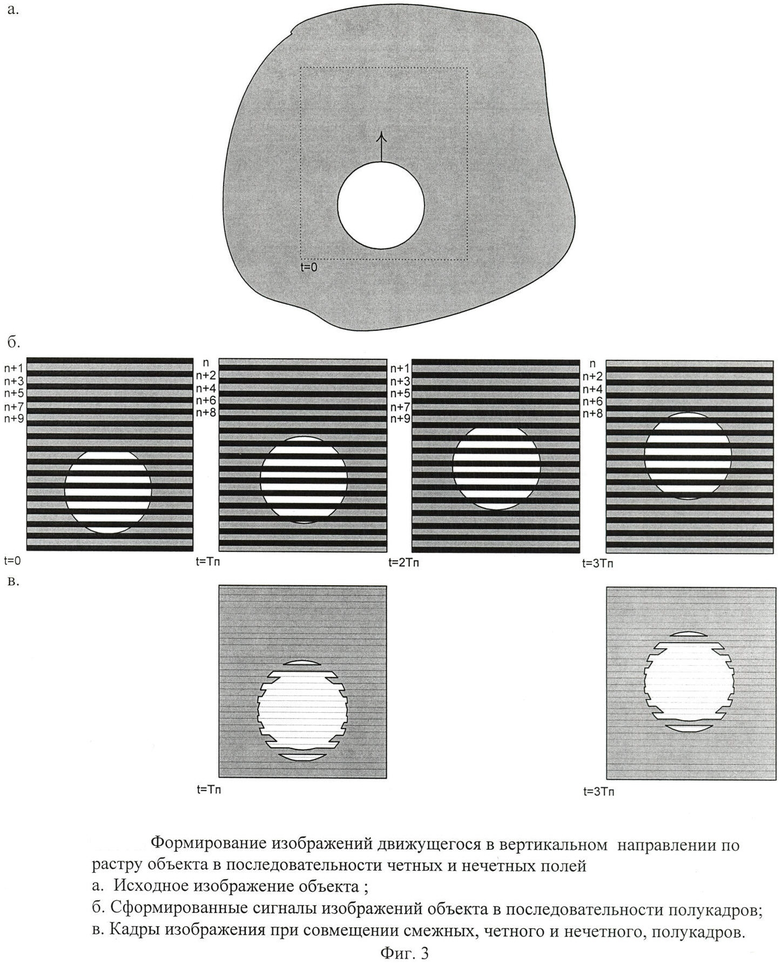

на фиг.3 - Формирование изображений движущегося в вертикальном направлении по растру объекта в последовательности четных и нечетных полей;

а. Исходное изображение объекта;

б. Сформированные сигналы изображений объекта в последовательности полукадров;

в. Кадры изображения при совмещении смежных, четного и нечетного, полукадров;

на фиг.4 - Формирование изображений движущегося в направлении 45 градусов по растру объекта в последовательности четных и нечетных полей;

а. Исходное изображение объекта;

б. Сформированные сигналы изображений объекта в последовательности полукадров;

в. Кадры изображения при совмещении смежных, четного и нечетного, полукадров;

на фиг.5 - а. Формирование интерполированного пикселя в первом и третьем полях;

б. Формирование НЧ-составляющих и экстраполированного пикселя во втором поле;

на фиг.6 - Синтезированное тестовое изображение;

а. без преобразования чересстрочного варианта развертки в построчный;

б. без преобразования чересстрочного варианта развертки в построчный, увеличенный фрагмент;

в. с преобразованием чересстрочного варианта развертки в построчный, выполненным как в прототипе, увеличенный фрагмент;

г. с преобразованием чересстрочного варианта развертки в построчный, выполненным предложенным методом, увеличенный фрагмент;

на фиг.7 - Реальное тестовое изображение:

а. без преобразования чересстрочного варианта развертки в построчный;

б. без преобразования чересстрочного варианта развертки в построчный, увеличенный фрагмент,

в. с преобразованием чересстрочного варианта развертки в построчный, выполненным предложенным методом;

г. с преобразованием чересстрочного варианта развертки в построчный, выполненным предложенным методом, увеличенный фрагмент;

на фиг.8 - блок (2) совмещения во времени строк и групп пикселей сигналов первого, второго и третьего полей, где 16 - блок совмещения строк и групп пикселей телевизионного сигнала текущего (первого) поля, 17 - блок совмещения строк и групп пикселей телевизионного сигнала предшествующего (второго) поля со строками и группами пикселей телевизионного сигнала первого поля, 18 - блок совмещения строк и групп пикселей телевизионного сигнала предшествующего второму полю со строками и группами пикселей телевизионного сигнала первого поля, 19 - выходы строк и групп пикселей телевизионного сигнала первого поля, совмещенных во времени со строками и группами пикселей телевизионного сигнала второго и третьего полей, 20 - выходы строк и групп пикселей телевизионного сигнала второго поля, совмещенных во времени со строками и группами пикселей телевизионного сигнала первого и третьего полей, 21 - выходы строк и групп пикселей телевизионного сигнала третьего поля, совмещенных во времени со строками и группами пикселей телевизионного сигнала первого и третьего полей;

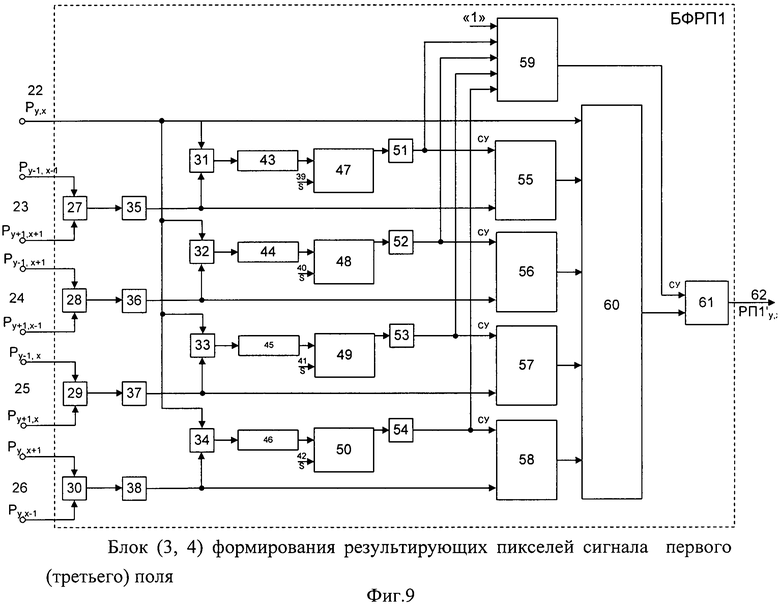

на фиг.9 - блок (3 (4)) формирования результирующих пикселей сигнала первого (третьего) поля, где 22 - вход пикселя сигнала первого поля, совпадающего по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, 23, 24, 25, 26 - пары входов пикселей сигналов смежных строк первого поля, симметрично распределенных по отношению к пикселю, совпадающему по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, 27, 28, 29, 30 - блоки суммирования с двумя входами, 31, 32, 33, 34 - блоки вычитания с двумя входами, 35, 36, 37, 38 - блоки умножения на фиксированный коэффициент, 39, 40, 41, 42 - входы сигналов фиксированного уровня, 43, 44, 45, 46 - блоки вычисления абсолютного значения, 47, 48, 49, 50 - компараторы, 51, 52, 53, 54 - логические элементы "НЕ", 55, 56, 57, 58 - блоки электронного ключа, 59, 60 - блоки суммирования с m+1 входами, "1" - вход сигнала "логической единицы" 61 - блок делителя с переменным коэффициентом деления, 62 - выход блока;

на фиг.10 - блок (5) горизонтальной низкочастотной фильтрации пикселей сигналов строк второго поля, где 63 (631, 632, 633; 632, 633, 634; …; 63k-3, 63k-2, 63k-1; 63k-2, 63k-1, 63k) - распределенные, по смежным трем, входы пикселей из числа совмещенных, первой и второй, групп пикселей верхней и нижней, по отношению к интерполируемому пикселю, сигналов строк второго поля, 64 (641, 642, 643 … 642n-3, 642n-2, 642n-1, 642n) - блоки умножения на фиксированный коэффициент, 65 (651, 652, 653 … 65n-3, 65n-2, 65n-1, 65n) - блоки суммирования, 66 (661, 662, 663 … 66n-3, 66n-2, 66n-1, 66n) - блоки умножения на фиксированный коэффициент, 67 (671, 672, 673, …, 67n-3, 67n-2, 67n-1, 67n) - выходы блока;

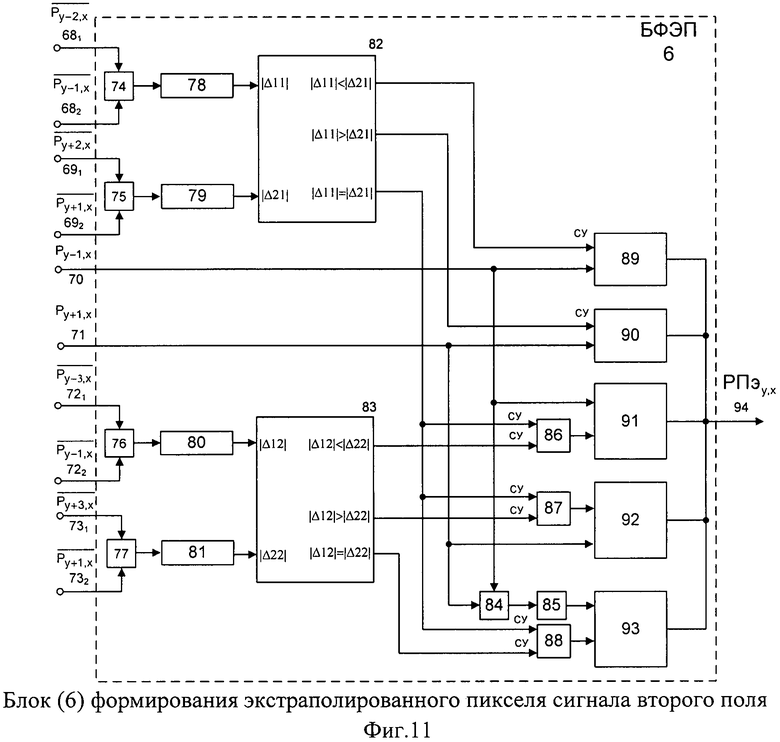

на фиг.11 - блок (6) блок формирования экстраполированного пикселя сигнала второго поля, где 68 - попарно распределенные входы пикселей, совпадающих по положению с интерполируемым пикселем в сигналах первой (вход 681) и второй (вход 682) из смежных, трех и более, предшествующих строк, 69 - попарно распределенные входы пикселей, совпадающих по положению с интерполируемым пикселем в сигналах первой (вход 691) и второй (вход 692) из смежных, трех и более, последующих строк, 70 - вход пикселя, совпадающего по положению в сигнале первой из смежных, трех и более, предшествующих строк с интерполируемым пикселем, 71 вход пикселя, совпадающего по положению в сигнале первой из смежных, трех и более, последующих строк с интерполируемым пикселем, 72 - попарно распределенные входы пикселей, совпадающих по положению с интерполируемым пикселем в сигналах первой (вход 721) и третьей (вход 722) из смежных, трех и более, предшествующих строк, 73 - попарно распределенные входы пикселей, совпадающих по положению с интерполируемым пикселем в сигналах первой (вход 731) и третьей (вход 732) из смежных, трех и более, последующих строк, 74, 75, 76, 77 - блоки вычитания с двумя входами, 78, 79, 80, 81 - блоки вычисления абсолютного значения сигналов разности, 82, 83 - блоки обнаружения заданного соотношения вычисленных абсолютных значений сигналов разности, 84 - блок суммирования с двумя входами, 85 - блок умножения на фиксированный коэффициент, 86, 87, 88 - логические элементы "И", 89, 90, 91, 92, 93 - блоки электронного ключа, 94 - выход блока формирования экстраполированного пикселя сигнала второго поля;

на фиг.12 - блок (7) вычисления среднего значения уровня пикселей в сигнале второго поля, где 95 - заданное количество входов пар пикселей сигналов двух смежных (верхней и нижней - 1 и 2) строк сигнала второго поля (три пары: 9511-9523, 9512-9522, 9513-9521), симметрично распределенных по отношению к центру симметрии, совпадающему по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, 96, 97, 98 - блоки суммирования с двумя входами, 99, 100, 101 - блоки умножения на фиксированный коэффициент, 102 - независимые выходы блока (1021, 1022, 1023) вычисления среднего значения уровня пикселей в сигнале второго поля;

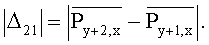

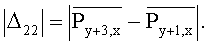

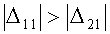

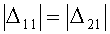

на фиг.13 - блок (9) обнаружения направления интерполяции пикселей сигналов смежных строк второго поля, где 103 - заданное количество входов пар пикселей сигналов двух смежных (верхней и нижней - 1 и 2) строк сигнала второго поля (три пары: 10311-10323, 10312-10322, 10313-10321), симметрично распределенных по отношению к центру симметрии, совпадающему по положению во внутрикадровом пространстве с интерполируемым пикселем дополнительных строк сигнала второго поля, 104, 105, 106 - блоки вычитания с двумя входами, 107, 108, 109 - блоки вычисления абсолютного значения сигналов разности, 110 - входы (1101, 1102, 1103 сигнала фиксированного уровня, 111, 112, 113 - компараторы, 114 - первые выходы (1141, 1142, 1143) сигналов управления, 115, 116, 117 - логические элементы "НЕ", 118 - вторые выходы (1181, 1182, 1183) сигналов управления блока обнаружения направления интерполяции пикселей сигналов смежных строк второго поля;

на фиг.14 - блок (10) выбора пикселей, где 119 - входы (1191, 1192, 1193) вторых сигналов управления блока обнаружения направления интерполяции пикселей сигналов смежных строк второго поля, 120 - информационные входы (1201, 1202, 1203) от блока вычисления среднего значения уровня пикселей в сигнале второго поля, 121, 122, 123 - блоки электронного ключа, 124 - информационные выходы (1241, 1242, 1243) блока выбора пикселей;