СП

со оо

О5

оэ

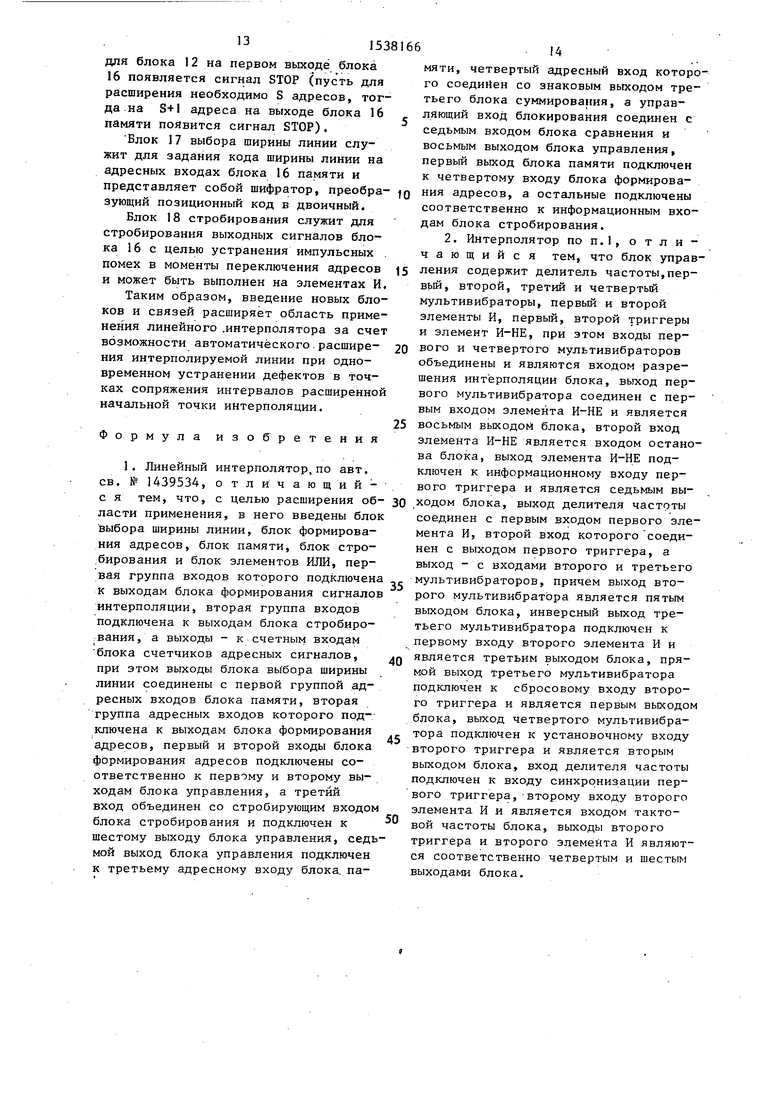

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

| Устройство для формирования растрового изображения кривых | 1986 |

|

SU1446646A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

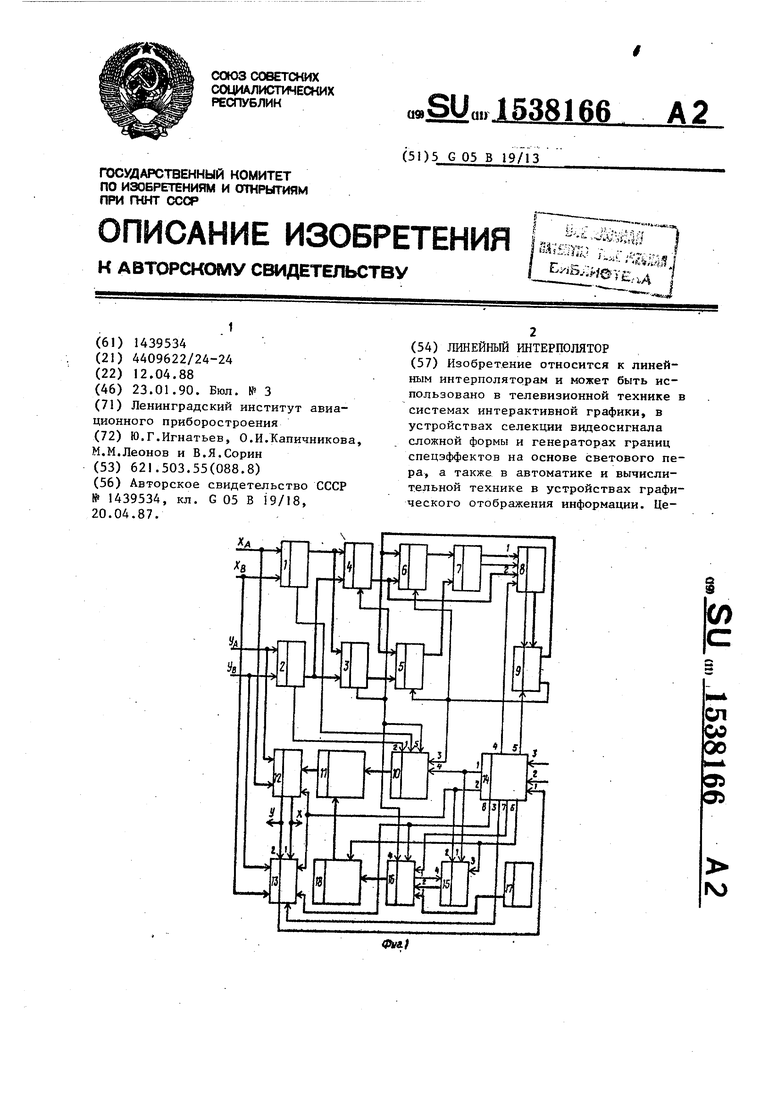

Изобретение относится к линейным интерполяторам и может быть использовано в телевизионной технике в системах интерактивной графики, в устройствах селекции видеосигнала сложной формы и генераторах границ спецэффектов на основе светового пера, а также в автоматике и вычислительной технике в устройствах графического отображения информации. Целью изобретения является расширение области применения линейного интерполятора. Интерполятор содержит первый 1, второй 2, третий 3 блоки суммирования, первый 4, второй 5, третий 6 коммутаторы, блок 7 вычисления оценочной функции, четвертый коммутатор 8, регистр 9 оценочной функции, блок 10 формирования сигналов интерполяции, блок 11 элементов ИЛИ, блок 12 счетчиков адресных сигналов, блок 13 сравнения, блок 14 управления, блок 15 формирования адресов, блок 16 памяти, блок 17 выбора ширины линии и блок 18 стробирования. Введение блоков формирования адресов, памяти, выбора ширины линии, стробирования, а также новых связей в линейный интерполятор расширяет область его применения за счет возможности автоматического расширения интерполируемой линии при одновременном устранении дефектов в точках сопряжения интервалов интерполяции путем формирования расширенной начальной точки интерполяции. 7 ил.

N)

3153

лью изобретения является расширение области применения линейного интерполятора. Интерполятор содержит первый 1, второй 2, третий 3 блоки суммирования, первый 4, второй 5, третий 6 коммутаторы, блок 7 вычисления оценочной функции, четвертый коммутатор 8, регистр 9 оценочной функции, блок 1& формирования сигналов интер- поляции, блок 11 элементов ИЛИ, блок

12счетчиков адресных сигналов, блок

13сравнения, блок 14 управления, блок 15 формирования адресов, блок

Изобретение относится к линейным интерполяторам, может быть использовано в телевизионной технике в системах интерактивной графики, в устройствах селекции видеосигнала сложной формы и генераторах границ спецэффектов на основе светового пера, а также в автоматике и вычислительной технике, в устройствах графического отображения информации и Является усовершенствованием устройст- ва по авт. св. W 1439534.

Целью изобретения является расширение области применения линейного интерполятора.

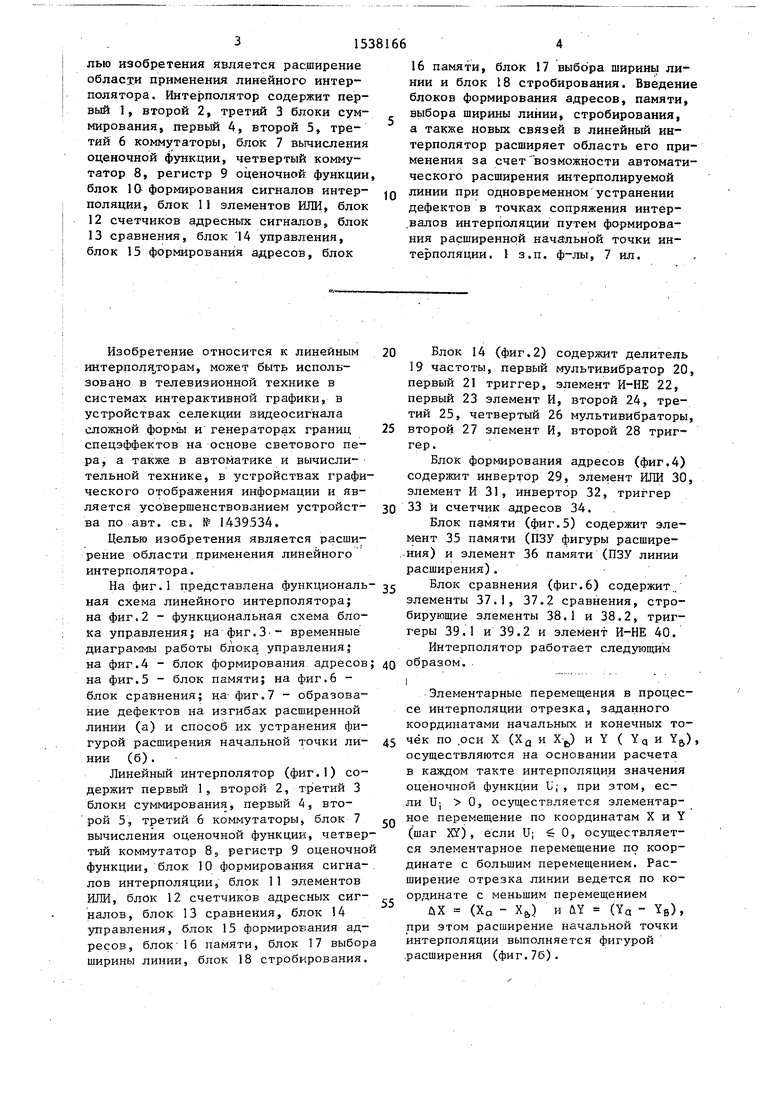

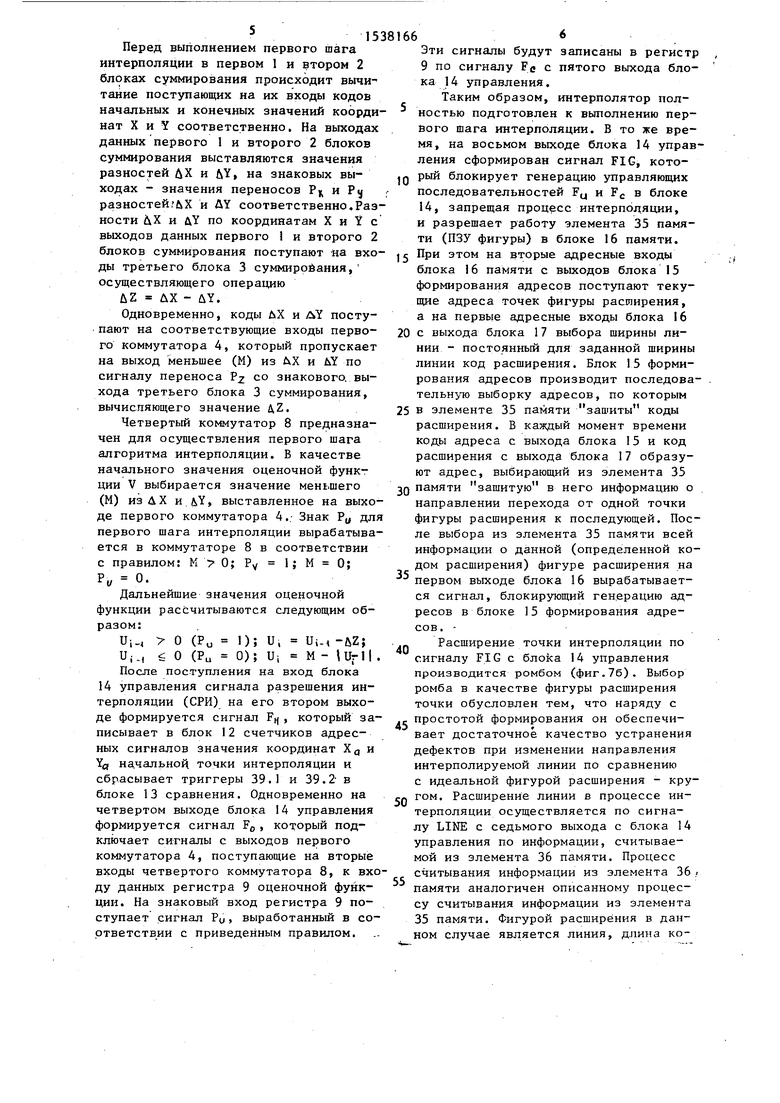

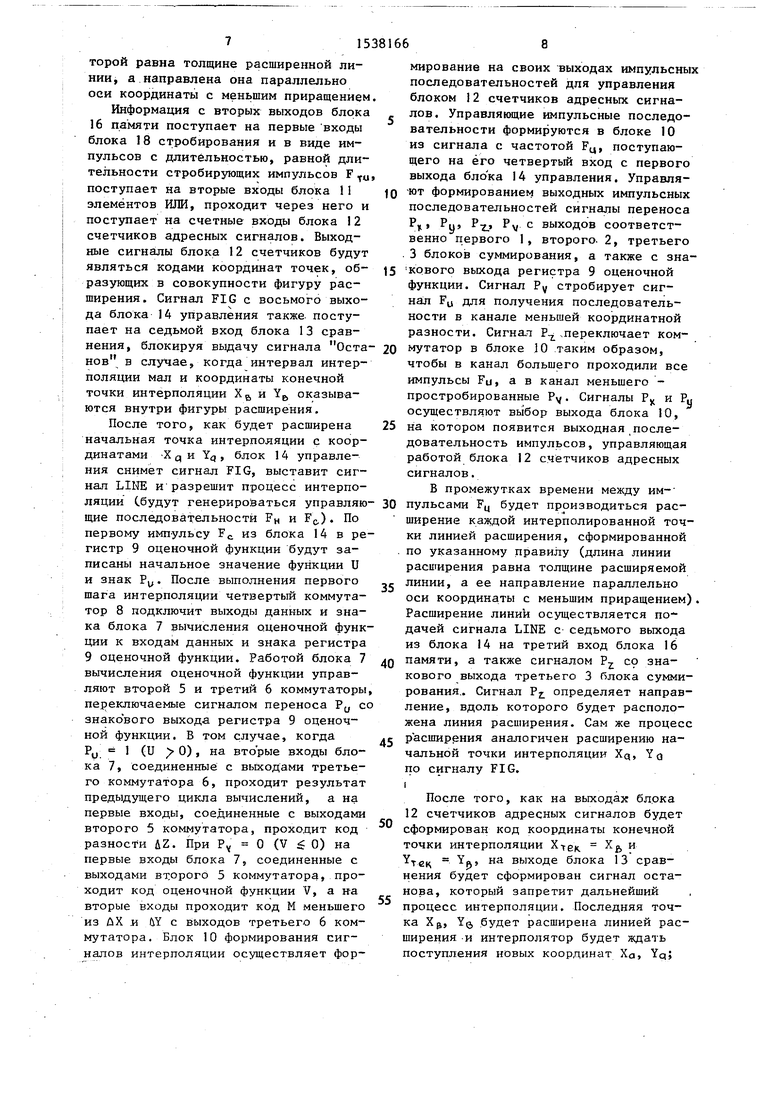

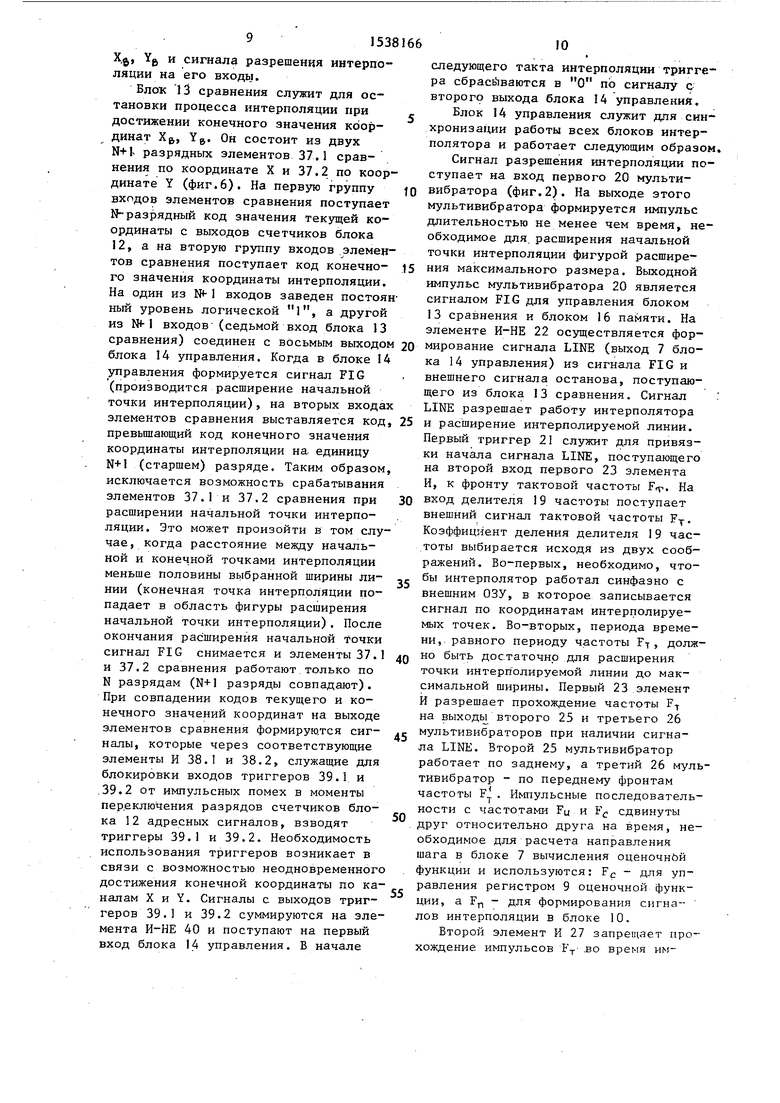

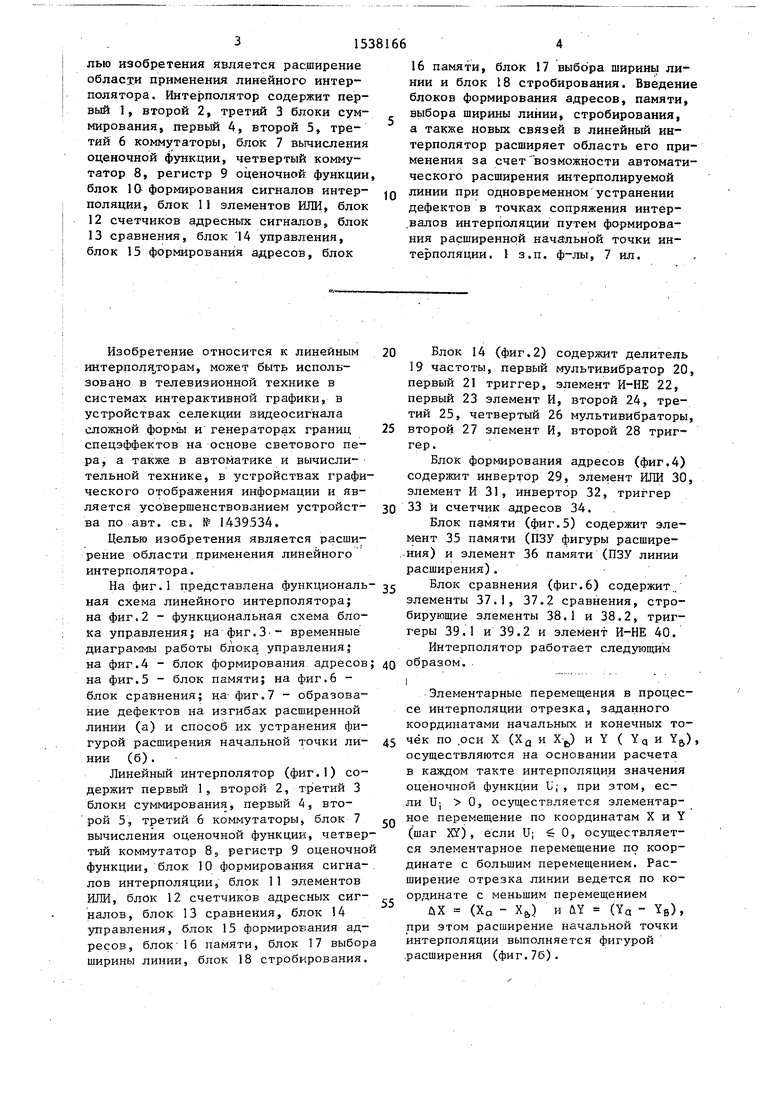

На фиг.1 представлена функциональ ная схема линейного интерполятора; на фиг.2 - функциональная схема блока управления; на фиг.З - временные диаграммы работы блока управления; на фиг.4 - блок формирования адресов на фиг.5 - блок памяти; на фиг.6 - блок сравнения; на фиг.7 - образование дефектов на изгибах расширенной линии (а) и способ их устранения фигурой расширения начальной точки ли-

НИИ (б).

Линейный интерполятор (фиг.1) содержит первый 1, второй 2, третий 3 блоки суммирования, первый 4, второй 5, третий 6 коммутаторы, блок 7 вычисления оценочной функции, четвертый коммутатор 89 регистр 9 оценочно функции, блок 10 формирования сигналов интерполяции, блок 11 элементов ИЛИ, блок 12 счетчиков адресных сиг- налов, блок 13 сравнения, блок 14 управления, блок 15 формирования адресов, блок 16 памяти, блок 17 выбор ширины линии, блок 18 стробирования.

16 памяти, блок 17 выбора ширины линии и блок 18 стробирования. Введение блоков формирования адресов, памяти, выбора ширины линии, стробирования, а также новых связей в линейный интерполятор расширяет область его применения за счет возможности автоматического расширения интерполируемой линии при одновременном устранении дефектов в точках сопряжения интервалов интерполяции путем формирования расширенной начальной точки интерполяции. 1 з.п. ф-лы, 7 ил.

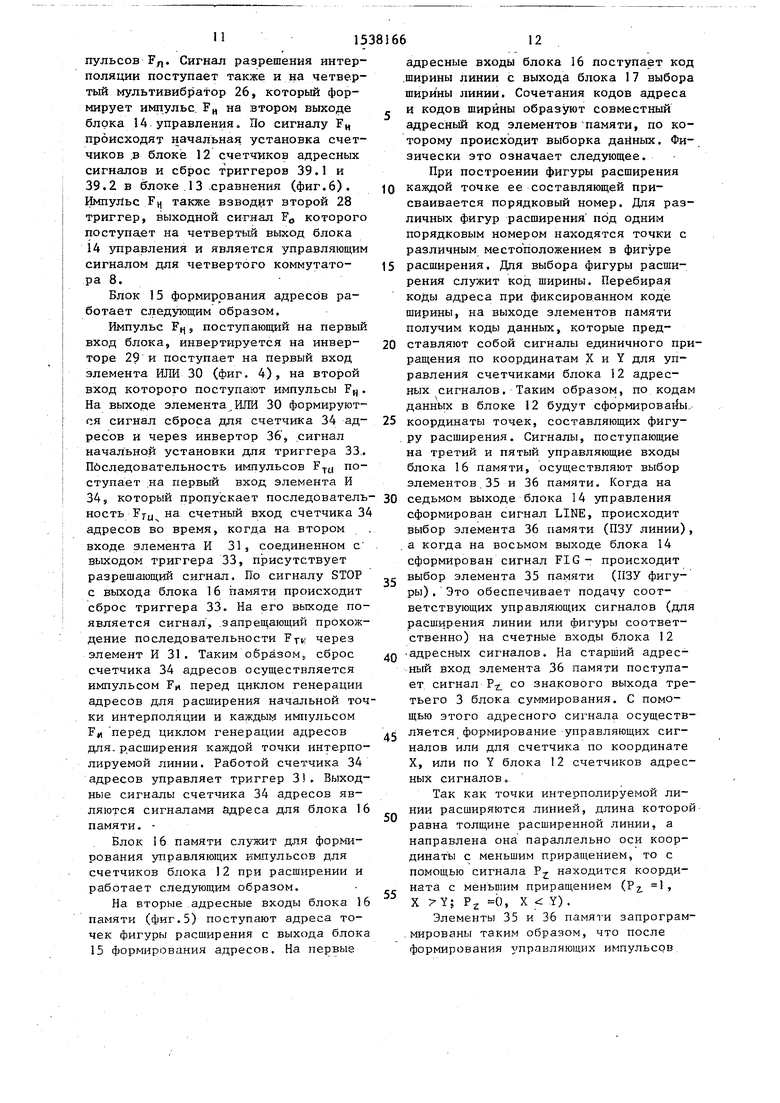

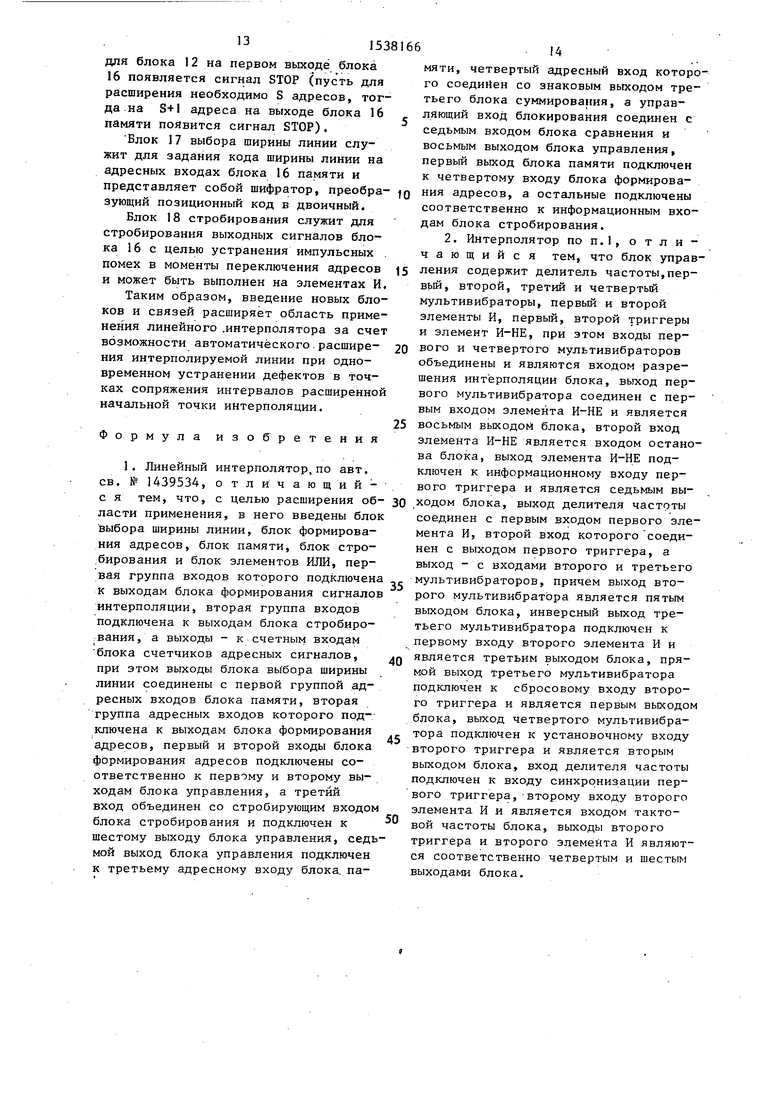

Блок 14 (фиг.2) содержит делитель 19 частоты, первый мультивибратор 20 первый 21 триггер, элемент И-НЕ 22, первый 23 элемент И, второй 24, третий 25, четвертый 26 мультивибраторы второй 27 элемент И, второй 28 триггер.

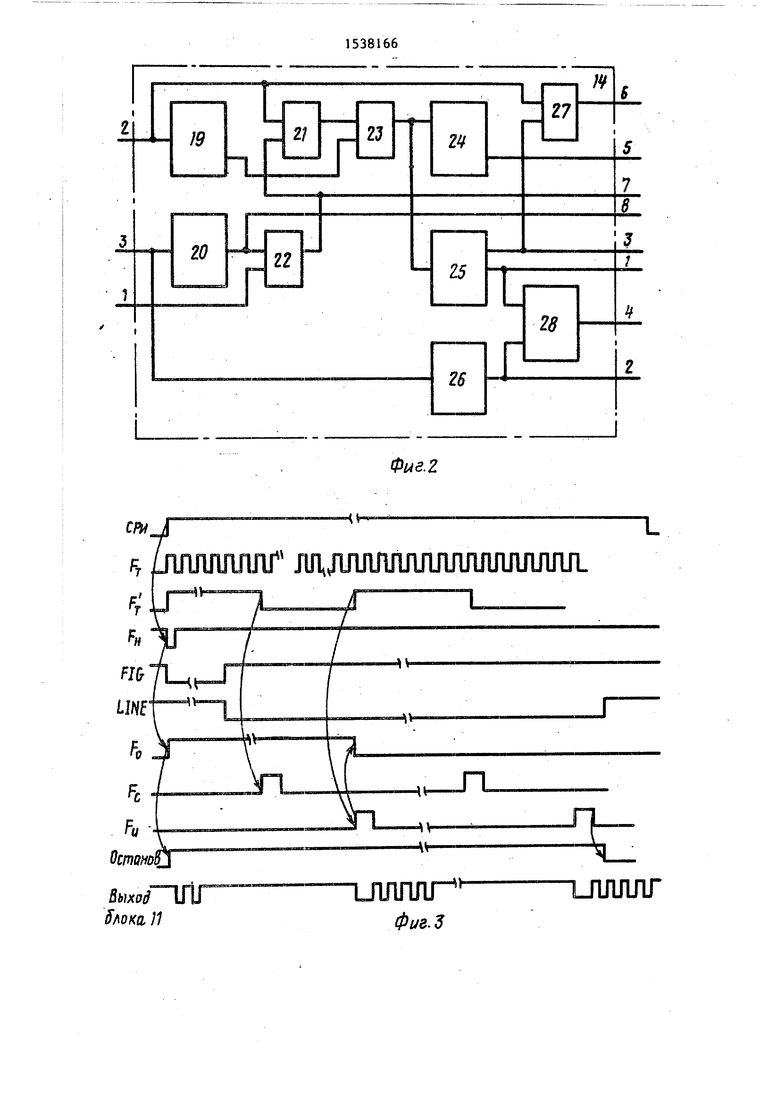

Блок формирования адресов (фиг.4) содержит инвертор 29, элемент ИЛИ 30 элемент И 31, инвертор 32, триггер 33 и счетчик адресов 34.

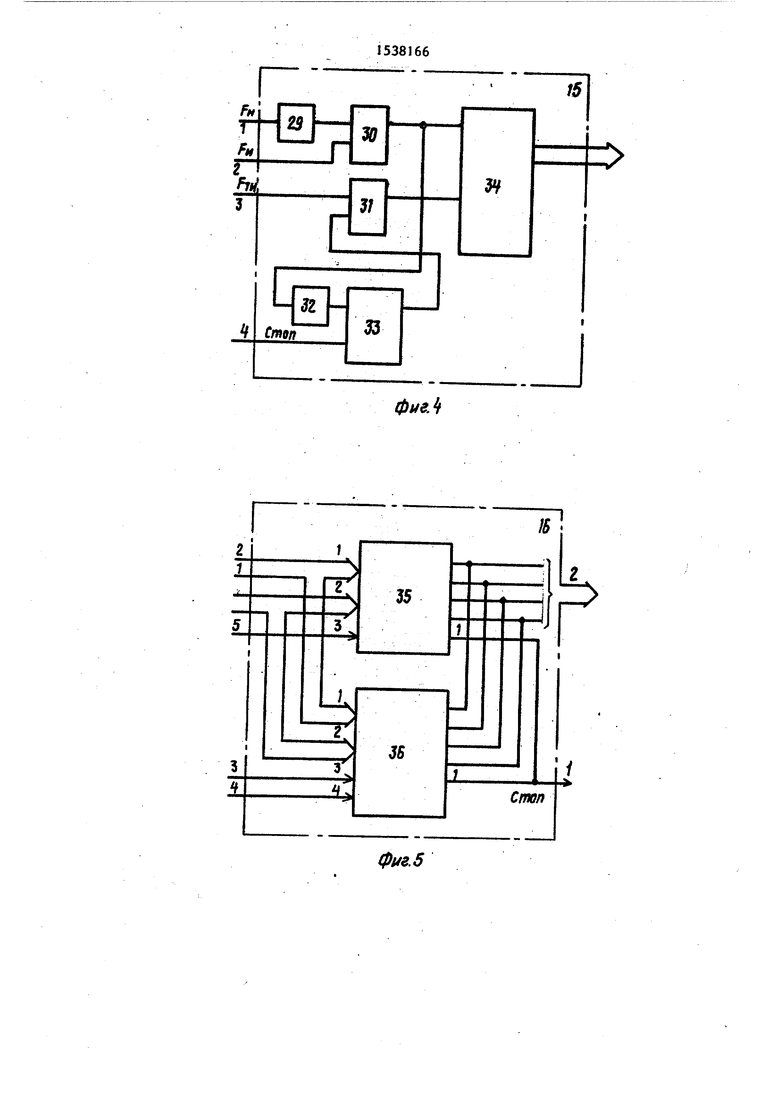

Блок памяти (фиг.5) содержит элемент 35 памяти (ПЗУ фигуры расширения) и элемент 36 памяти (ПЗУ линии расширения).

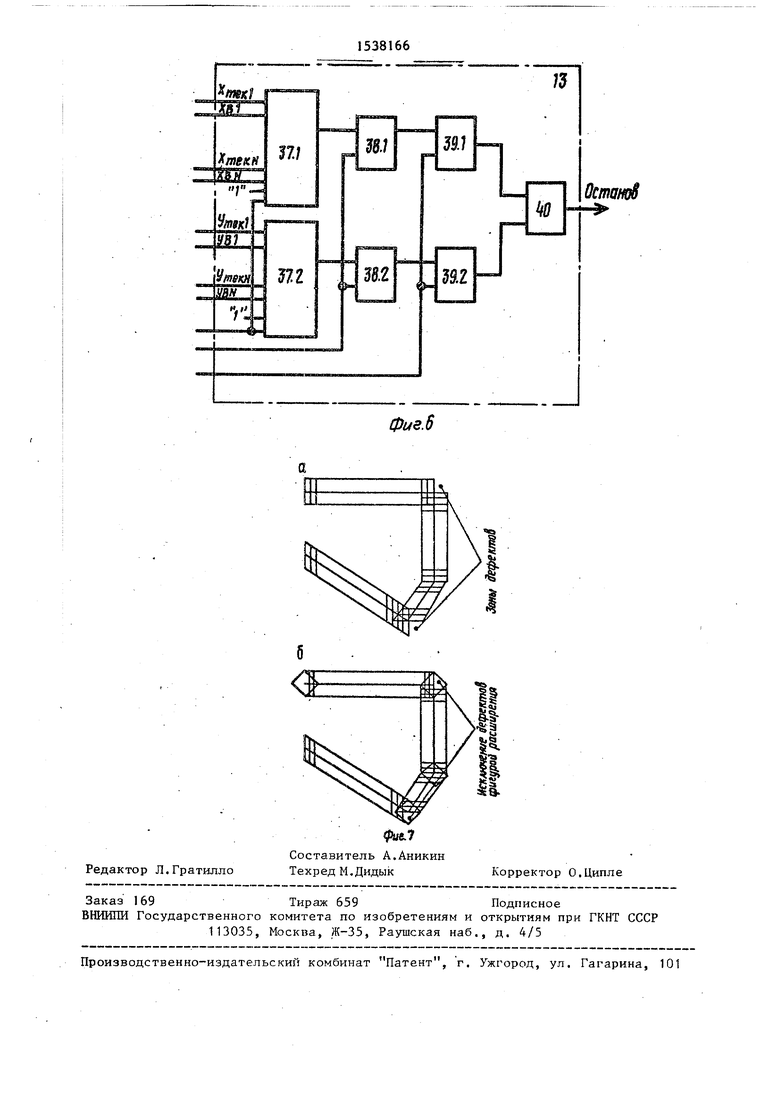

Блок сравнения (фиг.6) содержит, элементы 37.1, 37.2 сравнения, стро- бирующие элементы 38.1 и 38.2, триггеры 39.1 и 39.2 и элемент И-НЕ 40.

Интерполятор работает следующим образом.

I

Элементарные перемещения в процессе интерполяции отрезка, заданного координатами начальных и конечных точек по .оси X (Ха и Хь) и Y ( Yq и Yb осуществляются на основании расчета в каждом такте интерполяции значения оценочной функции Ь,, при этом, если Uj 0, осуществляется элементарное перемещение по координатам X и Y (шаг XY), если U; ё 0, осуществляется элементарное перемещение по координате с большим перемещением. Расширение отрезка линии ведется по координате с меньшим перемещением

йХ (Ха - Хь) и UY (Ya YB), при этом расширение начальной точки интерполяции выполняется фигурой расширения (фиг.76).

Перед выполнением первого шага интерполяции в первом 1 и втором 2 блоках суммирования происходит вычитание поступающих на их входы кодов начальных и конечных значений координат X и Y соответственно. На выходах данных первого 1 и второго 2 блоков суммирования выставляются значения разностей ДХ и &Y, на знаковых выходах - значения переносов Рц и Ру разностей. ЛХ и AY соответственно.Разности ДХ и дУ по координатам X и Y с выходов данных первого 1 и второго 2

блоков суммирования поступают «а вхо- jr При этом на вторые адресные входы

ды третьего блока 3 суммирования, осуществляющего операцию

Д2 ДХ - UY.

Одновременно, коды йХ и AY поступают на соответствующие входы первого коммутатора 4, который пропускает на выход меньшее (М) из ЛХ и &Y по сигналу переноса Р со знакового, выхода третьего блока 3 суммирования, вычисляющего значение &Z.

Четвертый коммутатор 8 предназначен для осуществления первого шага алгоритма интерполяции. В качестве начального значения оценочной функции V выбирается значение меньшего (М) из ДХ и Y, выставленное на выходе первого коммутатора 4. Знак Р„ для первого шага интерполяции вырабатывается в коммутаторе 8 в соответствии с правилом:

Р„ 0.

Дальнейшие значения оценочной функции рассчитываются следующим образом:

и-,., О (Ри - 1); U, - Ui-« -&Z;

и(и ё О (Pu 0); U, М - lUrll .

После поступления на вход блока 14 управления сигнала разрешения интерполяции (СРИ) на его втором выхоблока 16 памяти с выходов блока 15 формирования адресов поступают тек щие адреса точек фигуры расширения а на первые адресные входы блока I

20 с выхода блока 17 выбора ширины ли нии - постоянный для заданной шири линии код расширения. Блок 15 форм рования адресов производит последо тельную выборку адресов, по которы

25 в элементе 35 памяти зашиты коды расширения. В каждый момент времен коды адреса с выхода блока 15 и ко расширения с выхода блока 17 образ ют адрес, выбирающий из элемента 3

3Q памяти зашитую в него информацию направлении перехода от одной точк фигуры расширения к последующей. П ле выбора из элемента 35 памяти вс информации о данной (определенной дом расширения) фигуре расширения первом выходе блока 16 вырабатывае ся сигнал, блокирующий генерацию а ресов в блоке 15 формирования адре сов. Расширение точки интерполяции п сигналу FIG с блока 14 управления производится ромбом (фиг.7б). Выбо ромба в качестве фигуры расширения точки обусловлен тем, что наряду с

40

де формируется сигнал F, который за- простотой формирования он обеспечи50

писывает в блок 12 счетчиков адресных сигналов значения координат Ха и Ya начальной, точки интерполяции и сбрасывает триггеры 39.1 и 39.2 в блоке 13 сравнения. Одновременно на четвертом выходе блока 14 управления формируется сигнал F0, который подключает сигналы с выходов первого коммутатора 4, поступающие на вторые входы четвертого коммутатора 8, к входу данных регистра 9 оценочной функции. На знаковый вход регистра 9 поступает сигнал Р0, выработанный в соответствии с приведенным правилом.

вает достаточное качество устранени дефектов при изменении направления интерполируемой линии по сравнению с идеальной фигурой расширения - кр гом. Расширение линии в процессе ин терполяции осуществляется по сигналу LINE с седьмого выхода с блока 1 управления по информации, считываемой из элемента 36 памяти. Процесс считывания информации из элемента 3 памяти аналогичен описанному процес су считывания информации из элемент 35 памяти. Фигурой расширения в дан ном случае является линия, длина ко

1538166

Эти сигналы будут записаны в регистр 9 по сигналу Fc с пятого выхода блока 14 управления.

Таким образом, интерполятор полностью подготовлен к выполнению первого шага интерполяции. В то же время, на восьмом выходе блока 14 управления сформирован сигнал FIG, который блокирует генерацию управляющих последовательностей Fu и Fc в блоке 14, запрещая процесс интерподяции, и разрешает работу элемента 35 памяти (ПЗУ фигуры) в блоке 16 памяти.

r При этом на вторые адресные входы

блока 16 памяти с выходов блока 15 формирования адресов поступают текущие адреса точек фигуры расширения, а на первые адресные входы блока I6

0 с выхода блока 17 выбора ширины линии - постоянный для заданной ширины линии код расширения. Блок 15 формирования адресов производит последовательную выборку адресов, по которым

5 в элементе 35 памяти зашиты коды расширения. В каждый момент времени коды адреса с выхода блока 15 и код расширения с выхода блока 17 образуют адрес, выбирающий из элемента 35

Q памяти зашитую в него информацию о направлении перехода от одной точки фигуры расширения к последующей. После выбора из элемента 35 памяти всей информации о данной (определенной кодом расширения) фигуре расширения на первом выходе блока 16 вырабатывается сигнал, блокирующий генерацию адресов в блоке 15 формирования адресов. Расширение точки интерполяции по сигналу FIG с блока 14 управления производится ромбом (фиг.7б). Выбор ромба в качестве фигуры расширения точки обусловлен тем, что наряду с

0

0

вает достаточное качество устранения дефектов при изменении направления интерполируемой линии по сравнению с идеальной фигурой расширения - кругом. Расширение линии в процессе интерполяции осуществляется по сигналу LINE с седьмого выхода с блока 14 управления по информации, считываемой из элемента 36 памяти. Процесс считывания информации из элемента 36 памяти аналогичен описанному процессу считывания информации из элемента 35 памяти. Фигурой расширения в данном случае является линия, длина которой равна толщине расширенной пинии, а направлена она параллельно оси координаты с меньшим приращением

Информация с вторых выходов блока 16 памяти поступает на первые входы блока 18 стробирования и в виде импульсов с длительностью, равной длительности стробирующих импульсов FTO поступает на вторые входы блока 11 элементов ИЛИ, проходит через него и поступает на счетные входы блока 12 счетчиков адресных сигналов. Выходные сигналы блока 12 счетчиков будут являться кодами координат точек, об- разующих в совокупности фигуру расширения. Сигнал FIG с восьмого выхода блока 14 управления также поступает на седьмой вход блока 13 сравнения, блокируя выдачу сигнала Оста нов в случае, когда интервал интерполяции мал и координаты конечной точки интерполяции Хь и YB оказываются внутри фигуры расширения.

После того, как будет расширена начальная точка интерполяции с координатами -X д и Yq , блок 14 управления снимет сигнал FIG, выставит сигнал LINE и разрешит процесс интерполяции Сбудут генерироваться управляю щие последовательности FH и FC,). По первому импульсу Fc из блока 14 в регистр 9 оценочной функции будут записаны начальное значение функции U

и знак Ри. После выполнения первого шага интерполяции четвертый коммутатор 8 подключит выходы данных и знака блока 7 вычисления оценочной функции к входам данных и знака регистра 9 оценочной функции. Работой блока 7 вычисления оценочной функции управляют второй 5 и третий 6 коммутаторы переключаемые сигналом переноса Ри с знако вого выхода регистра 9 оценочной функции. В том случае, когда Рд 1 (U 0), на вторые входы блока 7, соединенные с выходами третьего коммутатора 6, проходит результат предыдущего цикла вычислений, а на первые входы, соединенные с выходами второго 5 коммутатора, проходит код разности UZ. При Ру О (V 0) на первые входы блока 7, соединенные с выходами второго 5 коммутатора, проходит код оценочной функции V, а на вторые входы проходит код М меньшего из UX JH UY с выходов третьего 6 коммутатора. Блок 10 формирования сигналов интерполяции осуществляет форQ$ 0

5 0

5

0

5

0

5

мирование на своих выходах импульсных последовательностей для управления блоком 12 счетчиков адресных сигналов. Управляющие импульсные последовательности формируются в блоке 10 из сигнала с частотой Рц, поступающего на его четвертьй вход с первого выхода бло ка 14 управления. Управляют формированием выходных импульсных последовательностей сигналы переноса PI, Ру, Р, Pv с выходов соответственно первого 1, второго. 2, третьего 3 блоков суммирования, а также с знакового выхода регистра 9 оценочной функции. Сигнал Pv стробирует сигнал Гц для получения последовательности в канале меньшей координатной разности. Сигнал Рт .переключает коммутатор в блоке 10 таким образом, чтобы в канал большего проходили все импульсы FO, а в канал меньшего - простробированные Ру. Сигналы Рх и Р„ осуществляют выбор выхода блока 10, на котором появится выходная последовательность импульсов, управляющая работой блока 12 счетчиков адресных сигналов.

В промежутках времени между им- пульсами FH будет производиться расширение каждой интерполированной точки линией расширения, сформированной по указанному правилу (длина линии расширения равна толщине расширяемой линии, а ее направление параллельно оси координаты с меньшим приращением). Расширение линий осуществляется подачей сигнала LINE с седьмого выхода из блока 14 на третий вход блока 16 памяти, а также сигналом 7г со знакового выхода третьего 3 блока суммирования . Сигнал РЈ определяет направление, вдоль которого будет расположена линия расширения. Сам же процесс расширения аналогичен расширению начальной точки интерполяции Xq, YQ по сигналу FIG. i

После того, как на выходах блока 12 счетчиков адресных сигналов будет сформирован код координаты конечной точки интерполяции Хтек Хь и тек в на вых°Де блока 13 сравнения будет сформирован сигнал останова, который запретит дальнейший процесс интерполяции. Последняя точка Х&, YU будет расширена линией расширения и интерполятор будет ждать поступления новых координат Ха, Yq;

X,ft, Yft и сигнала разрешения интерполяции на его входы.

Блок 13 сравнения служит для остановки процесса интерполяции при достижении конечного значения координат Х6, YB. Он состоит из двух N+1 разрядных элементов 37.1 сравнения по координате X и 37.2 по координате Y (фиг.6). На первую группу входов элементов сравнения поступает N разрядный код значения текущей координаты с выходов счетчиков блока 12, а на вторую группу входов элементов сравнения поступает код конечного значения координаты интерполяции. На один из № 1 входов заведен постоянный уровень логической 1, а другой из №-1 входов (седьмой вход блока 13 сравнения) соединен с восьмым выходом блока 14 управления. Когда в блоке 14 управления формируется сигнал FIG (производится расширение начальной точки интерполяции), на вторых входах элементов сравнения выставляется код, превышающий код конечного значения координаты интерполяции на единицу N+1 (старшем) разряде. Таким образом, исключается возможность срабатывания элементов 37.1 и 37.2 сравнения при расширении начальной точки интерполяции. Это может произойти в том случае, когда расстояние между начальной и конечной точками интерполяции меньше половины выбранной ширины линии (конечная точка интерполяции попадает в область фигуры расширения начальной точки интерполяции). После окончания расширения начальной точки сигнал FIG снимается и элементы 37.1 и 37.2 сравнения работают только по N разрядам (N+1 разряды совпадают). При совпадении кодов текущего и конечного значений координат на выходе элементов сравнения формируются сигналы, которые через соответствующие элементы И 38.1 и 38.2, служащие для блокировки входов триггеров 39.1 и 39.2 от импульсных помех в моменты переключения разрядов счетчиков блока 12 адресных сигналов, взводят триггеры 39.1 и 39.2. Необходимость использования триггеров возникает в связи с возможностью неодновременного достижения конечной координаты по каналам X и Y. Сигналы с выходов триггеров 39.1 и 39.2 суммируются на элемента И-НЕ 40 и поступают на первый вход блока 14 управления. В начале

10

15

20

25

166JO

следующего такта интерполяции триггера сбрасываются в О по сигналу с второго выхода блока 14 управления.

Блок 14 управления служит для синхронизации работы всех блоков интерполятора и работает следующим образом.

Сигнал разрешения интерполяции поступает на вход первого 20 мультивибратора (фиг.2). На выходе этого мультивибратора формируется импульс длительностью не менее чем время, необходимое для расширения начальной точки интерполяции фигурой расширения максимального размера. Выходной импульс мультивибратора 20 является сигналом FIG для управления блоком 13 сравнения и блоком 16 памяти. На элементе И-НЕ 22 осуществляется формирование сигнала LINE (выход 7 блока 14 управления) из сигнала FIG и внешнего сигнала останова, поступающего из блока 13 сравнения. Сигнал LINE разрешает работу интерполятора и расширение интерполируемой линии. Первый триггер 21 служит для привязки начала сигнала LINE, поступающего на второй вход первого 23 элемента И, к фронту тактовой частоты Fv. На вход делителя 19 частоты поступает внешний сигнал тактовой частоты FT. Коэффициент деления делителя 19 частоты выбирается исходя из двух соображений. Во-первых, необходимо, чтобы интерполятор работал синфазно с внешним ОЗУ, в которое записывается сигнал по координатам интерполируемых точек. Во-вторых, периода времени, равного периоду частоты Ff, должно быть достаточно для расширения точки интерполируемой линии до максимальной ширины. Первый 23 элемент И разрешает прохождение частоты FT на выходы второго 25 и третьего 26 мультивибраторов при наличии сигнала LINE. Второй 25 мультивибратор работает по заднему, а третий 26 мультивибратор - по переднему фронтам частоты F . Импульсные последовательности с частотами Fu и Fc сдвинуты друг относительно друга на время, необходимое для расчета направления шага в блоке 7 вычисления оценочной функции и используются: Fc - для управления регистром 9 оценочной функции, a Fn - для формирования сигналов интерполяции в блоке 10.

Второй элемент И 27 запрещает прохождение импульсов FT во время им30

35

40

45

50

55

1115

пульсов Fn. Сигнал разрешения интерполяции поступает также и на четвертый мультивибратор 26, который формирует импульс FH на втором выходе блока 14 управления. По сигналу FH происходят начальная установка счетчиков в блоке 12 счетчиков адресных сигналов и сброс триггеров 39.1 и 39.2 в блоке 13 сравнения (фиг.6). Импульс FH также взводит второй 28

триггер, выходной сигнал F0 которого поступает на четвертый выход блока

14управления и является управляющим сигналом для четвертого коммутатора 8.

Блок 15 формирования адресов работает следующим образом.

Импульс F4, поступающий на первый вход блока, инвертируется на инверторе 29 и поступает на первый вход элемента ИЛИ 30 (фиг. 4), на второй вход которого поступают импульсы FH. На выходе элемента ИЛИ 30 формируются сигнал сброса для счетчика 34 адресов и через инвертор 36, сигнал начальной установки для триггера 33. Последовательность импульсов FTt) поступает на первый вход элемента И 34, который пропускает последовательность FTu на счетный вход счетчика 34 адресов во время, когда на втором входе элемента И 31, соединенном с выходом триггера 33, присутствует разрешающий сигнал. По сигналу STOP с выхода блока 16 памяти происходит сброс триггера 33. На его выходе появляется сигнал, запрещающий прохождение последовательности Fft, через элемент И 31 . Таким образом,, сброс счетчика 34 адресов осуществляется импульсом FH перед циклом генерации адресов для расширения начальной точки интерполяции и каждым импульсом Р„ перед циклом генерации адресов для расширения каждой точки интерполируемой линии. Работой счетчика 34 адресов управляет триггер 3. Выходные сигналы счетчика 34 адресов являются сигналами адреса для блока 16 памяти. Блок 16 памяти служит для формирования управляющих ьмпульсов для счетчиков блока 12 при расширении и работает следующим образом.

На вторые адресные входы блока 16 памяти (фиг.5) поступают адреса точек фигуры расширения с выхода блока

15формирования адресов. На первые

12

g

5

0

5

0

5

0

5

0

5

адресные входы блока 16 поступает код ширины линии с выхода блока 17 выбора ширины линии. Сочетания кодов адреса и кодов ширины образуют совместный адресный код элементов памяти, по которому происходит выборка данных. Физически это означает следующее.

При построении фигуры расширения каждой точке ее составляющей присваивается порядковый номер. Для различных фигур расширения под одним порядковым номером находятся точки с различным местоположением в фигуре расширения. Для выбора фигуры расширения служит код ширины. Перебирая коды адреса при фиксированном коде ширины, на выходе элементов памяти получим коды данных, которые представляют собой сигналы единичного приращения по координатам X и Y для управления счетчиками блока 12 адресных сигналов. Таким образом, по кодам данных в блоке 12 будут сформированы координаты точек, составляющих фигуру расширения. Сигналы, поступающие на третий и пятый управляющие входы блока 16 памяти, осуществляют выбор элементов 35 и 36 памяти. Когда на седьмом выходе блока 14 управления сформирован сигнал LINE, происходит выбор элемента 36 памяти (ПЗУ линии), а когда на восьмом выходе блока 14 сформирован сигнал FIG - происходит выбор элемента 35 памяти (ПЗУ фигуры) . Это обеспечивает подачу соответствующих управляющих сигналов (для расширения линии или фигуры соответственно) на счетные входы блока 12 адресных сигналов. На старший адресный вход элемента 36 памяти поступает сигнал Р- со знакового выхода третьего 3 блока суммирования. С помощью этого адресного сигнала осуществляется формирование управляющих сигналов или для счетчика по координате X, или по Y блока 12 счетчиков адресных сигналов.

Так как точки интерполируемой линии расширяются линией, длина которой равна толщине расширенной линии, а направлена она параллельно оси координаты с меньшим приращением, то с помощью сигнала Рг находится координата с меньшим приращением (Рг X -Ґ; Pz 0, X Y).

Элементы 35 и 36 памяти запрограммированы таким обрачом, что после формирования управляющих импульсов

13

для блока 12 на первом выходе блока 16 появляется сигнал STOP (пусть для расширения необходимо S адресов, тогда на S-H адреса на выходе блока 16 памяти появится сигнал STOP).

Блок 17 выбора ширины линии служит для задания кода ширины линии на адресных входах блока 16 памяти и

1538

15

представляет собой шифратор, преобра- JQ ния адресов, а остальные подключены зующий позиционный код в двоичный.

Блок 18 стробирования служит для стробирования выходных сигналов блока 16 с целью устранения импульсных помех в моменты переключения адресов и может быть выполнен на элементах И.

Таким образом, введение новых блоков и связей расширяет область применения линейного .интерполятора за счет возможности автоматического расширения интерполируемой линии при одновременном устранении дефектов в точках сопряжения интервалов расширенной начальной точки интерполяции.

соответственно к информационным входам блока стробирования.

ласти применения, в него введены блок выбора ширины линии, блок формирования адресов, блок памяти, блок стробирования и блок элементов ИЛИ, первая группа входов которого подключена к выходам блока формирования сигналов интерполяции, вторая группа входов подключена к выходам блока стробирования, а выходы - к счетным входам блока счетчиков адресных сигналов, при этом выходы блока выбора ширины линии соединены с первой группой адресных входов блока памяти, вторая группа адресных входов которого подключена к выходам блока формирования адресов, первый и второй входы блока формирования адресов подключены соответственно к первому и второму выходам блока управления, а третий вход объединен со стробирующим входом блока стробирования и подключен к шестому выходу блока управления, седьмой выход блока управления подключен к третьему адресному входу блока, па

8166|4

мяти, четвертый адресный вход которого соедийен со знаковым выходом третьего блока суммирования, а управляющий вход блокирования соединен с седьмым входом блока сравнения и восьмым выходом блока управления, первый выход блока памяти подключен к четвертому входу блока формирова

ния адресов, а остальные подключены

соответственно к информационным входам блока стробирования.

.ходом блока, выход делителя частоты

5

0

5

0

соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, а выход - с входами второго и третьего мультивибраторов, причем выход второго мультивибратора является пятым выходом блока, инверсный выход третьего мультивибратора подключен к первому входу второго элемента И и является третьим выходом блока, прямой выход третьего мультивибратора подключен к сбросовому входу второго триггера и является первым выходом блока, выход четвертого мультивибратора подключен к установочному входу второго триггера и является вторым выходом блока, вход делителя частоты подключен к входу синхронизации первого триггера, второму входу второго элемента И и является входом тактовой частоты блока, выходы второго триггера и второго элемента И являются соответственно четвертым и шестым выходами блока.

-tVWU L

Fr ШШЛЛЛЛГ ЛП,ДПЛ1ЩП ШПЯШШЛШи1

OcmoHuQ

ВыхоГ М Г

&AOKQ, 11

Фие.г

Фиг.З

тллллг

1

я

- 22LJ

Утш

H3IL

т

и

OcmamS

т

т

фие.6

Ј1

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-01-23—Публикация

1988-04-12—Подача