Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения.

В современной микроэлектронике широко используются дифференциальные операционные усилители (ОУ), реализованные на основе так называемых «перегнутых» каскодов [1-11]. При малых напряжениях питания  и жестких ограничениях на диапазон изменения выходного напряжения, который должен быть как можно более близким к сумме

и жестких ограничениях на диапазон изменения выходного напряжения, который должен быть как можно более близким к сумме  , в известных ОУ коэффициент усиления по напряжению (Ку) получается небольшим. В значительной степени это связано с шунтирующим влиянием на Ку выходного сопротивления классического источника опорного тока, связанного с высокоимпедансным узлом схемы ОУ.

, в известных ОУ коэффициент усиления по напряжению (Ку) получается небольшим. В значительной степени это связано с шунтирующим влиянием на Ку выходного сопротивления классического источника опорного тока, связанного с высокоимпедансным узлом схемы ОУ.

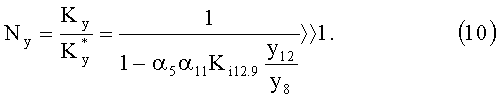

Ближайшим прототипом заявляемого устройства является классический операционный усилитель на основе «перегнутого» каскода, представленный в патенте US 3.569.848, fig.7-A1. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого связана с первой 4 шиной источника питания, первый 5 выходной транзистор, база которого соединена с источником вспомогательного напряжения 6, коллектор соединен со входом буферного усилителя 7 и через токостабилизирующий двухполюсник 8 соединен с первой 4 шиной источника питания, токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого связан со вторым 2 токовым выходом входного дифференциального каскада 1, а выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1 и эмиттеру первого 5 выходного транзистора.

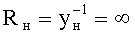

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно высокий предельный коэффициент усиления по напряжению (Ку), который измеряется при сопротивлении нагрузки  .

.

Основная задача предлагаемого изобретения состоит в повышении предельного коэффициента усиления по напряжению Ку.

Поставленная задача решается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого связана с первой 4 шиной источника питания, первый 5 выходной транзистор, база которого соединена с источником вспомогательного напряжения 6, коллектор соединен со входом буферного усилителя 7 и через токостабилизирующий двухполюсник 8 соединен с первой 4 шиной источника питания, токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого связан со вторым 2 токовым выходом входного дифференциального каскада 1, а выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1 и эмиттеру первого 5 выходного транзистора, предусмотрены новые элементы и связи - в схему введен первый 11 дополнительный транзистор, эмиттер которого связан по переменному току с первой 4 шиной источника питания через дополнительный 12 токостабилизирующий двухполюсник, коллектор подключен ко входу токового зеркала 9, а база связана по переменному току с выходом буферного усилителя 7.

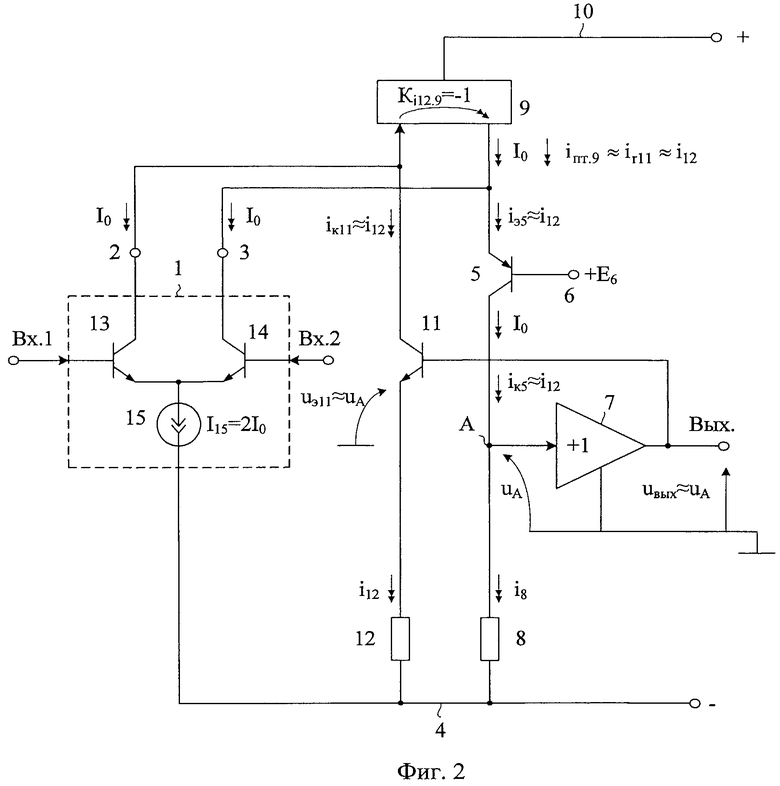

На фиг.1 представлена схема ДУ-прототипа. Схема заявляемого устройства в соответствии с формулой изобретения показана на фиг.2.

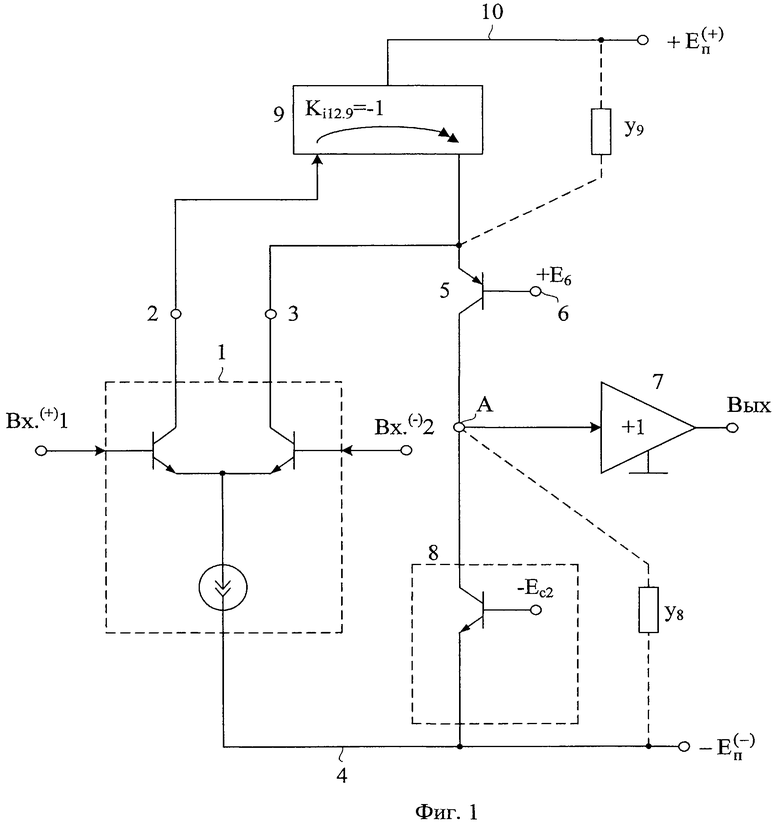

На фиг.3 показан заявляемый ДУ с частным вариантом построения токостабилизирующих двухполюсников 8 и 12, которые реализуются здесь на транзисторах 17 и 16 и элементах цепи смещения 18 и 19.

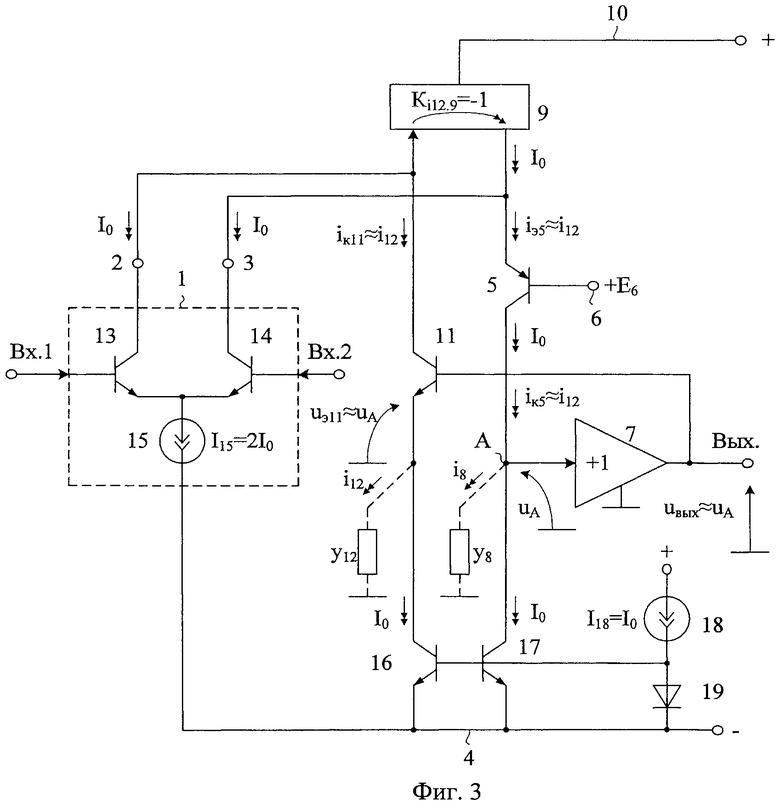

На фиг.4 представлена схема фиг.3 с конкретным выполнением буферного усилителя 7.

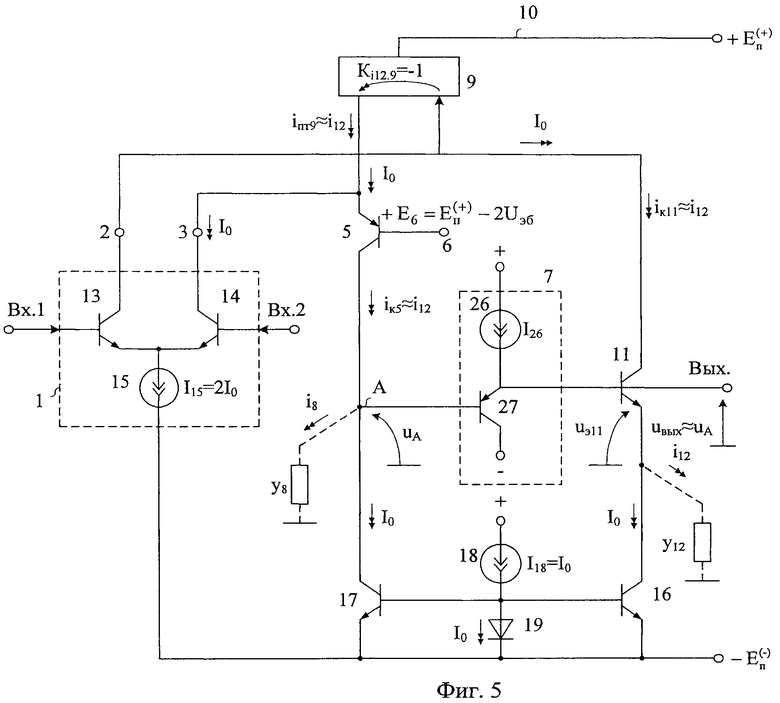

На фиг.5 представлена схема ДУ фиг.3, в котором буферный усилитель 7 реализован на основе транзистора 27 и источника опорного тока 26.

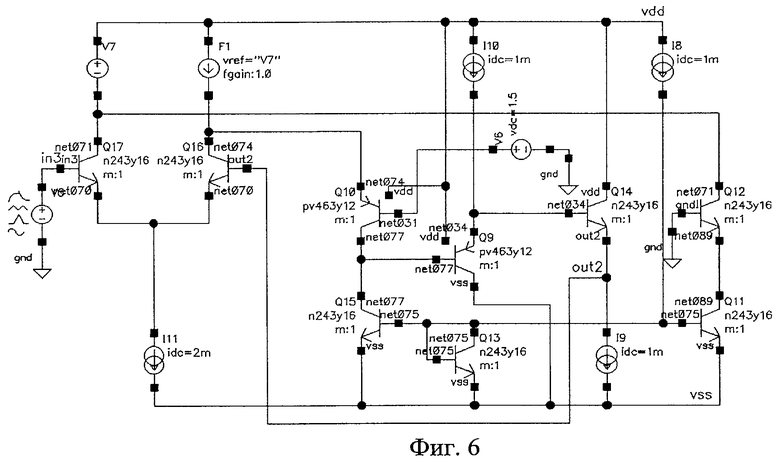

На фиг.6 показана схема ДУ-прототипа в среде Cadence на моделях интегральных транзисторов ФГУП НПП «Пульсар».

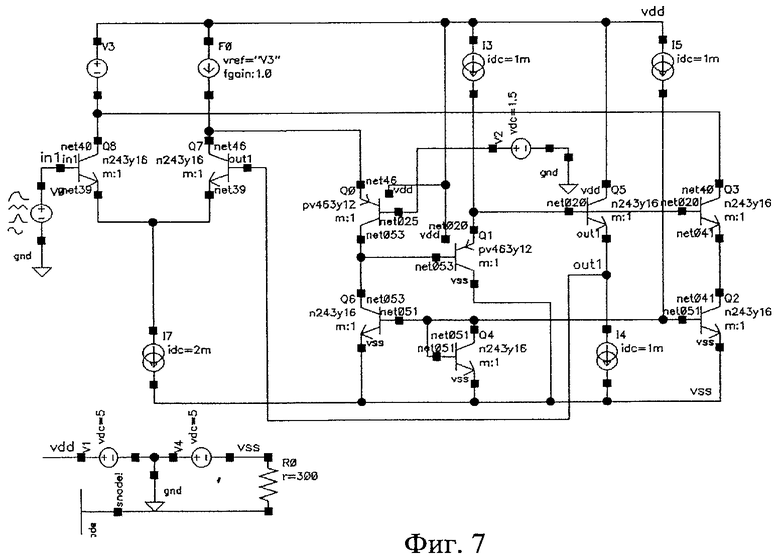

На фиг.7 представлена схема предлагаемого ДУ в среде Cadence на моделях ФГУП НПП «Пульсар».

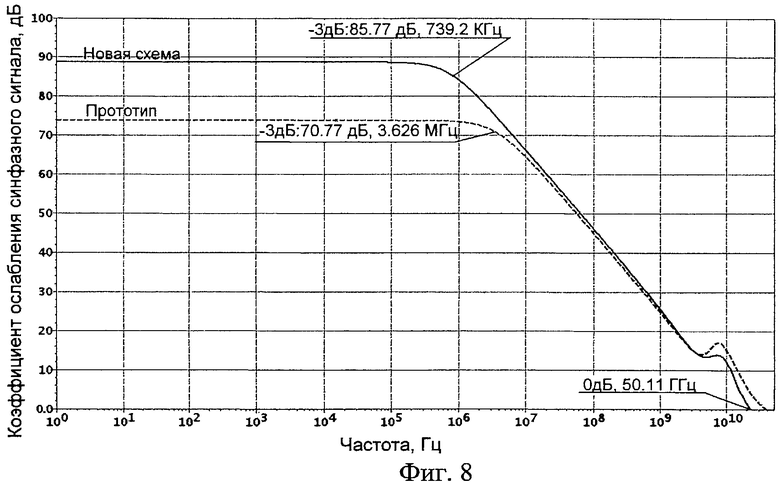

На фиг.8 показана логарифмическая амплитудно-частотная характеристика коэффициента усиления по напряжению сравниваемых схем фиг.6 и фиг.7.

Каскодный дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого связана с первой 4 шиной источника питания, первый 5 выходной транзистор, база которого соединена с источником вспомогательного напряжения 6, коллектор соединен со входом буферного усилителя 7 и через токостабилизирующий двухполюсник 8 соединен с первой 4 шиной источника питания, токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого связан со вторым 2 токовым выходом входного дифференциального каскада 1, а выход подключен ко второму 3 токовому выходу входного дифференциального каскада 1 и эмиттеру первого 5 выходного транзистора. В схему введен первый 11 дополнительный транзистор, эмиттер которого связан по переменному току с первой 4 шиной источника питания через дополнительный 12 токостабилизирующий двухполюсник, коллектор подключен ко входу токового зеркала 9, а база связана по переменному току с выходом буферного усилителя 7.

В схеме фиг.2 входной дифференциальный каскад реализован на входных транзисторах 13, 14 и источнике тока 15.

В схемах ДУ фиг.3, фиг.4, фиг.5 токостабилизирующие двухполюсники 12 и 8 реализованы соответственно на транзисторах 16 и 17, статический режим которых устанавливается цепью смещения на основе p-n перехода 19 и источника тока 18.

Кроме этого, в ДУ фиг.4 буферный усилитель 7 реализован на основе так называемых комплементарных «бриллиантовых» эмиттерных повторителей, которые содержат биполярные транзисторы 20, 21, 22, 23 и источники опорного тока 24, 25.

В частном случае в ДУ фиг.5 буферный усилитель 7 содержит входной транзистор 27 и источник опорного тока 26.

Эмиттеры У 8 и У 12 в схемах фиг.4, фиг.5 модернизируют выходные проводимости токостабилизирующих двухполюсников 8 и 12 при их реализации на транзисторах.

Рассмотрим работу заявляемого ДУ фиг.2.

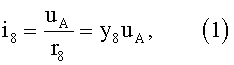

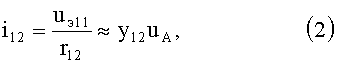

Изменение напряжения uA в высокоимпедансном узле «А» вызывает, с одной стороны, приращение тока i8 через двухполюсник 8, а с другой - изменение тока i12 через двухполюсник 12

где  ,

,  - дифференциальное сопротивления двухполюсников 8 и 12;

- дифференциальное сопротивления двухполюсников 8 и 12;

uэ11=uвых≈uA - приращение напряжения на двухполюснике 12.

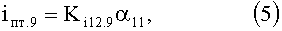

Приращение тока i12 поступает в эмиттер (iэ11), а затем коллектор (iк11) транзистора 11, и далее на вход и выход (iпт.9) токового зеркала 9:

где α11≈1 - коэффициент усиления по току эмиттера транзистора 11;

Кi12.9=1 - коэффициент усиления по току токового зеркала 9.

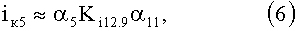

Поэтому коллекторный ток транзистора 5

где α5≈1 - коэффициент усиления по току эмиттера транзистора 5.

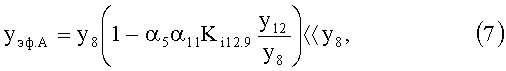

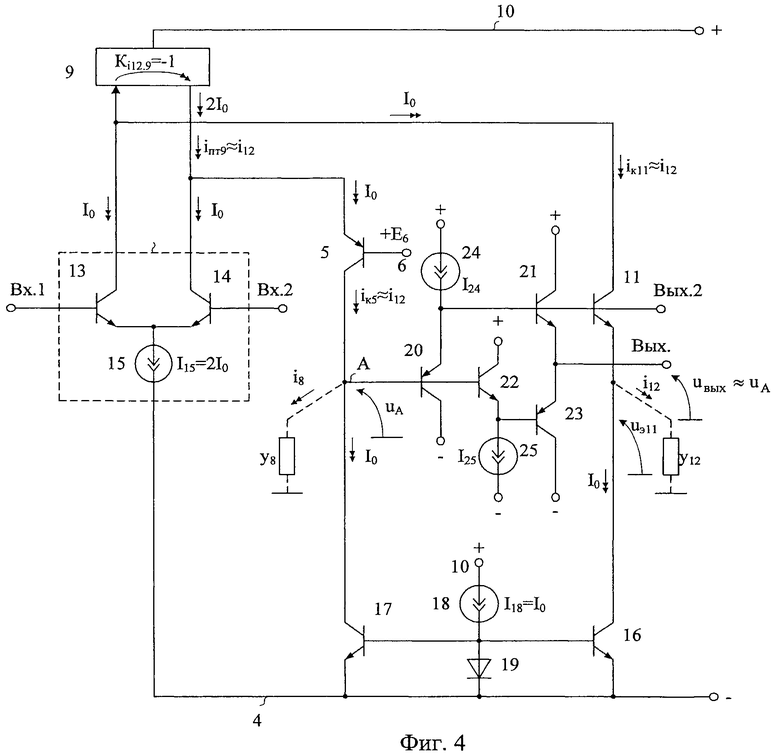

Как следствие, эффективная проводимость в узле «А» (уэф.А) существенно уменьшается, а коэффициент усиления по напряжению (Ку) предлагаемого ДУ возрастает:

где S - крутизна усиления со входа ДУ к узлу «А».

В ДУ-прототипе:

Поэтому заявляемый ОУ имеет более высокий (в Nу-раз) коэффициент усиления по напряжению:

Если учесть, что α5≈1, α11≈1, Кi12.9≈1, у12≈у8, то реальный выигрыш по Ку может достигать одного-двух порядков, что подтверждают результаты компьютерного моделирования фиг.8.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.569.8486 fig.7-A1.

2. Патент США №3.972.004, fig.3.

3. Патент США №4.511/857, fig.1.

4. Патент США №7.605.658, fig.5.

5. Патентная заявка США №2010/0271127, fig.1.

6. Патент США №4.406.990, fig.6.

7. Патент США №3.644.838, fig.1.

8. Патент США №4.959.622, fig.1b.

9. Патент США №6.448.853, fig.7.

10. Патент США №5.734.296, fig.3.

11. Патент США №6.483.382, fig.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2455756C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ И ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2010 |

|

RU2426221C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ВЫСОКОЧАСТОТНОЙ КОРРЕКЦИЕЙ | 2010 |

|

RU2423778C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2469465C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416146C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат - повышение предельного коэффициента усиления по напряжению Ку. Каскодный дифференциальный усилитель содержит входной дифференциальный каскад, первый выходной транзистор, токовое зеркало, первый дополнительный транзистор, первый токостабилизирующий двухполюсник, дополнительный токостабилизирующий двухполюсник, буферный усилитель. 8 ил.

Каскодный дифференциальный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, общая эмиттерная цепь которого связана с первой (4) шиной источника питания, первый (5) выходной транзистор, база которого соединена с источником вспомогательного напряжения (6), коллектор соединен со входом буферного усилителя (7) и через токостабилизирующий двухполюсник (8) соединен с первой (4) шиной источника питания, токовое зеркало (9), согласованное со второй (10) шиной источника питания, вход которого связан со вторым (2) токовым выходом входного дифференциального каскада (1), а выход подключен ко второму (3) токовому выходу входного дифференциального каскада (1) и эмиттеру первого (5) выходного транзистора, отличающийся тем, что в схему введен первый (11) дополнительный транзистор, эмиттер которого связан по переменному току с первой (4) шиной источника питания через дополнительный (12) токостабилизирующий двухполюсник, коллектор подключен ко входу токового зеркала (9), а база связана по переменному току с выходом буферного усилителя (7).

| US 6590452 В1, 08.07.2003 | |||

| US 3569848 А, 09.03.1971 | |||

| 0 |

|

SU295221A1 | |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

Авторы

Даты

2012-07-10—Публикация

2011-04-01—Подача