Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, драйверах дифференциальных линий связи, фильтрах, компараторах т.п.).

Известны схемы классических каскодных дифференциальных усилителей на n-р-n и р-n-р транзисторах (ДУ), которые стали основой многих серийных аналоговых микросхем [1-12]. ДУ данного класса широко применяются в структуре СВЧ-устройств [15-16], реализованных на базе SiGe-технологий. При этом при использовании симметричного выхода в ДУ (см., например, патенты US 4.600.893 и 4.406.990, fig.3 и др.) открываются большие перспективы построения на его основе фазорасщепителей однофазных сигналов (так называемых балунов (bulun), мостовых усилителей мощности и т.п.). В ряде важных для практики случаев симметричный (или парафазный) выход реализуется на основе резисторов (двухполюсников коллекторной нагрузки) [13, 14] или других неуправляемых источников опорного тока.

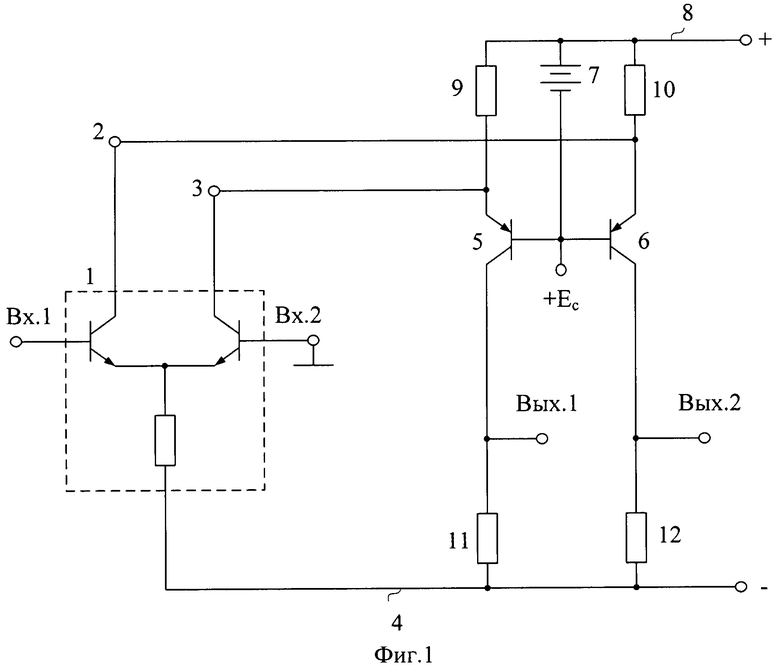

Ближайшим прототипом (фиг.1) заявляемого устройства является патент US №4.600.893, fig.5 фирмы Toshiba JP, который имеет резистивные двухполюсники коллекторной нагрузки. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого соединена с первым 4 источником питания, первый 5 и второй 6 выходные транзисторы с объединенными базами, цепь смещения 7, связанная с объединенными базами первого 5 и второго 6 выходных транзисторов, первый 9 вспомогательный резистор, включенный между вторым 8 источником питания и эмиттером первого 5 выходного транзистора, связанным со вторым 3 токовым выходом входного дифференциального каскада 1, второй 10 вспомогательный резистор, включенный между вторым 8 источником питания и эмиттером второго 6 выходного транзистора, связанным с первым 2 токовым выходом входного дифференциального каскада 1, первый 11 двухполюсник нагрузки, включенный между коллектором первого 5 выходного транзистора и первым 4 источником питания, второй 12 двухполюсник нагрузки, включенный между коллектором второго 6 выходного транзистора и первым 4 источником питания.

Существенный недостаток известного ДУ состоит в том, что он имеет нестабильный уровень выходного синфазного напряжения, зависящий от параметров двухполюсников нагрузки 11 и 12, которые в ряде важных для практики случаев должны выполняться в виде резисторов [13, 14]. Это значительно затрудняет его согласование с последующими функциональными узлами многокаскадных интерфейсных СФ-блоков и IP-модулей.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение при нестабильности параметров элементов 11, 12, 9, 10 и напряжении питания.

Поставленная задача решается тем, что в каскодном дифференциальном усилителе (фиг.1), содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого соединена с первым 4 источником питания, первый 5 и второй 6 выходные транзисторы с объединенными базами, цепь смещения 7, связанная с объединенными базами первого 5 и второго 6 выходных транзисторов, первый 9 вспомогательный резистор, включенный между вторым 8 источником питания и эмиттером первого 5 выходного транзистора, связанным со вторым 3 токовым выходом входного дифференциального каскада 1, второй 10 вспомогательный резистор, включенный между вторым 8 источником питания и эмиттером второго 6 выходного транзистора, связанным с первым 2 токовым выходом входного дифференциального каскада 1, первый 11 двухполюсник нагрузки, включенный между коллектором первого 5 выходного транзистора и первым 4 источником питания, второй 12 двухполюсник нагрузки, включенный между коллектором второго 6 выходного транзистора и первым 4 источником питания, предусмотрены новые элементы и связи - цепь смещения 7 включена между объединенными базами первого 5 и второго 6 выходных транзисторов и вторым 8 источником питания, причем в схему введены первый 13 и второй 14 дополнительные транзисторы, объединенные эмиттеры которых связаны с первым 4 источником питания через первый 15 токостабилизирующий двухполюсник, коллектор первого 13 дополнительного транзистора соединен с объединенными базами первого 5 и второго 6 выходных транзисторов, база первого 13 дополнительного транзистора соединена с общей шиной 16 первого 4 и второго 8 источников питания, коллектор первого 5 выходного транзистора связан с базой второго 14 дополнительного транзистора через последовательно соединенные первый 17 буферный усилитель и первый 18 дополнительный резистор, коллектор второго 6 выходного транзистора связан с базой второго 14 дополнительного транзистора через последовательно соединенные второй 19 буферный усилитель и второй 20 дополнительный резистор.

На фиг.1 показана схема ДУ-прототипа.

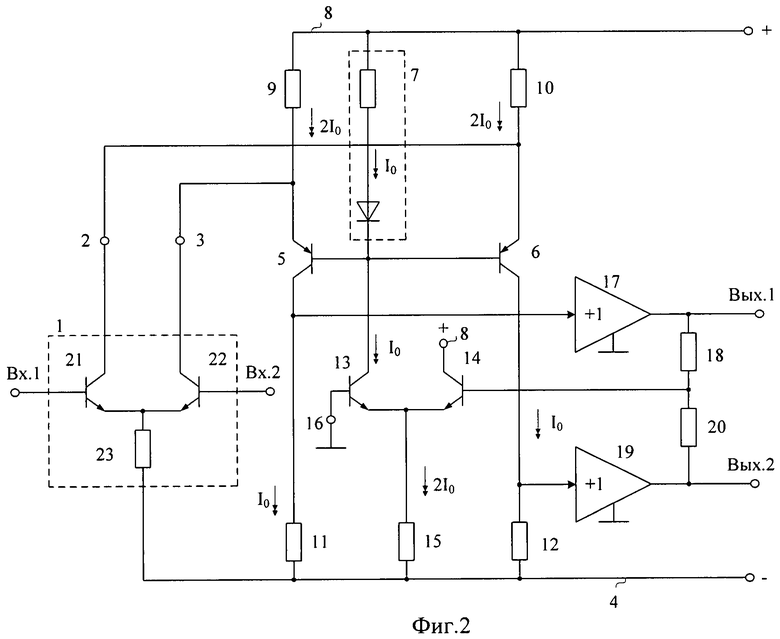

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

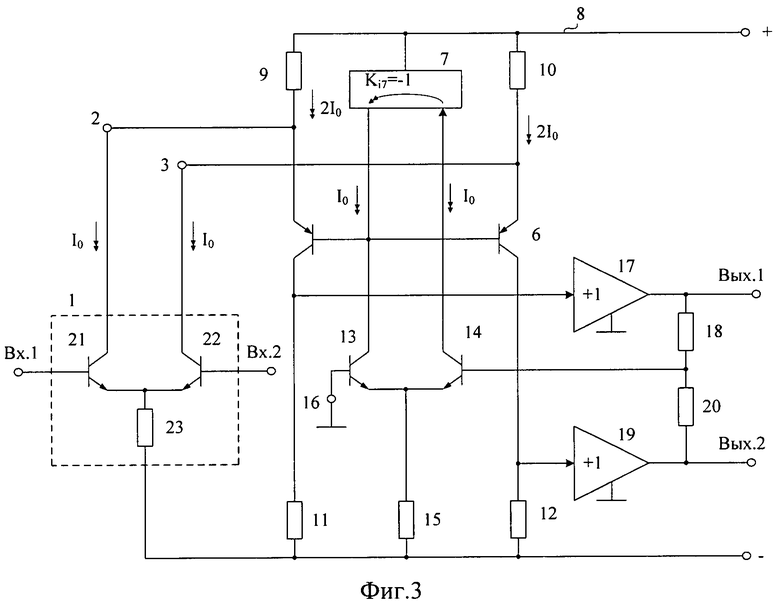

Схема ДУ по п.3 формулы изобретения приведена на фиг.3.

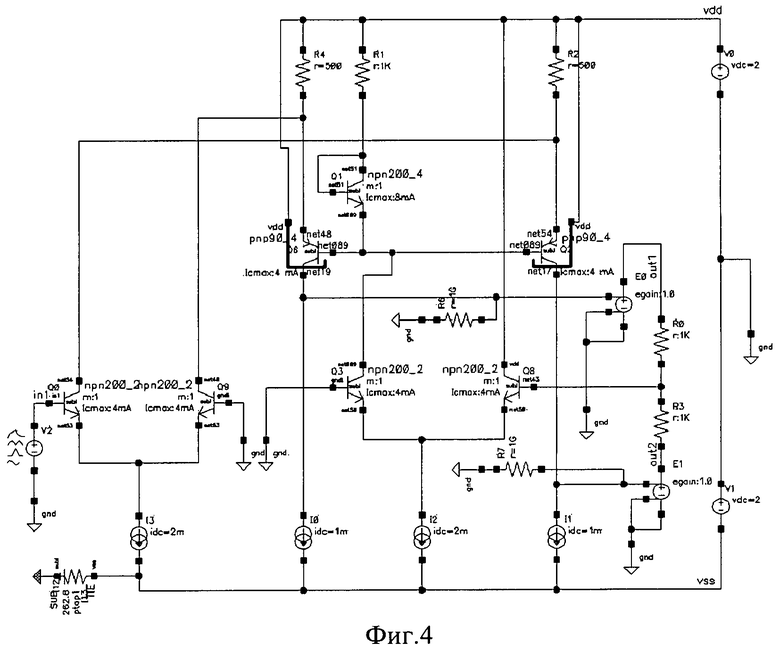

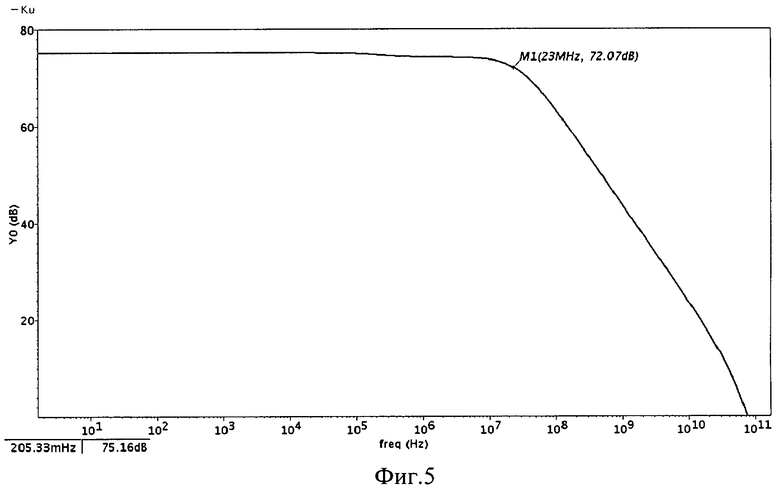

На фиг.4 показана схема заявляемого ДУ в среде компьютерного моделирования Cadance на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.5 - зависимость его коэффициента усиления по напряжению от частоты.

Каскодный дифференциальный усилитель (фиг.2) содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого соединена с первым 4 источником питания, первый 5 и второй 6 выходные транзисторы с объединенными базами, цепь смещения 7, связанная с объединенными базами первого 5 и второго 6 выходных транзисторов, первый 9 вспомогательный резистор, включенный между вторым 8 источником питания и эмиттером первого 5 выходного транзистора, связанным со вторым 3 токовым выходом входного дифференциального каскада 1, второй 10 вспомогательный резистор, включенный между вторым 8 источником питания и эмиттером второго 6 выходного транзистора, связанным с первым 2 токовым выходом входного дифференциального каскада 1, первый 11 двухполюсник нагрузки, включенный между коллектором первого 5 выходного транзистора и первым 4 источником питания, второй 12 двухполюсник нагрузки, включенный между коллектором второго 6 выходного транзистора и первым 4 источником питания. Цепь смещения 7 включена между объединенными базами первого 5 и второго 6 выходных транзисторов и вторым 8 источником питания, причем в схему введены первый 13 и второй 14 дополнительные транзисторы, объединенные эмиттеры которых связаны с первым 4 источником питания через первый 15 токостабилизирующий двухполюсник, коллектор первого 13 дополнительного транзистора соединен с объединенными базами первого 5 и второго 6 выходных транзисторов, база первого 13 дополнительного транзистора соединена с общей шиной 16 первого 4 и второго 8 источников питания, коллектор первого 5 выходного транзистора связан с базой второго 14 дополнительного транзистора через последовательно соединенные первый 17 буферный усилитель и первый 18 дополнительный резистор, коллектор второго 6 выходного транзистора связан с базой второго 14 дополнительного транзистора через последовательно соединенные второй 19 буферный усилитель и второй 20 дополнительный резистор.

На фиг.2, в соответствии с п.2 формулы изобретения, коллектор второго 14 дополнительного транзистора связан со вторым 8 источником питания, а входной дифференциальный каскад реализован на транзисторах 21 и 22 и двухполюснике 23.

На фиг.3, в соответствии с п.3 формулы изобретения, в качестве цепи смещения 7 используется дополнительное токовое зеркало 21, вход которого соединен с коллектором второго 14 дополнительного транзистора, токовый выход подключен к объединенным базам первого 5 и второго 6 выходных транзисторов, а общий эмиттерный выход связан со вторым 8 источником питания.

В качестве первого 11 и второго 12 двухполюсников нагрузки могут применяться резисторы, а в ряде случаев неуправляемые источники опорного тока.

Вместо токостабилизирующих двухполюсников 15, 23 авторы рекомендуют применять классические источники тока на резисторах или транзисторах, а в качестве буферных усилителей 17, 19 - обычные или двухтактные эмиттерные повторители напряжения.

Цепь смещения 7 может содержать резисторы и р-n переходы (фиг.2), а также выходные цепи токовых зеркал (фиг.3).

Рассмотрим работу ДУ (фиг.2).

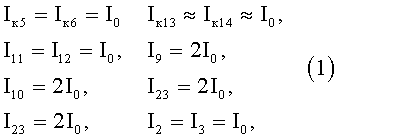

Статический режим по току предлагаемого ДУ устанавливается двухполюсниками 5, 15, 9, 10, 23. Причем коллекторные Iкi и эмиттерные Iэi токи транзисторов:

где I0 - устанавливаемый разработчиком параметр статического режима транзисторов схемы, например 1 мА.

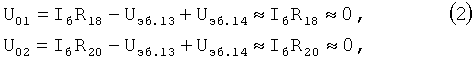

Статическое напряжение U01, U02 на выходах Вых.1 и Вых.2 ДУ при нулевом входном сигнале (uвх=0) можно найти из уравнения:

где Uэб.14=Uэб.13 - напряжение «эмиттер-база» транзисторов 14 и 13;

Iб - половина тока базы транзистора 14.

Введение транзисторов 13 и 14 обеспечивает устойчивость статического режима схемы благодаря петле отрицательной обратной связи «база транзистора 14 - эмиттер транзистора 13 - базы транзисторов 5 и 6 - коллекторы транзисторов 5 и 6 - буферные усилители 17 и 19 - резисторы 18 и 20 - база транзистора 14» и выполнение условий (2) независимо от параметров элементов 9, 10, 11, 12, которые могут изменяться в некоторых пределах.

Таким образом, при типовых значениях токов базы транзистора 14, а также при R20=R18=500÷1000 Ом выходное синфазное напряжение ДУ (фиг.2) практически равно нулю в широком диапазоне температурных и радиационных воздействий, а также изменений напряжений питания. Это весьма существенно для согласования заявляемого ДУ с последующими функциональными узлами радиоэлектронной аппаратуры.

Таким образом, предлагаемый ДУ при использовании в качестве двухполюсников нагрузки 11 и 12 пассивных элементов (резисторов или неуправляемых источников опорного тока) имеет существенные преимущества в сравнении с прототипом и другими известными техническими решениями.

Литература

1. Патент США №4.406.990, fig.3.

2. Патент США №6.114.234.

3. Патент США №5.091.701, fig.1.

4. Патент США №5.140.280.

5. Патент США №5.786.729.

6. Патент США №6.448.853.

7. Патент США №4.390.850.

8. Патент США №5.327.100 fig.2.

9. Патент США №6.4383.382 fig.2, fig.1.

10. Патент США №5.374.897.

11. Патент США №6.529.076.

12. Патент США №5.627.495 fig.2.

13. Патент США №7.605.658 fig 4, fig.5.

14. Патентная заявка US 2009/058529.

15. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007 - С.106-110.

16. СВЧ СФ-блоки систем связи на базе полностью дифференциальных операционных усилителей / Н.Н.Прокопенко, А.С.Будяков, К.Schmalz, С.Scheytt // Проблемы разработки перспективных микро- и наноэлектронных систем - 2010. Сборник трудов / под общ. ред. академика РАН А.Л.Стемпковского. - М.: ИППМ РАН, 2010. - С.583-586.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2439787C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441314C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421893C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439780C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ВЫСОКОЧАСТОТНОЙ КОРРЕКЦИЕЙ | 2010 |

|

RU2423778C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2469465C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2463703C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2394362C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение при нестабильности параметров элементов нагрузки, резисторов эмиттерных цепей выходных транзисторов и напряжений питания. Каскодный дифференциальный усилитель содержит входной дифференциальный каскад, первый и второй выходные транзисторы, цепь смещения, первый и второй вспомогательные резисторы, первый и второй двухполюсники нагрузки, первый и второй дополнительные транзисторы, первый токостабилизирующий двухполюсник, первый и второй буферные усилители, первый и второй дополнительные резисторы. 2 з.п. ф-лы, 5 ил.

1. Каскодный дифференциальный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, эмиттерная цепь которого соединена с первым (4) источником питания, первый (5) и второй (6) выходные транзисторы с объединенными базами, цепь смещения (7), связанная с объединенными базами первого (5) и второго (6) выходных транзисторов, первый (9) вспомогательный резистор, включенный между вторым (8) источником питания и эмиттером первого (5) выходного транзистора, связанным со вторым (3) токовым выходом входного дифференциального каскада (1), второй (10) вспомогательный резистор, включенный между вторым (8) источником питания и эмиттером второго (6) выходного транзистора, связанным с первым (2) токовым выходом входного дифференциального каскада (1), первый (11) двухполюсник нагрузки, включенный между коллектором первого (5) выходного транзистора и первым (4) источником питания, второй (12) двухполюсник нагрузки, включенный между коллектором второго (6) выходного транзистора и первым (4) источником питания, отличающийся тем, что цепь смещения (7) включена между объединенными базами первого (5) и второго (6) выходных транзисторов и вторым (8) источником питания, причем в схему введены первый (13) и второй (14) дополнительные транзисторы, объединенные эмиттеры которых связаны с первым (4) источником питания через первый (15) токостабилизирующий двухполюсник, коллектор первого (13) дополнительного транзистора соединен с объединенными базами первого (5) и второго (6) выходных транзисторов, база первого (13) дополнительного транзистора соединена с общей шиной (16) первого (4) и второго (8) источников питания, коллектор первого (5) выходного транзистора связан с базой второго (14) дополнительного транзистора через последовательно соединенные первый (17) буферный усилитель и первый (18) дополнительный резистор, коллектор второго (6) выходного транзистора связан с базой второго (14) дополнительного транзистора через последовательно соединенные второй (19) буферный усилитель и второй (20) дополнительный резистор.

2. Каскодный дифференциальный усилитель по п.1, отличающийся тем, что коллектор второго (14) дополнительного транзистора связан со вторым (8) источником питания.

3. Каскодный дифференциальный усилитель по п.1, отличающийся тем, что в качестве цепи смещения (7) используется дополнительное токовое зеркало (21), вход которого соединен с коллектором второго (14) дополнительного транзистора, токовый выход подключен к объединенным базам первого (5) и второго (6) выходных транзисторов, а общий эмиттерный выход связан со вторым (8) источником питания.

| US 4600893 А, 15.07.1986 | |||

| US 4406990 А, 27.09.1983 | |||

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349024C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

Авторы

Даты

2012-01-10—Публикация

2011-01-31—Подача