Изобретение относится к технике телевизионного и звукового вещания и предназначено для применения в области цифрового радиовещания и цифрового телевидения.

Изобретение относится к технике телевизионного и звукового вещания и может использоваться при расположении приемника в движущемся транспорте, в городских квартирах с плотной застройкой, многолучевостью, а также в районах со сложным рельефом, где в указанных условиях телевидение с используемыми на сегодня системами не может обеспечить удовлетворительного качества приема.

Известен способ телевизионного вещания RU 2219676 С2, который включает в себя блоки сжатия сигналов, мультиплексирования с получением сжатого сигнала информационного телевидения, помехозащищающего канального кодирования, модуляции несущих с применением ортогонального частотного разделения каналов (ОЧРК), добавление фазовых приращений случайной величины, назначаемых из набора заранее известных случайных величин, и излучение.

Наиболее близким по технической сущности к заявляемому техническому решению является способ цифрового телевизионного вещания по стандарту DVB-T (Цифровое Видео Вещание (DVB)). Кадровая структура, канальное кодирование и модуляция для цифрового наземного телевидения. Европейский стандарт (Телекоммуникационная серия). ETSI. EN 300 744 v 1.6.1 (2009-01), включающий в себе последовательно соединенные блоки интерфейс, рандомизатор, кодер Рида-Соломона, сверточный перемежитель, сверточный кодер, битовый перемежитель, символьный перемежитель, формирователь КАМ, вычислитель обратного быстрого преобразования Фурье (вычислитель ОБПФ), цифроаналоговый преобразователь (ЦАП), высокочастотный блок (ВЧ блок), формирователь пилот-сигналов на входе формирователя КАМ.

Недостатком этого способа является то, что каждый из блоков модулятора самостоятельно находит во входной информации синхронизирующие посылки, что приводит к усложнению алгоритмов работы всех блоков модулятора и, как следствие, работе их на более высоких частотах, что влечет повышение требований к вычислительному устройству.

Задачей настоящего изобретения является создание DVB-T модулятора, позволяющего уменьшить требования к вычислительному устройству за счет нахождения синхронизирующих посылок в единственном блоке и оптимизации процессов синхронизации работы всех блоков в целом и, как следствие, использование менее быстродействующих вычислительных устройств.

Технический результат, достигаемый при реализации изобретения, состоит в увеличении эффективности формирования цифрового сигнала и снижении требований к производительности вычислительного устройства.

Сущность изобретения заключается в том, что в DVB-T модуляторе, содержащем блоки интерфейс, рандомизатор, кодер Рида-Соломона, сверточный перемежитель, сверточный кодер, битовый перемежитель, символьный перемежитель, формирователь КАМ, вычислитель обратного быстрого преобразования Фурье (вычислитель ОБПФ), цифроаналоговый преобразователь (ЦАП), высокочастотный блок (ВЧ блок), формирователь пилот-сигналов на входе формирователя КАМ, дополнительно введены блок разбиения пакетов, регистр и блок управления. Вход блока разбиения пакетов подключен к выходу интерфейса, а выходы блока подключены к рандомизатору и блоку управления. Вход регистра подключен к выходу блока рандомизатора, а выходы подключены к блокам кодера Рида-Соломона и сверточному перемежителю. Вход блока управления подключен к выходу блока разбиения пакетов, а выходы подключены ко всем блокам модулятора.

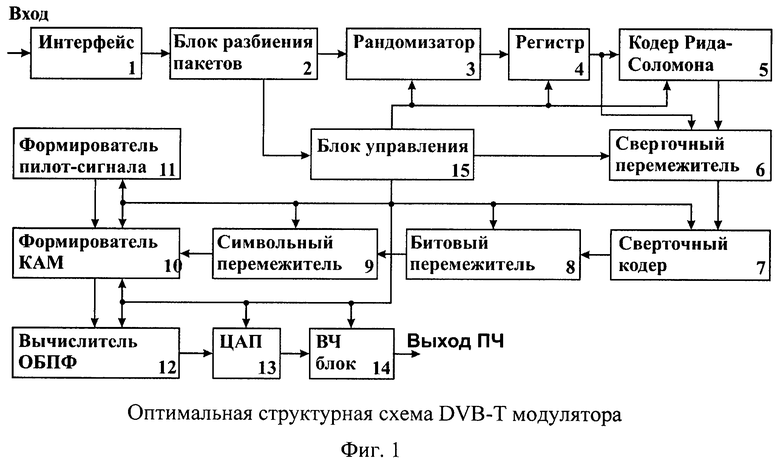

На фиг.1 изображен DVB-T модулятор.

DVB-T модулятор содержит последовательно соединенные интерфейс 1, блок разбиения пакетов 2, рандомизатор 3, регистр 4, кодер Рида-Соломона 5, сверточный перемежитель 6, сверточный кодер 7, битовый перемежитель 8, символьный перемежитель 9, формирователь КАМ 10, вычислитель обратного быстрого преобразования Фурье (ОБПФ) 12, цифроаналоговый преобразователь (ЦАП) 13, ВЧ блок 14, формирователь пилот-сигналов на входе формирователя КАМ 10, а также блок управления 15, который получает информацию с блока разбиения пакетов 2 и имеет связи со всеми блокам модулятора.

Работа DVB-T модулятора осуществляется следующим образом. Входной сигнал поступает на блок интерфейса 1, после чего на блок разбиения пакетов 2, где во входной последовательности находится синхронизирующая информация, которая поступает на блок управления 15, а также формируются группы пакетов для правильной работы всех остальных блоков модулятора. Блок управления 15 получает синхронизирующую информацию и организует синхронную работу всех блоков модулятора, тем самым, уменьшая общую нагрузку на каждый блок в отдельности.

После прохождения рандомизатора 3 информация поступает в регистр 4, в который запись производится за время tран, а считывание производится блоком кодера Рида-Соломона 5 за время tкод. Поскольку tран>tкод, а начала записи и считывания совпадают, то блок кодера Рида-Соломона 5 успевает получить хранящуюся в регистре информацию до того, как она будет затерта новой информацией, поступающей с рандомизатора 3.

Кодер Рида-Соломона 5 не изменяет входную информацию, а лишь добавляет к концу последовательности проверочные байты. В данном изобретении с регистра 4 информация также поступает на сверточный перемежитель 6 за время tпер. Поскольку tран>tпер>tкод и начала записи и считывания совпадают, то блок сверточного перемежителя 6 успевает получить хранящуюся в регистре 4 информацию до того, как она будет затерта новой информацией, поступающей с рандомизатора 3, а также начинает обработку поступившей информации еще до окончания работы блока кодера Рида-Соломона 5, и когда блок кодера Рида-Соломона 5 будет готов выдать последовательность проверочных байтов, блок сверточного перемежителя 6 принимает эту информацию и ставит ее в строго определенные места своей выходной информационной последовательности.

Блок разбиения пакетов 2 отвечает за первоначальный поиск синхронизирующей информации во входном потоке и передает ее на один общий для всех блок управления 15, а также формирует пачки пакетов для работы модулятора. Блок управления 15 принимает сигнал о начале очередного пакета (группы пакетов) данных и обеспечивает синхронную работу всех блоков модулятора в соответствии с алгоритмами работы каждого блока в отдельности.

Кроме того, блок управления 15 задает параметры, необходимые для работы блоков по алгоритмам, необходимым в данном конкретном случае.

Таким образом, в предлагаемом устройстве уменьшаются требования к быстродействию каждого блока в отдельности вследствие отсутствия необходимости поиска синхронизирующей информации каждым блоком, что в свою очередь сказывается на общем быстродействии, необходимом для реализации вычислительного устройства. Использование регистра 4 позволяет увеличить производительность предложенного DVB-T модулятора за счет параллельной обработки информации в программируемой логической интегральной схеме. Вследствие синхронной работы всех блоков, тактируемых одним общим блоком управления 15, существенно уменьшаются требования к вычислительному устройству.

Изобретение относится к технике телевизионного и звукового вещания и предназначено для применения в области цифрового радиовещания и цифрового телевидения. Техническим результатом является уменьшение требований к вычислительному устройству за счет оптимизации процессов синхронизации работы всех блоков в целом и, как следствие, использование менее быстродействующих вычислительных устройств. Результат достигается тем, что DVB-T модулятор содержит последовательно соединенные блоки интерфейс, рандомизатор, кодер Рида-Соломона, сверточный перемежитель, сверточный кодер, битовый перемежитель, символьный перемежитель, формирователь КАМ, вычислитель обратного быстрого преобразования Фурье (вычислитель ОБПФ), цифроаналоговый преобразователь (ЦАП), высокочастотный блок (ВЧ блок) и формирователь пилот-сигналов на входе формирователя КАМ, а также дополнительно введены блоки: блок разбиения пакетов, получающий информацию с интерфейса и выдающий ее на рандомизатор и блок управления, регистр, получающий сигналы с рандомизатора и выдающий сигнал на кодер Рида-Соломона и сверточный перемежитель, блок управления, получающий информацию с блока разбиения пакетов, а выходы подключены ко всем блокам модулятора. 1 ил.

DVB-T модулятор содержит последовательно соединенные блоки интерфейс, рандомизатор, кодер Рида-Соломона, сверточный перемежитель, сверточный кодер, битовый перемежитель, символьный перемежитель, формирователь КАМ, вычислитель обратного быстрого преобразования, Фурье (вычислитель ОБПФ), цифроаналоговый преобразователь (ЦАП), высокочастотный блок (ВЧ блок), формирователь пилот-сигналов на входе формирователя КАМ, отличающийся тем, что в структурную схему введены: блок разбиения пакетов, регистр и блок управления, причем вход блока разбиения пакетов подключены к выходу интерфейса, а выходы блока разбиения пакетов подключены к рандомизатору и блоку управления, кроме того, вход регистра подключен к выходу блока рандомизатора, а выходы - подключены к блокам кодера Рида-Соломона и сверточному перемежителю, вход блока управления подключен к выходу блока разбиения пакетов, а выходы - подключены ко всем блокам модулятора.

| KR 20030056505 А, 04.07.2003 | |||

| KR 20090035061 A, 09.04.2009 | |||

| СПОСОБ МОДУЛЯЦИИ И ДЕМОДУЛЯЦИИ, УСТРОЙСТВО МОДУЛЯЦИИ И УСТРОЙСТВО ДЕМОДУЛЯЦИИ | 2006 |

|

RU2384960C2 |

Авторы

Даты

2012-07-20—Публикация

2010-06-15—Подача