Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем, к системам связи и, в частности, к способу и устройству для присвоения вариантов избыточности кольцевому буферу в пределах системы связи.

Уровень техники

В системе связи, технологии защиты от ошибок используют, чтобы защитить сигнал от ухудшения во время передачи по каналу. В рамках таких технологий защиты от ошибок, кодовое слово производят для каждого информационного блока. Для того чтобы согласовать скорость передачи по радиоканалу, изменяют размер кодового слова посредством алгоритма согласования скорости до его передачи по физическому каналу. Алгоритм согласования скорости обеспечивает требуемое число битов, которые будут переданы по каналу посредством пунктирования или повторения кодового слова. Алгоритм согласования скорости является важным, поскольку он может значительно влиять на быстродействие системы и эффективность осуществления.

Если система использует только прямое исправление ошибок (FEC), тогда только одна передача необходима для данного информационного блока, и алгоритм согласования скорости обеспечивает только один вариант кодового слова. Если система использует действие гибридного автоматического запроса повторной передачи (HARQ), тогда многократные передачи могут быть необходимы для данного информационного блока, и алгоритм согласования скорости может потребоваться, чтобы обеспечить другие варианты кодового слова (например, для нарастающей избыточности HARQ). HARQ переходит в FEC, если только одна передача используется для информационного блока.

Один способ, чтобы выполнить функцию согласования скорости заключается в том, чтобы определить конфигурации пунктирования/повторения для каждого размера информационного блока и кодовую скорость, с которой может столкнуться система. Однако этот способ негибкий. Кроме того, он становится непрактичным, если система включает в себя тысячи размеров информационного блока и сочетаний кодовых скоростей, таких как в системе связи 3GPP.

Другой способ, чтобы выполнить согласование скорости заключается в том, чтобы определить правило, которое проходит через биты кодового слова один за другим и определяет, следует ли биту кодового слова быть выколотым (удаленным) или повторенным. Такой способ имеет преимущество гибкости и определен в 3GPP Rel-99. Однако такой способ страдает от неэффективности осуществления. Кроме того, не существует способа гарантировать, что передачи, связанные с данным информационным блоком не накладываются (т.е. ортогональные) для IR HARQ. Таким образом, может пострадать быстродействие системы.

С другой стороны, кольцевой буфер на основе алгоритма согласования скорости может быть разработан, чтобы обеспечить хорошее быстродействие с низкой сложностью осуществления. В этом способе, биты кодового слова перестраивают, чтобы образовать кольцевой буфер. Если N требуемых кодированных бита необходимо для передачи, блок длиной N требуемых последовательных битов берут из кольцевого буфера (циклически возвращаются к началу, если доходят до последнего бита кольцевого буфера). Поэтому пунктирование и повторение может быть достигнуто, используя единственный способ. Технология кольцевой буферизации имеет преимущества в гибкости, быстродействии и легкости осуществления.

Чтобы реализовывать другие варианты кодового слова в действии HARQ, параметр, такой как вариант избыточности (RV), может быть использован как ввод в кольцевой буфер на основе алгоритма согласования скорости. Варианты избыточности могут определять начальные положения в пределах кольцевого буфера для выбора секции кодового слова для передачи.

В предшествующем уровне техники, допустимые начальные положения RVs равномерно распределены по кольцевому буферу, содержащему последовательность битов кодового слова после перестройки, что делает его трудным, чтобы осуществлять каждую передачу HARQ. Поэтому существует потребность в способе и устройстве для присвоения вариантов избыточности кольцевому буферу в пределах системы связи, что улучшает эффективность кольцевого буфера на основе алгоритма согласования скорости.

Краткое описание чертежей

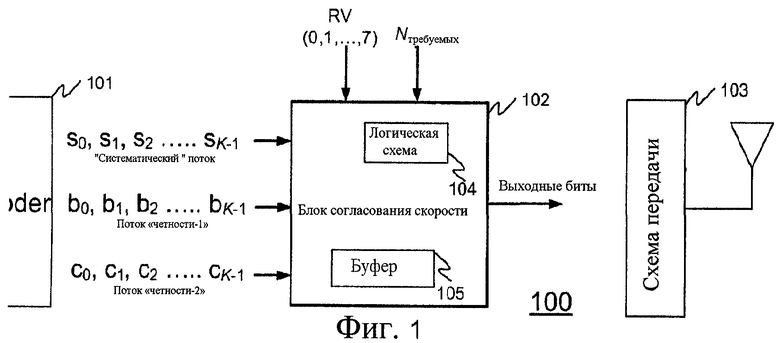

Фиг.1 является блок-схемой передатчика предшествующего уровня техники.

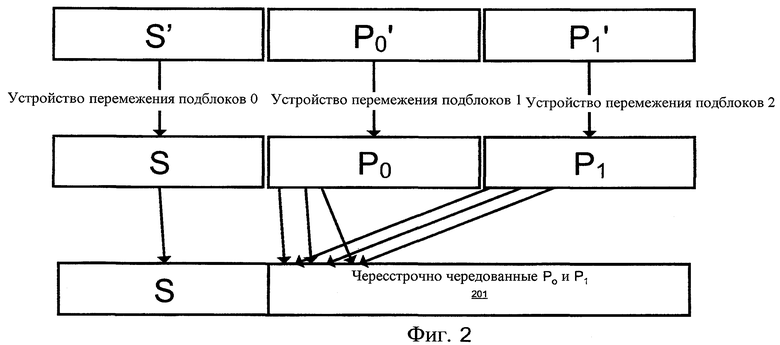

Фиг.2 изображает перемежение подблоков и чересстрочное чередование.

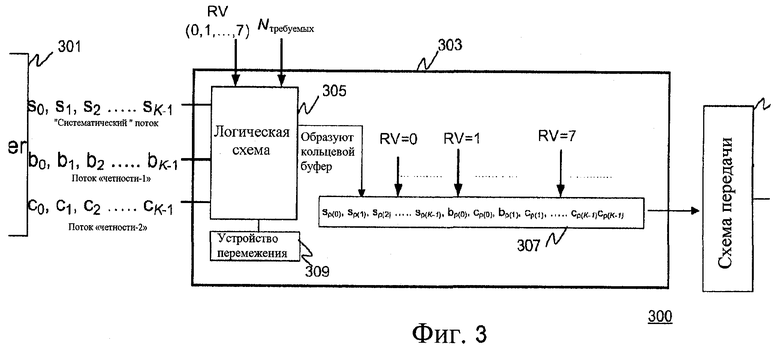

Фиг.3 является блок-схемой передатчика.

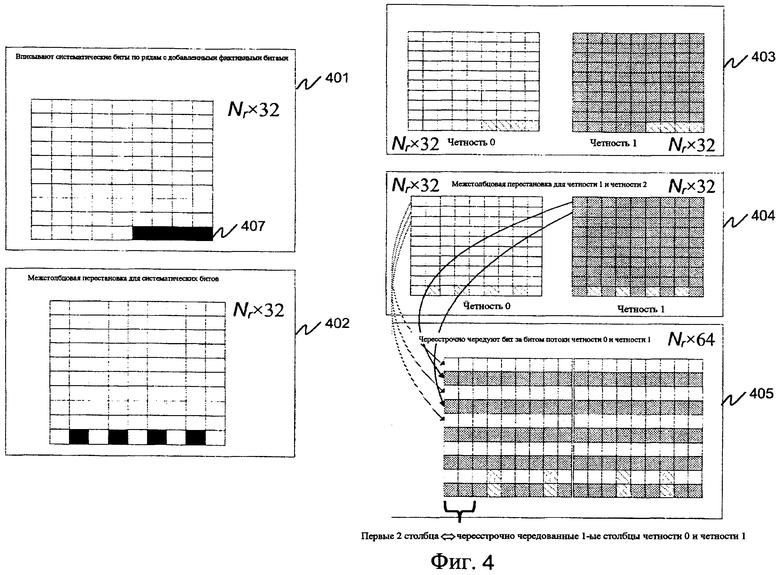

Фиг.4 и 5 изображает перемежение подблоков и чересстрочное чередование.

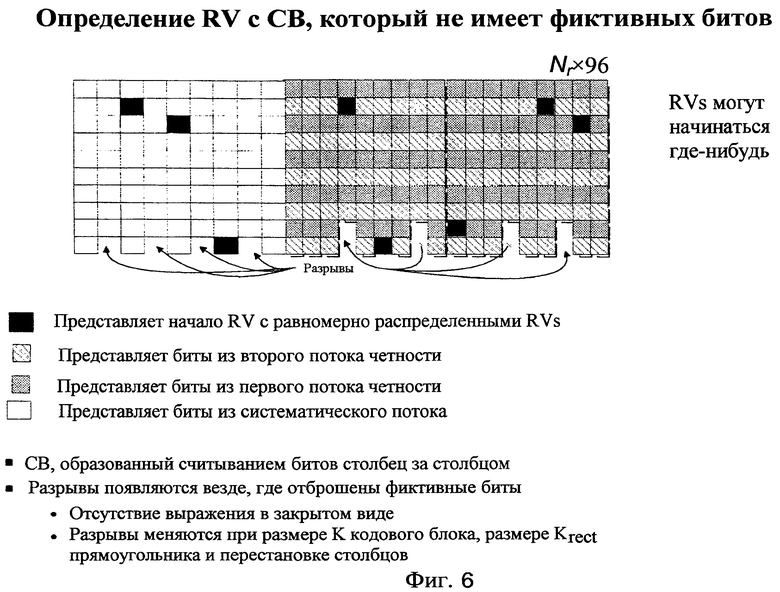

Фиг.6 изображает кольцевой буфер с удаленными фиктивными битами, который можно представить в матричном формате.

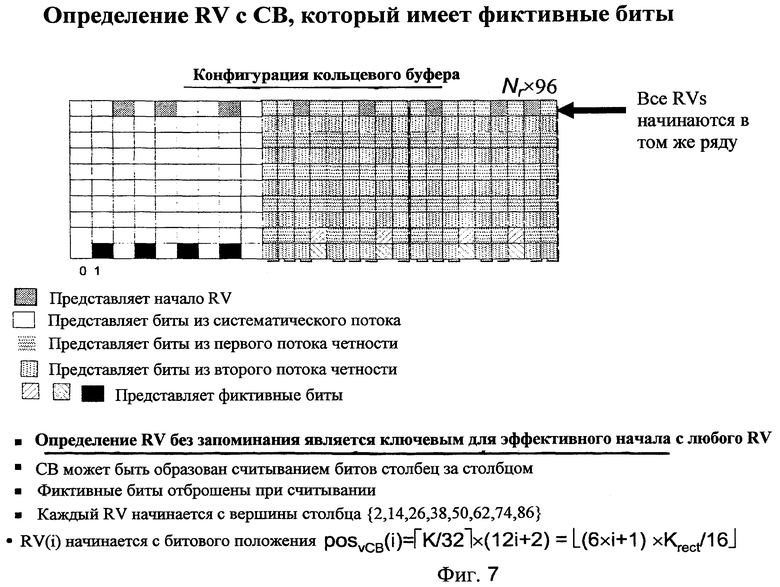

Фиг.7 изображает кольцевой буфер вариантов избыточности, который имеет фиктивные биты.

Фиг.8 изображает использование виртуального кольцевого буфера.

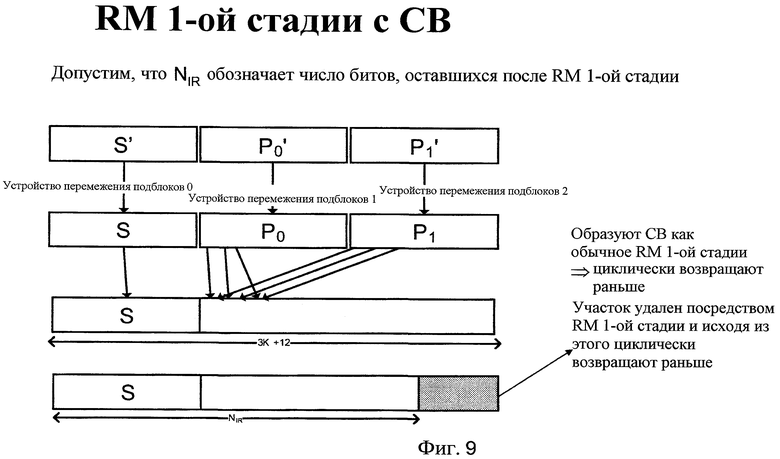

Фиг.9 изображает согласование скорости первой стадии с кольцевой буферизацией.

Фиг.10 изображает пунктирование систематического бита.

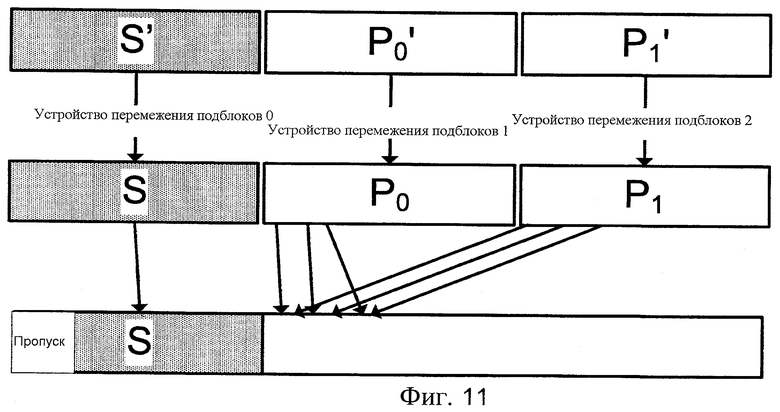

Фиг.11 изображает пропуск малого участка систематических битов в пределах кольцевого буфера.

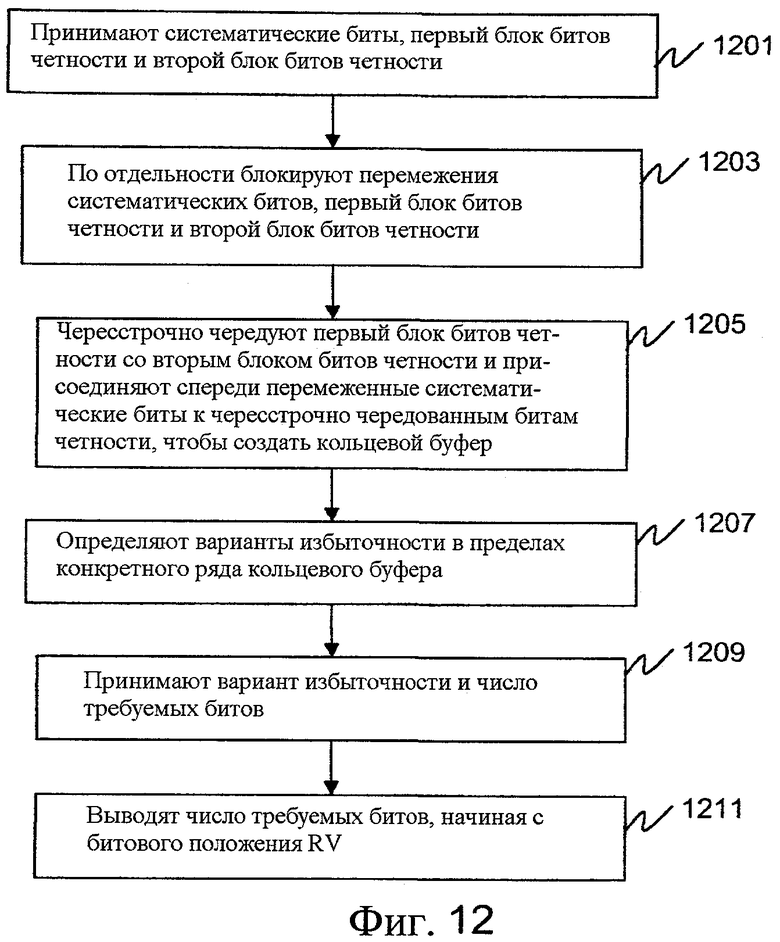

Фиг.12 является блок-схемой последовательности операций способа, показывающей действие передатчика фиг.3.

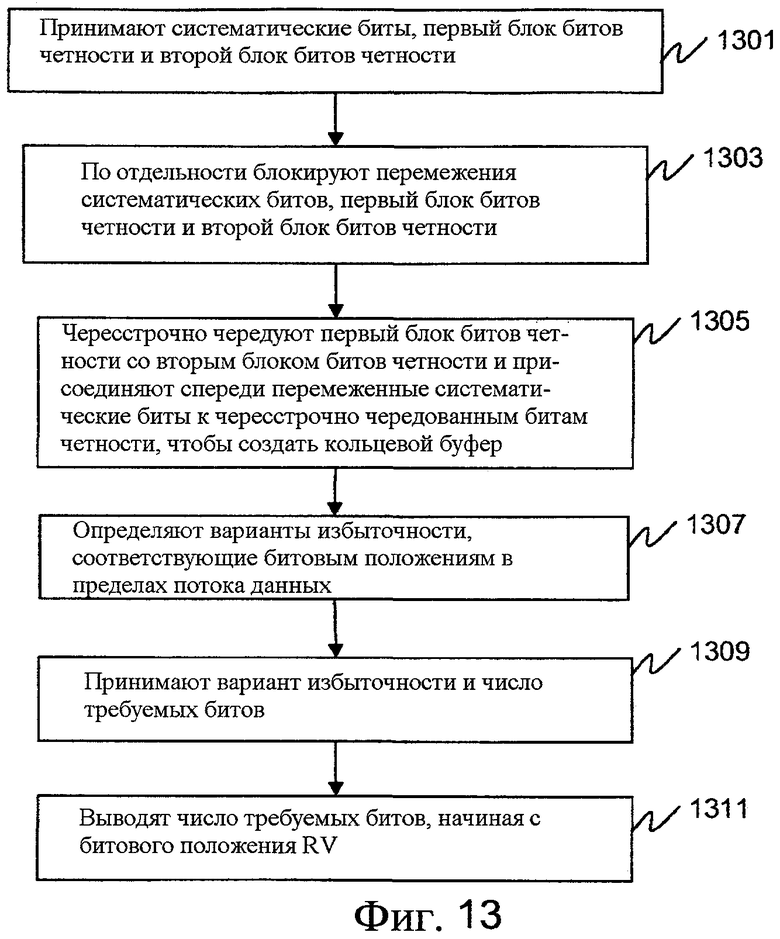

Фиг.13 является блок-схемой последовательности операций способа, показывающей действие передатчика фиг.3.

Подробное описание чертежей

Для того чтобы разрешить вышеупомянутую необходимость, здесь обеспечен способ и устройство для присвоения вариантов избыточности кольцевому буферу в пределах системы связи. Во время действия создают кольцевой буфер, где определяют только варианты избыточности, чтобы начинались с вершин (т.е. на первом ряду) устройств перемежения составных подблоков. Например, при сумме из восьми вариантов избыточности, варианты избыточности будут расположены в положениях

Kпотока/32(12×i+σ), i=0,1,...,7,

где σ указывает индекс столбца устройства перемежения подблоков положения первого RV (RV0).

Определение положений RV, как описано выше, имеет в результате более легкое осуществление HARQ. В большей частности, эта технология позволяет определение RV без запоминания, что очень полезно в поддержке большого числа размеров входных блоков при кольцевом буферном согласовании скорости (RM). В частности, вышеописанное расположение RV позволяет осуществление виртуального кольцевого буфера (т.е. физический кольцевой буфер не осуществляют), что позволяет требуемому числу битов быть непосредственно выбранными из выходного потока кодера, начиная от любого RV в кольцевом буфере.

Настоящее изобретение заключает в себе способ присвоения вариантов избыточности кольцевому буферу. Способ содержит этапы приема систематических битов, первого блока битов четности и второго блока битов четности. Все систематические биты, первый блок битов четности и второй блок битов четности содержат фиктивные биты. Систематические биты, первый блок битов четности и второй блок битов четности по отдельности блоками перемежают, и первый блок битов четности чересстрочно чередуют со вторым блоком битов четности, чтобы создать чересстрочно чередованные биты четности. Перемеженные систематические биты присоединяют спереди чересстрочно чередованных битов четности, чтобы создать кольцевой буфер, и определяют варианты избыточности, чтобы начинались в конкретном ряду кольцевого буфера. Когда принимают вариант избыточности (RV) и число требуемых битов, число требуемых битов является выводом, начиная с битового положения RV.

Настоящее изобретение содержит устройство, содержащее кодер, выводящий систематические биты, первый блок битов четности и второй блок битов четности. Обеспечена схема согласования скорости, принимающая систематические биты, первый блок битов четности и второй блок битов четности и создающая кольцевой буфер, имеющий фиктивные биты. Конкретный ряд кольцевого буфера используют как варианты избыточности (RVs), и схема согласования скорости выводит нефиктивные биты из кольцевого буфера в передатчик, начиная с конкретного RV. В заключение, обеспечена схема передачи, принимающая нефиктивные биты и передающая нефиктивные биты.

В заключение, настоящее изобретение содержит устройство, содержащее кодер, выводящий систематические биты, первый блок битов четности и второй блок битов четности, каждый длиной Kпотока. Устройство дополнительно содержит схему согласования скорости для приема систематических битов, первого блока битов четности и второго блока битов четности, и перемежения систематических битов, первого блока битов четности и второго блока битов четности. Логическая схема обеспечена для определения вариантов избыточности (RVs), соответствующих положениям в пределах потока данных, с которых начинают вывод данных. Когда используют восемь RVs, RVs находятся в положениях

Kпотока/32(12×i+σ), i=0,1,...,7,

где σ указывает индекс столбца устройства перемежения подблоков начального положения первого RV (RV0). Поток содержит перемеженные систематические биты, и перемеженный и чересстрочно чередованный первый и второй блок битов четности. В заключение, схема передачи обеспечена для приема нефиктивных битов, начиная с конкретного RV, и передачи нефиктивных битов.

Переходя теперь к чертежам, в которых одинаковые цифры обозначают одинаковые компоненты, фиг.1 и 2 изображают функциональное назначение кольцевого буфера на основе способа согласования скорости. Более конкретно, фиг.1 является блок-схемой передатчика и фиг.2 изображает перемежение подблоков и чересстрочное чередование. Во время действия передатчика 100, кодер 101 выводит систематический битовый поток и, по меньшей мере, два потока четности. Для этого конкретного примера, кодер 101 содержит турбокодер скорости 1/3, принятый в 3GPP стандартизации. Отмечено, что следующие принципы могут быть применены к другим типам кодов коррекции ошибок, таким как турбокоды с другими кодовыми скоростями, коды с малой плотностью проверок на четность (LDPC), сверточные коды и так далее.

Кодер 101 выводит три потока, соответствующих систематическому битовому потоку и двум потокам четности. В некоторых случаях систематический поток может содержать несколько (например, 4) бита, которые не являются систематическими, например, вследствие хвостовых битов, как для 3GPP турбокода. (Хвостовые биты отсутствуют, когда используют кольцевое кодирование.) Потоки могут также содержать биты наполнителя, вставленные до турбокодирования. Для простоты, все биты в систематическом потоке относят, как систематические биты, и все биты в соответственных потоках четности относят, как биты четности 0 и биты четности 1 соответственно.

Схема 102 согласования скорости принимает вывод потоков из кодера 101 и выполняет перемежение подблоков на каждом потоке по отдельности. Это изображено на фиг.2, где S′, P0′ и P1′ являются систематическим битовым потоком, потоком битов четности 0 и потоком битов четности 1 соответственно. Каждый поток перестраивают (перемежают) со своим собственным устройством перемежения подблоков (не показано на фиг.1 или 2), чтобы производить S, P0 и P1. Затем P0 и P1 чересстрочно чередуют друг с другом, чтобы производить участок 201 чересстрочно чередованных P0 и P1. Единственный выходной буфер 105 (также названный кольцевым буфером) образуют сохранением перестроенных систематических битов S в начале последующего участка 201 чересстрочно чередованных P0 и P1.

Для требуемой кодовой скорости действия, число кодированных битов N требуемых, которые будут выбраны для передачи, вычисляют и передают в логическую схему 104 как ввод. Логическая схема 104 свободно считывает блок длиной N требуемых последовательных битов из последовательности кольцевого буфера (циклически возвращается к началу, если превышен последний бит кольцевого буфера) от некоторой начальной точки. Поэтому пунктирование и повторение может быть достигнуто, используя единственный способ. Технология кольцевой буферизации имеет преимущества в гибкости (достигнутой в кодовых скоростях) и неравномерности (в размерах потоков). Кольцевое буферное согласование скорости выбирает биты четности, приблизительно равномерно распределенные по решетке кода, независимо от требуемой кодовой скорости действия, если устройства перемежения подблоков разработаны правильно.

Фиг.3 является блок-схемой передатчика 300. Передатчик 300 содержит кодер 301 и схему 303 согласования скорости. Схема 303 согласования скорости дополнительно содержит логическую схему 305 и запоминающее устройство 307. Логическая схема 305 является предпочтительно микропроцессором, микроконтроллером, цифровыми сигнальными процессорами (DSPs) или подобными другими устройствами, известными обычным специалистам в данной области техники. Конкретные действия/функции логической схемы 305, таким образом, передатчика 300 установлены с выполнением программных команд и операций. Запоминающее устройство 307 содержит оперативное запоминающее устройство (RAM), динамическое оперативное запоминающее устройство (DRAM) и/или постоянное запоминающее устройство (ROM) или равнозначные им, которые используют как кольцевой буфер. Кодер 301 является предпочтительно 3GPP турбокодер скорости 1/3, однако, технологии, описанные здесь, для действующего передатчика 300 могут быть применены к другим кодерам, включая, но не ограничиваясь турбокодерами, выполняющими турбокодирование с другими кодовыми скоростями, с хвостовыми битами или не хвостовыми битами, кольцевые, бинарные или дуобинарные турбокодеры, с или без вставки битов наполнителя,..., и так далее.

Во время действия кодер 301 выводит три потока, соответствующих систематическому битовому потоку и двум потокам четности. Логическая схема 305 принимает вывод потоков из кодера 301 и выполняет перемежение подблоков на каждом потоке по отдельности. Затем логическая схема 305 чересстрочно чередует P0′ и P1′. Единственный выходной буфер 307 (кольцевой буфер) образуют сохранением перестроенных систематических битов S в начале последующих чересстрочно чередованных P0 и P1.

Несмотря на то, что устройство перемежения подблоков может быть любым устройством перестановок, обычно для простоты используют устройство прямоугольного перемежения (также названное устройством перемежения блоков) N r рядов и N с столбцов. Действия являются простыми, если размер потока Kпотока каждого потока равен размеру N r×N с устройства прямоугольного перемежения (т. е. блок полный). Однако часто размер потока меньше чем N r×N с, поэтому необходимо (N r×N с - Kпотока) фиктивных битов, чтобы наполнить блок.

Этот процесс образования кольцевого буфера изображен на Фиг.4 и 5 с 4 фиктивными битами, вставленными в каждый поток. Со ссылкой на фиг.4, систематические биты 401, имеющие добавленные фиктивные биты 407, блоками перемежают, чтобы производить переставленные систематические биты S 402. Подобным образом биты четности P0′ и P1′ 403 (имеющие добавленные фиктивные биты) перемежают, чтобы производить биты четности P0 и P1 404. Фиктивные биты добавляют к потокам так, чтобы устройство перемежения блоков было наполненным для каждого потока. P0 и P1 чересстрочно чередуют, чтобы производить чересстрочно чередованный участок, участок 405 чересстрочно чередованных P0 и P1. Две матрицы S и P0-1 объединяют, как показано на фиг.5 и сохраняют в буфере 307. Буфер 307 считывают по столбцам, начиная с вершины матрицы. Несмотря на то, что выше в описании фиктивные биты вставляют после потока, в некоторых вариантах осуществления они могут также быть вставлены до потока.

Во время действия передатчика 300, число кодированных битов N требуемых, которые будут выбраны для передачи, вычисляют и передают в логическую схему 305. Логическая схема 305 свободно считывает блок длиной N требуемых последовательных битов из выходного буфера 307 (циклически возвращается к началу, если превышен последний бит кольцевого буфера) от некоторой начальной точки. Для действия гибридного автоматического запроса повторной передачи (HARQ), параметр (вариант избыточности (RV)) обеспечивают в логическую схему 305, чтобы определять начальную точку в пределах буфера 307, так что другие секции буфера могут быть выбраны для передачи. Так как FEC является равнозначной HARQ только с одной передачей, FEC может также быть определено значением RV. Таким образом, логическая схема 305 принимает значение RV и число кодированных битов N требуемых, которые будут выбраны для передачи. Биты N требуемые считывают из буфера 307, начиная с участка, определенного RV. Эти биты являются типично выводом в передатчик 311 для последующей модуляции и передачи.

Следует отметить, что для информационных целей конкретный формат для S и чересстрочно чередованных P0 и P1 дан выше, и может быть задан несколькими способами. Например, даже если кольцевой буфер представлен, используя одномерный массив, часто для математических целей полезно использовать двухмерный матричный формат.

Если фиктивные биты оставляют в кольцевом буфере, его называют кольцевым буфером, заполненным фиктивными битами. Размер кольцевого буфера, заполненного фиктивными битами, равен суммированию размеров входного потока и общего числа вставленных фиктивных битов. Как будет ясно из контекста, кольцевой буфер, заполненный фиктивными битами, может быть в матричном формате, как изображено на фиг.5, или в формате последовательности (т.е. одномерный массив или поток данных), как изображено на фиг.2. Если фиктивные биты удалены, это называют кольцевым буфером с удаленными фиктивными битами. Размер кольцевого буфера с удаленными фиктивными битами равен суммированию размеров входного потока. Подобным образом, кольцевой буфер с удаленными фиктивными битами может быть представлен в матричном формате, как на фиг.6, где существуют разрывы, откуда удалены фиктивные биты, или в формате последовательности. RVs предшествующего уровня техники приблизительно равномерно распределены по кольцевому буферу с удаленными фиктивными битами, что делает это трудным, чтобы осуществлять каждую передачу HARQ, так как точное начальное положение RV в выходном потоке кодера необходимо вычислять, используя нетривиальные действия для каждого случая. Для того чтобы решить этот вопрос, может быть использован кольцевой буфер 307, заполненный фиктивными битами, чтобы определять начальное положение для варианта избыточности.

Следующий текст может быть полезен в последующем описании технологий согласования скорости.

Kинфо относится к размеру информационного блока (или длине пакета сообщения).

KFEC относится к размеру входного блока, поддержанного FEC кодером (KFEC равен размеру устройства перемежения для бинарного турбокода, и равен двойному размеру устройства перемежения для дуобинарного турбокода).

Kнаполнителя относится к числу битов наполнителя, добавленных к информационному блоку, чтобы получать входной размер, который обеспечен для FEC кодера.

Kнаполнителя=KFEC - Kинфо

Kпотока называется длина потока, которая равна немного больше, чем KFEC, в зависимости от способа обрыва решетки, использованного в турбокоде. Для 3GPP турбокода существует три потока, каждый длиной Kпотока=KFEC+4, состоящий из систематических битов, битов четности из первого и второго кодеров соответственно, и 12 хвостовых битов равномерно распределены на три потока.

Nr относится к числу рядов в устройстве перемежения подблоков, используемом в кольцевом буфере.

Nс относится к числу столбцов в устройстве перемежения подблоков, используемом в кольцевом буфере.

Krect=Nr×Nс является размерностью устройства перемежения подблоков, используемого в кольцевом буфере. Обычно Krect выбрана больше чем, или равная Kпотока, хотя может также быть выбрана больше чем или равная KFEC, если биты наполнителя отбрасывают как часть алгоритма согласования скорости.

Определение RV

Для пояснения, рассмотрим случай, когда устройство перемежения подблоков имеет 30 столбцов и 8 RVs должны быть определены. В этом случае, буфер на фиг.7 может иметь 90 столбцов, которые не могут быть равномерно разделены на восемь RVs. Трудно выяснить начальную точку каждого RV в выходном потоке кодера (за исключением RV0, если RV0 всегда начинается от начала кольцевого буфера). Предположим, что необходимо 8 равномерно распределенных RVs, тогда начальной точкой RVi является K потока×3/8×i (когда необходимо, доведена до целого значения посредством действий, таких как округление, округление в меньшую сторону или округление в большую сторону), если нет включения фиктивных битов (т.е. кольцевой буфер с удаленными фиктивными битами), i=0,1,...7. С другой стороны, если учитываются фиктивные биты (т.е. кольцевой буфер, заполненный фиктивными битами), тогда начальной точкой RVi является

N r×N с×3/8×i=N r×90/8×i

(когда необходимо, доведена до целого значения посредством действий, таких как округление, округление в меньшую сторону или округление в большую сторону). В любом случае, начальные точки 7 RVs почти всегда размещены в середине прямоугольника N r×90, если требуются равномерно распределенные начальные положения RVs. (Решением является, чтобы все начальные точки 7 RVs были в верхнем ряду прямоугольника N r×30, что ведет к немного неравномерному распределению RVs в буфере). Обратите внимание на следующее, если 30-столбцовые устройства перемежения подблоков применены в стандарте 3GPP долгосрочного развития сетей связи (LTE).

Если сохраняют начальные точки RVs, тогда должно быть сохранено общее число 188×7 начальных точек, определяя стоимость запоминающего устройства. Обратите внимание, что существует 188 QPP размеров устройства перемежения и 7 RVs, которые должны быть сохранены для каждого размера.

Если начальные точки RVs вычисляют в движении, тогда в аппаратном обеспечении должны быть запрограммированы трудные действия, чтобы выяснить указатели ряда и столбца точки в пределах прямоугольника систематических битов или прямоугольника из прямоугольника четности 0/четности 1. Например, если RV начинается с L-го указателя в пределах систематического потока, тогда существуют два действия:

- разделение, чтобы выяснить индекс столбца = округление в меньшую сторону(L /_N r), предполагая, что индекс столбца начинается с 0. Так как N r изменяется с K потока, если N с установлено 30 и N r вероятнее всего не в степени 2, разделение не является тривиальным в аппаратном обеспечении;

- взятие модуля, чтобы выяснить индекс ряда = по модулю(L,N с)= по модулю(L,30). Так как 30 не в степени 2, действие по модулю также не является тривиальным в аппаратном обеспечении.

Использование N с=30 в значительной степени способствует трудностям размещения RVs. Вместо этого, предпочтительно иметь общее число столбцов в буфере 307, которые будут кратны общему числу RVs, поддержанному, чтобы иметь равномерно распределенные RVs (хотя RVs по-прежнему могут быть определены неравномерно). Например, устройство перемежения подблоков может использовать 32 столбца, когда будут определены 8 RVs. Часто 2с RVs должны быть определены, где c является целым. Таким образом, пригодно для использования N с=2d, где d является целым, больше чем или равное c. Чтобы дополнительно уменьшить сложность и минимизировать количество фиктивных битов, предпочтительно использовать те же значения d для всех размеров информационных блоков системы. Например, постоянная d=5 (таким образом, N с=32 столбца) может быть использована для всех размеров информационных блоков 3GPP LTE.

Дополнительно, равномерно распределенные RVs могут быть определены, чтобы всегда начинались с вершин (т.е. первый ряд) столбцов устройств перемежения составных подблоков, если фиктивные биты не отброшены до определения начального положения RVs, тем самым, избегая сложные действия, такие как разделение и взятие модуля, обсужденные выше.

Если используют устройство перемежения подблоков с N с=32 при конфигурации межстолбцовой перестановки = {0, 16, 8, 24, 4, 20, 12, 28, 2, 18, 10, 26, 6, 22, 14, 30, 1, 17, 9, 25, 5, 21, 13, 29, 3, 19, 11, 27, 7, 23, 15, 31}, тогда то же число столбцов используют для всего K потока с числом рядов, изменяющимся с K потока,

N r=K потока/N с=K потока/32.

Так как RVs обычно требуются, чтобы разделять буфер 307 на приблизительно равномерные секции, требуется дополнительная вычислительная нагрузка, чтобы моделировать неравномерность в определении RV для каждого размера потока, если используют кольцевой буфер с удаленными фиктивными битами.

Для дополнительной ясности рассмотрим случай, когда число RVs=8, числом столбцов в устройстве перемежения подблоков является N с=32, и размером входного потока является K потока, и используют перестановку длиной 32 столбца в перемежении подблоков S, P0 и P1.

Фиг.6 показывает кольцевой буфер с удаленными фиктивными битами (т.е. после отбрасывания фиктивных битов) с определенными 8 RVs. Обратите внимание, что существуют разрывы, откуда отброшены фиктивные биты; кольцевой буфер с удаленными фиктивными битами в формате последовательности (может быть использован в буфере 307) получают считыванием по столбцам элементов матрицы от левого верхнего угла вперед. Отсутствие закономерности в распределении RVs в прямоугольнике служит причиной трудности в действии HARQ, где любое значение RV может быть введено в блок RM. Индексы ряда и столбца для начальной точки RV должны быть рассчитаны на основании размера потока (и числа фиктивных битов), таким образом, приводя к усложненному аппаратному обеспечению.

Другой способ облегчить действие HARQ с кольцевым буфером описан далее. В этом случае фиктивные биты отбрасывают, после того как определяют RVs, как показано на фиг.7. Фактически, фиктивные биты оставляют в кольцевом буфере (кольцевой буфер, заполненный фиктивными битами), и так как размер кольцевого буфера, заполненного фиктивными битами кратный 8, возможно определить восемь RVs, которые расположены на равном расстоянии для любого размера потока K потока. В частности, восемь RVs могут быть определены, чтобы начинались с вершины столбца устройства перемежения подблоков. Это пригодно, в общем, чтобы присвоить RVs в любом положении в первом ряду (т.е. с вершины столбца) устройства перемежения подблоков. Например, восемь RVs могут начинаться с вершины следующих восьми столбцов 2, 14, 26, 38, 50, 62, 74, 86 на фиг.7 (при N с=32). Когда рассматривается исходя из положения в кольцевом буфере, заполненном фиктивными битами, формата последовательности, варианты избыточности начинаются с положений

Kпотока/32(12×i+σ), i=0,1,...,7,

где σ указывает указатель столбца начального положения первого RV (RV0).

Обратите внимание, что это определение RV без запоминания для кольцевого буфера, заполненного фиктивными битами, в том смысле, что легко начать вывод требуемых битов кода от любого RV, не зная начального положения предыдущих RVs. Фиктивные биты отбрасывают, когда биты считывают из кольцевого буфера, заполненного фиктивными битами. Даже если общее число столбцов не кратно общему числу RVs, поддержанных, например, N с=30 с 8 RVs, RVs по-прежнему могут быть определены, чтобы начинались с вершины любых 8 из 90 столбцов.

Несмотря на то, что вершина столбца использована в обсуждении выше как простой способ, чтобы определить начальные положения RVs, другие пригодные положения могут быть использованы также. Например, все начальные положения RVs размещены в конкретном ряду r кольцевого буфера, заполненного фиктивными битами, где 0≤r<N r.

Обоснование для определения RVs по кольцевому буферу, заполненному фиктивными битами, дано ниже.

• Перестановка каждого потока (или устройство перемежения подблоков) описана как Krect=N r×N с прямоугольный массив с фиктивными битами.

○ Когда Kпотока=N r×N с, биты каждого потока вписывают в прямоугольник по рядам и считывают по столбцам (после столбцовой перестановки).

○ Когда Kпотока<N r×N с, биты каждого потока вписывают в прямоугольник по рядам и считывают по столбцам, и заполняют (N r×N с-Kпотока) фиктивными битами, чтобы наполнить прямоугольник. Фиктивные биты удаляют или «обрезают» до передачи по каналу.

• Следует отметить, что когда прямоугольник полный (используются фиктивные биты или нет), перестановка каждого потока имеет выражение в закрытом виде, которое означает, что легко установить обратную перестановку. Если легко установить обратную перестановку, следовательно, также легко установить положение в выходном потоке кодера, соответствующее конкретному RV. Если прямоугольник частично наполнен (нет фиктивных битов и Kпотока<N r×N с), перестановка каждого потока не имеет выражения в закрытом виде. В этом случае, трудно установить обратную перестановку и, следовательно, также трудно установить положение в выходном потоке кодера, соответствующее конкретному RV.

Для облегчения объяснения, в обсуждениях выше, предполагают, что кольцевой буфер 307 (с удаленными фиктивными битами или заполненный фиктивными битами) физически образуют, например, сохранением битов кольцевого буфера в запоминающем устройстве. Для аппаратного осуществления, лучше использовать принцип виртуального кольцевого буфера, который непосредственно генерирует требуемые выходные биты без образования физического кольцевого буфера 307. Другими словами, функциональное назначение согласования скорости выполняют без промежуточного сохранения. Этот принцип показан на фиг.8.

Промежуточный этап образования физического кольцевого буфера можно избежать нахождением алгебраического правила, чтобы легко генерировать требуемый участок физического кольцевого буфера без прохождения через весь способ образования физического кольцевого буфера.

В виртуальном кольцевом буфере, алгоритм согласования скорости инициализирует свой генератор адресов для подходящего начального значения, основанного на входных параметрах (число RVs и входной размер). Затем он непосредственно начинает вывод битов, следуя правилу генерации адресов, как описано перестановками подблоков входных потоков. Правило генерации адресов определяет последовательность положений в выходном потоке кодера, из которого выводят биты.

Виртуальный кольцевой буфер может быть задействован как кольцевой буфер, заполненный фиктивными битами, так и кольцевой буфер с удаленными фиктивными битами. Однако если используют кольцевой буфер с удаленными фиктивными битами, тогда RVs могут начинаться где-нибудь в кольцевом буфере (в матричном формате), как изображено на фиг.6. Исходя из этого, в таком плане действий, начальные точки RVs возможно должны быть явно сохранены, определяя стоимость запоминающего устройства. С другой стороны, начальные точки RVs могут быть получены для каждого случая, но инициализация адресов в действии виртуального кольцевого буфера становится усложненной, чтобы осуществляться в аппаратном обеспечении.

В противоположность этому, чтобы задействовать виртуальный кольцевой буфер, когда используется кольцевой буфер, заполненный фиктивными битами, RVs начинаются с вершины столбцов устройства перемежения подблоков и, исходя из этого, инициализация адресов в действии виртуального кольцевого буфера становится эффективной. Всякий раз, когда генератор адресов отмечает фиктивный бит, генератор адресов автоматически продвигают вперед без вывода бита.

Определение RV с согласованием скорости 1-й стадии

Технология согласования скорости 1-й стадии может быть необходима, когда приемник имеет ограниченную величину размера программного буфера. В согласовании скорости 1-й стадии, передатчик может иметь знание возможности программного буфера передатчика и, исходя из этого, разрешено передавать биты кода только не больше, чем может быть сохранено в программном буфере приемника.

Максимальный размер программного буфера может налагать некоторое ограничение на согласование скорости с кольцевым буфером. В частности, кольцевой буфер для каждого блока кода может быть дополнительно ограничен, как показано на фиг.9. В этом случае, циклический возврат в кольцевом буфере может происходить с более ранней точки, чем конец кольцевого буфера.

Обычно, если ввод (транспортный блок или каскадный транспортный блок) в турбокодер больше, чем максимальный размер, поддержанный турбоустройством перемежения, тогда TB делят на многократные сегменты блока кода, каждый из которых по отдельности турбокодируют и согласуют скорость, таким образом, позволяя действие с конвейерной обработкой. Поэтому каждый сегмент может иметь свой собственный кольцевой буфер (или виртуальный кольцевой буфер) (Обратите внимание, что нет необходимости создавать физический кольцевой буфер для каждого сегмента). Предположим, что NIR является общим размером программного буфера за процесс HARQ (или максимальный размер буфера, соответствующий TB).

Если согласование скорости выполняют на основе кодовое слово за кодовым словом (т.е. сегмент за сегментом), предпочтительно, что согласование скорости 1-й стадии, если включено, будет также выполнено на основе кодовое слово за кодовым словом (сегмент за сегментом). Размер кольцевого буфера для каждого кодового слова (или сегмента) ограничен до Ncw, где Ncw<3×Kпотока, и 3×Kпотока=3×Kинфо+12 полный размер кольцевого буфера (на сегмент) до согласования скорости 1-й стадии. Обратите внимание, что когда Ncw≥3×Kпотока, RM первой стадии (на сегмент) прозрачное. Суммирование размера Ncw для всех кодовых слов (из всех транспортных блоков) не может превышать NIR, которое является размером программного буфера всех TBs. Вместо взятых NIR, как ввод в алгоритм RM 1-й стадии, RM 1-й стадии RM на кодовое слово в LTE может взять Ncw, как ввод.

Возможные варианты для согласования скорости 1-й стадии могут включать в себя:

1. Ограничение размера буфера до максимального значения набора для класса UE (по всем TBs, всем кодовым словам данных TTI. Класс оборудования пользователя (UE) определяет набор возможностей передатчика/приемника в 3GPP и 3GPP LTE.). Определить предел на TB и на кодовое слово от NIR посредством масштабирования. Например, Ncw= округление в меньшую сторону (NIR/C), где C является числом турбокодовых слов для каскадных TBs, установленным правилом деления на сегменты блоков кода. Возможно установить предел на кодовое слово способом, подобным правилу деления на сегменты блоков кода;

2. Ограничение буфера до максимального значения N′IR набора для класса UE (установите предел на TB). Определить предел на кодовое слово от этого максимального значения посредством масштабирования;

3. Ограничение буфера до максимального значения набора на кодовое слово для класса UE.

При любом из этих трех возможных вариантов, предел на кодовое слово может быть определен удалением целых столбцов из виртуального кольцевого буфера (в отдельных сегментах).

Для определений RV, варианты включают в себя:

Схема 1. Позволяет только подмножество возможных RVs. Если Y RVs определяют без согласования скорости 1-й стадии (т.е. согласование скорости 1-й стадии прозрачное), тогда Y′ RVs из Y доступных RVs может быть оставлено, когда согласование скорости 1-й стадии не прозрачное, Y′<=Y. Например, RV-i, i=0,1,...,Y′-1, используют, где начальная точка RV - Y′ меньше, чем Ncw.

Схема 2. Переопределяет RVs так, что полный набор Y RVs является доступным внутри позволенного максимального размера кольцевого буфера. RVs переопределяют так, что они начинаются с вершины столбцов кольцевого буфера с вставленными фиктивными битами. Количество пунктирования систематических битов не изменяется, так что RV0 начинается в одинаковых положениях для всех классов UE. Например, если Ncol столбцов кольцевого буфера, заполненного фиктивными битами (содержащего 3×Nc столбцов до согласования скорости 1-й стадии), остается после согласования скорости 1-й стадии, тогда Y RVs могут начинаться с вершин столбцов указателя столбца округление в меньшую сторону ((Ncol-2)/Y)×i+2, i=0,1,...,Y-1.

Начальные точки RVs могут также быть определены на основе кодового слова, несмотря на то, что предпочтительно передать сигнал единственного RV на TB для эффективного действия HARQ.

Пунктирование систематических битов

Определение RV, обсужденное выше, может быть усовершенствовано, чтобы приспособить технологию увеличения быстродействия, названную систематическим пунктированием.

Хорошо известно в литературе, что частично систематические турбокоды могут превосходить систематические турбокоды, являясь одним простым объяснением того, что последнее является подмножеством первого. Однако пунктирование систематических битов не используют в алгоритме согласования скорости в существующих беспроводных стандартах, таких как WCDMA или CDMA2000 турбокодирование. Основная причина этого в том, что предпочтительно, чтобы передача (с RV0) была самодекодируемой, когда эффективная скорость кодирования высокая.

Пунктирование систематических битов используют, чтобы избежать чрезмерного пунктирования битов четности, которое, в противном случае, приведет к недостаточным минимальным расстояниям при более высоких скоростях кодирования и, следовательно, плохому быстродействию.

В системах связи, таких как 3GPP, скорости кодирования, возможно, могут быть до 5/6 (или даже выше) и, исходя из этого, такие системы должны быть способны обходиться малой долей пунктирования систематических битов. Обратите внимание, такие частично систематические коды по-прежнему являются самодекодируемыми. Для турбокода с размером блока Kинфо, пусть ∆K(R) обозначают долю систематических битов, которые выкалывают при кодовой скорости R.

Тогда в разрабатываемом согласовании скорости существует одна проблема, чтобы найти оптимальные значения ∆K(R) для всех действенных сочетаний Kинфо и R. После того как ∆K(R) установлено, кольцевой буфер может быть реконфигурирован, чтобы включать в себя пунктирование систематических битов. Существует много возможных вариантов реконфигурации, как показано на фиг.10. В обсуждении систематического пунктирования, кольцевой буфер в формате последовательности используют, чтобы изобразить технологии, и кольцевой буфер может быть заполненный фиктивными битами или с удаленными фиктивными битами. В следующих примерах предполагают, что основная кодовая скорость 1/3, и биты всегда берут последовательно, начиная от первого бита в кольцевом буфере. Как упоминалось, Kинфо обозначает размер информационного блока, Kпотока обозначает длину потока.

1. Возможный вариант 1 на фиг.10 описывает обычный кольцевой буфер в формате последовательности, где все систематические биты передают первыми, за которыми следуют несколько или все биты четности.

2. Возможный вариант 2 на фиг.10 содержит такие же биты, как обычный кольцевой буфер, но кольцевой буфер видоизменяют; несколько систематических битов (SA) берут из систематического участка кольцевого буфера и располагают в конце буфера. Поэтому, в первой передаче, систематические биты в SA выкалывают при многих кодовых скоростях. Возможный вариант 2 также может быть достигнут просто располагая RV0 в начале участка со смещением относительно начала кольцевого буфера. Это смещение может быть установлено на основании требуемого количества пунктирования систематических битов. Для кодовой скорости R>=Kинфо/(3×L-SA), систематические биты в SA всегда выкалывают.

3. Возможный вариант 3 такой же, как возможный вариант 2, в котором кольцевой буфер видоизменяют. Однако систематические биты (SA), взятые из систематического участка кольцевого буфера располагают в буфере после битов X из потоков четности. Поэтому, в первой передаче, несколько систематических битов выкалывают при многих кодовых скоростях. Для кодовой скорости R>=Kинфо/(SB+X), систематические биты в SA всегда выкалывают.

а. С кодовой скоростью Kинфо/(SB+X)>R>Kинфо/(SB+X+SA), часть систематических битов в SA выкалывают.

б. Для кодовой скорости Kинфо/(SB+X+SA)>=R, все систематические биты передают.

4. Возможный вариант 4 такой же, как возможный вариант 3, в котором кольцевой буфер видоизменяют. Однако систематические биты (SA), взятые из систематического участка кольцевого буфера, распределяют в кольцевом буфере в некотором интервале. Поэтому, в первой передаче, несколько систематических битов выкалывают при многих кодовых скоростях. Возможный вариант 4 позволяет больше гибкости в разработке кольцевого буфера, оптимизируя соотношение систематического пунктирования ∆K(R). Например, систематические биты в (SA) могут быть равномерно распределены в пределах интервала; или они распределены с увеличивающейся плотностью систематических битов в пределах интервала; или они распределены с уменьшающейся плотностью систематических битов в пределах интервала.

Другие разновидности возможных вариантов существуют в вышеперечисленных. Например, систематические биты в (SA) не могут быть размещены перед перемеженным подблоками систематическим потоком S′, скорее в середине или в конце S′. Они также могут быть взяты из дискретных местоположений S′, таких как один бит для каждых x битов S′, x>1.

Хотя новое видоизменение показано как дополнительный этап, выполненный после образования кольцевого буфера, этот этап можно было бы объединить непосредственно с определением кольцевого буфера.

Другие возможные варианты имеют другие соотношения сложность/быстродействие. Возможный вариант 2 не может быть предпочтительным, когда пунктирование систематических битов установлено для всех скоростей почти близких к 1/3. Моделирования предлагают, что для LTE, пунктирование систематических битов около 5% может быть предпочтительно для высоких скоростей, таких как 3/4 или 5/6, тогда как 0% предпочтительно для более низких скоростей кодирования, таких как 2/3 или 1/2. Поэтому может быть предпочтительно располагать систематические биты в участках буфера, как продиктовано такими причинами. С другой стороны, предложено использовать RV7 в низкой скорости кодирования, чтобы выключить пунктирование систематических битов.

Несмотря на то, что обсуждение сосредоточено на разработке согласования скорости для первой передачи (таким образом, FEC), подобным образом реконфигурированный кольцевой буфер может быть использован в контексте HARQ с многократными передачами на информационный блок. Другие варианты избыточности для передачи HARQ могут быть получены взятием других секций реконфигурированного кольцевого буфера, где размер секции равен длине, требуемой для текущей передачи по физическому каналу. В частности, если необходимы Y вариантов избыточности (RVs), существует простой способ, чтобы определить Y других начальных точек (A0, A1,..., AY-1) в пределах реконфигурированного кольцевого буфера, одна для варианта избыточности. Для RVi биты берут из Ai в по модулю (Ai+Ntx,NCB), где i=0,1,...,Y-1 и Ntx является числом битов, требуемых для передачи, NCB является длиной кольцевого буфера. Другими словами, Ntx битов считывают, начиная с положения Ai, циклически возвращаясь к началу кольцевого буфера, если доходят до конца буфера. Для данного информационного блока, Ntx может быть другим для каждой передачи.

Определение RV с систематическим пунктированием

Объединяя (а), определение RV, основанное на кольцевом буфере, заполненном фиктивными битами и (б), систематическое пунктирование, улучшенная разработка согласования скорости имеет следующие преимущества, используя N с =32 и основную кодовую скорость 1/3 (т.е. три потока из турбокодера 101) для изображения:

- фиктивные биты включены в кольцевой буфер, чтобы облегчить определение RV (т.е. кольцевой буфер, заполненный фиктивными битами);

- легко начать каждый RV для повторной передачи HARQ. Например, RVs определяют, чтобы начинались с вершины (т.е. первый ряд) столбцов устройства перемежения подблоков в кольцевом буфере матричного формата. Более конкретно;

- если 8 RVs должны быть определены, RVi начнется с положения

N r×(N с ×3/8×i+σ)=N r×(12×i+σ)=Kпотока/32(12×i+σ), i=0,1,...,7,

в кольцевом буфере, заполненном фиктивными битами формата последовательности. В матричном формате, RVi начинается с вершины (12×i+σ)-го столбца;

- если определяют только 4 RVs, каждый RV начинается с вершины (24×i+σ)-го столбца (с σ =2). Равнозначно, в формате последовательности, RVi начинается с битового положения

N r×(N с ×3/4×i+σ)= N r×(24×i+σ)=Kпотока/32(12×i+σ), i=0,1,...,3.

Когда σ=0 (по модулю 3×N с), RV0 начнется с начала кольцевого буфера, таким образом, нет пунктирования систематических битов. Пунктирование систематических битов может быть включено установкой σ, величина которой будет больше чем 0 (по модулю 3×N с) для 3 потоков (т.е. основная кодовая скорость 1/3), таким образом, пропуская малую долю систематических битов при считывании битов для RV0. Другими словами, RV0 (первый вариант избыточности) определяют, чтобы начинался с вершины σ-го столбца, где σ является числом смещенных столбцов. Это показано на фиг.11. Например, RV0 может быть определен, чтобы начинался от столбца #2, вместо столбца #0 посредством установки σ=2. Другие значения σ могут также быть рассмотрены.

Улучшенная разработка, обсужденная выше, может иметь несколько разновидностей. Некоторые из которых следующие:

- несмотря на то, что используют 32 столбца в предложенной разработке, другие значения могут быть использованы как Nс, особенно 2 в степени, такие как 8, 16, 64 или 128;

- несмотря на то, что в примере разработки используют конкретную столбцовую перестановку, может быть использована другая перестановка, чтобы также переставлять столбцы;

- если в разработке согласования скорости используют два или более Nс, тогда каждое Nс может быть использовано для многочисленных размеров устройства перемежения;

- устройство перемежения подблоков не может быть одним и тем же для всех потоков. Например, устройство перемежения подблоков может быть тем же для потоков как систематического, так и четности 1, но устройство перемежения подблоков потока четности 2 может быть другим;

- несмотря на то, что для облегчения описания, RVs определяют, чтобы начинались с вершин столбцов устройства перемежения подблоков, они также могут быть определены, чтобы начинались с других пригодных местоположений в кольцевом буфере, заполненном фиктивными битами. Например, все RVs могут начинаться в том же ряду r устройств перемежения составных подблоков, где 0≤r≤N r.

Определение RV с согласованием скорости 1-й стадии и систематическим пунктированием

Когда используют как систематическое пунктирование, так и согласование скорости 1-й стадии, определение RV возможно должно быть видоизменено, чтобы удовлетворить следующие требования:

- облегчение определения RV посредством включения фиктивных битов в кольцевой буфер (т.е. кольцевой буфер, заполненный фиктивными битами);

- облегчение начала генерации адресов для каждого RV для повторной передачи HARQ. Например, RVs можно было бы определить, чтобы начинались с вершин столбцов устройства перемежения подблоков (т.е. первого ряда в столбце устройства перемежения подблоков) в кольцевом буфере матричного формата;

- оставление начальных положений RVs в пределах интервала кольцевого буфера, который ограничивает после согласования скорости 1-й стадии.

Когда используют как систематическое пунктирование, так и согласование скорости 1-й стадии, осуществление может быть изображено как следующее. Сначала, согласование скорости 1-й стадии достигается удалением одного или более столбцов (предпочтительно от последнего столбца виртуального кольцевого буфера) из кольцевого буфера, чтобы образовать укороченный кольцевой буфер. Таким образом, систематические биты могут быть выколоты посредством определения первого варианта избыточности, чтобы начинался в положении со смещением относительно начала укороченного кольцевого буфера. Другими словами, пунктирование систематических битов может быть достигнуто посредством определения RV0 с некоторым не нулевым числом столбца в устройстве перемежения подблоков устройства перемежения систематических подблоков. Обратите внимание, что вышеупомянутые этапы могут быть также непосредственно объединены. И снова согласование скорости первой стадии может быть рассмотрено, как примененное на основе на кодовое слово (на сегмент). Для удобства, укороченный кольцевой буфер также относят как кольцевой буфер после того, как применено согласование скорости 1-й стадии. Это различие должно быть ясно из контекста.

Например, если 8 RVs используют как исходные данные (когда отсутствует RM 1-й стадии), тогда следующие возможные варианты доступны для определения RVs с RM 1-й стадии.

- При схеме 1 определения RV, начальные положения 8 RVs могут быть оставлены, но не обязательно использованы всегда. Могут быть позволены только исходные начальные положения RVs, которые лежат в пределах интервала (0≤j≤Ncw-1) в кольцевом буфере. Это также может быть установлено, используя следующее условие: используют только RV-i с N r×σ<= N r(12×i+σ)<= Ncw-1, в некоторых случаях получая в результате возможно меньше чем 8 RVs. Последним позволенным указателем i для RVs является, таким образом, округление в меньшую сторону (((Ncw-1)/N r-σ)/12).

- При схеме 2 определения RV, 8 RVs по-прежнему необходимы (во всех случаях), тогда начальные положения RVs могут быть N r(C×i+σ), i=0,1,...,7, где C является максимальным целым, таким что N r(C×i+σ)<= Ncw-1. Другими словами, C= округление в меньшую сторону (((Ncw-1)/N r-σ)/7).

В обсуждении выше, C указывает число столбцов между двумя соседними RVs, Y является числом определенных RVs.

Подобное видоизменение RV может быть применено, если другое число (например, 4) RVs определяют до согласования скорости 1-й стадии. Например, если 4 RVs используют как исходные данные (когда отсутствует RM 1-й стадии), тогда следующие возможные варианты доступны для определения RVs с RM 1-й стадии.

Без согласования скорости 1-й стадии, в кольцевом буфере, заполненном фиктивными битами, формата последовательности RV-i начинается с положения N r×(N c×3/4×i+σ)=N r×(24×i+σ), i=0,1,2,3. После того как использовано согласование скорости 1-й стадии, кольцевой буфер содержит биты участка j, где 0≤j≤Ncw-1.

• При схеме 1 определения RV, начальные положения 4 RVs оставляют, тогда используют только RV-i с N r×2<=N r×(24×i+σ)<=Ncw-1, получая в результате возможно меньше чем 4 RVs.

• При схеме 2 определения RV, 4 RVs по-прежнему необходимы, тогда начальные положения RVs могут быть N r×(C×i+2), i=0,1,2,3, где C является максимальным целым, таким что N r×(C×i+σ)<=Ncw-1.

Фиг.12 является блок-схемой последовательности операций способа, показывающей действие передатчика фиг.3. В частности, логическая последовательность операций способа фиг.12 показывает этапы для присвоения вариантов избыточности кольцевому буферу 307, и последующей передачи битов из кольцевого буфера 307. Логическая последовательность операций способа начинается как этап 1201, где логическая схема 305 принимает систематические биты, первый блок битов четности и второй блок битов четности. Эти биты являются выводом из кодера 301. Как обсуждалось выше, систематические биты, первый блок битов четности и второй блок битов четности все содержат фиктивные биты. Логическая схема 305 по отдельности блокирует перемежение систематических битов, первый блок битов четности и второй блок битов четности, используя устройство 309 перемежения (этап 1203). На этапе 1205, логическая схема 305 чересстрочно чередует первый блок битов четности со вторым блоком битов четности и присоединяет спереди перемеженные систематические биты к чересстрочно чередованным битам четности, чтобы создать кольцевой буфер 307. Затем на этапе 1207, логическая схема 305 определяет варианты избыточности в пределах конкретного ряда кольцевого буфера. В одном варианте осуществления настоящего изобретения, конкретный ряд содержит верхний ряд кольцевого буфера, например 8 или 4 вершин столбцов устройства перемежения подблоков. Логическая схема 305 принимает вариант избыточности и число требуемых битов (этап 1209) и выводит в передатчик число требуемых битов, начиная с битового положения RV (этап 1211).

Фиг.13 является блок-схемой последовательности операций способа, показывающей действие передатчика фиг.3. В частности, логическая последовательность операций способа фиг.13 показывает этапы для присвоения вариантов избыточности виртуальному кольцевому буферу, и последующей передачи битов из виртуального кольцевого буфера. Логическая последовательность операций способа начинается как этап 1301, где логическая схема 305 принимает систематические биты, первый блок битов четности и второй блок битов четности. Как обсуждалось выше, систематические биты, первый блок битов четности и второй блок битов четности все содержат фиктивные биты. Логическая схема 305 по отдельности блокирует перемежения систематических битов, первый блок битов четности и второй блок битов четности, используя устройство 309 перемежения (этап 1303). На этапе 1305, логическая схема 305 чересстрочно чередует первый блок битов четности со вторым блоком битов четности и присоединяет спереди перемеженные систематические биты к чересстрочно чередованным битам четности. Затем на этапе 1307, логическая схема 305 определяет варианты избыточности, соответствующие битовым положениям в пределах потока данных и где все возможные RVs находятся в положениях

Kпотока/32(13×i+σ), i=0,1,...,7

и где σ указывает указатель столбца начального положения первого RV (RV0). Поток данных содержит перемеженные систематические биты, и чересстрочно чередованные первый блок перемеженных битов четности и второй блок перемеженных битов четности. Логическая схема 305 принимает вариант избыточности и число требуемых битов (этап 1309) и выводит в передатчик число требуемых битов, начиная с битового положения RV (этап 1311).

Хотя изобретение, в частности, показано и описано со ссылкой на конкретный вариант осуществления, специалистам в данной области техники будет понятно, что различные изменения в форме и деталях могут быть произведены в нем без отступления от существа и объема изобретения.

В одном примере, несмотря на то, что метод объяснен, фиктивные биты не могут быть добавлены в потоки и позже удалены из кольцевого буфера, скорее такое же действие реализуют другими способами, такими как правильное генерирование адресов.

В другом примере, начальные RVs из конкретного ряда (например, вершин столбцов) кольцевого буфера могут быть равнозначными, чтобы начинать RVs из конкретного ряда в устройствах перемежения подблоков для каждого потока, при присутствии фиктивных битов. Преобразование начальных точек для их местоположений в пределах устройства перемежения подблоков может быть более пригодным для некоторого осуществления, тогда как определение начальных точек RVs в кольцевом буфере может быть более пригодным для других осуществлений.

Предполагается, что такие изменения входят в объем следующей формулы изобретения.

Изобретение относится к системам связи и, в частности, к способу и устройству для присвоения вариантов избыточности кольцевому буферу в пределах системы связи. Во время действия передатчика создают кольцевой буфер, где только вершины столбцов кольцевого буфера определяют как начальное положение для варианта избыточности. Когда кольцевой буфер находится в формате последовательности, все возможные варианты избыточности расположены как функция индекса столбца начального положения первого варианта избыточности. Технический результат - улучшение эффективности кольцевого буфера на основе алгоритма согласования скорости. 2 н. и 17 з.п. ф-лы, 13 ил.

1. Способ для присвоения вариантов избыточности кольцевому буферу, содержащий этапы, на которых:

принимают систематические биты, первый блок битов четности и второй блок битов четности, при этом систематические биты, первый блок битов четности и второй блок битов четности - все содержат фиктивные биты;

по отдельности блоками перемежают систематические биты, первый блок битов четности и второй блок битов четности;

чересстрочно чередуют первый блок битов четности со вторым блоком битов четности, чтобы создать чересстрочно чередованные биты четности;

присоединяют спереди перемеженные систематические биты к чересстрочно чередованным битам четности, чтобы создать кольцевой буфер;

удаляют один или более столбцов из кольцевого буфера для формирования укороченного кольцевого буфера;

определяют варианты избыточности для начала в конкретном ряду укороченного кольцевого буфера;

принимают вариант избыточности (RV) и число требуемых битов; и

выводят число требуемых битов, начиная с битового положения RV.

2. Способ по п.1, дополнительно содержащий этап, на котором определяют варианты избыточности для начала с вершин столбцов укороченного кольцевого буфера.

3. Способ по п.2, в котором этап, где определяют варианты избыточности, для начала с вершин столбцов укороченного кольцевого буфера содержит этап, где определяют варианты избыточности, для начала с 8 вершин столбцов укороченного кольцевого буфера.

4. Способ по п.2, в котором этап, где определяют варианты избыточности, для начала с вершин столбцов укороченного кольцевого буфера содержит этап, где определяют варианты избыточности, для начала с 4 вершин столбцов укороченного кольцевого буфера.

5. Способ по п.2, дополнительно содержащий этап, на котором определяют первый вариант избыточности, для начала с вершины σ-ого столбца, где σ является числом смещенных столбцов.

6. Способ по п.2, дополнительно содержащий этап, на котором

выкалывают систематические биты посредством определения первого варианта избыточности, для начала в положении со смещением относительно начала укороченного кольцевого буфера.

7. Способ по п.1, в котором этап, где выводят требуемые биты, начиная с битового положения RV, включает в себя этап, где циклический возврат в кольцевом буфере может происходить с более ранней точки, чем конец кольцевого буфера.

8. Способ по п.1, в котором этап, где удаляют один или более столбцов, содержит этап, где удаляют столбцы из последнего столбца кольцевого буфера.

9. Способ по п.1, в котором этап, где удаляют один или более столбцов, содержит этап, где определяют размер буфера на сегмент на основании округления в меньшую сторону (NIR/C), где С является числом сегментов транспортного блока, определенного посредством правила деления на сегменты блоков кода, причем NIR является общим размером программного буфера за процесс гибридного автоматического запроса повторной передачи (HARQ).

10. Устройство для присвоения вариантов избыточности кольцевому буферу, содержащее:

кодер, выводящий систематические биты, первый блок битов четности и второй блок битов четности;

схему согласования скорости, принимающую систематические биты, первый блок битов четности и второй блок битов четности и создающую кольцевой буфер, имеющий фиктивные биты, и при этом конкретный ряд кольцевого буфера содержит начальные точки вариантов избыточности (RVs), и при этом схема согласования скорости удаляет один или более столбцов из кольцевого буфера для формирования укороченного кольцевого буфера, и при этом схема согласования скорости выводит нефиктивные биты из укороченного кольцевого буфера в передатчик, начиная с конкретного RV;

схему передачи, принимающую нефиктивные биты и передающую нефиктивные биты.

11. Устройство по п.10, в котором 8 вершин столбцов укороченного кольцевого буфера определяют как начальное положение для варианта избыточности (RV).

12. Устройство по п.10, в котором 4 вершины столбцов укороченного кольцевого буфера определяют как начальное положение для варианта избыточности (RV).

13. Устройство по п.10, в котором укороченный кольцевой буфер содержит перемеженные систематические биты, перемеженные и чересстрочно чередованные первый и второй блоки битов четности.

14. Устройство по п.10, в котором схема согласования скорости начинает первый вариант избыточности с вершины σ-го столбца, где σ является числом смещенных столбцов.

15. Устройство по п.10, в котором схема согласования скорости определяет варианты избыточности для начала с вершин столбцов укороченного кольцевого буфера.

16. Устройство по п.15, в котором схема согласования скорости выкалывает систематические биты посредством определения первого варианта избыточности для начала в положении со смещением относительно начала укороченного кольцевого буфера.

17. Устройство по п.10, в котором схема согласования скорости выводит биты, начиная с битового положения RV, включая в себя циклический возврат в кольцевом буфере, который происходит с более ранней точки, чем конец кольцевого буфера.

18. Устройство по п.10, в котором схема согласования скорости, которая удаляет один или более столбцов, удаляет столбцы из последнего столбца кольцевого буфера.

19. Устройство по п.10, в котором схема согласования скорости определяет размер буфера на сегмент на основании округления в меньшую сторону (NIR/C), где С является числом сегментов транспортного блока, определенного посредством правила деления на сегменты блоков кода, причем NIR является общим размером программного буфера за процесс гибридного автоматического запроса повторной передачи (HARQ).

| US 7180952 В1, 20.02.2007 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| US 2007098110 A1, 03.05.2007 | |||

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДАННЫХ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2002 |

|

RU2251804C2 |

Авторы

Даты

2012-11-20—Публикация

2008-06-17—Подача