УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

Область техники, к которой относится изобретение

Настоящее изобретение относится к способу и устройству процесса согласования скорости, чтобы улучшить работу гибридного автоматического запроса на повторение (HARQ), а конкретнее к способу и устройству процесса согласования скорости в работе гибридного автоматического запроса на повторение (HARQ), в котором кодированные биты выбирают для передачи в зависимости от того, несет ли передача первую передачу нового пакета или повторную передачу для существующего пакета.

Описание предшествующего уровня техники

В настоящее время гибридный автоматический запрос на повторение (HARQ) широко используют в системах связи для борьбы с ошибками декодирования и повышения надежности передачи данных. В системе передачи данных каждый пакет данных защищен с использованием определенной схемы кодирования с прямым исправлением ошибок (FEC). Каждый подпакет может содержать только часть кодированных битов полного пакета. Процесс выбора кодированных битов в подпакете, которые должны быть переданы, называется формированием подпакетов, или согласованием скорости.

В современной работе HARQ пакет данных кодируют с использованием кодера с определенным видом схемы прямого исправления ошибок (FEC). Пакет данных обрабатывают этапом формирования подпакетов/согласования скорости, а затем формируют набор подпакетов. Подпакет, например подпакет k, может содержать только часть кодированных битов. Если передача приемопередатчиком для подпакета k не удается, что указано сообщением с отрицательным подтверждением (NAK), предоставленным каналом подтверждения по обратной связи, то предоставляют подпакет повторной передачи, подпакет k+1, для повторения приемопередачи этого пакета данных. Если подпакет k+1 успешно передан и принят, то каналом подтверждения по обратной связи предоставляется сообщение с подтверждением приема (ACK). Подпакеты повторной передачи могут содержать разные кодированные биты из одного подпакета. Приемник легко может объединять или одновременно декодировать все принятые подпакеты с помощью декодера, чтобы повысить вероятность декодирования. Обычно максимальное количество передач пакета конфигурируют с учетом надежности, задержки пакета и сложности реализации.

N-канальный синхронный гибридный автоматический запрос на повторение (HARQ) широко используют в системах беспроводной связи из-за простоты N-канального синхронного гибридного автоматического запроса на повторение (HARQ). Например, синхронный гибридный автоматический запрос на повторение (HARQ) принят в качестве схемы гибридного автоматического запроса на повторение (HARQ) для восходящей линии связи системы долгосрочного развития (LTE) в Проекте партнерства третьего поколения (3GPP).

Из-за фиксированной временной зависимости между последующими передачами временные интервалы передачи в отдельном канале гибридного автоматического запроса на повторение (HARQ) проявляют чередующуюся структуру. Когда пакет правильно декодирован, приемник отправляет обратно подтверждение приема (АСК) передатчику. Передатчик тогда начинает передачу нового пакета в следующий временной интервал в текущем чередовании. В противном случае передатчик принимает отрицательное подтверждение (NAK) от приемника и передатчик передает другой подпакет из того же пакета в следующий временной интервал в текущем чередовании. Непохожий на синхронный гибридный автоматический запрос на повторение (HARQ), асинхронный гибридный автоматический запрос на повторение (HARQ) может использоваться для обеспечения большей гибкости в планировании и мультиплексировании разных пользователей. С помощью асинхронного гибридного автоматического запроса на повторение (HARQ) интервал времени между передачами одного и того же пакета может быть нефиксированным. У передатчика есть свобода в принятии решения, когда пакет повторно передавать.

Если схемы выделения ресурса или модуляции могут быть изменены во время повторных передач, то работа гибридного автоматического запроса на повторение (HARQ) является адаптивной. В системах долгосрочного развития (LTE) работа гибридного автоматического запроса на повторение (HARQ) может быть одновременно асинхронной и адаптивной. Иногда приемник может испытывать сложности в определении границы пакета, то есть сложность в определении, является ли подпакет первым подпакетом нового пакета, который должен быть передан, или подпакетом повторной передачи из предыдущего пакета. Чтобы смягчить эту проблему, в канале управления может передаваться индикатор нового пакета, который несет информацию о формате передачи для пакета. Иногда более подробная версия информации о канале гибридного автоматического запроса на повторение (HARQ), например идентификатор подпакета (ID) или даже ID канала гибридного автоматического запроса на повторение (HARQ), может передаваться для помощи приемнику в обнаружении и декодировании пакета.

В системе долгосрочного развития (LTE), когда размер транспортного блока большой, транспортный блок сегментируют на несколько кодовых блоков, чтобы можно было сформировать несколько кодированных пакетов, что является выгодным из-за таких преимуществ, как предоставление возможности реализации конвейерной или параллельной обработки и гибкий компромисс между потреблением энергии и сложностью аппаратных средств. В случае нескольких кодовых блоков процесс согласования скорости может выполняться для каждого кодового блока. Во время процесса согласования скорости функциональны средства гибридного автоматического запроса на повторение (HARQ) выбирают количество битов на выходе кодера канала для совпадения с общим количеством битов, которое может транспортировать физический канал. Функциональные средства гибридного автоматического запроса на повторение (HARQ) управляется параметрами версии избыточности (RV). Точный набор битов на выходе функциональных средств гибридного автоматического запроса на повторение (HARQ) зависит от количества входных битов, количества выходных битов и параметров версии избыточности (RV). Процесс согласования скорости на основе кольцевого буфера принят в системах долгосрочного развития (LTE).

Каждый кодовый блок C на выходе турбо-кодера может быть разделен на поток S систематических битов, первый поток P1 четности и второй поток P2 четности. Могут быть описаны четыре версии избыточности (RV), каждая из которых задает начальный индекс бита в буфере. Передатчик выбирает одну RV для каждой передачи с гибридным автоматическим запросом на повторение (HARQ). Передатчик считывает блок кодированных битов из буфера, начиная с индекса бита, заданного выбранной RV, наряду с удалением заполняющих битов и фиктивных битов. Если достигается максимальная емкость буфера и для передачи нужно больше кодированных битов, то передатчик обходит по кругу и продолжает с начала буфера, поэтому образуется термин "кольцевой буфер".

Согласование скорости на основе кольцевого буфера может быть реализовано в системе долгосрочного развития (LTE) для совместно используемого канала нисходящей линии связи (DL_SCH) и совместно используемого канала восходящей линии связи (UL_SCH).

Однако иногда приемник может испытывать сложности в обнаружении границы пакета, то есть сложность в определении того, является ли подпакет первым подпакетом нового пакета или подпакетом повторной передачи. Сбои в информировании приемника о передаче нового пакета могут либо ухудшать эффективность передачи пакета и скорость кодирования из-за повторной передачи, либо вызывать ухудшение качества принятого пакета.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Поэтому одной особенностью настоящего изобретения является предоставление способа и устройства процесса согласования скорости, чтобы улучшить эффективность работы гибридного автоматического запроса на повторение (HARQ).

Другой особенностью настоящего изобретения является предоставление способа и устройства процесса согласования скорости в работе гибридного автоматического запроса на повторение (HARQ), в котором кодированные биты выбирают для передачи пакета в зависимости от того, является ли эта передача первой передачей нового пакета или повторной передачей для существующего пакета.

В одном варианте осуществления настоящего изобретения группа кодированных битов, выбранных для передачи, зависит от того, является ли передача первой передачей нового пакета или повторной передачей для существующего пакета. Поэтому группа кодированных битов, выбранных для передачи пакета, не только зависит от версии избыточности, но также от того, является ли передача первой передачей пакета.

В другом варианте осуществления настоящего изобретения в нисходящей линии связи системы долгосрочного развития (LTE) сообщение предоставления нисходящей линии связи передают вместе с передачей пакетных данных. Сообщение предоставления может содержать версию избыточности (RV) и индикатор новых данных (NDI) для указания начала нового пакета. Цель указания RV - позволить приемнику правильно установить, где в кольцевом буфере следует разместить принятый сигнал в этой передаче. Цель индикатора новых данных (NDI) - позволить приемнику правильно установить начало передачи нового пакета, так что приемник может очищать буфер после начала передачи нового пакета. Передатчик мог бы устанавливать бит индикатора новых данных (NDI) для каждой передачи одного и того же пакета. Это приведет к очистке буфера приемником для каждой передачи, заставляя работу гибридного автоматического запроса на повторение (HARQ) стать эффективнее работы автоматического запроса на повторение (ARQ), поскольку канальное декодирование не будет использовать принятые сигналы предыдущих передач.

В еще одном варианте осуществления настоящего изобретения указатель может обходить по кругу кольцевой буфер и начинать с начала буфера. Другими словами, приемник может очищать буфер после начала передачи нового пакета.

В еще одном варианте осуществления настоящего изобретения указатель указывает на положение выбранного бита в буфере. Когда индикатор новых данных (NDI) установлен в единицу, указатель перемещается в буфере в направлении по часовой стрелке; а когда индикатор новых данных (NDI) установлен в ноль, указатель перемещается в буфере в направлении против часовой стрелки.

В еще одном варианте осуществления настоящего изобретения, когда индикатор новых данных (NDI) установлен в ноль, указатель перемещается в буфере в направлении по часовой стрелке; а когда индикатор новых данных (NDI) установлен в единицу, указатель перемещается в буфере в направлении против часовой стрелки.

В еще одном варианте осуществления настоящего изобретения может отсутствовать прямая связь между значением индикатора новых данных (NDI) и направлением перемещения указателя.

В еще одном варианте осуществления настоящего изобретения начальное положение версии избыточности (RV) может регулироваться на основе значения индикатора новых данных (NDI).

В еще одном варианте осуществления изобретения начальное положение RV может не зависеть от значения указания направления (DIR).

В еще одном варианте осуществления настоящего изобретения одинаковая версия избыточности (RV) используется для двух передач одного и того же пакета наряду с установкой индикатора новых данных (NDI) в "1" для одной передачи и в "0" для другой передачи. Поэтому гарантируется, что выбранные биты в этих двух передачах будут смежными в кольцевом буфере, за исключением эффекта циклического перехода в конце буфера. Поэтому эффективная скорость кодирования на этих двух передачах может быть максимизирована.

В еще одном варианте осуществления настоящего изобретения направление перемещения указателя может быть фиксированным, а начальная точка определения версии избыточности (RV) может быть изменена в соответствии со значением индикатора новых данных (NDI).

В еще одном варианте осуществления настоящего изобретения интерпретация значения по меньшей мере одного поля в управляющем сообщении зависит от значения индикатора новых данных, который встраивается в управляющее сообщение.

В еще одном варианте осуществления настоящего изобретения по меньшей мере две разных версии избыточности определяют в одинаковых начальных положениях.

В еще одном варианте осуществления настоящего изобретения RV из четного числа перемещает указатель в направлении по часовой стрелке в буфере, а RV из нечетного числа перемещает указатель в направлении против часовой стрелки в буфере.

В еще одном варианте осуществления настоящего изобретения значение, то есть указание направления (DIR), применяют для указания перемещения указателя в кольцевом буфере. Поэтому схема определения версии избыточности (RV) может рассматриваться как использующая однобитовую версию избыточности (RVB) и однобитовое указание направления (DIR). Вводят преобразование из RVB и DIR в версию избыточности (RV).

В еще одном варианте осуществления настоящего изобретения двухбитовое значение RV используется вместе с однобитовым значением DIR, и соответственно может быть описано всего 8 (0-7, то есть 000-111, представленных трехбитовым значением) расширенных версий избыточности (ERV). Вводят преобразование из версии избыточности (RV) и указания направления (DIR) в расширенные версии избыточности (ERV).

В еще одном варианте осуществления настоящего изобретения одна версия избыточности (RV) может перемещать указатель в буфере либо в направлении по часовой стрелке, либо в направлении против часовой стрелки.

В еще одном варианте осуществления настоящего изобретения расширенная версия избыточности (ERV) может быть одновременно определена индикатором новых данных и версией избыточности. Преобразование из (RV, NDI) в ERV может быть произвольным. Предпочтительно определяют однозначное преобразование. Например, ERV может быть преобразована как ERV=2×RV+NDI. Кодированные биты или программные значения считывают или записывают в буфер, начиная с положения, определенного расширенной версией избыточности (ERV).

В другом варианте осуществления настоящего изобретения процесс согласования скорости, который на стороне передатчика выбирает биты из буфера передатчика (или на стороне приемника, или на входе в декодер приемника, процесс согласования скорости, который записывает программные значения в буфер приемника), зависит от значения указания новых данных (NDI), установленного по меньшей мере для первой версии избыточности, тогда как процесс согласования скорости, который на стороне передатчика выбирает биты из буфера передатчика (или на стороне приемника, или на входе в декодер приемника, процесс согласования скорости, который записывает программные значения в буфер приемника), работает независимо от значения индикатора новых данных по меньшей мере для второй версии избыточности.

В другом варианте осуществления настоящего изобретения для первой передачи новых данных (RV=0) NDI=1, и указатель перемещается по часовой стрелке; для повторных передач NDI=0, и указатель перемещается против часовой стрелки независимо от значения версии избыточности (RV).

В другом варианте осуществления настоящего изобретения при объединении индикатора новых данных (NDI) с поднабором версий избыточности RV, отличные от RV=0, могут использоваться, чтобы позволить процессу согласования скорости работать в зависимости от значения NDI. Процесс согласования скорости может работать в зависимости от значения NDI для более, чем одной версии избыточности (RV).

В другом варианте осуществления настоящего изобретения и направление перемещения указателя, и начальное положение RV могут одновременно зависеть от значения индикатора новых данных (NDI).

В другом варианте осуществления настоящего изобретения первая передача нового пакета указана по меньшей мере одним значением версии избыточности. Другими словами, по меньшей мере одно значение версии избыточности используют, только когда новый пакет начинают отправлять.

В другом варианте осуществления настоящего изобретения множество RV может совместно использовать или по меньшей мере одно начальное положение RV для выбора битов в процессе согласования скорости, по меньшей мере с одной из множества RV, используемой только для передачи нового пакета.

В другом варианте осуществления настоящего изобретения усовершенствованный способ согласования скорости может быть внедрен либо в передатчик, либо в приемник. Реализация согласования скорости либо в передатчике, либо в приемнике может быть достигнуто вместе с другими процессами, например согласованием скорости из-за ограничения размера буфера, перемежением субблоков, выбором битов для данной версии избыточности, наполнением/опустошением, вставкой/отсечением фиктивных битов, модуляцией, перемежением в канале и преобразованием символов модуляции в физические ресурсы и т.д.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Более полная оценка изобретения и многие из его сопутствующих преимуществ будут полностью очевидны, когда они же становятся понятнее исходя из нижеследующего подробного описания, при рассмотрении в сочетании с прилагаемыми чертежами, на которых одинаковые обозначения ссылок указывают одинаковые или аналогичные компоненты, где:

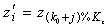

Фиг.1 - схема, иллюстрирующая работу современного гибридного автоматического запроса на повторение (HARQ);

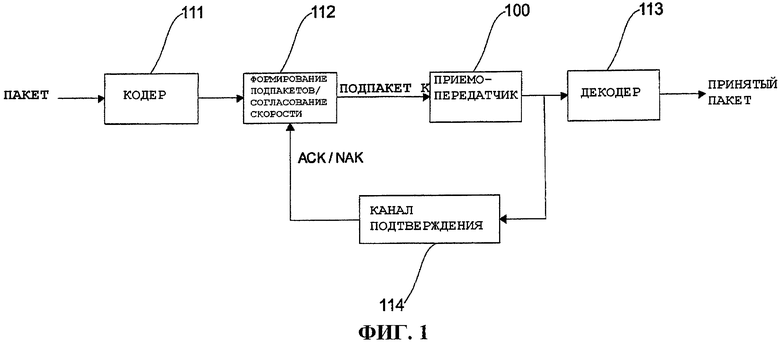

Фиг.2 - иллюстрация, показывающая пример работы 4-канального синхронного гибридного автоматического запроса на повторение (HARQ);

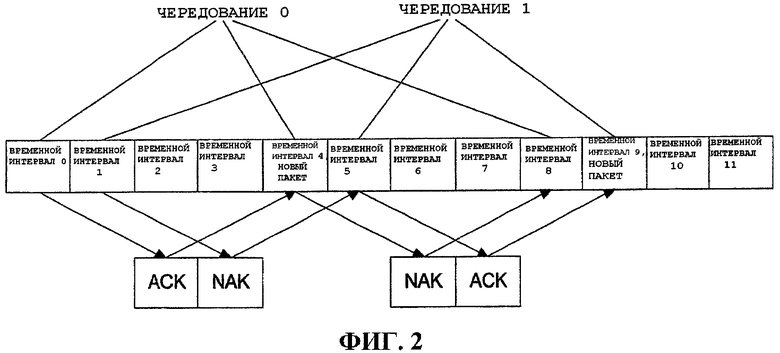

Фиг.3 - иллюстрация, показывающая пример работы асинхронного гибридного автоматического запроса на повторение (HARQ);

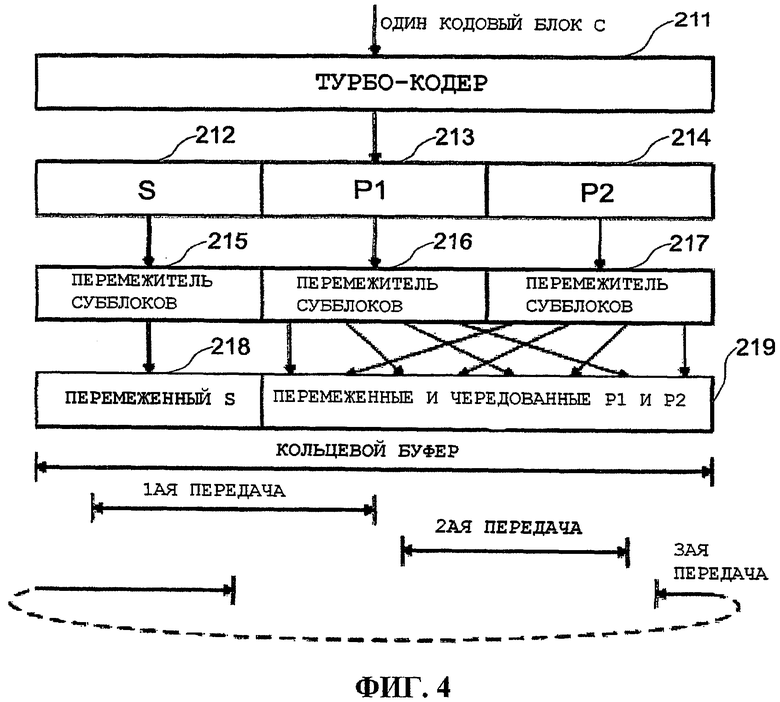

Фиг.4 - схема, показывающая процесс согласования скорости с помощью применения кольцевого буфера;

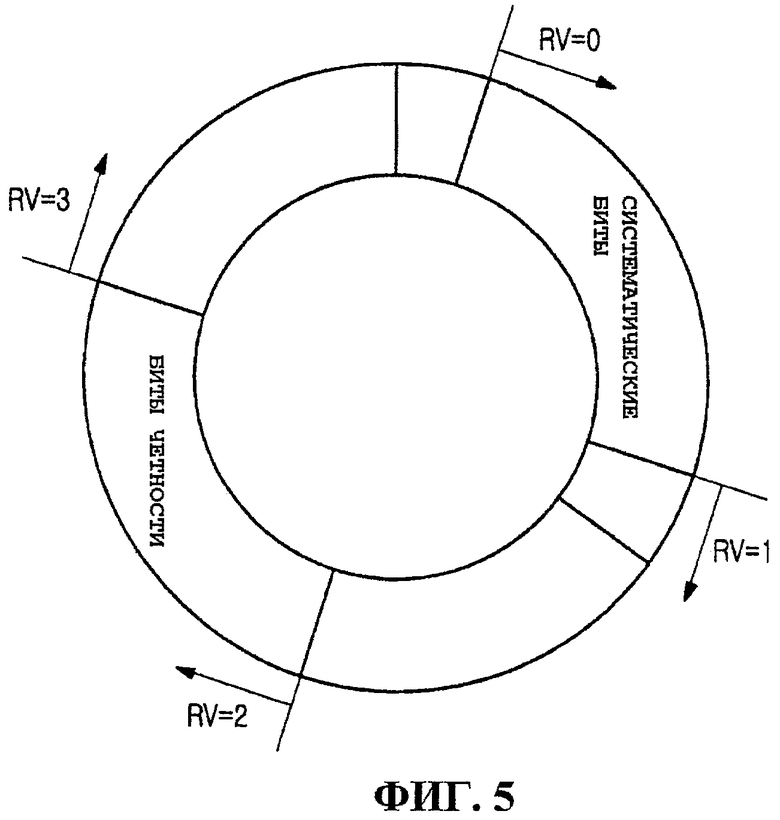

Фиг.5 - кольцевой буфер, проиллюстрированный в виде окружности;

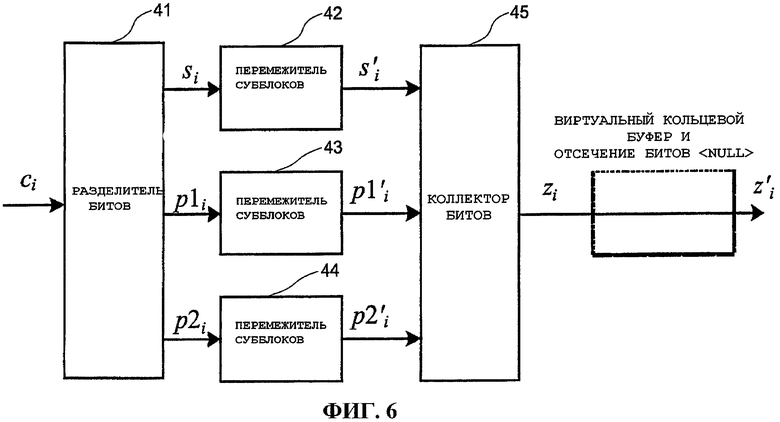

Фиг.6 показывает работу кольцевого буфера в процессе согласования скорости в передатчике;

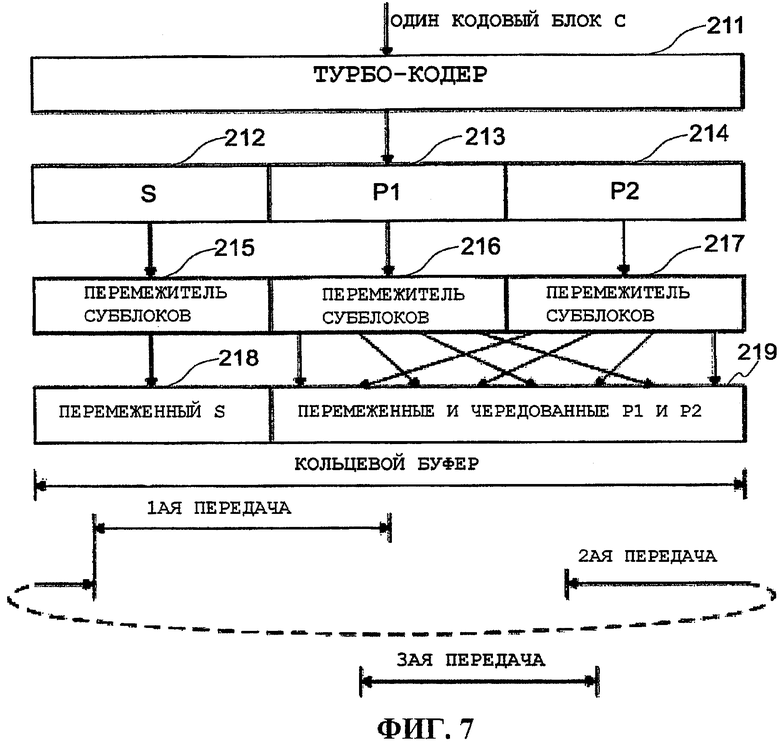

Фиг.7 показывает улучшенное согласование скорости на основе кольцевого буфера, созданное в соответствии с принципами настоящего изобретения;

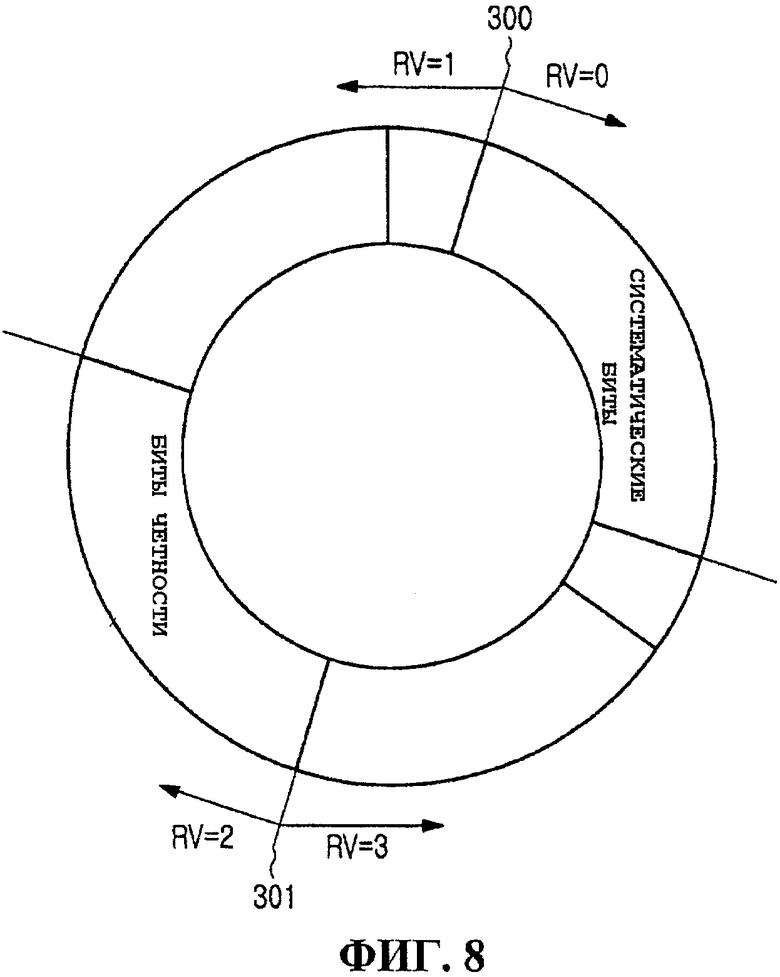

Фиг.8 показывает пример определения по меньшей мере двух разных версий избыточности в одинаковых начальных положениях, созданный в соответствии с принципами настоящего изобретения;

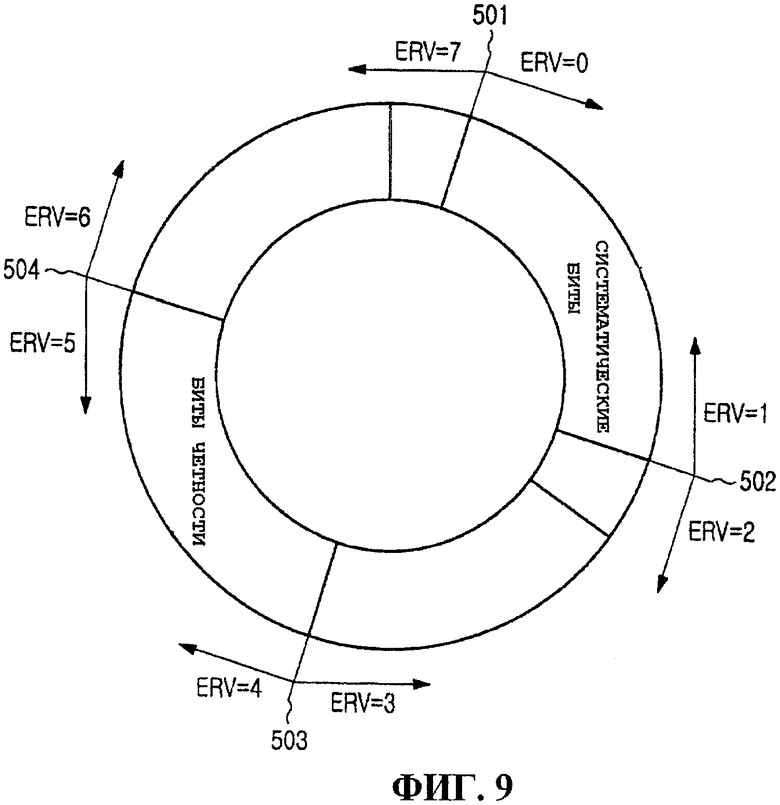

Фиг.9 показывает пример описания расширенной версии избыточности (ERV) путем объединения версии избыточности (RV) и указания направления (DIR), созданный в соответствии с принципами настоящего изобретения;

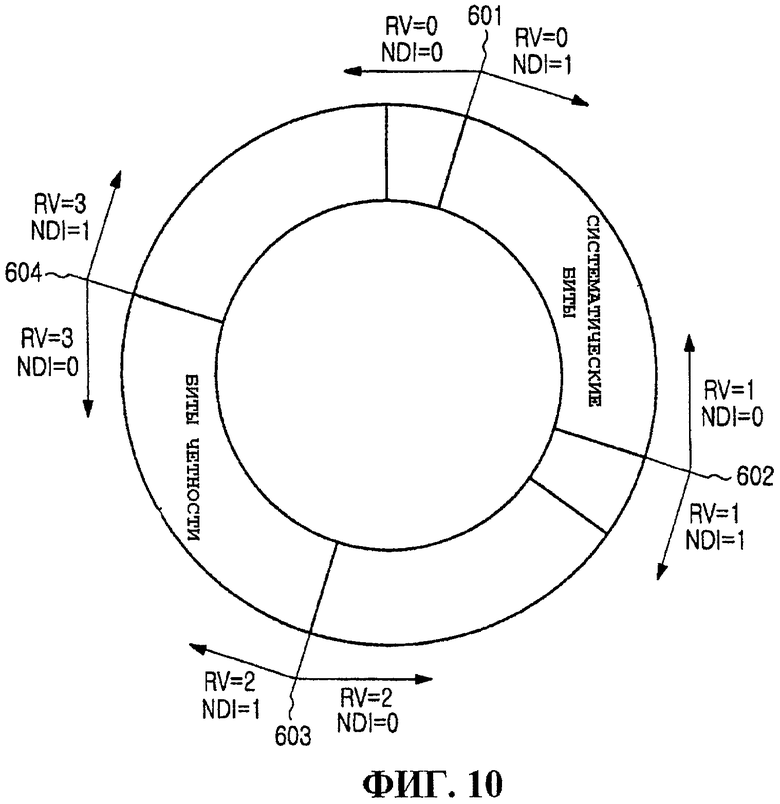

Фиг.10 показывает пример объединения версии избыточности (RV) и указания новых данных (NDI), чтобы приобрести дополнительную гибкость в выборе битов для согласования скорости, созданный в соответствии с принципами настоящего изобретения;

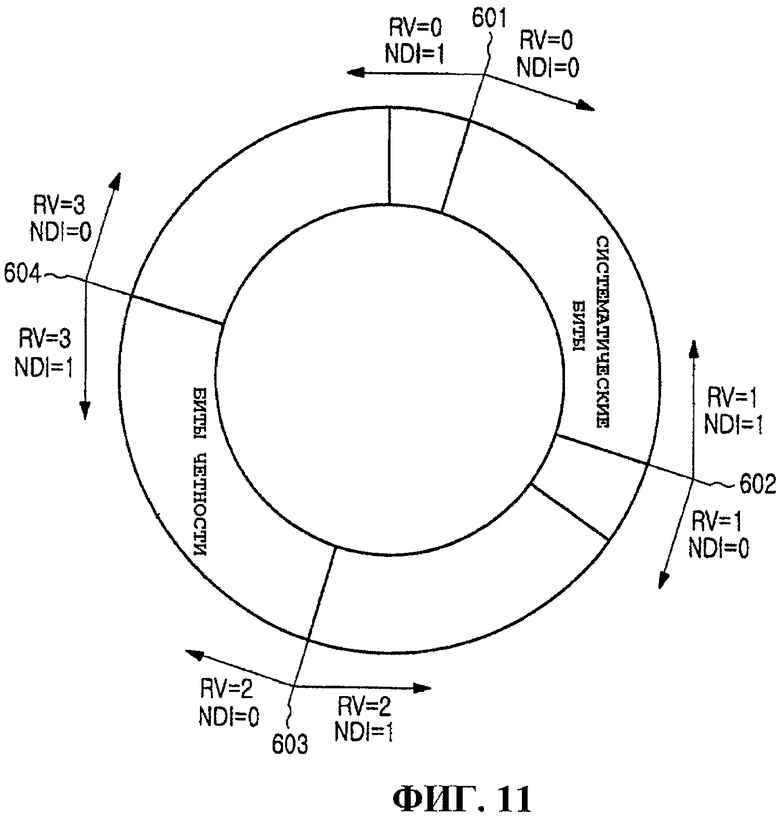

Фиг.11 показывает другой пример объединения версии избыточности (RV) и указания новых данных (NDI), чтобы приобрести дополнительную гибкость в выборе битов для согласования скорости, созданный в соответствии с принципами настоящего изобретения;

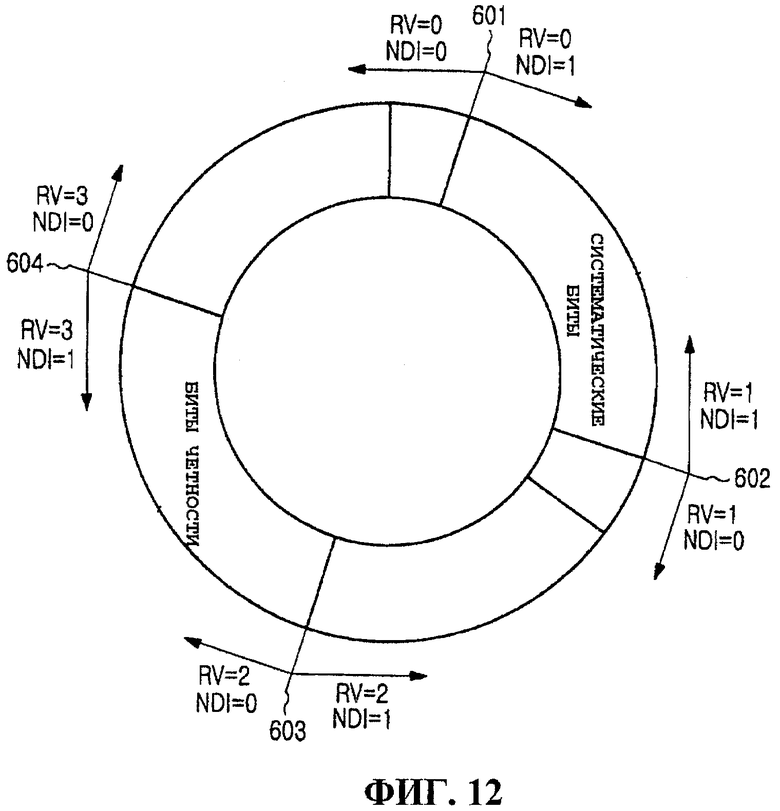

Фиг.12 показывает еще один пример объединения версии избыточности (RV) и указания новых данных (NDI), чтобы приобрести дополнительную гибкость в выборе битов для согласования скорости, созданный в соответствии с принципами настоящего изобретения;

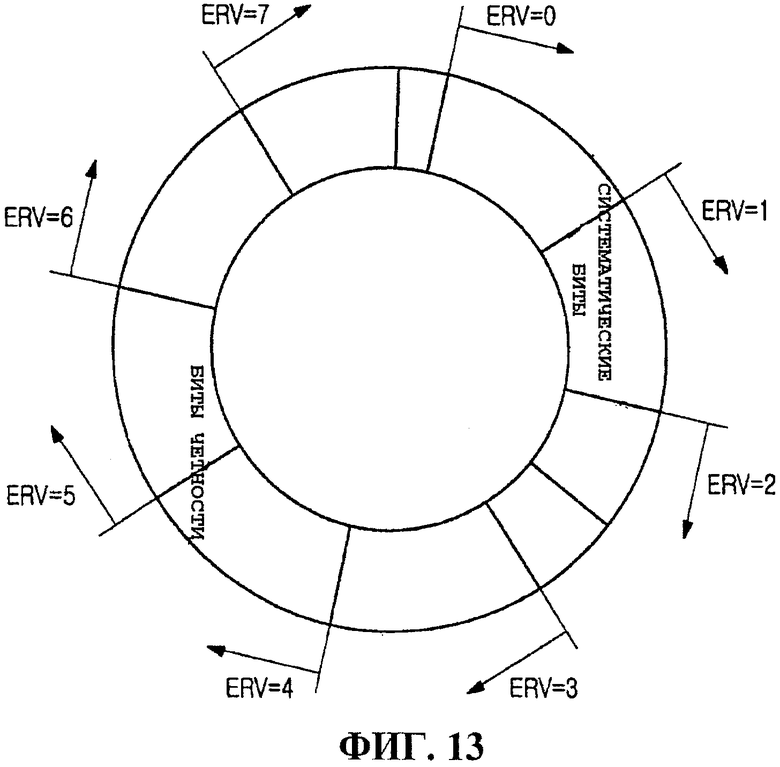

Фиг.13 показывает пример определения расширенной версии избыточности (ERV) с помощью версии избыточности (RV) и индикатора новых данных (NDI), созданный в соответствии с принципами настоящего изобретения;

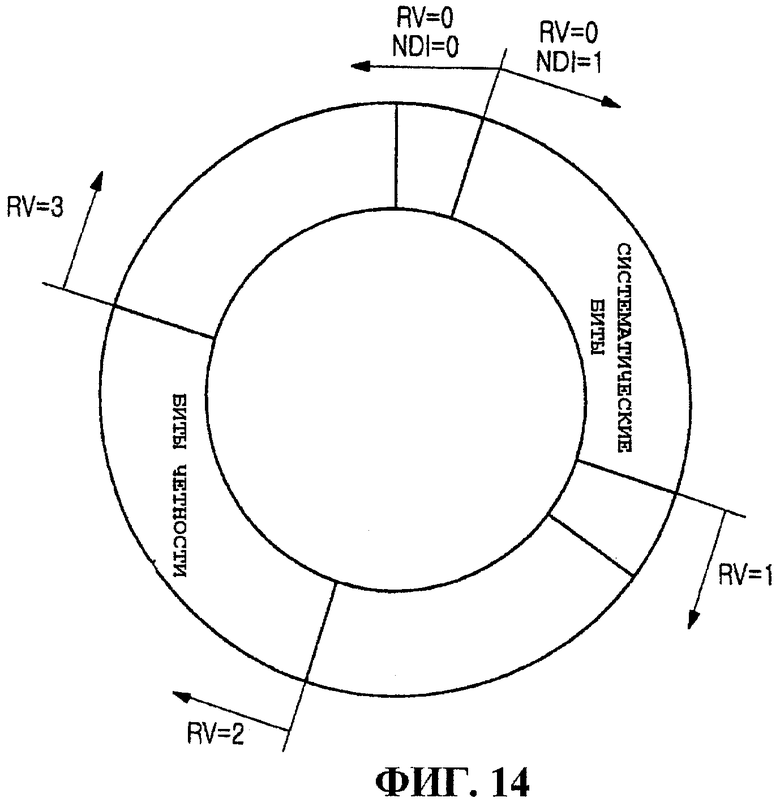

Фиг.14 показывает пример, в котором процесс согласования скорости зависит от значения указания новых данных (NDI) по меньшей мере для первой версии избыточности, тогда как процесс согласования скорости не зависит от значения индикатора новых данных по меньшей мере для второй версии избыточности, созданный в соответствии с принципами настоящего изобретения;

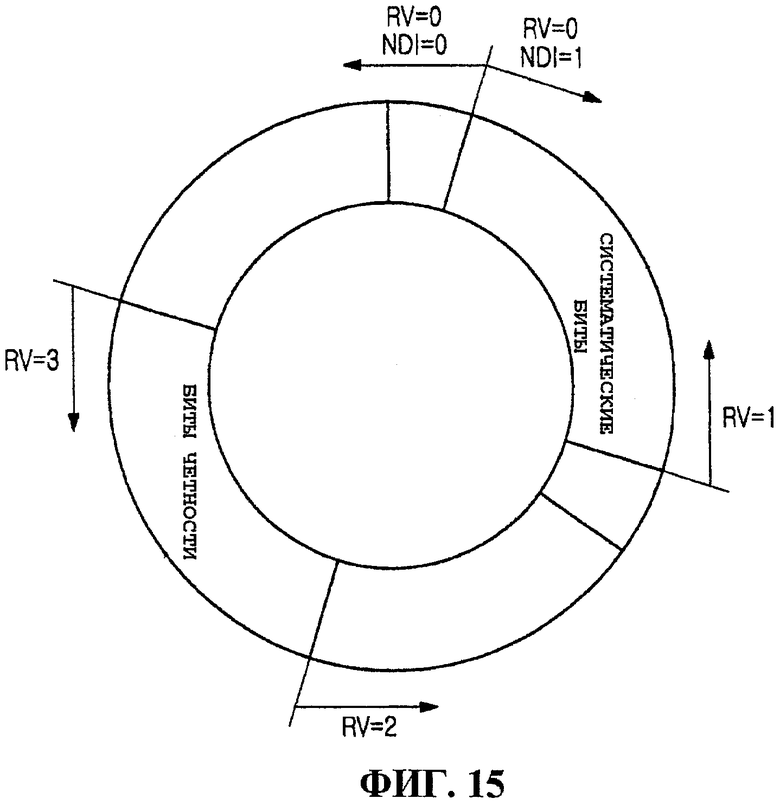

Фиг.15 показывает другой пример, в котором процесс согласования скорости зависит от значения указания новых данных (NDI) по меньшей мере для первой версии избыточности, тогда как процесс согласования скорости не зависит от значения индикатора новых данных по меньшей мере для второй версии избыточности, созданный в соответствии с принципами настоящего изобретения;

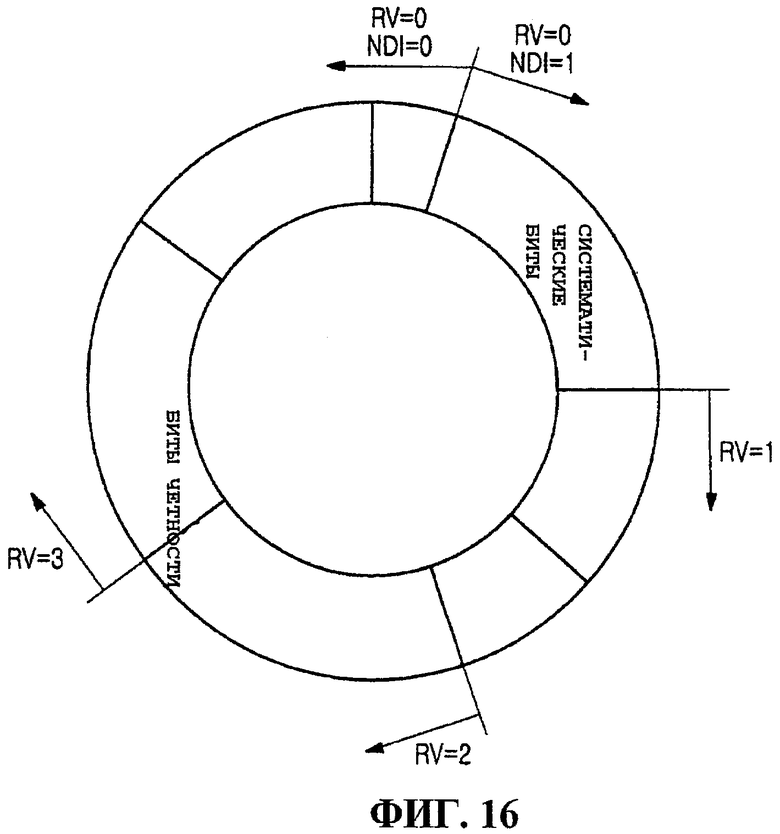

Фиг.16 показывает пример описания начальных положений RV на основе индикатора новых данных (NDI), созданный в соответствии с принципами настоящего изобретения;

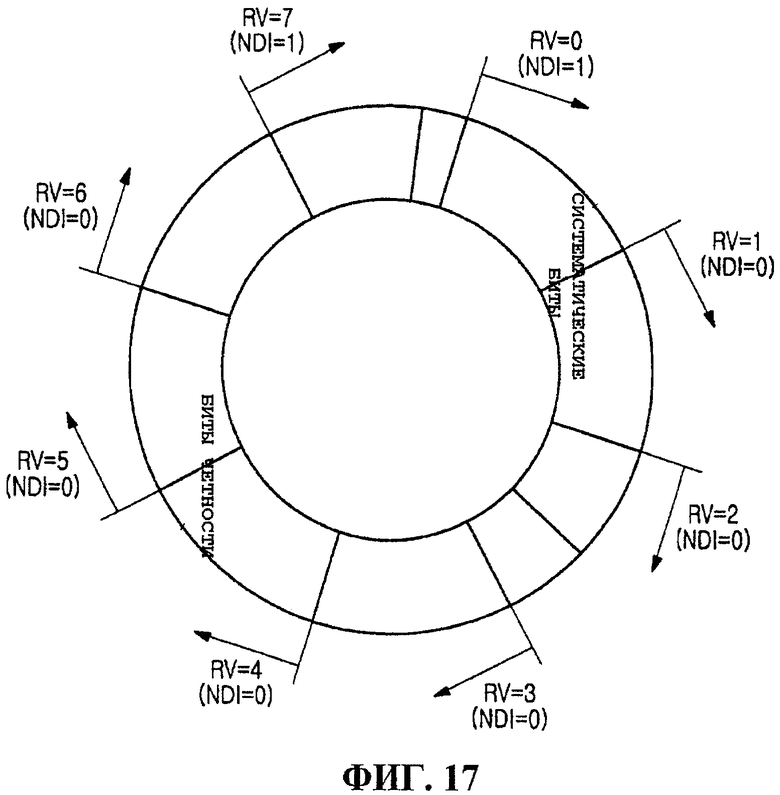

Фиг.17 показывает пример, в котором первая передача нового пакета указана по меньшей мере одним значением версии избыточности (RV), созданный в соответствии с принципами настоящего изобретения;

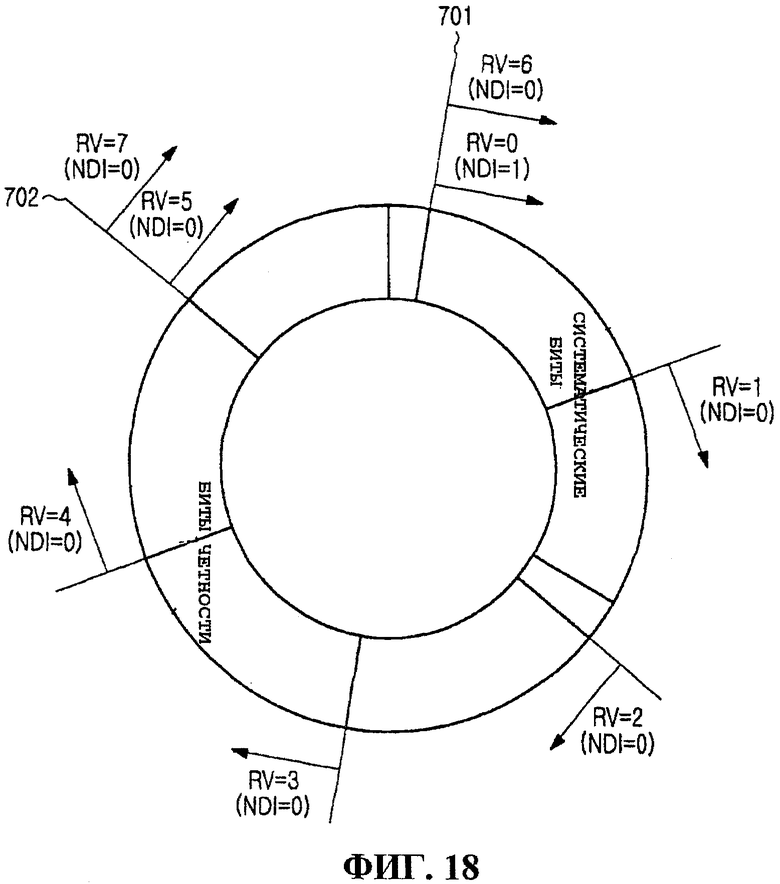

Фиг.18 показывает пример, в котором множество RV может быть определено по меньшей мере для одного одинакового начального положения, и по меньшей мере одна из множества RV может быть зарезервирована для передачи нового пакета, созданный в соответствии с принципами настоящего изобретения;

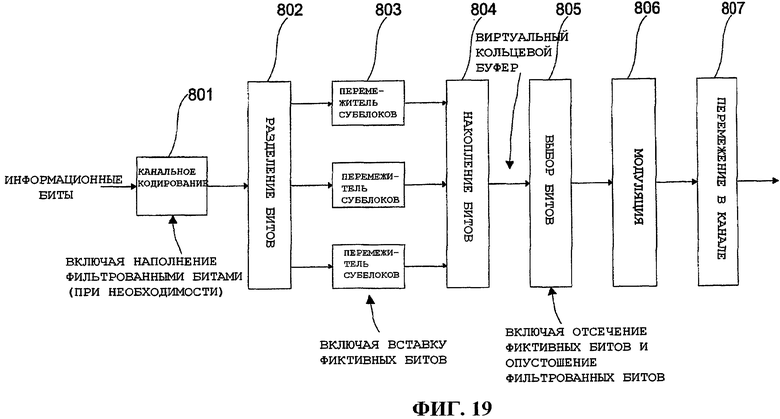

Фиг.19 - схема, которая иллюстрирует часть цепи передатчика для совместно используемого канала нисходящей линии связи (DL_SCH) и совместно используемого канала восходящей линии связи (UL_SCH) LTE, созданную в соответствии с принципами настоящего изобретения; и

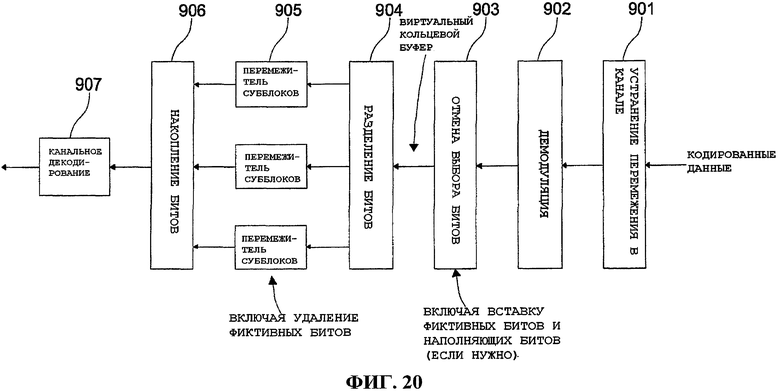

Фиг.20 - схема, которая иллюстрирует часть цепи приемника для совместно используемого канала нисходящей линии связи (DL_SCH) и совместно используемого канала восходящей линии связи (UL_SCH), созданную в соответствии с принципами настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

В настоящее время гибридный автоматический запрос на повторение (HARQ) широко используют в системах связи для борьбы с ошибками декодирования и повышения надежности. В системе передачи данных каждый пакет данных защищают с использованием определенной схемы кодирования с прямым исправлением ошибок (FEC). Каждый подпакет может содержать только часть кодированных битов полного пакета. Процесс выбора кодированных битов в подпакете, которые должны быть переданы, может называться формированием подпакетов, или согласованием скорости.

Работа современного гибридного автоматического запроса на повторение (HARQ) показана на фиг.1. Пакет данных кодируют кодером 111 с помощью определенной разновидности схемы прямого исправления ошибок (FEC). Пакет данных обрабатывают этапом 112 формирования подпакетов/согласования скорости, и таким образом формируют набор подпакетов. Например, подпакет k может содержать только часть кодированных битов. Если передача подпакета k приемопередатчиком 100 терпит неудачу, что указано сообщением с отрицательным подтверждением (NAK), предоставленным каналом 114 подтверждения по обратной связи, то предоставляют подпакет повторной передачи, подпакет k+1, для повторения приемопередачи этого пакета данных. Если подпакет k+1 успешно передан и принят, то каналом 114 подтверждения по обратной связи предоставляется подтверждение приема (ACK). Подпакеты повторной передачи могут содержать разные кодированные биты из предыдущих подпакетов. Приемник может легко объединять или одновременно декодировать все принятые подпакеты с помощью декодера 113, чтобы улучшить вероятность декодирования. Обычно максимальное количество передач конфигурируют с учетом надежности, задержки пакета и сложности реализации.

N-канальный синхронный гибридный автоматический запрос на повторение (HARQ) широко используют в системах беспроводной связи из-за простоты N-канального синхронного гибридного автоматического запроса на повторение (HARQ). Например, синхронный гибридный автоматический запрос на повторение (HARQ) принят в качестве схемы гибридного автоматического запроса на повторение (HARQ) для восходящей линии связи LTE в 3GPP.

Фиг.2 показывает пример 4-канального синхронного гибридного автоматического запроса на повторение (HARQ). Вследствие фиксированной временной зависимости между последующими передачами временные интервалы передачи в том же канале гибридного автоматического запроса на повторение (HARQ) проявляют чередующуюся структуру.

Из-за фиксированной временной зависимости между последующими передачами временные интервалы передачи в отдельном канале гибридного автоматического запроса на повторение (HARQ) проявляют чередующуюся структуру. Например, чередование 0 включает в себя временной интервал 0, 4, 8, …, 4k, …; чередование 1 включает в себя временной интервал 1, 5, 9, …, 4k+1, …; чередование 2 включает в себя временной интервал 2, 6, 10, …, 4k+2, …; чередование 3 включает в себя временной интервал 3, 7, 11, …, 4k+3, …. Пакет передают во временном интервале 0. После правильного декодирования пакета приемник отправляет обратно передатчику подтверждение приема (ACK). Передатчик затем начинает передачу нового пакета в следующем временном интервале в этом чередовании, то есть временном интервале 4. Однако первый подпакет в новом пакете, переданном в временном интервале 4, не принят должным образом. После того, как передатчик принимает отрицательное подтверждение NAK от приемника, передатчик передает другой подпакет из того же пакета в следующем временном интервале в чередовании 0, то есть временном интервале 8. Иногда приемник может испытывать сложности в обнаружении границы пакета, то есть сложность в обнаружении того, является ли подпакет первым подпакетом нового пакета или подпакетом повторной передачи. Чередования 1-3 действуют так же, как чередование 0. Чтобы смягчить эту проблему, в канале управления может быть передан индикатор нового пакета, который несет информацию о формате передачи для пакета. Иногда более подробная версия информации о канале гибридного автоматического запроса на повторение (HARQ), например ID подпакета и/или ID канала гибридного автоматического запроса на повторение (HARQ), может предоставляться для помощи приемнику в обнаружении и декодировании пакета.

Вместо синхронного гибридного автоматического запроса на повторение (HARQ) асинхронный гибридный автоматический запрос на повторение (HARQ) может обеспечивать большую гибкость в планировании и мультиплексировании разных пользователей. С помощью асинхронного гибридного автоматического запроса на повторение (HARQ) интервал времени между передачами одного и того же пакета может быть непостоянным. У передатчика есть свобода в принятии решения, когда повторно передавать пакет.

Пример асинхронного гибридного автоматического запроса на повторение (HARQ) показан на фиг.3.

Для процесса 0 HARQ первый интервал времени между двумя передачами, например, передачами субкадра 0 и субкадра 4, составляет четыре субкадра; второй интервал времени между двумя передачами, например, передачами субкадра 4 и субкадра 10, составляет шесть субкадров. После правильного декодирования пакета приемник отправляет обратно передатчику подтверждение приема (ACK). Передатчик затем начинает передачу нового пакета в следующем субкадре в этом процессе HARQ, то есть в субкадре 4.

Для процесса 1 HARQ первый интервал времени между двумя передачами, например, передачами субкадра 1 и субкадра 6, составляет пять субкадров; второй интервал времени между двумя передачами, например, передачами субкадра 6 и субкадра 11, составляет пять субкадров. Первый подпакет в новом пакете, переданном в субкадре 1, не принят должным образом. Когда передатчик принимает отрицательное подтверждение NAK от приемника, передатчик передает другой подпакет из того же пакета в следующем субкадре в процессе 1 HARQ, то есть в субкадре 6. После правильного декодирования пакета приемник отправляет обратно передатчику подтверждение приема (ACK). Передатчик затем начинает передачу нового пакета в следующем субкадре в этом процессе HARQ, то есть в субкадре 11.

Если схемы выделения ресурса или модуляции могут быть изменены во время повторных передач, то работа гибридного автоматического запроса на повторение (HARQ) является адаптивной. В системах долгосрочного развития (LTE) работа гибридного автоматического запроса на повторение (HARQ) является одновременно асинхронной и адаптивной. Иногда приемник мог испытывать сложности в обнаружении границы пакета, то есть сложность в обнаружении того, является ли подпакет первым подпакетом нового пакета или подпакетом повторной передачи. Чтобы смягчить эту проблему, в канале управления может быть передан индикатор нового пакета, который несет информацию о формате передачи для пакета. Иногда более подробная версия информации о канале гибридного автоматического запроса на повторение (HARQ), например идентификатор подпакета (ID) или даже ID канала HARQ, может быть передан для помощи приемнику в обнаружении и декодировании пакета.

В системе долгосрочного развития (LTE), когда размер транспортного блока большой, транспортный блок сегментируют на несколько кодовых блоков, чтобы можно было сформировать несколько кодированных пакетов, что является выгодным из-за таких преимуществ, как предоставление возможности реализации конвейерной или параллельной обработки и гибкий компромисс между потреблением энергии и сложностью аппаратных средств. В случае нескольких кодовых блоков согласования скорости может проводиться для каждого кодового блока. Во время процесса согласования скорости функциональность гибридного ARQ выбирает количество битов на выходе кодера канала для совпадения с общим количеством битов, которое может транспортировать физический канал. Функциональность гибридного ARQ управляется параметрами версии избыточности (RV). Точный набор битов на выходе функциональности гибридного ARQ зависит от количества входных битов, количества выходных битов и параметров RV. Согласование скорости на основе кольцевого буфера принято в системах долгосрочного развития (LTE).

Обращаясь теперь к фиг.6, фиг.6 показывает работу кольцевого буфера в процессе согласования скорости в передатчике.

Каждый кодовый блок C (включающий несколько битов, а именно ci) разделяется на три битовых потока на выходе турбо-кодера, а именно на поток S систематических битов (включающий несколько битов, а именно si), первый поток P1 четности (включающий несколько битов, а именно p1i) и второй поток P2 четности (включающий несколько битов, а именно p2i). Определяют четыре версии избыточности (RV), каждая из которых задает начальный индекс бита в буфере. Передатчик выбирает одну RV для каждой передачи HARQ. Передатчик считывает блок кодированных битов из буфера, начиная с индекса бита, заданного выбранной RV, наряду с удалением заполняющих битов и фиктивных битов. Если достигнута максимальная емкость буфера и для передачи нужно больше кодированных битов, то передатчик обходит по кругу и продолжает с начала буфера, поэтому образуется термин "кольцевой буфер".

Согласование скорости на основе кольцевого буфера графически иллюстрируется на фиг.4. В качестве альтернативы кольцевой буфер может быть проиллюстрирован в виде окружности, как показано на фиг.5.

Как показано на фиг.4, один кодовый блок C помещен в турбо-кодер 211. Турбо-кодер образуется с помощью параллельного соединения двух рекурсивных систематических сверточных кодеров (RSC), разделенных перемежителем. Кодовый блок C разделяют на поток S 212 систематических битов (включающий несколько битов, а именно si), первый поток P1 213 четности (включающий несколько битов, а именно p1i) и второй поток P2 214 четности (включающий несколько битов, а именно p2i). Поток S 212 систематических битов вводят в перемежитель 215 субблоков, первый поток P1 213 четности вводится в перемежитель 216 субблоков, а второй поток P2 четности вводят в перемежитель 217 субблоков. Поток S 212 систематических битов затем преобразуют в перемеженный поток S 218 систематических битов. Первый поток P1 213 четности и второй поток P2 214 четности преобразуют в перемеженный и чередованный поток 219 четности. Передатчик считывает блок кодированных битов из буфера, начиная с индекса бита, заданного выбранной RV, наряду с удалением заполняющих битов и фиктивных битов на этапах первой передачи (1ая ТХ) и повторных передач (например, 2ой ТХ 3ей ТХ). Если достигнута максимальная емкость буфера и нужно передать больше кодированных битов, то передатчик обходит по кругу и продолжает с начала буфера.

Как показано на фиг.5, кольцевой буфер заполняется систематическими битами и битами четности. Биты в кольцевом буфере задают разными версиями избыточности (RV), то есть RV=0, RV=1, RV=2 и RV=3. Передатчик удаляет заполняющие биты и фиктивные биты, начиная с заранее определенной RV. Когда достигнута максимальная емкость буфера и для передачи нужно больше кодированных битов, то передатчик обходит по кругу и продолжает с начала буфера. На фиг.5 буфер изображен в виде окружности, чтобы показать, что передатчик может продолжить с начала буфера, когда достигнута максимальная емкость буфера. Поэтому образуется термин "кольцевой буфер".

В качестве примера согласование скорости на основе кольцевого буфера реализовано в системе долгосрочного развития (LTE) для совместно используемого канала нисходящей линии связи (DL_SCH) и совместно используемого канала восходящей линии связи (UL_SCH), как проиллюстрировано на фиг.6.

Биты, введенные в согласование скорости, обозначены c 0, c 1, c 2,…, c E-1, где E - количество битов, введенное в блок согласования скорости. Отметим, что E является кратным 3. Биты после разделителя 41 битов обозначены s 0, s 1, s 2,…, sK'-1; p 1,0, p 1,1, p 1,2,…, p 1, K'-1 и p 2,0, p 2,1, p 2,2,…, p 2, K'-1, где K' - количество битов в каждой разделенной последовательности битов. Связь между входной последовательностью и выходной последовательности дана ниже.

Отметим, что K'=K+4 является длиной кодового блока, включая концевые биты.

Поток s i информационных битов перемежают с помощью перемежителя 42 субблоков с выходной последовательностью, определенной как v 0, v 1, v 2,…,v K''-1, и приводящей к битовому потоку.

где K''=K'/32×32 - размер перемежителя субблоков. Поток p1i битов четности перемежают в соответствии с перемежителем 43 субблоков с выходной последовательностью, определенной как v 0, v 1, v 2,…,v K''-1, и приводящей к битовому потоку

Поток p2i битов четности перемежается в соответствии с перемежителем 44 субблоков с выходной последовательностью, определенной как v 0, v 1, v 2,…,v K''-1, и приводящей к битовому потоку.

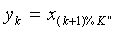

Перемежение субблоков является перемежителем блоков и состоит из битов, введенных в матрицу с заполнением, перестановки между столбцами для матрицы и битов, выведенных из матрицы. Биты, введенные в перемежитель блоков, обозначены u0, u1, u2,…,u(K'-1), где K' - количество входных битов. Последовательность выходных битов из перемежителя блоков получают следующим образом.

Назначить C=32 количеством столбцов матрицы. Столбцы матрицы нумеруют 0, 1, 2, …, C-1 слева направо.

Определить количество строк матрицы, R, путем определения минимального целого числа R из условия, что K'≤R×C=K''. Строки прямоугольной матрицы нумеруются 0, 1, 2,…, R-1 сверху вниз.

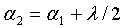

Если K''> K', то количество N

D=(K''-K') фиктивных битов заполняют так, что x

k =<NULL> для k=0, 1,…,N

D-1, и 1 для k=0, 1,…, K'-1. Если последовательность входных битов является вторым потоком p2

i четности, то последовательность заполненных битов сдвигают циклически так, что

для k=0, 1,…, K'-1. Если последовательность входных битов является вторым потоком p2

i четности, то последовательность заполненных битов сдвигают циклически так, что  для k=0, 1,…, K''-1; в противном случае

для k=0, 1,…, K''-1; в противном случае  , для k=0, 1,…, K''-1. Затем записать получившуюся последовательность в матрицу

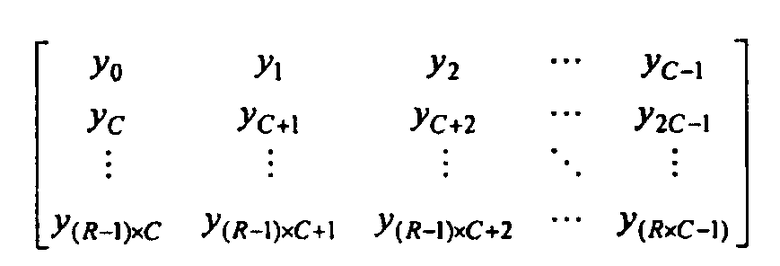

, для k=0, 1,…, K''-1. Затем записать получившуюся последовательность в матрицу  строку за строкой начиная с бита y0 в позиции строка 0 столбец 0.:

строку за строкой начиная с бита y0 в позиции строка 0 столбец 0.:

(7)

(7)

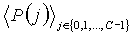

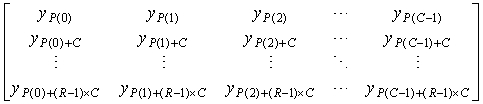

Перестановку между столбцами выполняют для матрицы на основе шаблона  , как показано в таблице 1, (таблица 1 это шаблон перестановки между столбцами для перемежителя субблоков), где

, как показано в таблице 1, (таблица 1 это шаблон перестановки между столбцами для перемежителя субблоков), где  - исходная позиция столбца -j-го переставляемого столбца. После перестановки столбцов переставленная по столбцам матрица

- исходная позиция столбца -j-го переставляемого столбца. После перестановки столбцов переставленная по столбцам матрица  становится:

становится:

(8)

(8)

Выходом перемежителя блоков является последовательность битов, считанная по столбцам из матрицы  с переставленными столбцами. Биты после перемежения субблоков обозначены v

0, v

1, v

2,…,v

K''-1, где v

0 соответствует y

P(0), v

1 соответствует y

P(0)+C, и так далее.

с переставленными столбцами. Биты после перемежения субблоков обозначены v

0, v

1, v

2,…,v

K''-1, где v

0 соответствует y

P(0), v

1 соответствует y

P(0)+C, и так далее.

Шаблон перестановки между столбцами

для перемежителя субблоков

<P(0), P(1), …, P(C-1)>

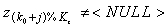

Для передачи кольцевой буфер с длиной K z=3K'' для r-ого кодированного блока определяют в виде уравнений с (9) по (11):

- длина выходной последовательности согласования скорости для этого кодированного блока, а rv

idx - номер версии избыточности для этой передачи,

- длина выходной последовательности согласования скорости для этого кодированного блока, а rv

idx - номер версии избыточности для этой передачи,  - последовательность выходных битов согласования скорости после коллектора 45 битов, где i=0,1,...,

- последовательность выходных битов согласования скорости после коллектора 45 битов, где i=0,1,...,  . Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

. Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

Set k 0=R×(24×rv idx+2)

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+1

else

j=j+1

end if

end while

где k 0 - начальное положение RV, i - индекс выбранных битов, и j - индекс исходных битов.

Поэтому в современных способах передачи пакета, которые показаны на фиг.2 и 3, приемник иногда может испытывать сложности в определении границы пакета, то есть сложность в определении, является ли подпакет первым подпакетом нового пакета или подпакетом повторной передачи. Сбои в информировании приемника о передаче нового пакета могут либо ухудшать эффективность передачи пакета и скорость кодирования из-за повторной передачи, либо вызывать ухудшение качества принятого пакета.

В этом изобретении предложены решения для повышения производительности согласования скорости для операций гибридного ARQ.

Особенности, признаки и преимущества изобретения полностью очевидны из нижеследующего подробного описания изобретения, просто с помощью иллюстрации некоторого количества конкретных вариантов осуществления и реализаций, включая лучший вариант осуществления, предполагаемый для осуществления изобретения. Настоящее изобретение также допускает другие и отличные варианты осуществления, и некоторые их подробности могут быть изменены в различных очевидных отношениях, и все это без отклонения от сущности и объема изобретения. Соответственно, чертежи и описание должны рассматриваться как пояснительные по характеру, а не как ограничивающие. Настоящее изобретение иллюстрируется в качестве примера, а не в качестве ограничения, на фигурах прилагаемых чертежей.

В одном варианте осуществления настоящего изобретения набор кодированных битов, выбранных для передачи, зависит от того, несет ли передача первую передачу нового пакета или повторную передачу для существующего пакета. При этом набор кодированных битов, выбранных для передачи пакета, не только зависит от версии избыточности, но также и от того, является ли передача первой передачей пакета. Например, в нисходящей линии связи LTE сообщение предоставления нисходящей линии связи передают вместе с передачей пакетных данных. Сообщение предоставления может содержать версию избыточности (RV) и индикатор новых данных (NDI) для указания начала нового пакета. Цель указания RV - позволить приемнику правильно установить, где в буфере следует разместить принятый сигнал в этой передаче. Цель индикатора новых данных (NDI) - позволить приемнику правильно установить начало нового пакета, так что приемник может очищать буфер после начала нового пакета. Без NDI приемнику было бы сложно узнать, является ли передача повторной передачей для предыдущего пакета или передачей для нового пакета. Передатчик мог бы устанавливать бит NDI для каждой передачи одного и того же пакета. Это приведет к очистке буфера приемником для каждой передачи, заставляя работу гибридного автоматического запроса на повторение (HARQ) стать эффективнее работы ARQ, поскольку канальное декодирование не будет использовать принятые сигналы предыдущих передач. Индикатор новых данных в настоящем изобретении - не только идентификатор границы пакетов данных, но также применяется для выбора кодированных битов, которые должны быть переданы.

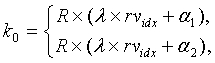

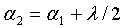

Например, один из путей реализации этой идеи описывается следующим образом. Для передачи кольцевой буфер с длиной K z=3K'' для r-ого кодированного блока определен следующим образом:

Обозначая с помощью  длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является

длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является  , i=0,1,...,

, i=0,1,...,  . Последовательность выходных битов может быть выбрана в соответствии со следующей процедурой:

. Последовательность выходных битов может быть выбрана в соответствии со следующей процедурой:

if (NDI=1)

γ= +1

else

γ=-1

end if

Set k 0=R×(24×rv idx+2)

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+γ

else

j=j+γ

end if

end while

где k 0 - начальное положение RV, i - индекс выбранных битов, j - индекс исходных битов, а γ относится к направлению перемещения указателя в буфере.

В этом примере R является минимальным целым числом R из условия, что K'≤R×C=K'', при этом C=32 - количество столбцов в перемежителе субблоков. Другими словами, R=K'/32 - количество строк в перемежителе субблоков, используемое в согласовании скорости в кольцевом буфере. В примере вышеизложенного примера начальное положение RV определяют как k 0=R×(24×rv idx+2) независимо от значения NDI. Начальное положение RV, в качестве другого варианта осуществления настоящего изобретения, может регулироваться на основе значения NDI. Один простой пример - использовать k 0=R×(24×rv idx+2), когда NDI="1", и использовать k 0=R×(24×rv idx+2)-1, когда NDI="0". Таким образом, бит в положении R×(24×rv idx+2) может выбираться, когда NDI="1", но может не выбираться, когда NDI="0" (пока не выбраны все остальные биты в кольцевом буфере), соответственно максимизируя эффективную скорость кодирования посредством повторных передач.

Фиг.7 показывает улучшенное согласование скорости на основе кольцевого буфера, созданное в соответствии с принципами настоящего изобретения. Одинаковые компоненты и процессы, которые показаны в описании фиг.4, будут пропущены. Разница между фиг.7 и фиг.4: на второй передаче NDI установлена в ноль и указывает повторную передачу пакета. Указатель начинает с сохраненного индекса бита, начиная с первой передачи, и перемещается по противоположному направлению в кольцевом буфере.

Передатчик может выбрать использование одинаковой RV для двух передач одного и того же пакета наряду с установкой NDI в "1" для одной передачи и "0" для другой передачи. При этом гарантируется, что выбранные биты в этих двух передачах будут смежными в кольцевом буфере, за исключением эффекта циклического перехода в конце буфера. Поэтому эффективная скорость кодирования на этих двух передачах может быть минимизирована. Очевидно, что двум передачам не нужно быть непрерывными, чтобы применить этот вариант осуществления. В этой реализации указатель перемещается вперед (γ=+1), когда NDI="1", и назад (γ= -1) в противном случае. В качестве альтернативы указатель может быть перемещен назад (γ=-1), когда NDI="1", и вперед (γ=+1) в противном случае. Здесь γ предполагает положение указателя.

Порядок выбранных битов или перемещение указателя не важны для применения идей этого изобретения. В другом варианте осуществления настоящего изобретения направление перемещения указателя может быть неизменным, а начальная точка определения RV может изменяться в соответствии со значением NDI. Например, в согласовании скорости в DL_SCH и UL_SCH в LTE начальная точка версии избыточности может быть определена как k 0=(R×(24×rv idx+2)+f(rv idx, NDI))%K Z . Например, начальная точка версии избыточности может быть определена как

(15)

(15)

Предпочтительно, чтобы  для распространения начальных точек RV по кольцевому буферу, и соответственно RV для исходной передачи и повторных передач пакета равномерно распределены по кольцевому буферу. Здесь

для распространения начальных точек RV по кольцевому буферу, и соответственно RV для исходной передачи и повторных передач пакета равномерно распределены по кольцевому буферу. Здесь  указывает расстояние между RV;

указывает расстояние между RV;  и

и  - параметры для регулировки смещений, или начальных положений, для RV в случае исходной передачи и повторных передач соответственно. Если размер кольцевого буфера не ограничивается, то предпочтительно

- параметры для регулировки смещений, или начальных положений, для RV в случае исходной передачи и повторных передач соответственно. Если размер кольцевого буфера не ограничивается, то предпочтительно  . Более того, чтобы RV для исходной передачи и для повторных передач равномерно распределялись по кольцевому буферу, связь между

. Более того, чтобы RV для исходной передачи и для повторных передач равномерно распределялись по кольцевому буферу, связь между  ,

,  и

и  может быть установлена с помощью

может быть установлена с помощью  , как представлено выше.

, как представлено выше.

В варианте осуществления настоящего изобретения интерпретация значения по меньшей мере одного поля в управляющем сообщении зависит от значения индикатора новых данных, который встраивают в управляющее сообщение. Например, в нисходящей линии связи системы LTE сообщение предоставления нисходящей линии связи может передаваться в одном субкадре с данными. Сообщение предоставления содержит индикатор новых данных (NDI), указывающий, предназначена ли соответствующая передача пакетных данных для нового пакета или продолжения предыдущего пакета. Сообщение предоставления также может содержать другие поля сообщения, например порядок модуляции, выделение ресурса, предварительное кодирование MIMO, ранг MIMO и т.д. Интерпретация всех этих полей может зависеть от значения NDI. Например, одно и то же значение поля для порядка модуляции может означать 16-QAM, когда NDI="1", и может означать QPSK, когда NDI="0".

В одном варианте осуществления изобретения по меньшей мере две разных версии избыточности определены в одинаковых начальных положениях. Один пример показан на фиг.8. На фиг.8 RV=0 и RV=1 определяют имеющими одинаковое начальное положение 300, тогда как RV=2 и RV=3 определяются имеющими одинаковое начальное положение 301. Например, одна возможная формула для начального положения для RV i может выражаться в виде уравнения (16):

В примере, который показан на фиг.8, RV со значениями четного числа (то есть 0 и 2) переместят указатель в буфере в направлении по часовой стрелке при считывании кодированных битов на передатчике или записи программных значений на приемнике, и RV со значениями нечетного числа (то есть 1 и 3) переместят указатель в буфере в направлении против часовой стрелки. Один способ реализации этой идеи выглядит следующим образом:

DIR=rv idx %2

if (DIR=0)

γ= +1

else

γ= -1

end if

Set k 0=R×(48×rv idx/2+2)

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+γ

else

j=j+γ

end if

end while

где rv idx - индекс RV, k 0 - начальное положение RV, i - индекс выбранных битов, j - индекс исходных битов, а γ относится к направлению перемещения указателя в буфере.

В вышеизложенном примере начальное положение RV определено как k 0=R×(48×rv idx/2+2) независимо от значения DIR, направления, по которому перемещается указатель в кольцевом буфере. Однако в другом варианте осуществления настоящего изобретения начальное положение RV также может регулироваться на основе значения DIR. Один простой пример - использовать k 0=R×(48×rv idx/2+2), когда DIR="0", и использовать k =R0×(48×rv idx/2+2)-1, когда DIR="1". Таким образом, бит в положении R×(48×rv idx/2+2) может выбираться, когда DIR="0", но может не выбираться, когда DIR="1" (пока не выбраны все остальные биты в кольцевом буфере), соответственно максимизируя эффективную кодовую скорость посредством повторных передач. С помощью этого варианта осуществления, если DIR=1, то можно выбрать только бит в положении R×(48×rv idx/2+2) после того, как выбраны все остальные биты в кольцевом буфере.

В качестве альтернативы может быть представлено значение, которое указывает перемещение указателя в кольцевом буфере. Например, схема определения RV на фиг.8 может рассматриваться как использующая однобитовую версию избыточности (RVB) и однобитовое указание направления (DIR). RV=0, как показано на фиг.8, может представляться путем установки однобитового RVB в 0 и DIR в 0, то есть RV=0 ⇔ (RVB=0, DIR=0). Преобразование между RV и RVB и DIR показывается в Таблице 2. Таблица 2 предполагает преобразование из RVB и DIR в версию избыточности (RV). Чтобы уменьшить служебную нагрузку канала управления, индикатор новых данных в канале управления (сообщение предоставления) может повторно использоваться для указания направления перемещения указателя в буфере передатчика и приемника. Или, в более общем виде, направление перемещения указателя, DIR, является функцией индикатора новых данных (NDI).

Преобразование из RVB и DIR в RV

Таблица 2 может быть изображена в виде уравнений (17)-(20):

RV=0 ⇔ (RVB=0, DIR=0 (по часовой стрелке)); (17)

RV=1 ⇔ (RVB=1, DIR=0 (против часовой стрелки)); (18)

RV=2 ⇔ (RVB=1, DIR=0 (по часовой стрелке)); и (19)

RV=3 ⇔ (RVB=1, DIR=1 (против часовой стрелки)). (20)

Альтернативные способы могут применяться к идее добавления направления перемещения указателя в определение версии избыточности (RV) и принципу выведения направления перемещения указателя из индикатора новых данных. Один пример показан на фиг.9. В этом случае двухбитовое значение RV объединяют с однобитовым значением DIR, и соответственно может быть определено всего 8 (0-7, то есть 000-111, представленных трехбитовым значением) расширенных версий избыточности (ERV). Вновь DIR может быть либо равно NDI, либо зависеть от NDI. Преобразование из RV и DIR в ERV, которое показано в Таблице 3, никоим образом не является единственным решением. Таблица 3 показывает преобразование из RV и DIR в ERV. Фактически, преобразование из 8 сочетаний 2-битовой RV и 1-битового DIR в 8 значений ERV может быть произвольным. Предпочтительно однозначное преобразование определяется между (RV, DIR) и ERV. Отметим, что всего возможно 8!=40320 однозначных преобразований. Один пример преобразования из RV и DIR в ERV иллюстрируется в Таблице 3, которая соответствует фиг.9.

Преобразование из RV и DIR в ERV

Таблица 3 может быть изображена в виде уравнений (21)-(28):

ERV=0 ⇔ (RV=0, DIR=1 (по часовой стрелке)); (21)

ERV=1 ⇔ (RV=1, DIR=0 (против часовой стрелки)); (22)

ERV=2 ⇔ (RV=1, DIR=1 (по часовой стрелке)); и (23)

ERV=3 ⇔ (RV=2, DIR=0 (против часовой стрелки)). (24)

ERV=4 ⇔ (RV=2, DIR=1 (по часовой стрелке)); (25)

ERV=5 ⇔ (RV=3, DIR=0 (против часовой стрелки)); (26)

ERV=6 ⇔ (RV=3, DIR=1 (по часовой стрелке)); и (27)

ERV=7 ⇔ (RV=0, DIR=0 (против часовой стрелки)). (28)

На фиг.9 ERV=0 и RV=7 определены имеющими одинаковое начальное положение 501, ERV=1 и ERV=2 определены имеющими одинаковое начальное положение 502, ERV=3 и ERV=4 определены имеющими одинаковое начальное положение 503, и ERV=5 и RV=6 определены имеющими одинаковое начальное положение 504.

В примере, который показан на фиг.9, ERV со значениями четного числа (то есть 0, 2, 4 и 6) переместят указатель в буфере в направлении по часовой стрелке, а ERV со значениями нечетного числа (то есть 1, 3, 5 и 7) переместят указатель в буфере в направлении против часовой стрелки.

Альтернативные способы могут применяться к идее объединения RV и NDI для получения дополнительной гибкости в выборе битов для согласования скорости.

В одном примере, который показан на фиг.10, NDI=1 указывает, что указатель перемещается по часовой стрелке в кольцевом буфере, а NDI=0 указывает противоположное. Одна и та же RV может перемещать указатель либо в направлении по часовой стрелке, либо в направлении против часовой стрелки. Например, RV=0 может перемещать указатель как в направлении по часовой стрелке, так и в направлении против часовой стрелки. Аналогичная ситуация применяется к RV=1, RV=2 и RV=3. Четыре начальных положения 601, 602, 603 и 604 определены четырьмя RV, то есть RV=0, RV=1, RV=2 и RV=3 соответственно. Поэтому в итоге восемь возможностей разрешены для процесса согласования скорости, чтобы считать (или записать) биты (или программные значения) в кольцевом буфере или на выходе кодера (или входе декодера).

В другом примере, показанном на фиг.11, аналогичное описание, которое изложено для фиг.10, будет пропущено, и будет показано только отличие. В отличие от примера, который показан на фиг.10, NDI=0 на фиг.11 указывает, что указатель перемещается по часовой стрелке в кольцевом буфере, а NDI=1 указывает противоположное. Вновь четыре начальных положения определяются четырьмя RV соответственно.

В другом примере, показанном на фиг.12, аналогичное описание, которое изложено для фиг.11, будет пропущено, и будет показано только отличие. В отличие от примера, который показан на фиг.11, в этом примере отсутствует прямая связь между NDI и направлением перемещения указателя. Четыре начальных положения определены четырьмя RV. Преобразование из RV и NDI в согласование скорости показано в Таблице 4.

Преобразование из RV и NDI

в конфигурацию согласования скорости

Как показано на фиг.12 и в таблице 4, NDI в этом примере может относиться либо к перемещению в направлении против часовой стрелки, либо к перемещению в направлении по часовой стрелке.

Идея использования индикатора новых данных (NDI) для расширения количества версий избыточности может быть дополнительно обобщена. В одном варианте осуществления настоящего изобретения расширенная версия избыточности (ERV) может быть одновременно определена индикатором новых данных и версией избыточности. Как показано ранее в Таблице 3, один бит поля NDI и два бита поля RV соединяют в виде одного указания, и соответственно всего восемь расширенных RV (ERV) может быть определено как сочетание поля NDI и поля RV. Фиг.13 показывает другой пример определения расширенной ERV с помощью индикатора новых данных (NDI). В отличие от примера, который показан на фиг.9, каждая из этих восьми RV (то есть ERV 0, ERV=1, ERV=2, ERV=3, ERV=4, ERV=5, ERV=6 и ERV=7) в этом примере могут иметь разные начальные положения. Другими словами, не нужно использовать NDI для указания направления перемещения указателя, чтобы применить идеи в этом изобретении. Вновь преобразование из (RV, NDI) в ERV может быть произвольным. Предпочтительно определяют однозначное преобразование. Например, ERV может быть преобразована как ERV=2×RV+NDI. Один пример использования расширенных RV показывается в следующей процедуре:

erv idx =2×rv idx +NDI

Set k 0=R×(12×erv idx+2)

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+1

else

j=j+1

end if

end while

где erv idx - индекс ERV, rv idx - индекс RV, k 0 - начальное положение ERV, i - индекс выбранных битов, и j - индекс исходных битов. В этом примере кодированные биты или программные значения считывают или записывают в буфер, начиная с положения, определенного расширенной версией избыточности (ERV).

В другом варианте осуществления настоящего изобретения процесс согласования скорости, который на стороне передатчика выбирает биты из буфера передатчика (или на стороне приемника, или на входе в декодер приемника, который записывает программные значения в буфер приемника) в зависимости от значения указания новых данных (NDI) по меньшей мере для первой версии избыточности, тогда как процесс согласования скорости, который на стороне передатчика выбирает биты из буфера передатчика (или на стороне приемника, или на входе в декодер приемника, который записывает программные значения в буфер приемника) в режиме независимо от значения индикатора новых данных по меньшей мере для второй версии избыточности. Один пример этого варианта осуществления показан на фиг.14. Используя согласование скорости на основе кольцевого буфера в качестве примера, для RV=0, с таким же начальным положением, указатель перемещается в буфере в разных направлениях в зависимости от значения NDI (то есть 0 или 1) (Вновь, как проиллюстрировано в предыдущих вариантах осуществления, как показано на фиг.13, смещение к начальному положению, определенное RV, также может применяться к разным значениям NDI). Однако для других версий избыточности (то есть RV=1, RV=2 и RV=3) не определен способ, которым указатель перемещается в буфере в разных направлениях в зависимости от значения NDI. Другими словами, для RV=1, 2 или 3 процесс согласования скорости всегда считывает или записывает биты или программные значения одинаковым образом, независимо от значения NDI. Это исполнение максимально совместимо с современным исполнением, в котором NDI не учитывают в определении RV или согласовании скорости. Путем объединения NDI с одной RV эта RV с NDI="1" может использоваться для первой передачи, тогда как RV с NDI="0" может использоваться для одной из повторных передач после первой передачи. Предпочтительно, чтобы RV с NDI="0" использовалась для второй передачи, так что эффективная скорость кодирования после второй передачи максимизируется.

Например, один из путей реализации этой идеи может быть показан следующим образом. Для передачи кольцевой буфер с длиной K z=3K'' для r-ого кодированного блока определяется следующим образом:

Обозначая с помощью  длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является

длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является  , i=0,1,...,

, i=0,1,...,  . Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

. Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

if (NDI=0 and RV=0)

γ= -1

else

γ= +1

end if

Set k 0=R×(24×rv idx+2)

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+γ

else

j=j+γ

end if

end while

Здесь R является минимальным целым числом R из условия, что K'≤R×C=K'', когда C=32 является количеством столбцов в перемежителе субблоков. Другими словами, R=K'/32 - количество строк в перемежителе субблоков, используемое в согласовании скорости на основе кольцевого буфера. Вновь смещение может применяться к начальному положению для (RV=0, NDI=0), чтобы начальное положение бита для (RV=0, NDI=0) не перекрывалось с положением бита (RV=0, NDI=1).

Фиг.15 показывает другой пример использования NDI, чтобы дать возможность процессу согласования скорости выбирать разный набор кодированных битов (большей версий избыточности) в зависимости от значения NDI. В этом примере указатель перемещается против часовой стрелки (γ=-1) в кольцевом буфере для RV=1, 2 и 3. Указатель также перемещается против часовой стрелки для (RV=0, NDI=0). Указатель перемещается по часовой стрелке (γ=+1) для (RV=0, NDI=1). Когда NDI=1 указывает новый пакет и RV=0 используется для первой передачи, это исполнение допускает такое же согласование скорости, как и современное согласование скорости на основе кольцевого буфера, хотя при этом смысл NDI может интерпретироваться как направление перемещения указателя в кольцевом буфере. Для первой передачи (RV=0) NDI=1 и указатель перемещается по часовой стрелке; для повторных передач NDI=0, и указатель перемещается против часовой стрелки независимо от значения RV.

В качестве другого примера объединения NDI с поднабором RV, RV, отличные от RV=0, могут использоваться, чтобы позволить процессу согласования скорости работать по-разному в зависимости от значения NDI. Процесс согласования скорости может работать по-разному в зависимости от значения NDI для более чем одной RV.

Один пример использования индикатора новых данных для определения начальных положений в согласовании скорости показан на фиг.16. В этом примере не только направление перемещения указателя изменяется на основе NDI, заодно также может изменяться начальное положение RV. Например, один из путей реализации этой идеи может быть следующим. Для передачи кольцевой буфер с длиной K z=3K'' для r-ого кодированного блока определяется следующим образом:

Обозначая с помощью  длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является

длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является  , i = 0,1,...,

, i = 0,1,...,  . Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

. Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

if (NDI=0 and RV=0)

γ= -1

else

γ= +1

end if

Set k 0=R×(19×rv idx+2)

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+γ

else

j=j+γ

end if

end while

Здесь R является минимальным целым числом R из условия, что K'≤R×C=K'', при этом C=32 является количеством столбцов в перемежителе субблоков. Другими словами, R=K'/32 - количество строк в перемежителе субблоков, используемое в согласовании скорости на основе кольцевого буфера. В этом примере путем изменения определения начального положения с k0=R×(24×rv idx+2) на k0=R×(19×rv idx+2) для RV=0, 1, 2 и 3. Разрешающая способность согласования скорости увеличивается, так что можно улучшить эффективную кодовую скорость на повторных передачах. Однако "дополнительная версия избыточности", полученная путем введения (RV=0, NDI=0), предоставляет процессу согласования скорости такую же или аналогичную возможность забирать кодированные биты между начальными положениями RV=0 и RV=3.

В одном варианте осуществления изобретения первая передача нового пакета указывается по меньшей мере одним значением версии избыточности. Другими словами, по меньшей мере одно значение версии избыточности используется, только когда отправляется новый пакет. Один пример этого варианта осуществления показан на фиг.17. В этом примере RV=0 и RV=7 зарезервированы для передач нового пакета (то есть NDI задано как 1), RV=1, 2, 3, 4, 5, 6 используются для повторных передач (то есть NDI задано как 0). После приема версии избыточности приемник знает, предназначена ли передача для нового пакета, в соответствии со значением версии избыточности. В этом примере причина наличия нескольких RV для передачи нового пакета состоит в том, чтобы обеспечить гибкость для процесса согласования скорости в передаче наиболее подходящего набора битов для первой передачи, в зависимости от других условий, например, среди прочего, выделение ресурса, условие в канале и эффективная скорость кодирования.

В качестве альтернативы множество RV может быть определено по меньшей мере для одного начального положения для выбора битов в процессе согласования скорости, причем по меньшей мере одна из множества RV используется только для передачи нового пакета. Один пример показан на фиг.18, RV=0 и RV=6 определяют в одинаковом начальном положении 701. RV=0 может использоваться, когда передают новый пакет, тогда как RV=6 может использоваться для повторной передачи с использованием того же начального положения 701, что и RV=0. Аналогичным образом, RV=5 и RV=7 определены в одинаковом начальном положении 702. RV=5 может использоваться, когда передают новый пакет, тогда как RV=7 может использоваться для повторной передачи с использованием того же начального положения 702, что и RV=5.

Например, один из путей реализации этой идеи может быть показан следующим образом. Для передачи кольцевой буфер с длиной K z=3K'' для r-ого кодированного блока определен следующим образом:

Обозначая с помощью  длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является

длину выходной последовательности согласования скорости для этого кодированного блока и с помощью rv

idx номер версии избыточности для этой передачи, последовательность выходных битов согласования скорости является  , i=0,1,...,

, i=0,1,...,  . Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

. Последовательность выходных битов может выбираться в соответствии со следующей процедурой:

if (rv idx<6)

k 0=R×(16×rv idx+2)

else if (rv idx=6)

k 0=R×(16×0+2)

else

k 0=R×(16×5+2)

end if

Set i=0 and j=0

while {i<K rm}

if

i=i+1

j=j+1

else

j=j+1

end if

end while

Отметим, что R является минимальным целым числом R из условия, что K'≤R×C=K'', при этом C=32 является количеством столбцов в перемежителе субблоков. Другими словами, R=K'/32 - количество строк в перемежителе субблоков, используемое в согласовании скорости на основе кольцевого буфера. В этом примере путем изменения определения начального положения с k 0=R×(24×rv idx+2) на k 0=R×(16×rv idx+2) для RV=0, 1, 2, …, 5. RV=6 использует такое же начальное положение, что и RV=0, и RV=7 использует такое же начальное положение, что и RV=5. При этом первая передача нового пакета обладает гибкостью выбора между RV=0 и RV=5, наряду с тем, что разрешающая способность согласования скорости увеличивается, так что можно улучшить эффективную кодовую скорость на повторных передачах.

Существует много путей применения вариантов осуществления, раскрытых в этом изобретении. Хотя один или два бита версии избыточности используются в качестве примеров в вышеупомянутых вариантах осуществления, несомненно, что раскрытые в этом изобретении идеи могут применяться к сценариям с версиями избыточности, имеющими помимо одного или двух битов. И количество версий избыточности не обязательно должно быть степенью 2. Для простоты и ясности описание в этом изобретении главным образом описывает операции на стороне передатчика. Обычный специалист в данной области техники может признать, что варианты осуществления изобретений также могут быть применены на стороне приемника. Например, когда передатчик выбирает начальное положение в выборе битов для передачи, приемнику нужно выбрать начальное положение в приеме этой передачи, чтобы поместить принятые сигналы в правильное положение либо в буфере приемника, либо на вход декодера.

Хотя описание вариантов осуществления основывается на принципе кольцевого буфера, фактическая реализация либо передатчика, либо приемника может не реализовывать кольцевой буфер в качестве единственного и отдельного этапа. Вместо этого операция согласования скорости на основе кольцевого буфера может выполняться вместе с другими процессами, например согласованием скорости из-за ограничения размера буфера, перемежением субблоков, выбором битов для данной версии избыточности, наполнением/опустошением, вставкой/отсечением фиктивных битов, модуляцией, перемежением в канале и преобразованием символов модуляции в физические ресурсы и т.д.

Фиг.19 иллюстрирует часть цепи передатчика для совместно используемого канала нисходящей линии связи (DL_SCH) и совместно используемого канала восходящей линии связи (UL_SCH) в LTE. Как показано на фиг.19, информационные биты кодируют на этапе 801 канального кодирования, который при необходимости может включать в себя процесс заполнения заполняющими битами. Кодированные информационные биты затем разделяют на этапе 802 разделения битов на три потока данных, то есть один поток систематических битов и два потока битов четности, как показано на фиг.6. Эти три битовых потока затем перемежаются соответствующими перемежителями 803 субблоков. Перемежители 803 субблоков могут вставлять фиктивные биты при необходимости. Перемеженные биты дополнительно накапливаются на этапе 804 накопления битов. Кольцевой буфер внедряют между этапами накопления битов и выбора битов. Используя значение версии избыточности и/или указания новых данных, кодированные биты должным образом выбирают для каждой передачи. После этапа 805 выбора битов информационные биты модулируют этапом 806 модуляции и затем перемежаются на этапе 807 перемежения в канале. На этап 805 выбора битов фиктивные биты могут отсекаться, и наполняющие биты могут опустошаться. Варианты осуществления, описанные в настоящем изобретении, могут применяться к этапу 805 "Выбор битов" в процессе, который использует значение версии избыточности и/или указания новых данных, чтобы выбрать кодированные биты для каждой передачи. Обычный специалист в данной области техники может признать, что варианты осуществления изобретений обладают применимостью к реализациям, если этап "Выбор битов" объединен с другими этапами в цепи обработки передатчика.

Фиг.20 иллюстрирует часть цепи приемника для совместно используемого канала нисходящей линии связи (DL_SCH) и совместно используемого канала восходящей линии связи (UL_SCH).

Как показано на фиг.20, кодированные информационные биты обращенно перемежают на этапе 901 устранения перемежения в канале и затем демодулируются на этапе 902 демодуляции. Виртуальный кольцевой буфер внедряют между этапами отмены выбора битов и этапом разделения битов. Используя значение версии избыточности и/или указания новых данных, принятые программные значения должным образом помещают в правильные положения в буфере приема или входе в канальный декодер для каждой передачи. После этапа 904 разделения битов кодированные биты разделяют на три потока, то есть один поток систематических битов и два потока битов четности. Эти три битовых потока затем обращенно перемежают соответствующими перемежителями 905 субблоков, и затем дополнительно накапливают на этапе 906 накопления битов. Перемежители 905 субблоков могут удалять фиктивные биты. Затем накопленные биты декодируют на этапе 907 канального декодирования. Варианты осуществления, описанные в этом изобретении, могут применяться к этапу 903 "Отмена выбора битов" в процессе, который использует значение версии избыточности и/или указания новых данных, чтобы поместить принятые программные значения в правильные положения в буфере или входе в канальный декодер для каждой передачи. Этап 903 отмены выбора битов может вставлять фиктивные биты и заполняющие биты при необходимости. Обычный специалист в данной области техники может признать, что варианты осуществления изобретения обладают применимостью к реализациям, если этап "Отмена выбора битов" объединен с другими этапами в цепи обработки передатчика.

Для удобства часть описания в этом изобретении предполагает, что кольцевой буфер не усекают. Например, мы предполагаем турбо-код с 1/3 исходной кодовой скорости и отсутствие исключения кодированных битов, за исключением вызванного согласованием скорости для передачи. Однако в некоторых системах или реализациях, чтобы уменьшить размер буфера на передатчике и приемнике, исключение некоторых кодированных битов может происходить даже без согласования скорости для передачи. Обычный специалист в данной области техники может признать, что варианты осуществления изобретения обладают применимостью к тем сценариям. К тому же, хотя описание вариантов осуществления основывается на принципе кольцевого буфера, многие из вышеупомянутых вариантов осуществления вместе с общей идеей объединения указания новых данных с указанием версии избыточности применимы, когда используются другие типы буферов.

В качестве непосредственного расширения вышеупомянутые варианты осуществления легко могут быть объединены.

Настоящее изобретение относится к способу и устройству процесса согласования скорости с использованием гибридного автоматического запроса на повторение (HARQ). Техническим результатом является улучшение работы HARQ, снижение ошибок декодирования и повышение надежности. Указанный технический результат достигается тем, что кодируют входные биты, разделяют кодированные биты на множество битовых потоков, перемежают соответственно множество битовых потоков, накапливают перемеженные битовые потоки, выбирают группу кодированных битов из буфера, которая должна быть передана, из накопленных битовых потоков на основе начальной позиции, соответствующей версии избыточности (RV), и длины выходной битовой последовательности и передают выбранную группу кодированных битов через одну или множество передающих антенн. 4 н. и 14 з.п. ф-лы, 20 ил., 4 табл.

1. Способ для передачи данных, содержащий этапы, на которых:

кодируют входные биты;

разделяют кодированные биты на множество битовых потоков;

перемежают соответственно множество битовых потоков;

накапливают перемеженные битовые потоки;

выбирают группу кодированных битов из буфера, которая должна быть передана, из накопленных битовых потоков на основе начальной позиции, соответствующей версии избыточности (RV), и длины выходной битовой последовательности; и

передают выбранную группу кодированных битов через одну или множество передающих антенн.

2. Способ по п.1, дополнительно содержащий этапы, на которых:

сегментируют входные биты в по меньшей мере один кодовый блок;

и

кодируют соответственно каждый из по меньшей мере одного кодового блока.

3. Способ по п.1, причем множество битовых потоков содержит по меньшей мере один поток систематических битов и по меньшей мере два потока битов четности.

4. Способ по п.3, причем этап накопления содержит этапы, на которых:

записывают перемеженный по меньшей мере один поток систематических битов в переднем положении буфера и записывают перемеженные по меньшей мере два потока битов четности чередующимся образом следом за перемеженным по меньшей мере одним потоком систематических битов.

5. Способ по п.1, причем этап выбора группы кодированных битов для передачи основан на порядке модуляции дополнительно с RV и длине выходной битовой последовательности.

6. Передатчик, содержащий:

кодер для кодирования входных битов;

разделитель битов для разделения кодированных битов на множество битовых потоков;

перемежитель для соответственного перемежения множества битовых потоков;

накопитель битов для накопления перемеженных битовых потоков;

селектор битов для выбора группы кодированных битов, которая должна быть передана, из накопленных битовых потоков на основе начальной позиции, соответствующей версии избыточности (RV), и длины выходной битовой последовательности; и

одну или более передающих антенн для передачи выбранной группы кодированных битов.

7. Передатчик по п.6, причем кодер сегментирует входные биты в по меньшей мере один кодовый блок и кодирует по меньшей мере один кодовый блок соответственно.

8. Передатчик по п.6, причем множество битовых потоков содержит по меньшей мере один поток систематических битов и по меньшей мере два потока битов четности.

9. Передатчик по п.8, причем накопитель битов записывает перемеженный по меньшей мере один поток систематических битов в переднем положении буфера и записывает перемеженные по меньшей мере два потока битов четности чередующимся образом следом за перемеженным по меньшей мере одним потоком систематических битов.

10. Передатчик по п.6, причем селектор битов выбирает группу кодовых битов на основе порядка модуляции дополнительно с RV и длины выходной битовой последовательности.

11. Способ для приема данных, способ, содержащий этапы, на которых:

принимают множество кодированных битов кодового блока на одной или множестве приемных антенн;

выбирают множество групп кодированных битов из принятого множества кодированных битов на основе начальной позиции соответствующей версии избыточности (RV) и длины выходной битовой последовательности;

разделяют выбранные группы кодированных битов на множество битовых потоков;

перемежают соответственно множество битовых потоков;

накапливают перемеженные битовые потоки; и

декодируют накопленные битовые потоки.

12. Способ по п.11, причем множество битовых потоков содержит по меньшей мере один поток систематических битов и по меньшей мере два потока битов четности.

13. Способ по п.12, причем этап накопления содержит этап, на котором

записывают перемеженный по меньшей мере один поток систематических битов в переднем положении буфера и записывают перемеженные по меньшей мере два потока битов четности чередующимся образом следом за перемеженным по меньшей мере одним потоком систематических битов.

14. Способ по п.11, причем этап выбора кодированных битов основан на порядке модуляции дополнительно с RV и длине выходной битовой последовательности.

15. Приемник, содержащий:

множество приемных антенн для приема множества кодированных битов;

устройство обратного выбора битов для выбора группы кодированных битов из принятого множества кодированных битов на основе начальной позиции, соответствующей версии избыточности (RV), и длины выходной битовой последовательности;

разделитель битов для разделения выбранных групп кодированных битов на множество битовых потоков;

перемежитель для соответственного перемежения множества битовых потоков;

накопитель битов для накопления перемеженных битовых потоков; и

декодер для декодирования накопленных битовых потоков.

16. Приемник по п.15, причем множество битовых потоков содержит по меньшей мере один поток систематических битов и по меньшей мере два потока битов четности.

17. Приемник по п.16, причем накопитель битов записывает перемеженный по меньшей мере один поток систематических битов в переднем положении буфера и записывает перемеженные по меньшей мере два потока битов четности чередующимся образом следом за перемеженным по меньшей мере одним потоком систематических битов.

18. Приемник по п.15, причем устройство обратного выбора выбирает группу кодированных битов на основе порядка модуляции дополнительно с RV и длины выходной битовой последовательности.

| WO 2006000991 А1, 05.01.2006 | |||

| KR 20030060387 А, 16.07.2003 | |||

| US 2002009157 A1, (SIPOLA J.) 24.01.2002 | |||

| US 2004221219 A1, 04.11.2004 | |||

| US 2002075867 A1, 20.06.2002 | |||

| KR 20050069902 A, 05.07.2005 | |||

| KR 20040084212 A, 06.10.2004 | |||