Область техники

Настоящее раскрытие относится к защите от электростатического разряда (ESD) для полупроводниковых устройств и, в частности, к системам и способам для обеспечения ESD-защиты в трехмерных многоуровневых полупроводниковых устройствах.

Уровень техники

Согласно технологии формирования сквозной многоуровневой кремниевой структуры (TSS) кремниевые микросхемы упорядочиваются в многоуровневых структурах, чтобы сформировать трехмерные электронные устройства. В таких устройствах создаются взаимосвязи между упомянутыми микросхемами. Эти взаимосвязи часто включают в себя сквозные кремниевые переходные отверстия (TSV).

Каждая схема на каждой многоуровневой микросхеме требует ESD-защиты на портах ввода/вывода этой схемы. К сожалению, схема ESD-защиты занимает относительно большую площадь на кремнии. Когда существующая схема разделяется на множество микросхем трехмерного устройства, эти схемы (и их соответствующая ESD-защита) могут быть разделены. Как следствие, ESD-защита предоставляется на каждой микросхеме, чтобы защищать каждую часть схемы, разделенной между разными микросхемами. В результате схеме ESD-защиты требуется еще больше пространства на трехмерных многоуровневых микросхемах.

Раскрытие изобретения

Схема ESD-защиты формируется в вертикальном пространстве (например, в TSV) между активными слоями на разных микросхемах трехмерных многоуровневых устройств, в результате чего используется пространство, которое в противном случае использовалось бы только для целей коммуникации. Площадь вертикальной поверхности TSV поглощает крупные события ESD.

В одном варианте осуществления полупроводниковый кристалл включает в себя, по меньшей мере, одну активную схему внутри, по меньшей мере, одного переходного отверстия, сформированного в подложке.

В еще одном варианте осуществления диод ESD-защиты создается в вертикальном измерении между активными слоями многоуровневых кристаллов. Этот диод ESD-защиты может совместно использоваться схемой на обоих полупроводниковых кристаллах многоуровневой структуры, в результате чего обеспечивается экономия пространства и сокращается площадь микросхемы, требуемая для схемы ESD-защиты.

В еще одном варианте осуществления создается полупроводниковый кристалл, который содержит, по меньшей мере, одно TSV. Это TSV содержит, по меньшей мере, одну активную схему. Полупроводниковый кристалл накладывается в параллельной комбинации со вторым полупроводниковым кристаллом, и TSV позиционируется вертикально между активными слоями многоуровневых кристаллов.

В еще одном варианте осуществления предоставлен способ для создания схемы ESD-защиты, которая включает в себя этап, на котором располагают многоуровневое полупроводниковое устройство таким образом, чтобы TSV из одного полупроводникового кристалла устройства соединялись со смежным кристаллом. При использовании этой структуры контактные площадки ввода/вывода, по меньшей мере, одного из полупроводниковых кристаллов могут быть соединены со схемой ESD-защиты, созданной, по меньшей мере, частично внутри, по меньшей мере, одного из TSV.

В еще одном варианте осуществления многоуровневое полупроводниковое устройство включает в себя первый и второй полупроводниковые кристаллы, расположенные параллельно друг другу. Упомянутое устройство также включает в себя средство для соединения активных слоев упомянутых кристаллов. Упомянутое средство соединения включает в себя активные элементы.

Выше было приведено обобщенное описание отличительных признаков и технических преимуществ настоящего изобретения, чтобы облегчить понимание подробного описания, которое изложено ниже. Дополнительные отличительные признаки и преимущества настоящего изобретения описаны ниже в форме объекта формулы изобретения. Специалистам в данной области техники будет очевидно, что концепция и описанные конкретные варианты осуществления могут быть использованы как база для модификации или разработки других структур, предназначенных для достижения целей настоящего изобретения. Следует понимать, что такие эквивалентные конструкции входят в рамки сущности и объема настоящего изобретения, как определено в прилагаемой формуле изобретения. Новые отличительные признаки, а также дополнительные цели и преимущества настоящего изобретения будут более понятны из следующего описания в сочетании с прилагаемыми чертежами. Также следует четко понимать, что чертежи предназначены для иллюстрации и описания, а не для определения границ настоящего изобретения.

Краткое описание чертежей

Для более полного понимания настоящего изобретения ниже приведено подробное описание в сочетании с прилагаемыми чертежами.

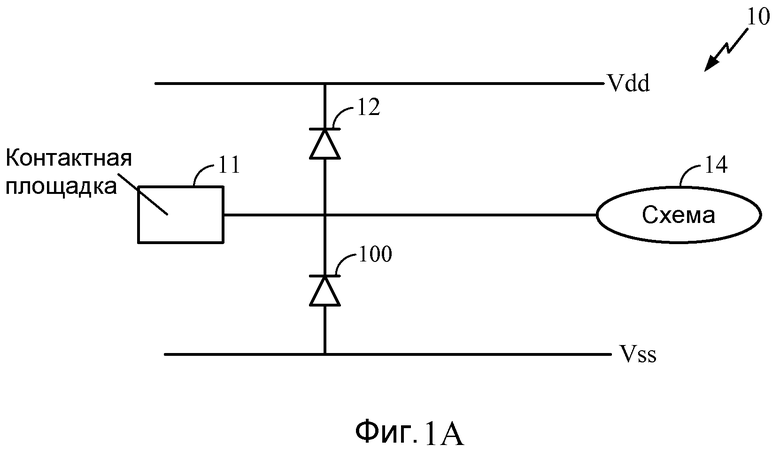

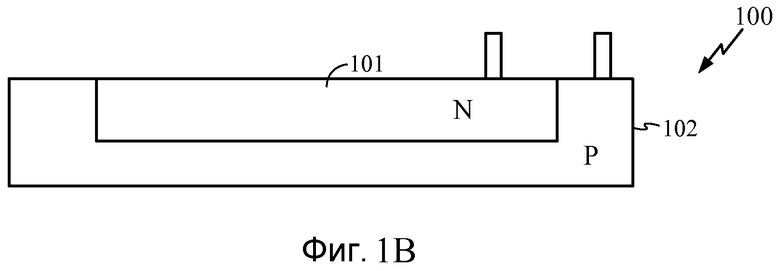

Фиг. 1A и 1B - иллюстрации обычной схемы ESD-защиты;

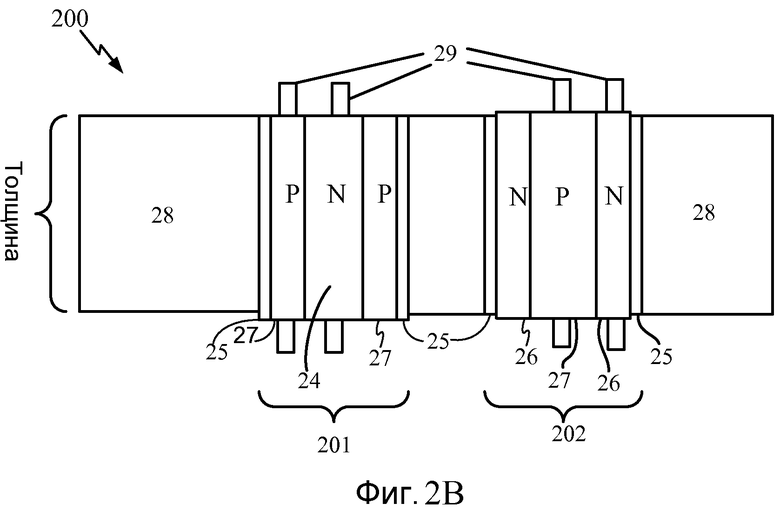

Фиг. 2A и 2B - виды поперечных сечений, иллюстрирующие один вариант осуществления настоящего изобретения;

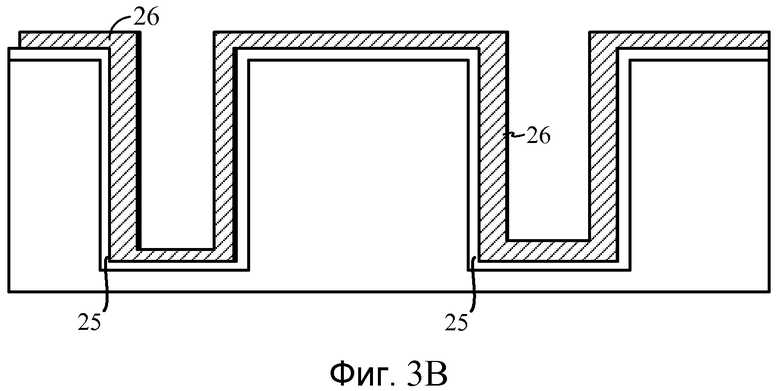

Фиг. 3A-3G - виды поперечных сечений, иллюстрирующие варианты осуществления процесса создания устройства, показанного на Фиг.2A и 2B;

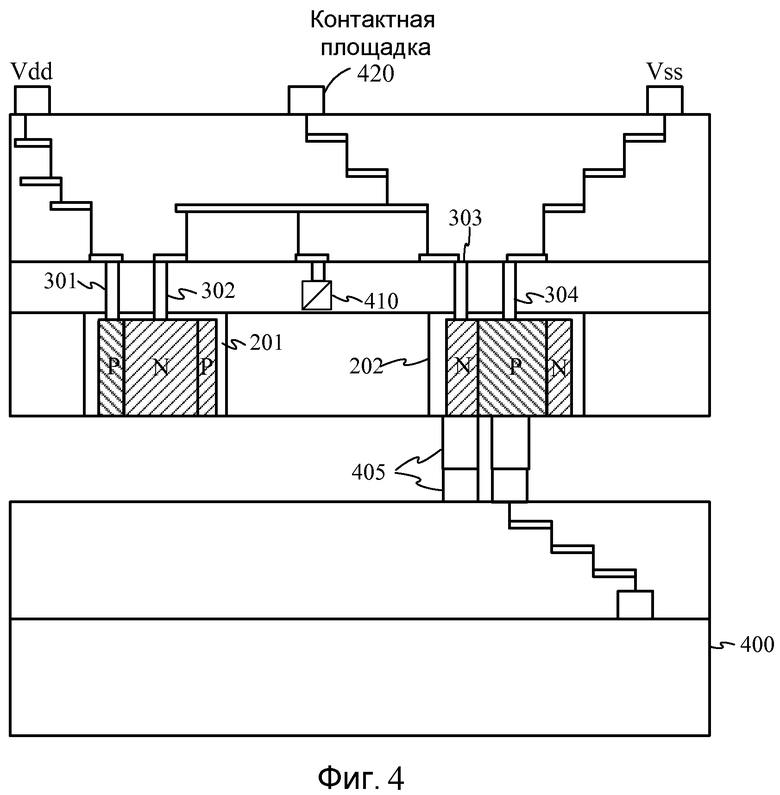

Фиг. 4 - вид поперечного сечения, иллюстрирующий еще один вариант осуществления настоящего изобретения.

Осуществление изобретения

Фиг. 1A и 1B представляют собой иллюстрации обычной схемы ESD-защиты. Фиг. 1A иллюстрирует часть устройства 10, в котором контактная площадка 11 ввода/вывода принимает разряд высокого напряжения или большого тока, который может образоваться при событии ESD. Для того чтобы защитить схему 14 от негативного воздействия события ESD, диод 12 разряжает избыточное напряжение на Vdd. В некоторых случаях, например, когда имеет место событие отрицательного высокого напряжения (или тока), диод 100 разряжает избыточное напряжение на Vss или землю. Как правило, диоды 12, 100 являются достаточно большими.

Фиг. 1B иллюстрирует типовую структуру 100 диода, содержащую P-секцию 102 и N-секцию 101. Эти структуры 100 диода имеют большие размеры, чтобы обрабатывать относительно высокие напряжения при событиях ESD. Один из этих диодов обычно связан с каждой контактной подложкой ввода/вывода.

Фиг. 2A и 2B иллюстрируют один вариант осуществления настоящего раскрытия. Фиг. 2A иллюстрирует устройство 20, содержащее кристаллы 21 и 22 в многоуровневом параллельном расположении относительно друг друга, а также устройство 200 ESD-защиты. Защитный слой 21-1 верхнего кристалла 21 расположен поверх его лицевого (активного) слоя 21-2. Нижний кристалл 22 расположен в такой же ориентации, и его защитный слой 22-1 расположен сверху лицевого (активного) слоя 22-2. Следует отметить, что концепции настоящего изобретения могут быть применены даже тогда, когда каждый кристалл имеет любую требуемую ориентацию.

Сквозные кремниевые переходные отверстия (TSV) 23 образуются в защитном слое 22-1 между активными поверхностями 21-2, 22-2 кристаллов 21, 22, чтобы обеспечить связи между кристаллами. Одно или более из этих переходных отверстий 23 сформировано как вертикальное устройство ESD-защиты, такое как устройство 200, содержащее один или более диодов. В данном контексте термин "вертикальный" обозначает перпендикулярное направление относительно плоскости кристаллов, для защиты которых сформировано устройство 200 ESD-защиты. Вертикальное устройство 200 ESD-защиты может быть сформировано целиком на одной микросхеме или частично на каждой из двух смежных микросхем, наложенных друг на друга. Кроме того, вертикальное устройство 200 необязательно строго перпендикулярно относительно площади микросхем 21, 22, и оно может быть наклонено или даже частично параллельно относительно наложенных друг на друга микросхем 21, 22 в этой площади.

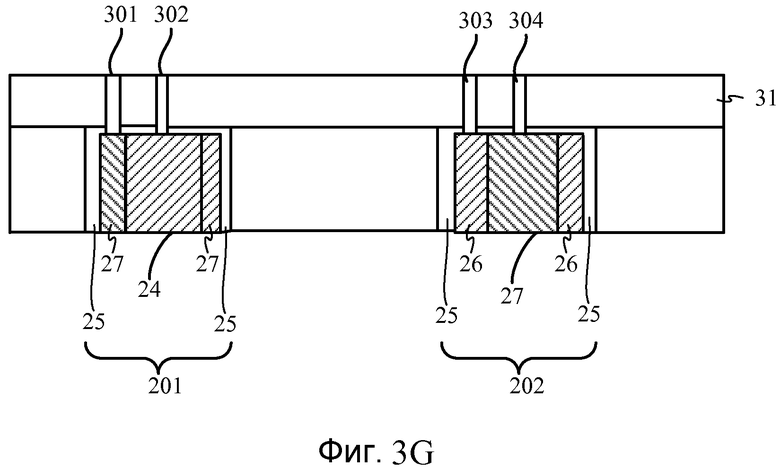

Фиг. 2B иллюстрирует такое вертикальное устройство 200 с парой диодов 201 и 202. Диод 201 содержит P-материал 27, который окружает N-материал 24, а диод 202 содержит N-материал 26, который окружает P-материал 27. Изолятор 25 разделяет каждый диод 201, 202 от полупроводниковой подложки 28. Электродные соединения 29 обеспечивают доступ к секциям N и P. Следует отметить, что хотя в настоящем варианте осуществления описаны диоды, при необходимости могут быть сформированы транзисторы или любые другие активные элементы.

Толщина кремния, формирующего эти диоды 201, 202, в одном варианте осуществления составляет от 20 до 100 мкм, в результате чего диоды 201, 202 имеют относительно большие размеры и способны выдерживать высокие напряжения при событиях электростатического разряда. Эффективная площадь диода увеличивается путем использования площади поверхности периферии переходного отверстия, которое может иметь, по существу, цилиндрическую форму. Иначе говоря, применение трехмерной конструкции вместо стандартной двухмерной конструкции увеличивает общую активную площадь при использовании одинаковой площади, занимаемой телом компонента на плате. Следует отметить, что когда кристаллы 21, 22 располагаются друг на друге, как показано на Фиг. 2A, оба кристалла 21, 22 могут совместно использовать общий набор ESD-диодов 201, 202. Кроме того, один диод может быть сформирован на одной микросхеме, тогда как другой диод (или другие части одного или более диодов) может быть сформирован на другой микросхеме.

Фиг. 3A-3G иллюстрируют варианты осуществления процесса формирования диодов внутри сквозных кремниевых переходных отверстий (TSV) относительно вариантов осуществления, показанных на Фиг. 2A и 2B.

Фиг. 3A иллюстрирует переходное отверстие, сформированное путем травления. Далее, изолирующий материал 25 осаждается на кремнии 30 (или другом полупроводниковом материале).

На Фиг. 3B проиллюстрирован N-материал 26, осажденный в оба пространства диода поверх изолирующего материала 25.

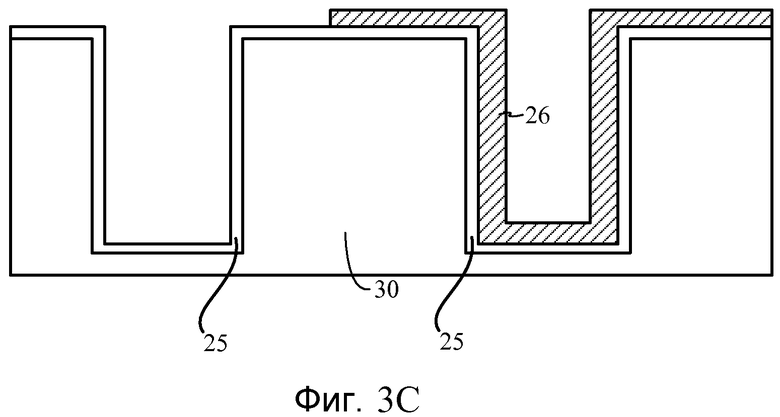

На Фиг. 3C проиллюстрирован N-материал 26, селективно вытравленный (в этом примере) из левого диода или пространства. N-материал 26 остается в пространстве правого диода.

На Фиг. 3D проиллюстрирован P-материал 27, осажденный в пространстве левого диода и в пространстве правого диода.

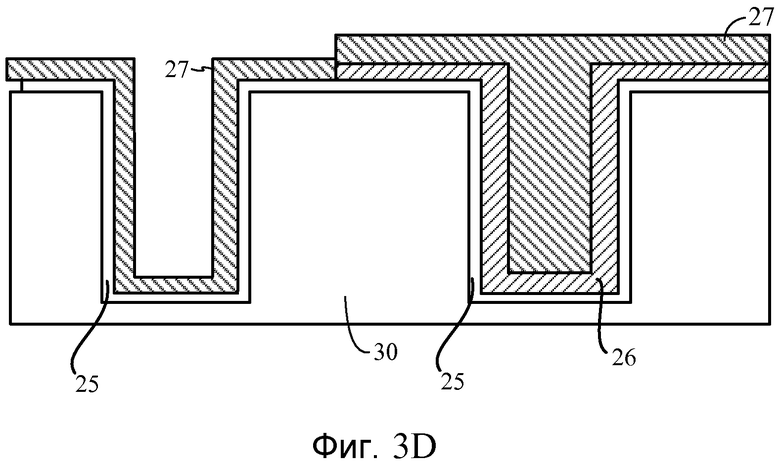

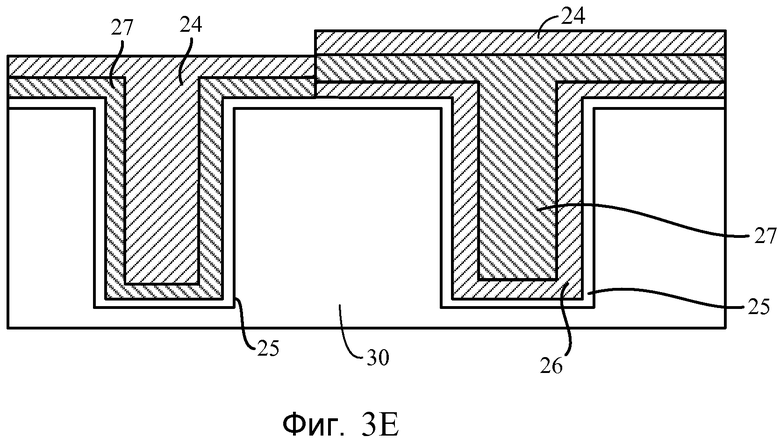

На Фиг.3E проиллюстрирован N-материал 24, осажденный в пространстве левого диода и в пространстве правого диода.

На Фиг. 3F проиллюстрирована полировка или удаление лишнего материала иным способом, чтобы получить диоды PN и NP. В еще одном варианте осуществления в "пространстве диода" вместо диодов NP и PN, описанных выше, создаются транзисторы NP и PN (или другие активные элементы).

После этого нормальная схема активного слоя 31 может быть изготовлена по известному способу. Осаждение оксида (не показано) изолирует полученную схему. Далее, могут быть сформированы контакты 301, 302, 303 и 304, чтобы обеспечить доступ к диодам. Эти контакты могут быть сформированы множеством путей, и при желании они могут представлять собой провода, контактные площадки или их комбинации. Например, контактные площадки 302, 303 могут представлять собой контактные площадки ввода/вывода, контакт 301 может соединяться с Vdd, а контакт 304 может соединяться с Vss, как показано на Фиг.4.

Согласно одному варианту осуществления площадь диодов PN или NP достаточна для надежной обработки (рассеивания) электростатических разрядов. Эти разряды могут быть приблизительно от 100 Вольт до нескольких тысяч Вольт.

Фиг.3G иллюстрирует множество TSV, открытых сзади (снизу) путем полировки. Далее, осаждается изолирующий слой (не показан) и переходное отверстие вытравливается таким образом, чтобы соединения к задней стороне диодов можно было реализовать с использованием соединений 405 кристалл-кристалл (Фиг.4). Используя эти соединения задней стороны, нормальная схема на активном слое другого многоуровневого кристалла 400 (Фиг.4) может связываться с другими TSV и применять ESD-защиту на другом кристалле. В еще одном варианте осуществления соединение с задней стороны обеспечивает возможность соединения диодов с землей. Этот вариант осуществления может быть полезен, когда в трехмерном устройстве существует аналоговая схема, и может быть сокращено влияние шума.

Ссылаясь на Фиг.4, описана защита внутренней схемы 410 посредством диодов 201, 202 внутри переходных отверстий. Внутренняя схема 410 принимает сигналы от контактной площадки 420. Если напряжение принимаемого сигнала слишком низкое, то включается диод 201 правой стороны, соединенный с Vss, и ток протекает от контактной площадки 420 к Vss. Если же напряжение слишком высокое, то включается диод 202 и ток протекает от контактной площадки 420 к Vdd. Если напряжение лежит в допустимых пределах (например, если не происходит события ESD), то внутренняя схема 410 принимает сигнал от контактной площадки 420.

Следует отметить, что проиллюстрированные процессы являются типовыми процессами в производстве полупроводников, и для изготовления устройства ESD-защиты в вертикальном направлении между активными слоями полупроводникового устройства может использоваться любой известный способ. Кроме того, наряду с тем, что в данном описании внимание сконцентрировано на изготовлении устройств ESD-защиты в переходных отверстиях, также могут быть изготовлены другие типы устройств. Одним из типов устройств, которые могут быть изготовлены с использованием идей настоящего изобретения, являются устройства и схемы управления питанием. Сверх того, следует отметить, что в некоторых ситуациях часть активного устройства может быть сформирована на кристалле, в котором сформировано переходное отверстие.

Хотя настоящее изобретение и его преимущества были подробно описаны в конкретных примерах, следует понимать, что в рамках сущности и объема настоящего изобретения могут быть выполнены различные изменения, замены и преобразования. Более того, объем настоящего изобретения не ограничивается конкретными вариантами осуществления процесса, устройства, изделия, химического соединения, средства, способов и этапов, описанных в настоящей спецификации. Из раскрытия настоящего изобретения специалистам в данной области техники будет очевидно, что процессы, устройства, изделия, химические соединения, средства, способы или этапы, которые существуют в настоящее время или будут разработаны в будущем и которые выполняют, по существу, ту же функцию или достигают, по существу, такого же результата, как соответствующие варианты осуществления, описанные выше, могут быть использованы согласно настоящему изобретению. Соответственно, прилагаемая формула изобретения предназначена для охвата всех таких процессов, устройств, изделий, химических соединений, средств, способов или этапов в рамках объема настоящего изобретения.

Изобретение относится к системам и способам для обеспечения защиты от электростатического разряда в трехмерных многоуровневых интегральных схемах. Сущность изобретения: устройство трехмерной (3-D) многоуровневой интегральной схемы содержит первый и второй полупроводниковые кристаллы, наложенные друг на друга, множество сквозных переходных отверстий, сформированных, чтобы проходить, по существу, между активными слоями первого и второго полупроводниковых кристаллов, и выполненных с возможностью обеспечения связи между первым и вторым полупроводниковыми кристаллами, и активную схему, сформированную, по меньшей мере, частично внутри, по меньшей мере, одного из множества сквозных переходных отверстий, причем первый и второй полупроводниковые кристаллы совместно используют активную схему, по меньшей мере, для защиты от электростатического разряда. Изобретение позволяет осуществить экономию пространства и сократить площадь кристалла, требуемую для схемы ESD-защиты. 3 н. и 8 з.п. ф-лы, 12 ил.

1. Устройство трехмерной (3-D) многоуровневой интегральной схемы, содержащее:

первый и второй полупроводниковые кристаллы, наложенные друг на друга,

множество сквозных переходных отверстий, сформированных, чтобы проходить, по существу, между активными слоями первого и второго полупроводниковых кристаллов, и выполненных с возможностью обеспечения связи между первым и вторым полупроводниковыми кристаллами, и

активную схему, сформированную, по меньшей мере, частично внутри, по меньшей мере, одного из множества сквозных переходных отверстий, причем первый и второй полупроводниковые кристаллы совместно используют активную схему, по меньшей мере, для защиты от электростатического разряда.

2. Устройство по п.1, в котором упомянутая активная схема содержит полупроводниковые устройства.

3. Устройство по п.1, в котором упомянутая активная схема содержит, по меньшей мере, одно устройство защиты от электростатического разряда (ESD).

4. Устройство по п.3, в котором устройство ESD-защиты содержит диод.

5. Устройство по п.1, в котором упомянутая активная схема содержит устройства с P/N-переходом.

6. Устройство по п.1, в котором упомянутая активная схема сформирована в сквозных переходных отверстиях в обоих из первого и второго полупроводниковых кристаллов.

7. Способ изготовления устройства трехмерной (3-D) многоуровневой интегральной схемы, содержащий этапы, на которых:

накладывают первый полупроводниковый кристалл на второй полупроводниковый кристалл,

формируют множество сквозных переходных отверстий, по существу, между активными слоями первого и второго полупроводниковых кристаллов, причем множество сквозных переходных отверстий выполнено с возможностью обеспечения связи между первым и вторым полупроводниковыми кристаллами, и

формируют активную схему, по меньшей мере, частично внутри, по меньшей мере, одного из множества сквозных переходных отверстий, причем первый и второй полупроводниковые кристаллы совместно используют активную схему, по меньшей мере, для защиты от электростатического разряда.

8. Способ по п.7, в котором упомянутая активная схема содержит схему защиты от электростатического разряда (ESD).

9. Способ по п.8, в котором упомянутая схема ESD-защиты содержит диод.

10. Способ защиты от электростатического разряда в устройстве трехмерной (3-D) многоуровневой интегральной схемы, содержащем первый и второй полупроводниковые кристаллы, наложенные друг на друга, и множество сквозных переходных отверстий, сформированных, по существу, между активными слоями первого и второго полупроводниковых кристаллов, причем множество сквозных переходных отверстий выполнено с возможностью обеспечения связи между первым и вторым полупроводниковыми кристаллами, при этом способ содержит этапы, на которых:

формируют схему защиты от электростатического разряда (ESD), по меньшей мере, частично внутри, по меньшей мере, одного из множества сквозных переходных отверстий, и

соединяют контактные площадки ввода/вывода, по меньшей мере, одного из первого и второго полупроводниковых кристаллов со схемой ESD-защиты, причем первый и второй полупроводниковые кристаллы совместно используют схему ESD-защиты.

11. Способ по п.10, в котором упомянутая схема ESD-защиты содержит диод.

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| US 5807791 A, 15.09.1998 | |||

| US 5703747 A, 30.12.1997 | |||

| RU 99116320 A, 10.07.2001. | |||

Авторы

Даты

2012-12-10—Публикация

2009-09-01—Подача