Устройство относится к области цифровой техники и может быть использовано в вычислительной технике, системах передачи и обработки информации, при построении различного рода управляющих автоматов циклического действия, то есть устройств, принимающих при воздействии входных сигналов одну и ту же последовательность внутренних состояний (состояний элементов памяти), предназначенных для формирования последовательностей управляющих сигналов.

Наиболее типичными, простыми и наиболее исследованными устройствами такого вида являются счетчик и распределители импульсов, а также более сложные управляющие автоматы циклического действия с произвольным алгоритмом функционирования (например, устройства управления процессоров, формирующие на своих выходах последовательности сигналов, управляющие операционными устройствами, генераторы кодов, а также кодирующие и декодирующие устройства систем передачи информации).

Устройства циклического действия традиционно выполняется в виде счетчика импульсов совместно с дешифратором. Наиболее распространенным примером такого подхода являются распределители импульсов. При этом важной является возможность использования логических элементов, входящих в счетчик, для реализации дешифратора, что позволяет уменьшать количество оборудования.

Название предлагаемого изобретения выбрано исходя из того, что предлагаемое устройство при частной реализации может выполнять функции всех вышеперечисленных устройств циклического действия, то есть обладать универсальностью, позволяет строить различные его варианты и выбирать наиболее подходящий с учетом используемой элементной базы (например, с учетом ограничений на реализацию логических элементов и элементов памяти при разработке микросхем), а также других требуемых параметров, отличается оригинальностью структуры. То есть название принято обобщающего характера и не отражает частную функцию (счетчик, распределитель, устройство и т.п.), а отражает общее понятие (выражающее функцию), охватывающее разные частные формы его реализации (см. «Правила составления, подачи и рассмотрения заявки…». П.3.3.1 (6)).

Показателями технического уровня цифрового устройства циклического действия, как и других видов цифровых устройств, являются используемое для его реализации количество оборудования и быстродействие.

Известны устройства, которые обеспечивают высокие показатели по быстродействию и экономии количества оборудования.

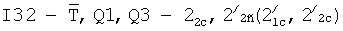

Это, например, устройство в соответствии с патентом на изобретение №2397610 («Цифровое устройство для формирования последовательностей управляющих сигналов», зарегистрированное 20.08.2010 г.). Пример его реализации приведен на Фиг.1.

Выберем его в качестве прототипа.

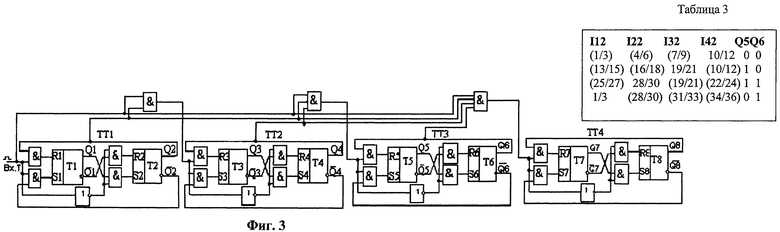

Другое широко используемое устройство с высоким быстродействием (счетчик с параллельным переносом информации), приведенное на схеме Фиг.3, (см. также, например, Ю.Ф.Опадчий, О.Г.Глудкин, А.И.Гуров. Аналоговая и цифровая электроника. Полный курс. М.: Горячая линия - Телеком. 2000 г., Рис.17.35, Рис.17.8, Рис.17.4а; в схеме Фиг.3 приведена подробная схема T-триггера с изображением RS-триггеров и вентилей (Рис.17.8, Рис.17.4а)), используем в качестве аналога.

В изобретении №2397610, H03K 5/15 (прототипе) описано цифровое устройство для формирования последовательностей управляющих сигналов, содержащее два или более последовательно соединенных блоков, являющихся последовательностными устройствами, имеющими по несколько входов и выходов, каждый из которых соответствует одному внутреннему состоянию, меняющими в одной очередности свои внутренние состояния только при воздействии активного уровня на один из очередных входов и не меняющие внутреннее состояние при переходе активного уровня в пассивный, что в сочетании с оригинальной организацией связей между выходами и входами блоков таких, что после сигнала на очередном входе последующего блока, переключающем этот блок в очередное внутреннее состояние «j» в данном цикле предыдущего блока, следующим сигналом, переключающим последующий блок в следующее внутреннее состояние (j+1) в следующем цикле предыдущего блока, является сигнал, предшествующий по циклу предыдущего блока сигналу, переключающему последующий блок во внутреннее состояние «j» позволяет экономить количество оборудования, повышать быстродействие, обеспечивать регулярность (однородность) структуры.

Однако в этом устройстве можно дополнительно повысить быстродействие за счет замены каждого из единичных выходов блоков комбинациями выходов тактовых сигналов и триггеров данного и предыдущего блоков, участвующих в формировании данного выхода.

При этом на входы всех последующих блоков вместо единичных выходов предыдущего блока подаются комбинации выходов всех предыдущих блоков, каждая из которых соответствует одному из его состояний, в соответствии с принятой организацией связей в случае единичных входов и выходов в прототипе.

То есть каждая единичная шина заменяется комбинацией шин, являющихся выходами триггеров всех предыдущих блоков и тактовых сигналов, участвующих в формировании сигнала на соответствующей единичной шине.

Такая замена единичных шин на комбинацию шин, активный уровень на которых формирует сигнал на единичной шине в схеме прототипа, позволяет повысить быстродействие, так как из цепи передачи информации исключаются вентили, формирующие сигнал на единичной выходной шине (но они остаются в схеме для переключения триггеров в своем блоке), а вся информация подается на каждый блок со всех предыдущих блоков непосредственно, вызывая изменение его состояния. То есть устройство работает с параллельным переносом информации, в отличии от прототипа, где осуществляется сквозной перенос информации.

При этом несколько увеличивается количество оборудования по сравнению с прототипом из-за увеличения числа входов вентилей, принимающих информацию в каждом блоке, но уменьшение его за счет принятого алгоритма переключения состояний блоков и принципа организации связей блоков, принятых в прототипе, сохраняется, что приводит в результате к значительной экономии количества оборудования в целом.

В результате достигается его значительная экономия по сравнению с известными схемами с параллельным переносом, например по сравнению с аналогом Фиг.3.

Все вышеописанное поясним на конкретных примерах.

На Фиг.1 приведена схема счетчика, ярко иллюстрирующая прототип, так как по сравнению со схемой с таким же составом блоков как и широко известная схема на T-триггерах за счет выбора алгоритма функционирования блоков и оригинальной организации соединений между их входами и выходами позволяет экономить количество оборудования и повысить быстродействие. Схема состоит из трех блоков и имеет коэффициент счета КСЧ=18. При этом все блоки, кроме первого, имеют КСЧ=3, вместо 2-х в схеме на T-триггерах (см. описание изобретения №2397610). Быстродействие повышается за счет того, что при использовании указанного принципа триггеры переключаются не последовательно друг за другом, когда в цепочке переноса информации участвуют последовательно соединенные триггеры всех блоков и вентили на входах триггеров (последовательный перенос), а последовательно с появлением сигнала на выходах последовательно соединенных вентилей. Например, если в схеме Фиг.1 единица появляется на выходе вентиля «И» (на входе S1), то она может проходить цепочку: вентиль на входе S1 и далее через выход I 21 и вентиль на входе R3, выход I 42 и вентиль на входе S5, вызывая переключение соответствующих триггеров. Суммарная задержка определяется суммой времен переключения вентилей. На это нужно значительно меньше времени, чем при последовательном переносе, где последовательно переключаются и вентили и триггеры, так как в этом случае суммарная задержка определяется суммой времен переключения вентилей и триггеров. То есть в схеме Фиг.1 информация распространяется по последовательной цепочке вентилей (сквозной перенос информации). И тот и другой принцип широко известны, но в данном случае сквозной перенос организован совершенно по-другому, в сравнении с известными случаями, так как реализуется в рамках принципа, заложенного в прототипе.

Быстродействие прототипа можно существенно увеличить путем изменения характера связей между блоками, приводящего к параллельному переносу информации.

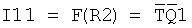

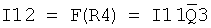

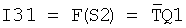

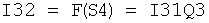

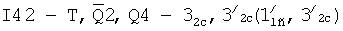

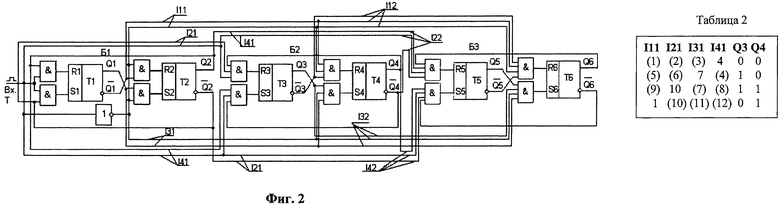

На Фиг.2 приведена схема счетчика, аналогичная по функциям схеме Фиг.1 с КСЧ=18, но реализующая параллельный перенос информации. Каждый из выходов блоков Б1 (I11, I21, I31, I41), Б2 (I12, I22, I32, I42) заменяется на выходы соответствующих триггеров и тактовых сигналов, формирующих данный выход.

В обозначениях выходов первая цифра - это номер выхода, а вторая - номер блока.

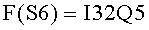

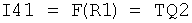

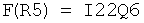

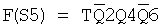

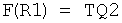

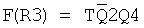

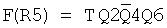

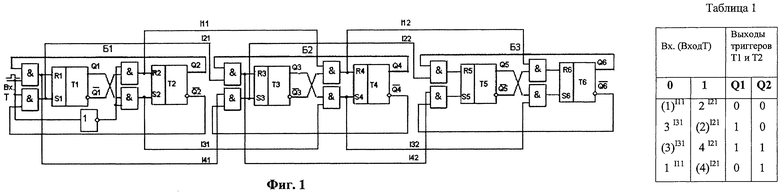

Логические функции, описывающие цепи, воздействующие на входы триггеров и на выходы блоков Б1 и Б2 в схеме Фиг.1

Здесь все логические функции «I» реализованы 2- входовыми схемами «И». Следовательно, выходы блоков Б1 и Б2 заменяются: I11 на выходы  и

и  ; I21 на T и

; I21 на T и  ; I31 на

; I31 на  и Q1; I41 на T и Q2; I12 на

и Q1; I41 на T и Q2; I12 на  ,

,  ,

,  ; I22 на T, Q2,

; I22 на T, Q2,  ; I32 на

; I32 на  , Q1, Q3; I42 на T,

, Q1, Q3; I42 на T,  ,Q4, что отображено на схеме Фиг.2.

,Q4, что отображено на схеме Фиг.2.

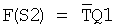

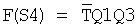

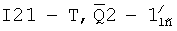

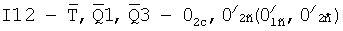

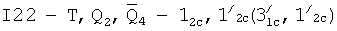

Логические функции, описывающие цепи, воздействующие на входы триггеров в схеме Фиг.2

Цепи блока Б1 остаются без изменения, так как они определяются входными сигналами.

Детально работу схемы Фиг.2 удобно рассматривать по тем же таблицам переходов, что и схемы Фиг.1 в описании прототипа (Здесь эти таблицы 1, 2, 3 приведены). В описании прототипа схема Фиг.1 обозначена как Фиг.2.

Из схемы видно, что при переходе устройства из одного состояния в другое переключается один вентиль и один RS-триггер, что является фактически предельно возможным случаем, так как в любой логической схеме существует переход, когда триггер переключается под воздействием вентиля. Это определяет максимально возможное быстродействие.

В схеме по Фиг.1 переключаются последовательно несколько вентилей и триггер.

В предлагаемой схеме используются RS-триггеры, в то время как в широко применяемых схемах с параллельным переносом используются сложные триггеры, внутри которых имеются RS-триггеры и вентили. Следовательно, в этом случае при смене состояния переключается вентиль, обеспечивающий параллельный перенос, вентиль внутри сложного триггера (например, T-триггера, JK-триггера, D-триггера и других) и RS-триггер внутри сложного триггера, что значительно снижает быстродействие.

Это видно из схемы Фиг.3, являющейся широко используемой (См., например, Ю.Ф.Опадчий, О.Г.Глудкин, А.И.Гуров. Аналоговая и цифровая электроника. Полный курс. М.: Горячая линия - Телеком. 2000 г., Рис.17.35, Рис.17.8, Рис.17.4а).

В схеме Фиг.3 приведена подробная схема Т-триггера с изображением RS-триггеров и вентилей (Рис.17.8, Рис.17.4а).

Из этой схемы видно, что при переходе из одного состояния в другое переключаются схема «И», обеспечивающая перенос, схема «И» внутри T-триггера на входе RS-триггера и RS-триггер, то есть на один вентиль больше, чем в предлагаемой схеме.

Эта схема при коэффициенте счета КСЧ=16 использует в 4-х блоках, являющихся T-триггерами, и в цепях переноса всего 39 вентилей (схема RS-триггера состоит из 2-х вентилей).

Предлагаемая схема при большем коэффициенте счета (КСЧ=18) использует 25 вентилей. Экономия (39-25)/39≈36% при значительно большем быстродействии.

По сравнению со схемой прототипа Фиг.1 проигрыш в количестве оборудования заключается в данном случае в увеличении числа входов схем «И» (кроме блока Б1), но зато получается существенный выигрыш в быстродействии.

Необходимо отметить, что при увеличении числа блоков проигрыш в количестве оборудования по сравнению со схемой Фиг.1 будет увеличиваться из-за увеличения числа входов схем «И».

Схема прототипа обеспечивает и достаточно высокое быстродействие и значительную экономию оборудования и однородность структуры.

Существуют устройства циклического действия (счетчики распределители и др.), в которых при переходе из состояния в состояние переключается один вентиль и один RS-триггер. Это счетчики в коде Грея и счетчики в коде Джонсона, но они значительно проигрывают в количестве оборудования и устройству по основному изобретению и устройству по предполагаемому дополнительному изобретению. Это обосновывается в описании прототипа.

Представим предлагаемое изобретение в виде обобщенной схемы Фиг.4, отражающей общее понятие, так же как в прототипе, охватывающем разные частные формы его реализации (См. «Правила составления, подачи и рассмотрения заявки…» П.3.3.1(6)). То есть эта схема отражает сущность изобретения в обобщенном виде.

Устройство содержит блоки 1, 2, …P. Входы и выходы блоков, кроме входов входного блока и выходов выходного блока, представляют собой не единичные шины, а комбинации определенных выходов тактовых сигналов и триггеров. Порядок соединения комбинации входов и выходов такой же как и единичных, соответствующих им.

Входной блок 1 имеет номера входов 01, 11, …n1, где нижний индекс является номером блока. Эти входы полностью идентичны входам прототипа. Выходной блок «P» имеет номера выходов 0⁄ p, 1⁄ p, …n⁄ p, где нижний индекс - номер блока. Эти выходы также идентичны выходам прототипа.

Блок 1 имеет комбинации выходов 0⁄ 1c, 1⁄ 1c, 2⁄ 1c…i⁄ 1c-1, i⁄ 1c, i⁄ 1c+1…n⁄ 1c-1, n⁄ 1c (в нижнем индексе 1 - номер блока, c - означает комбинацию).

Каждая комбинация выходов является выходами триггеров и тактовых входов, определяющих переход в очередное состояние блока.

Комбинации входов блоков (кроме первого) 0ic, 1ic, …nic, где i - номер блока. Каждая комбинация определяется той комбинацией выходов предыдущего блока, с которой она соединяется.

Комбинация выходов других блоков, кроме первого, состоит из комбинации, которая подана на соответствующий вход с тем же номером и комбинации выходов триггеров данного блока, определяющих переход к состоянию, в котором находится блок.

То есть комбинация выходов 02с, 02 ⁄ c блока 2 состоит из комбинации входов 02c и комбинации выходов триггеров 02 ⁄ c, данного блока 2, определяющих переход в состояние «0» блока 2.

Комбинация выходов 12c, 12 ⁄ c блока 2 состоит из комбинации входов 12с и комбинации выходов триггеров данного блока 2, определяющих переход в состояние 1 блока 2 и т.д.

Комбинации выходов и входов соединяются в том же порядке, что соответствующие им единичные входы и выходы в прототипе.

В данном случае на вход 02с подается комбинация выхода блока 1 01 ⁄ c, а на вход 12с комбинация выхода блока 1 n1 ⁄ с в соответствии со схемой Фиг.4 и т.д.

Рассмотрим работу схемы Фиг.4 совместно со схемами по Фиг.1 и 2. Схема Фиг.4 является обобщенной (то есть в общем виде отображающей суть изобретения) и при задании конкретных ее параметров приводит к частному решению.

Схема Фиг.2 является таким частным решением при числе комбинаций входов и выходов блоков равном 4 (от «0» до nic или ni ⁄ c), которое равно числу внутренних состояний блоков при n1 ⁄ c=n2cn=n⁄ 2c=…nic=n⁄ ic=…n(p-1),c=n⁄ (p-1), c=npc=3.

Входы блока 1 в частном случае Фиг.2 являются тактовыми входами T и  .

.

Выходы блока «Р» и формирующие их цепи на Фиг.2 не показаны, так как эти выходы формируются из выходов логических схем (вентилей) блоков в виде комбинационной схемы, что является тривиальной задачей. Это показано на Фиг.4 выходами блоков 1, 2, … и т.д. и входами Р выходного блока P, по которому поступают комбинации сигналов от других блоков, и выходами блока Р.

Каждый блок Фиг.2 состоит из 2-х триггеров с выходами Q1Q2, Q3Q4, Q5Q6 для формирования четырех выходных комбинаций (22=4).

Схема Фиг.2 отличается от схемы Фиг.1 существенными признаками предлагаемого изобретения. В Фиг.2 единичные выходы Фиг.1 заменены на комбинации выходов, состоящих из входов вентилей, формирующих единичные выходы в Фиг.1.

Эти входы вентилей являются комбинациями тактовых сигналов и выходов триггеров, вызывающих переход в данное состояние блока.

Работа схемы Фиг.1 и 2 описывается таблицами переходов (таблица 1 - блок 1; таблица 2 - блок 2; таблица 3 - блок 3).

При этом в вершинах столбцов таблиц применительно к схеме Фиг.1 обозначены единичные выходы вентилей (двухвходовых схем «И»), а применительно к схеме Фиг.2 это комбинации переменных, подаваемых на входы этих вентилей (кроме таблицы 1, где в вершинах столбцов состояние входа Т). Это приводит к вышеприведенным логическим выражениям для цепей, воздействующих на входы триггеров в обеих схемах.

Более подробно принцип построения таблиц переходов приведен в описании прототипа.

Если число входов и выходов блоков обобщенной схемы принять равным 4-м (кроме входов первого блока и выходов последнего), как указано выше, при числе блоков равным 3-м, то в обозначениях обобщенной схемы выходы блоков Фиг.1 и 2 выглядят так: I11 для схемы Фиг.1 и выходы

и

и  для схемы Фиг.2 - это выход 01 ⁄ с. И далее соответственно

для схемы Фиг.2 - это выход 01 ⁄ с. И далее соответственно

;

;  ;

;  ;

;

;

;  ,

,

;

;  .

.

Из вышеизложенного следует, что устройства, реализованные в соответствии с принципами предлагаемого изобретения, имеют большее быстродействие по сравнению с устройствами, основанными на принципах прототипа, в результате описанного усовершенствования порядка фиксации циклов предыдущего блока последующим путем замены единичных выходов и входов блоков на комбинации выходов и входов триггеров и тактовых сигналов, при сохранении порядка их соединения между собой.

При этом в прототипе требуется для его реализации несколько меньшее количество оборудования и обеспечивается большая однородность структуры, что в определенных условиях, когда не требуется по быстродействию показателей устройств, соответствующих предлагаемому изобретению, дает ему преимущества.

В случае, когда основным критерием является быстродействие, преимущества устройств, соответствующих предлагаемому изобретению, очевидны.

Оба вида устройств имеют преимущества по быстродействию и количеству оборудования по сравнению с другими устройствами такого же назначения.

Функционирование схемы, приведенной на Фиг.2, было проверено путем моделирования на ПЭВМ с использованием программы Electronics Workbench 6.0. На Фиг.5 приводится распечатка схемы, полностью соответствующей схеме Фиг.2, подвергавшейся моделированию, с использованием изображений логических элементов в соответствии с американским стандартом ANSI, принятых в этой программе.

В схеме раскрыта структура RS-триггеров на основе 2-х элементов «ИЛИ-НЕ», используется переключатель S4 для формирования входных сигналов, переключатель S3 для начальной установки RS-триггеров, а также индикаторы состояний триггеров (обозначены буквой X).

Схема состоит из 3-х блоков, полностью идентичны по структуре блокам Б1-Б3 на Фиг.2.

При этом каждый RS-триггер выполнен на 2-х элементах «ИЛИ-НЕ»: T1(U2A, U2B), T2(U2C, U1A) - блок Б1; T3(U6A, U6B), Т4 (U6C, U7A) - блок Б2; T5(U10A, U10B), Т6 (U10C, U11A) - блок Б3. Инвертор - U5A.

Схема функционирует в полном соответствии с таблицами переходов (таблица 1 - блок Б1, таблица 2 - блок Б2, таблица 3 - блок Б3), обеспечивая заданный коэффициент счета КСЧ=18. В таблицах переходов цифрами обозначены номера импульсов и пауз (символов), поступивших на вход для достижения данного состояния (Всего 36 символов за цикл - 18 импульсов и 18 пауз).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ УПРАВЛЯЮЩИХ СИГНАЛОВ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ ИНФОРМАЦИИ | 2016 |

|

RU2642395C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2008 |

|

RU2397610C2 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU423249A1 |

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| Устройство контроля параметров | 1983 |

|

SU1087962A1 |

| Устройство для @ -канального импульсного регулирования мощности в @ -фазной сети | 1985 |

|

SU1354359A1 |

| Устройство для обучения операторов | 1991 |

|

SU1785026A1 |

| Импульсный преобразователь переменного тока в переменный | 1988 |

|

SU1508321A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Фазометр | 1991 |

|

SU1817037A1 |

Изобретение относится к области цифровой технике и может быть использовано при построении различного рода автоматов циклического действия. Техническим результатом является повышение быстродействия и экономия количества оборудования. Устройство содержит последовательно соединенные блоки, принимающие при воздействии тактовых сигналов одну и ту же последовательность внутренних состояний; при этом переход к очередным состояниям осуществляется под действием активного уровня на соответствующих им входах и очередным состояниям соответствуют определенные выходы, после сигнала на очередных входах, являющихся выходами предыдущего блока, соответствующими определенным его состояниям, переключающих блок в очередное внутреннее состояние «j» в данном цикле предыдущего блока, следующим сигналом, переключающем последующий блок в следующее внутреннее состояние (j+1) в следующем цикле предыдущего блока, является сигнал предыдущего блока, соответствующий другому его внутреннему состоянию, предшествующий по циклу предыдущего блока сигналу, переключающему последующий блок в состояние «j», при этом выходами данного блока, соответствующими его очередному состоянию, и соответствующими им входами последующего блока являются входы тактовых сигналов и выходы триггеров данного и предыдущих блоков. 5 ил., 3 табл.

Цифровое устройство для формирования последовательностей управляющих сигналов с параллельным переносом, содержащее два или более последовательно соединенных блоков, являющихся последовательностными устройствами, принимающими при воздействии тактовых сигналов одну и ту же последовательность внутренних состояний; при этом переход к очередным состояниям осуществляется под действием активного уровня на соответствующих им входах и очередным состоянием соответствуют определенные выходы, а связи между выходами и входами соседних блоков такие, что после сигнала на очередных входах, являющихся выходами предыдущего блока, соответствующими определенным его состояниям, переключающих блок в очередное внутреннее состояние j в данном цикле предыдущего блока, следующим сигналом, переключающим последующий блок в следующее внутреннее состояние j+1 в следующем цикле предыдущего блока, является сигнал предыдущего блока, соответствующий другому его внутреннему состоянию, предшествующий по циклу предыдущего блока сигналу, переключающему последующий блок в состояние j, отличающееся тем, что выходами данного блока, соответствующими его очередному состоянию, и соответствующими им входами последующего блока являются входы тактовых сигналов и выходы триггеров данного и предыдущих блоков, определяющие переход к этому состоянию.

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2008 |

|

RU2397610C2 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU423249A1 |

| US 2003222689 А1, 04.12.2003 | |||

| JP 3094514 A, 19.04.1991. | |||

Авторы

Даты

2013-02-20—Публикация

2011-03-22—Подача