(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для импульсного регулирования мощности переменного тока | 1984 |

|

SU1244763A1 |

| Многоканальное устройство для импульсного регулирования мощности в @ подключенных через вентили к сети нагрузках | 1983 |

|

SU1226585A1 |

| Импульсный регулятор мощности | 1983 |

|

SU1111143A1 |

| Распределитель импульсов | 1979 |

|

SU856004A1 |

| Устройство для управления вентилем | 1982 |

|

SU1107230A1 |

| Устройство для управления многоканальным импульсным регулятором мощности переменного тока с @ -нагрузками | 1987 |

|

SU1545306A1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОВОГО СДВИГА ПЕРЕМЕННЫХ НАПРЯЖЕНИЙ В ЦИФРОВОЙ КОД | 1972 |

|

SU359756A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1994 |

|

RU2072550C1 |

| Устройство для управления вентилем | 1986 |

|

SU1513575A1 |

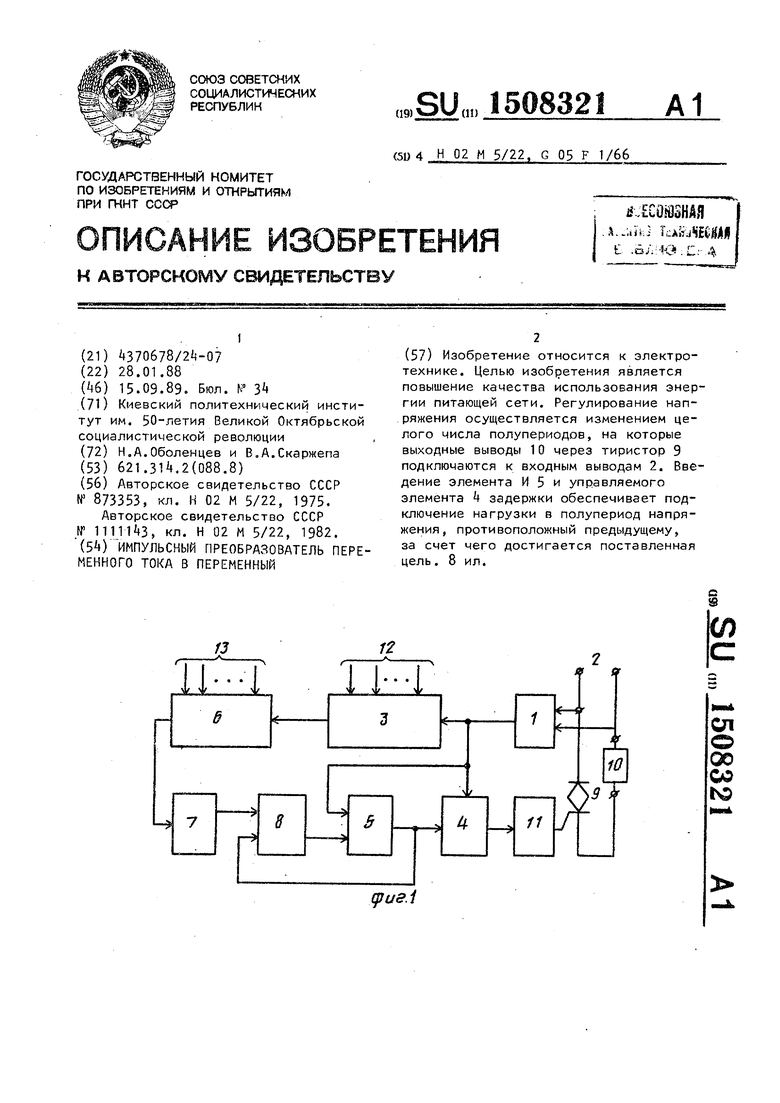

Изобретение относится к электротехнике. Целью изобретения является повышение качества использования энергии питающей сети. Регулирование напряжения осуществляется изменением целого числа полупериодов, на которые выходные выводы 10 через тиристор 9 подключаются к входным выводам 2. Введение элемента И 5 и управляемого элемента задержки 4 обеспечивает подключение нагрузки в полупериод напряжения, противоположный предыдущему, за счет чего достигается поставленная цель. 8 ил.

00 00 ls5

gjus.i

3150832

Изобретение относится к электротехнике .

Цель изобретения - повышение Качества использования энергии питаюи1ей ,. сети.

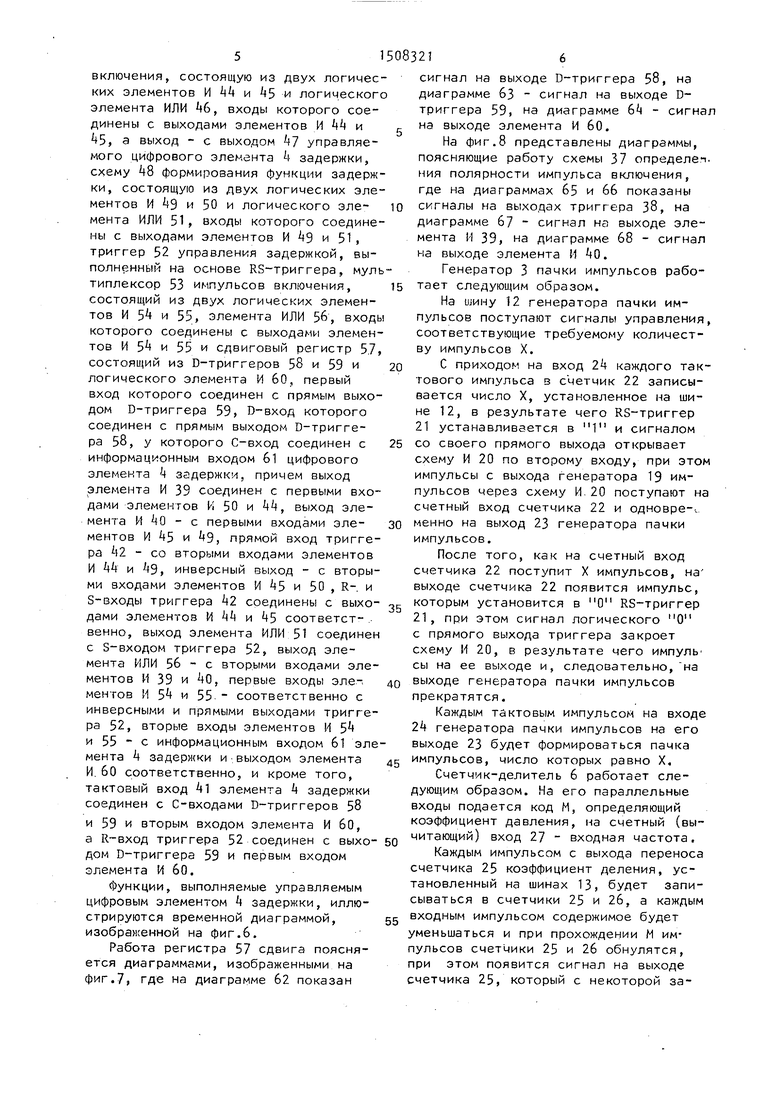

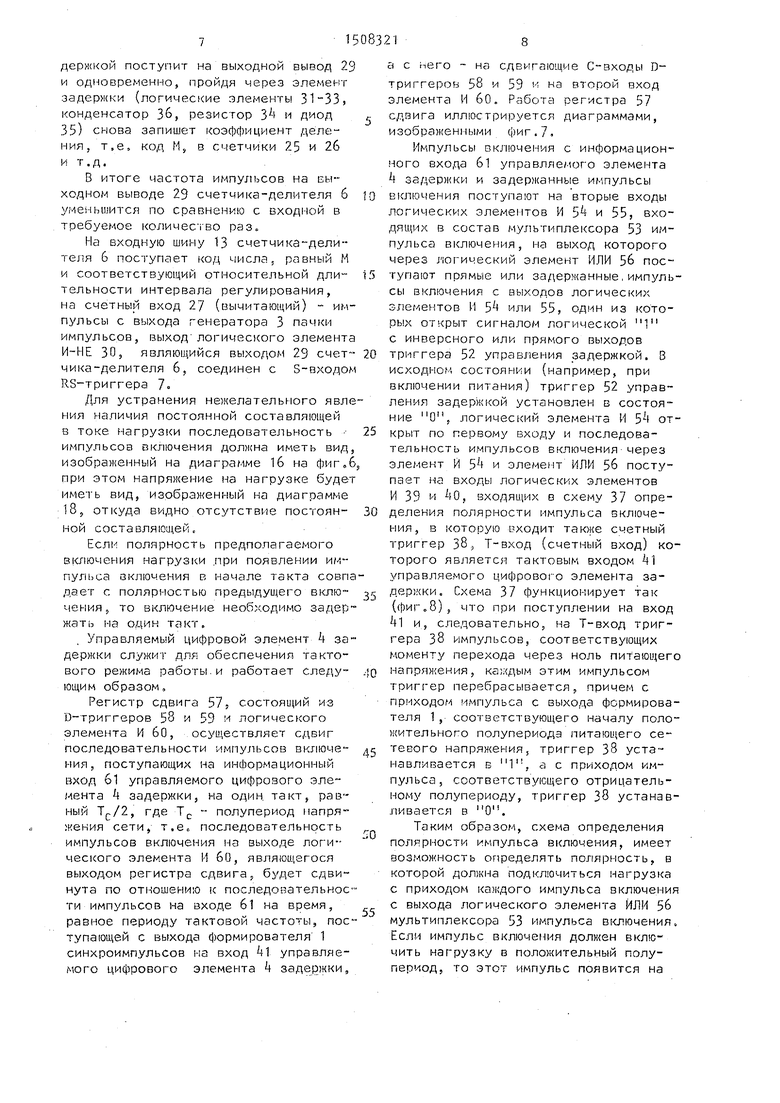

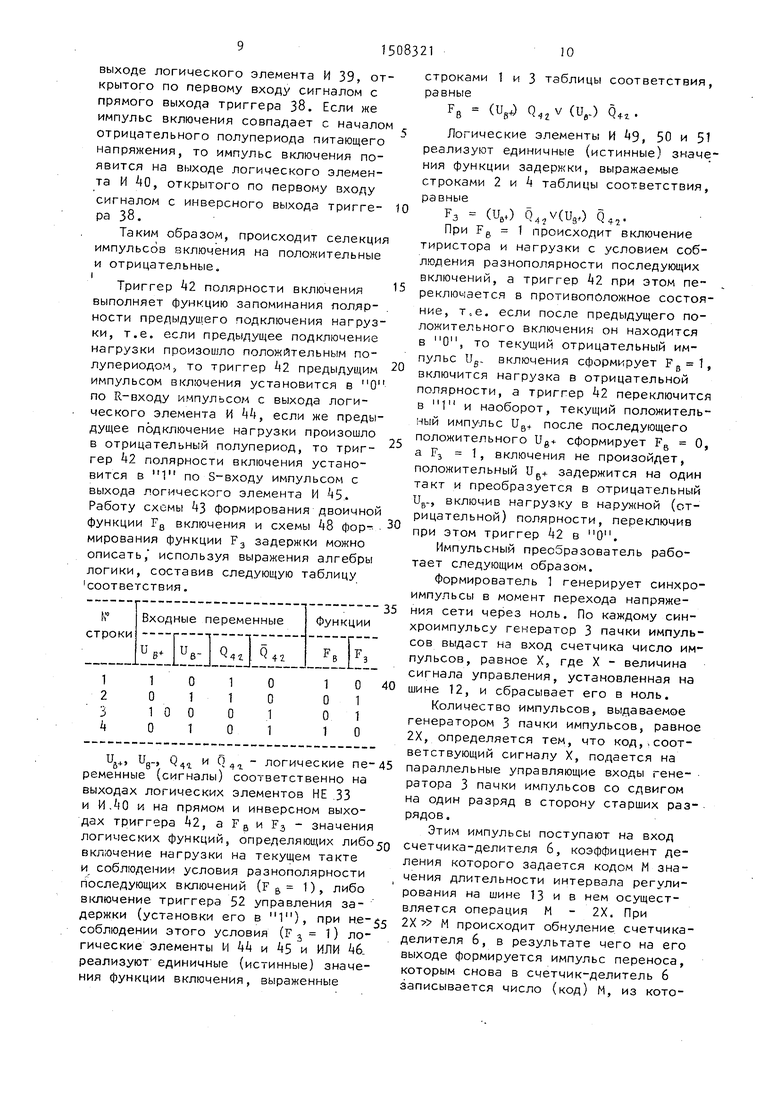

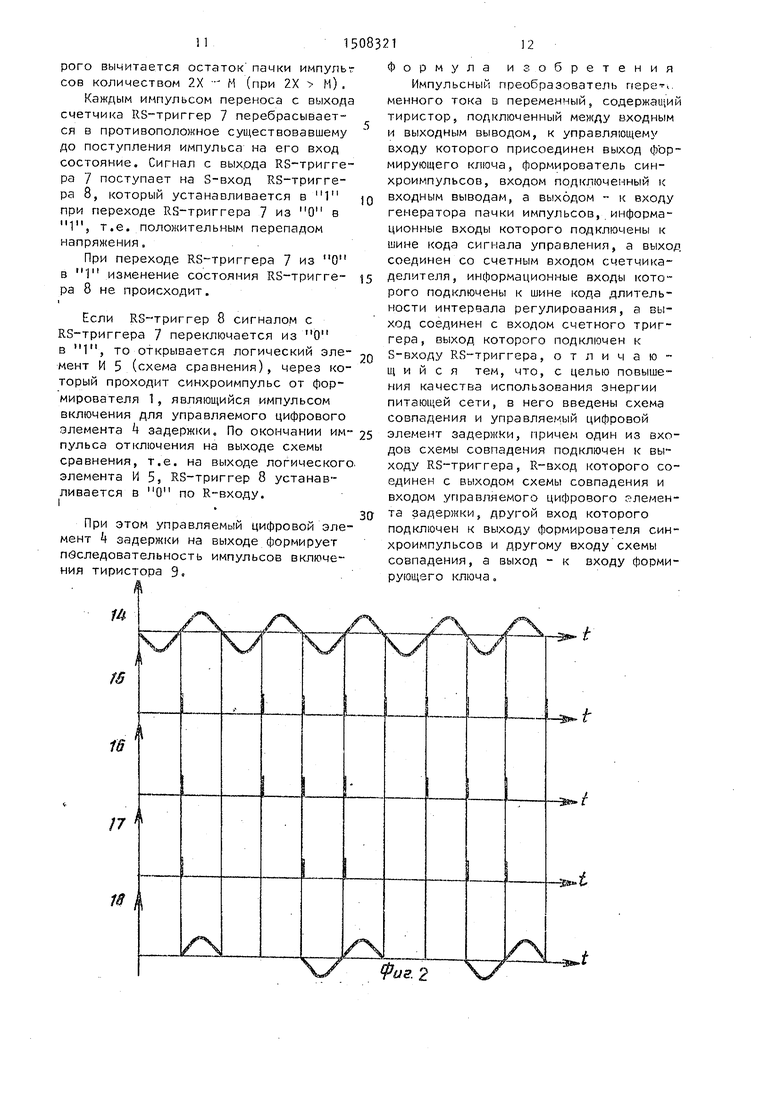

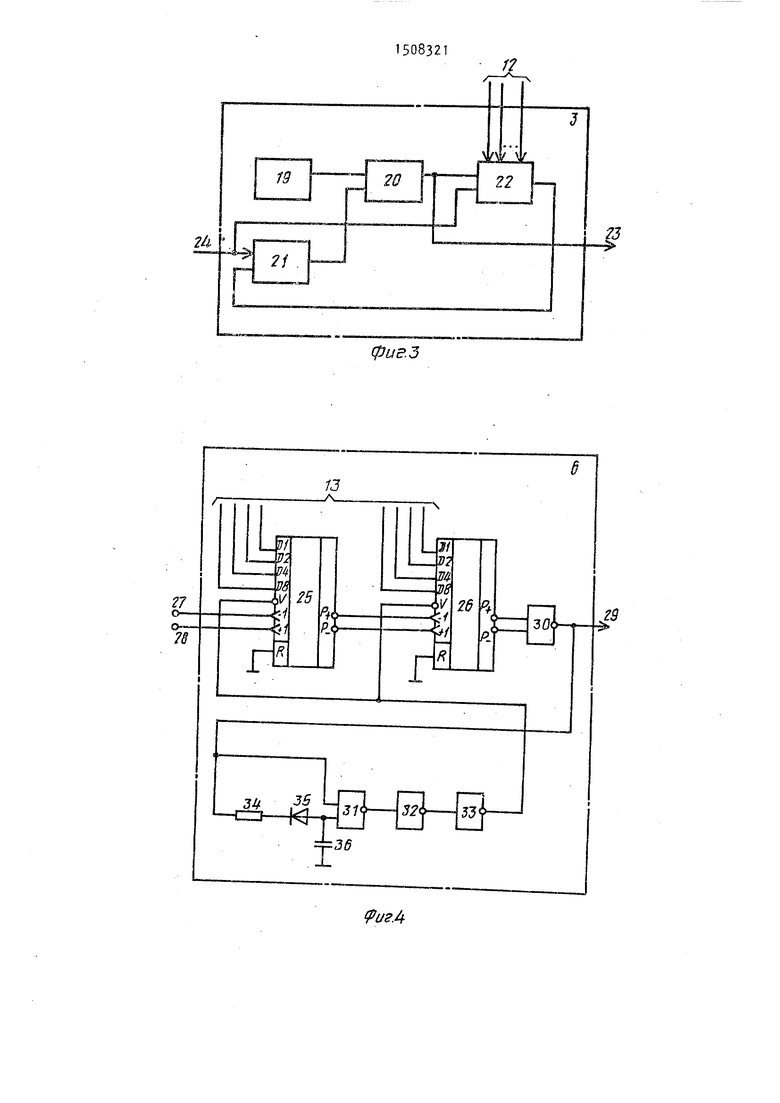

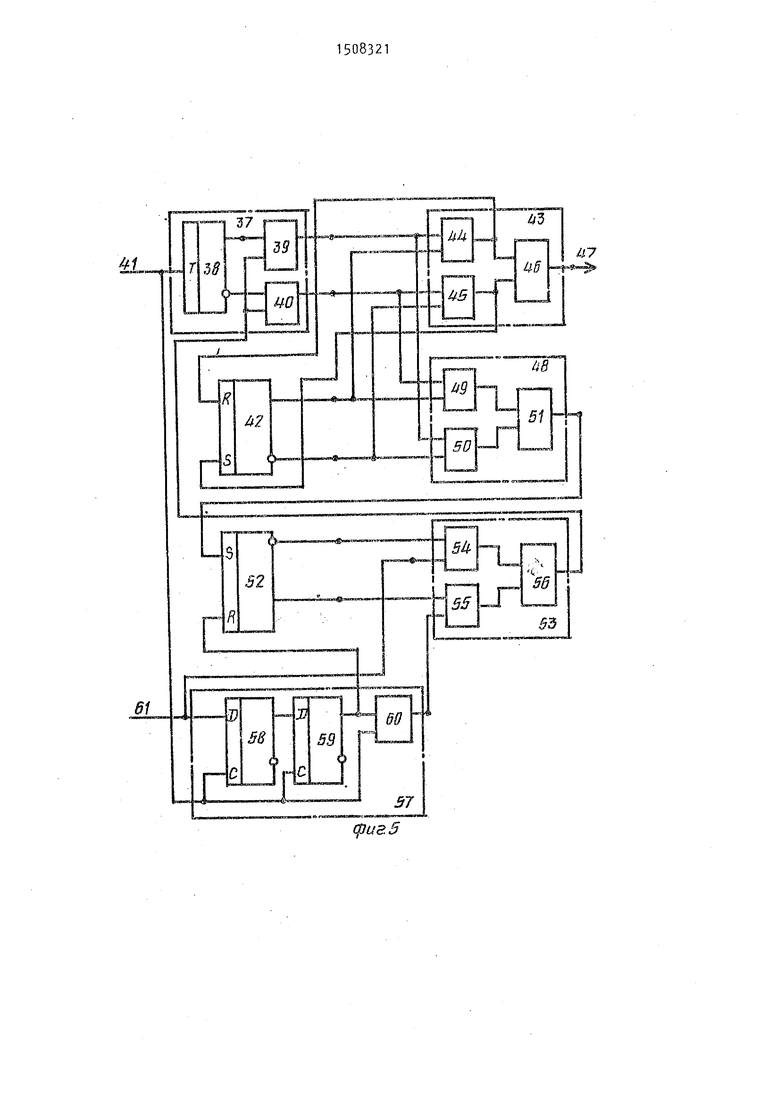

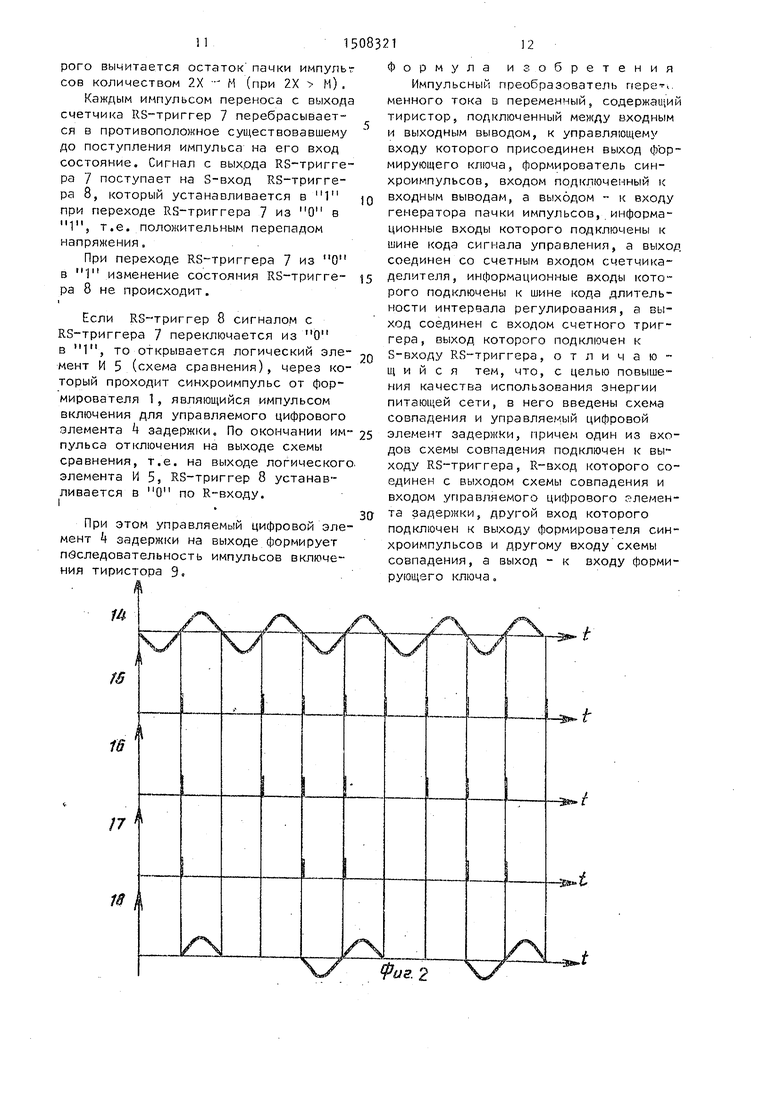

На фиг.1 изображена схема предла-- гаемого импульсного преобразователя на фиг.2 - диаграмма его работы на

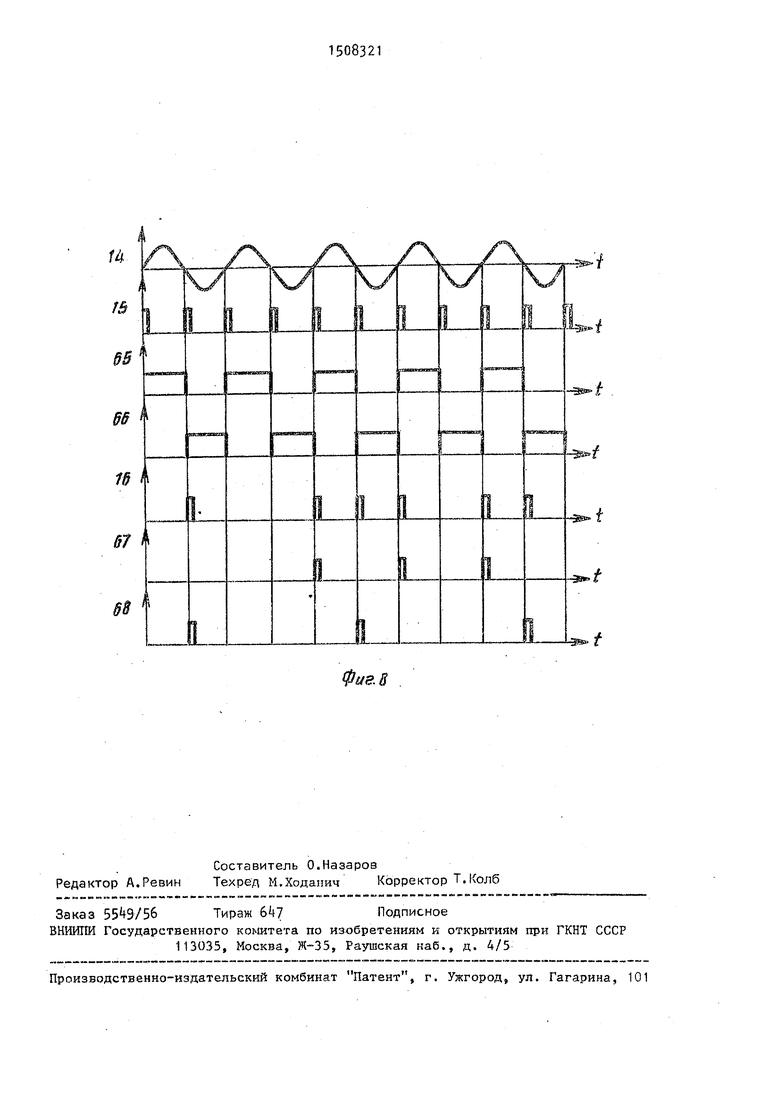

фиг.З принципиальная схема генера- тора пачки импульсов; на фиг.) принципиальная схема счетчика делителя частоты-, на фиг.5 принципиальная схема управляемого цчфроиого элемента задержки; на фиг,6-8 - диаграммы его работы.

Импульсный преобразователь содер.-жит формирователь 1 синхроимпульсов, соединенный своим входом с входными вводами 2, а выходом - с входом гене- ратора 3 пачки импульсов, тактовым входом управляемого цифрового элемента А задержки и первым входом схемы 5 совпадения. Выход , генератора 3 пачки импульсов соединен со счетным входом счетчика-делителя 6, выход которого через счетный RS-триггер 7 соединен со входом установки в 1 (3 входом) RS-триггера 8,, прямой выход которого соединен с вторым входом схемы 5 сов- падения. Выход 5 совпадения соединен с входом сброса в О (R-входом) RS-триггера 7 м информационным входом управляемого цифрового глемен™ та задержки„

Тиристор 3 включен между входными выводами 2 и выходными выводами 10.

Формирующий ключ 11 включен между выходом управляемого цифрового эле-, мента задержки и управляющим выво дом тиристора.

Параллельные информационные входы генератора 3 пачки импульсов и счетчика-делителя 6 являются соотретст венно шиной 12 кода сигнала управле- НИЛ и шиной 13 длительности кода интервала регулирования.

Диаграмма работы импульсного преобразователя представлена на фиг.2 где на диаграмме показано -напряже ние на входных выводах 2, на диаграмме 115

сигнал на выходе формирователя 1 синхроимпульсов, на диаграмме 1б сигнал на выходе схемы 5 совпадения, на диаграмме 17 сигнал на выходе управляемого цифрового элемента 4 задержки, на диаграмме 10 напряжение на выходных выводах 10.

0 5 0 5

о

5

0

4

Гене)атор 3 пач|. и импульсов может бьп I, выполнен по схеме, изображенной на фиГсЗ, и включать в себя автоколе- бaтeJ ьнbiй генератор 19 импульсов, выход которого соединен с первым входом схемы И 20, второй вход которой соединен с прямым выходом RS-триггера 21, а выход со счетным входом счетчика 22, лараллельные входы которого являются шиной 12 кода сигнала управления, а выход соединен с R-входом RS TpHrrepa 21, причем выход схемы И 20 является выходом 23 генератора пачки импульсов, тактовый вход 2k котооого соединен с входом установки 13 1 RS-триггера 21 и тактовым вхо- до(- , счетчика 22.

Счетчик-делитель 6 может быть выполнен по схеме делителя частоты с изне :яемь М коэффициентом eлeния на основе реверсивных с - ет1-1иков, имеющих параллельные входы каждого разряда, суммирующие и вычитающие (счетные) входы и вход разрешения параллельной записи. Схема такого делителя частоты i-ia основе, например, реверсивных счетчиков К155ИЕ6 изображена на „ и включает в себя счетчики 25 и 2б, соединенные последовательно, их параллельные входы являются шиной 13 кода длительности интервала регулирования. Входные выводы 27 и 28 счетчика-делителя 6 присоединены к соответствующим счетным входам счетчика 25, а выходной вывод 29 подключен к выходу элемента И-НЕ 30, входы которого присоединены к выходам счетчика 2б. Между выходными выводами 29 и входами разрешения параллельной записи у счетчиков 25 и 2б включена линия задержки на элементах И-НЕ 31, НЕ 32 и 33, резисторе 3, диоде 35 и конденсаторе Зб, собранная по известной схеме.

Управляемый цифровой элемент k задержки может быть выполнен по схеме, изображенной на фиг„5, и включает в себя схему 37 определения полярности импульса включения, состоящую из счетного триггера 38 и двух логических элементов И 39 и -iO, первые входы которых связаны соответственно с прямым и инверсным выходами триггера 38, счетный вход которого соединен с тактовым входом 1 цифрового элемента А задержки, триггер 42 .полярности включения, выполненный на основе RS-триггера, схему V-5 формирования функции

включения, состоящую из двух логических элементов И А4 и 5 и логического элемента ИЛИ Цб, входы которого соединены с выходами элементов И А4 и 5, а выход - с выходом k7 управляемого цифрового элемента k задержки, схему 8 формирования функции задержки, состоящую из двух логических элементов И kS и 50 и логического эле- мента ИЛИ 51, входы которого соединены с выходами элементов И 49 и 51 , триггер 52 управления задержкой, выполненный на основе RS-триггера, мультиплексор 53 импульсов включения, состоящий из двух логических элементов И 5 и 55, элемента ИЛИ 56, входы которого соединены с выходами элементов И 5 и 55 и сдвиговый регистр 5,7, состоящий из D-триггеров 58 и 59 и логического элемента И 60, первый вход которого соединен с прямым выходом D-триггера 59, которого соединен с прямым выходом В-тригге ра 58, у которого С-вход соединен с информационным входом 61 цифрового элемента 4 задержки, причем выход элемента И 39 соединен с первыми входами элементов И 50 и kk, выход элемента И 40 - с первыми входами эле- ментов И 5 и 9, прямой вход триггера 42 - со вторыми входами элементов И А4 и 49, инверсный выход - с вторыми входами элементов И 45 и 50 , R-. и S-входы триггера 42 соединены с выхо- дами элементов И 44 и 45 соответст- . венно, выход элемента ИЛИ 51 соединен с S-входом триггера 52, выход элемента ИЛИ 5б - с вторыми входами элементов И 39 и 40, первые входы эле-, ментов И 54 и 55 соответственно с инверсными и прямыми выходами триггера 52, вторые входы элементов И 54 и 55 с информационным входом б1 элемента 4 задержки и выходом элемента И.60 соответственно, и кроме того, тактовый вход 41 элемента 4 задержки соединен с С-входами D-триггеров 58

и 59 и вторым входом элемента И 60, а триггера 52 соединен с выхо- дом D-триггера 59 и первым входом элемента И 60.

Функции, выполняемые управляемым цифровым элементом 4 задержки, иллюстрируются временной диаграммой, изображенной на фиг.6.

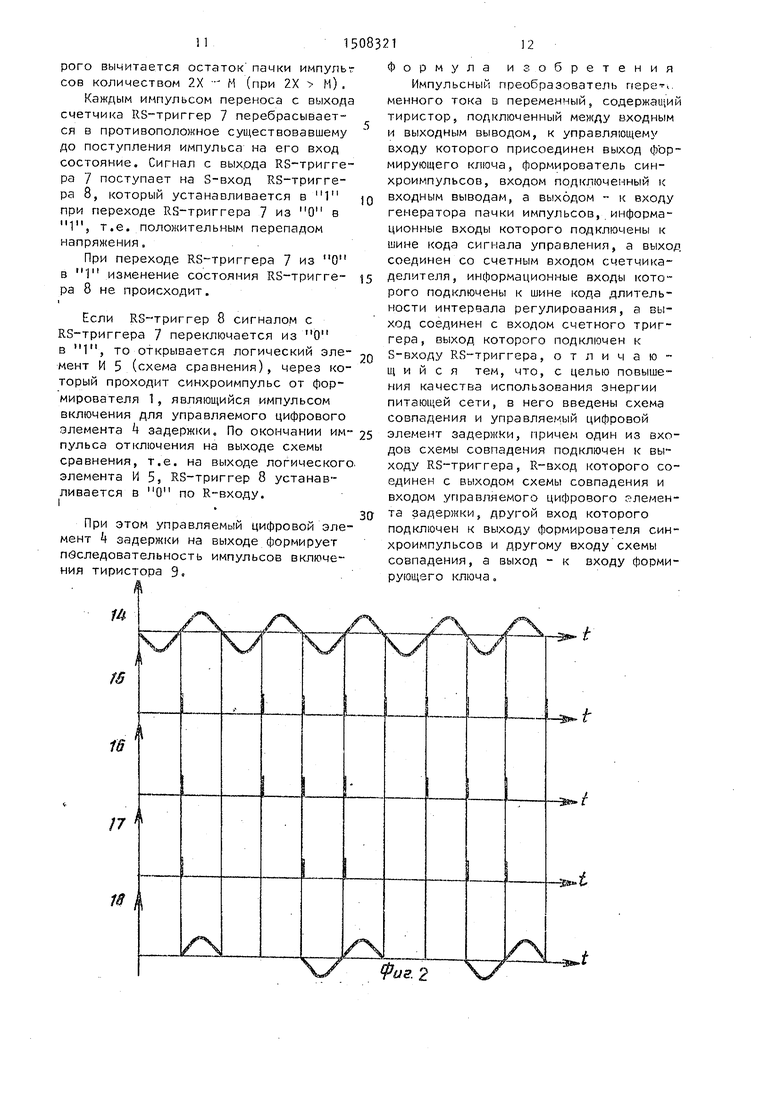

Работа регистра 57 сдвига поясняется диаграммами, изображенными на фиг.7, где на диаграмме б2 показан

сигнал на выходе D-триггера 58, на диаграмме 63 - сигнал на выходе D- триггера 59, на диаграмме 64 - сигна на выходе элемента И 60.

На фиг.8 представлены диаграммы, поясняющие работу схемы 37 определе.п ния полярности импульса включения, где на диаграммах 65 и 66 показаны сигналы на выходах триггера 38, на диаграмме 67 - сигнал на выходе элемента И 39, на диаграмме 68 - сигнал на выходе элемента И 40.

Генератор 3 пачки импульсов работает следующим образом.

На шину 12 генератора пачки импульсов поступают сигналы управления соответствующие требуемому количеству импульсов X.

С приходом на вход 24 каждого тактового импульса S счетчик 22 записывается число X, установленное на шине 12, в результате чего RS-триггер 21 устанавливается в 1 и сигналом со своего прямого выхода открывает схему И 20 по второму входу, при этом импульсы с выхода генератора 19 импульсов через схему И.20 поступают на счетный вход счетчика 22 и одновре-i менно на выход 23 генератора пачки импульсов.

После того, как на счетный вход счетчика 22 поступит X импульсов, на выходе счетчика 22 появится импульс, которым установится в О RS-триггер 21 , при этом сигнал логического О с прямого выхода триггера закроет схему И 20, в результате чего импуль сы на ее выходе и, следовательно, на выходе генератора пачки импульсов прекратятся.

Каждым тактовым импульсом на входе 24 генератора пачки импульсов на его выходе 23 будет формироваться пачка импульсов, число которых равно X,

Счетчик-делитель 6 работает следующим образом. На его параллельные входы подается код М, определяющий коэффициент давления, на счетный (вычитающий) вход 27 - входная частота.

Каждым импульсом с выхода переноса счетчика 25 коэффициент деления, установленный на шинах 13, будет записываться в счетчики 25 и 26, а каждым входным импульсом содержимое будет уменьшаться и при прохождении М импульсов счетчики 25 и 26 обнулятся, при этом появится сигнал на выходе счетчика 25, который с некоторой задержкой поступит на выходной вывод 29 и одновременно, пройдя через элемент задержки (логические элементы , конденсатор Зб, резистор и диод 35) снова запишет коэффициент деления, т.е, код М, в сметчики 25 и 2б и т.д.

В итоге частота импульсов на ЕЫ- ходном выводе 29 счетчика-делителя 6 уме мьшится по сравнению с входной в требуемое количесч во раз

На входную шину 13 счетчика-делителя 6 поступает код числа, равный М и соответствующий относительной дли- тельности интервала регулирования, на счетный вход 27 (t-зычитающий) - импульсы с выхода генератора 3 пачки импульсов, ВЫХОД логического элемента И-НЕ 30, являющийся выходом 29 счет- чика-делителя 6, соединен с S-входом RS-триггера 7.

Для устранения нежелательного явления наличия постоянной составляющей в токе нагрузки последовательность импульсов включения должна иметь вид, изображенный на диаграмме 1б на фиг.б при этом напряжение на нагрузке будет иметь вид, изображенный на диаграмме 18, откуда видно отсутствие постоян- ной составляющей.

Если полярность предполагаемого включения нагрузки .при появлении им пульса включения в начале такта совпадает с полярностью предыдущего вклю- чения, то включение необходимо задер жать на один такт.

Управляемый цифровой элемент 4 за™ держки служит для обеспечения тактового режима работы,и работает следу- ющим образом.

Регистр сдвига 57. состоящий из D-триггеров 58 и 59 и логического элемента И 60, осуществляет сдвиг последовательности импульсов включе- ния, поступающих на информационный вход 61 управляемого цифрового элемента А задержки, на один, такт, равный , где Tj, - полупериод напря :кения сети, т.е последовательность импульсов включения на выходе логического элемента И 60, являющегося выходом регистра сдвига, будет сдвинута по отношению ic последовательности импульсов на входе б1 на время, равное периоду тактовой частоты, поступающей с выхода формирователя 1 синхроимпульсов на вход kl управляемого цифрового элемента k задержки.

а с него на сдвигающие С-входы D- триггеров 58 и 59 и на второй вход элемента И 60. Работа регистра 57 сдвига иллюстрируется диаграммами, изображенными фиг.7.

Импульсы включения с информационного входа 61 управляемого элемента задержки и задержанные импульсы включения поступают на вторые входы логических элементов И 5 и 55, входящих в состав м.ультиплексора 53 импульса включения, на выход которого через логический элемент ИЛИ 5б поступают прямые или задержанные,импульсы включения с выходов логических элементов И 5 или 55, один из которых открыт сигналом логической 1 с инверсного или прямого выходов триггера 52 управления задержкой. В исходном состоянии (например, при включении питания) триггер 52 управления задер жкой установлен в состояние О, логический элемента И 5 t открыт по первому входу и пос.педова- тельность и.мпульсов включения через элемент И 5 и элемент ИЛИ 56 поступает на входы логических элементов И 39 и АО, входящих в схему 37 определения полярности импульса включения, в которую входит (е счетный триггер 38, Т-вход (счетный вход) которого является тактовым входом 1 управляе.мого цифрового элемента задержки. Схема 37 функционирует так (фиг.8), что при поступлении на вход +1 и, следовательно, на Т-вход триггера 38 импульсов, соответствующих моменту перехода через ноль питаюьцег напряжения, этим импульсом триггер перебрасывается 5 причем с приходом импульса с выхода формирователя 1, соответствующего началу положительного полупериода питающего сетевого напряжения, триггер 38 устанавливается в 1-, а с приходом импульса, соответствующего отрицательному полупериоду, триггер ЗВ устанавливается в О.

Таким образом, схема определения полярности импульса включения, имеет возможность определять полярность, в которой должна подключиться нагрузка с приходом каждого импульса включени с выхода логического элемента ИЛИ 56 мультиплексора 53 импульса включения Если импульс включения должен включить нагрузку в положительный полупериод, то этот импульс появится на

выходе логического элемента И 39, открытого по первому входу сигналом с прямого выхода триггера 38. Если же импульс включения совпадает с началом отрицательного полупериода питающего напряжения, то импульс включения появится на выходе логического элемента И 0, открытого по первому входу сигналом с инверсного выхода триггера 38.

Таким образом, происходит селекция импульсов включения на положительные

и отрицательные. )

Триггер ч2 полярности включения

выполняет функцию запоминания яоляр- ности предыдущего подключения нагрузки, т.е. если предыдущее подключение нагрузки произошло положйтельнь1м полупериодом, то триггер А2 предыдущим импульсом включения установится в О по R-входу импульсом с выхода логического элемента И 4, если же предыдущее подключение нагрузки произошло в отрицательный полупериод, то триггер 2 полярности включения установится в 1 по S-входу импульсом с выхода логического элемента И 5,. Работу схемы 43 формирования двоичной функции FQ включения и схемы 48 фор-- мирования функции Fj задержки можно описать, используя выражения алгебры логики, составив следующую таблицу

соответствия.

Uj4.. Ug-, Q и С)г логические переменные (сигналы) соответственно на выходах логических элементов НЕ 33 и И,(О и на прямом и инверсном выходах триггера 42, а Fц и ЕЗ - значения логических функций, определяющих либо включение нагрузки на текущем такте и соблюдении условия разнополярности последующих включений (F 1), либо включение триггера 52 управления задержки (установки его в 1), при несоблюдении этого условия (F 1) логические элементы И 44 и 45 и ИЛИ 46. реализуют единичные (истинные) значения функции включения, выраженные

0

5

0

5

5

0

5 д

строками 1 и 3 таблицы соответствия, равные

FB (Ug Q,,v (и,.) Q, .

Логические элементы И 49, 50 и 51 реализуют единичные (истинные) значения функции задержки, выражаемые строками 2 и 4 таблицы соответствия, равные

РЗ ( Q4jV(UgO Q 2При Fg 1 происходит включение тиристора и нагрузки с условием соблюдения разнополярности последующих включений, а триггер 42 при этом переключается в противоположное состояние, т„е. если после предыдущего положительного включения он находится в О, то текущий отрицательный импульс Ug, включения сформирует Fj5 1, включится нагрузка в отрицательной полярности, а триггер 42 переключится в 1 и наоборот, текущий положительный импульс Ugt после последующего положительного сформирует Fg О, а Fj 1, включения не произойдет, положительный Ug+ задержится на один такт и преобразуется в отрицательный , включив нагрузку в наружной (отрицательной) полярности, переключив при этом триггер 42 в О.

Импульсный преобразователь работает следующим образом.

Формирователь 1 генерирует синхроимпульсы в момент перехода напряжения сети через ноль. По каждому синхроимпульсу генератор 3 пачки импульсов выдаст на вход счетчика число импульсов, равное X, где X - величина сигнала управления, установленная на шине 12, и сбрасывает его в ноль.

Количество импульсов, выдаваемое генератором 3 пачки импульсов, равное 2Х, определяется тем, что код,-соответствующий сигналу X, подается на параллельные управляющие входы гене- ратора 3 пачки импульсов со сдвигом на один разряд в сторону старших раз- рядов.

Этим импульсы поступают на вход счетчика-делителя 6, коэффициент деления которого задается кодом М значения длительности интервала регулирования на шине 13 и в нем осуществляется операция М - 2Х. При 2Х М происходит обнуление счетчика- делителя 6, в результате чего на его выходе формируется импульс переноса, которым снова в счетчик-делитель 6 записывается число (код) М, из которого вычитается остаток памки импулы сов количеством 2Х М (при 2Х М) ,

Каждым импульсом переноса с выхода счетчика RS-триггер 7 перебрасывается в противоположное существовавшему до поступления импульса на его вход состояние. Сигнал с выхрда КЗ-триггера 7 поступает на S-вход RS-тригге- ра 8, который устанавливается в 1 при переходе RS-триггера 7 из О в 1, т.е. положительным перепадом напряжения.

При переходе КЗ-триггера 7 из О в 1 изменение состояния RS-триггера 8 не происходит.

Если К8 триггер 8 сигналом с RS-триггера 7 переключается из О в 1, то открывается логический элемент И 5 (схема сравнения), через который проходит синхроимпульс от формирователя 1, являющийся импульсом включения для управляемого цифрового

формула изобретен Импульсный преобразователь nep менного тока в переменный, содерж тиристор, подключенный между вход и выходным выводом, к управляющем входу которого присоединен выход мирующего ключа, формирователь си хроимпульсов, входом подключенный

JQ входным выводам, а выходом - к вх генератора пачки импульсов, инфо ционные входы которого подключен шине кода сигнала управления, а соединен со счетным входом счетч

5 делителя, информационные входы к рого подключены к шине кода длит ности интервала регулирования, а ход соединен с входом счетного т гера, выход которого подключен к

2Q S-входу КЗ-триггера, отлича щийся тем, что, с целью пов ния качества использования энерг питающей сети, в него введены сх совпадения и управляемый цифрово

элемента k задержки. По окончании им- 25 элемент задержки, причем один из

дов схемы совпадения подключен к ходу RS-триггера, R-вход которог единен с выходом схемы совпадени входом управляемого цифрового эл та задержки, другой вход которог подключен к выходу формирователя хроимпульсов и другому входу схе совпадения, а выход - к входу ф рующего ключа.

пульса отключения на выходе схемы сравнения, т.е. на выходе логического, элемента И 5, RS-триггер 8 устанавливается в О по К-входу.

При этом управляемый цифровой элемент задержки на выходе формирует последовательность импульсов включения тиристора 9.

У Физ. 2

формула изобретения Импульсный преобразователь nepe-i-i. менного тока в переменный, содержащий тиристор, подключенный между входным и выходным выводом, к управляющему входу которого присоединен выход формирующего ключа, формирователь синхроимпульсов, входом подключенный к

входным выводам, а выходом - к входу генератора пачки импульсов, информационные входы которого подключены к шине кода сигнала управления, а выход соединен со счетным входом счетчикаделителя, информационные входы которого подключены к шине кода длительности интервала регулирования, а выход соединен с входом счетного триггера, выход которого подключен к

S-входу КЗ-триггера, отличающийся тем, что, с целью повышения качества использования энергии питающей сети, в него введены схема совпадения и управляемый цифровой

элемент задержки, причем один из

входов схемы совпадения подключен к выходу RS-триггера, R-вход которого соединен с выходом схемы совпадения и входом управляемого цифрового элемента задержки, другой вход которого подключен к выходу формирователя синхроимпульсов и другому входу схемы совпадения, а выход - к входу формирующего ключа.

111

1

-p35

-I.-

fV f

20

Г

3

фие.З

(риг 5

/А

г

/л

7

М S

W

/л

ЛУ

Фаг в

TojZ фаг.7

f4 /5

5 Т

.

ffff w / ; A

.8

-

Авторы

Даты

1989-09-15—Публикация

1988-01-28—Подача