Область техники, к которой относится изобретение

Настоящее изобретение относится к полупроводниковому устройству формирования изображения, устройству формирования изображения и способу управления полупроводниковым устройством формирования изображения. Более конкретно, настоящее изобретение относится к технологии управления пикселем, пригодной для полупроводниковых устройств, таких как полупроводниковые устройства формирования изображения, для детектирования распределения физической величины, и другого электронного оборудования, которое включает в себя размещение множества единичных пикселей, чувствительных к подаваемым извне электромагнитным волнам, таким как свет и излучение, и из которых распределение физической величины, преобразованное в электрический сигнал компонентами модуля, может быть считано в форме электрического сигнала, используя произвольный выбор посредством управления выборкой по адресу.

Уровень техники

Полупроводниковые устройства, предназначенные для детектирования распределения физической величины, нашли широкое применение в различных областях. Такие устройства имеют множество единичных компонентов (например, пикселей), чувствительных к подаваемым извне электромагнитным волнам, таким как свет и излучение, расположенных линейно или в форме матрицы.

В области видеооборудования, например, используются полупроводниковые устройства формирования изображения типа ПЗС (прибор с зарядовой связью) или МОП (металло-оксидный полупроводник) и КМОП (комплементарный металло-оксидный полупроводник). Эти устройства разработаны для детектирования света (например, электромагнитных волн) помимо других физических величин. Такие устройства позволяют считывать из них распределение физической величины, преобразованное в электрический сигнал единичными компонентами (пикселями в полупроводниковом устройстве формирования изображения), в форме электрического сигнала.

Некоторые полупроводниковые устройства формирования изображения представляют собой усилительные устройства. Эти устройства включают в себя, в блоке генерирования сигнала пикселя, пиксели, выполненные как полупроводниковые элементы формирования изображения (APS: датчики с активными пикселями, также называемые усиливающими ячейками), каждый из которых имеет усилительный управляющий транзистор. Блок генерирования сигнала пикселя генерирует сигнал пикселя, пропорциональный заряду сигнала, генерируемого блоком генерирования заряда. Например, многие из полупроводниковых устройств формирования изображения типа КНОП выполнены таким образом.

Для считывания сигнала пикселя с выводом его наружу из такого усилительного полупроводникового устройства формирования изображения, блоком пикселя, имеющим компоновку из множества единичных пикселей, управляют по адресу таким образом, что сигнал из модульного пикселя может быть произвольно выбран и считан. Таким образом, усилительное полупроводниковое устройство формирования изображения представляет собой пример полупроводникового устройства формирования изображения, управляемого по адресу.

Единичный пиксель включает в себя блок генерирования заряда и блок вывода сигнала. Блок генерирования заряда генерирует сигнальный заряд. Блок вывода сигнала имеет транзистор, выполненный с возможностью генерирования и вывода целевого сигнала, пропорционального сигнальному заряду, генерируемому блоком генерирования заряда. Например, блок генерирования заряда имеет фотодиод, который выполняет фотоэлектрическое преобразование. Блок вывода сигнала имеет транзистор выбора считывания, усилительный транзистор, транзистор сброса и транзистор выбора. Транзистор выбора считывания считывает сигнальный заряд, генерируемый фотодиодом. Усилительный транзистор преобразует считанный сигнальный заряд в сигнал пикселя. Транзистор сброса выполняет сброс сигнального заряда. Транзистор выбора выбирает пиксель для считывания.

Здесь полупроводниковое устройство формирования изображения типа МОП имеет проблему темнового тока, связанную с явлением утечки, в соответствии с которым происходит утечка сигнального заряда, генерируемого модулем генерирования заряда, на сторону выхода сигнала. Если сигнальный заряд накапливать, в частности, в течение длительного времени, измеряемого часами, компонент темнового тока увеличивается с накоплением, так что на него приходится большая доля сигнального заряда. Компонент темнового тока невозможно отделить от сигнального заряда во время считывания. Его вариации приводят к шумам, которые значительно ухудшают качество изображения. Например, колебания компонента темнового тока от одного пикселя к другому приводят к шумам с фиксированной структурой, которые вызывают появление белых точек на изображении. В результате, изображение выглядит, как если бы оно было снято через матовое стекло. Кроме того, вариации компонента темнового тока с течением времени приводят к возникновению случайных шумов. Поэтому в случае полупроводниковых устройств формирования изображения типа МОП существует повод для беспокойства, связанный с необходимостью уменьшения компонента темнового тока.

В качестве меры противодействия этому, например, в повторно опубликованной заявке на патент № WO 2003/085964 предложена компоновка для уменьшения темнового тока. В этой компоновке переводят напряжение, приложенное к затвору (ниже называется передаточным затвором) транзистора выбора считывания до потенциала земли или меньше, то есть прикладывают отрицательное напряжение к затвору транзистора так, что происходит накопление дырок в канале передаточного затвора, что способствует уменьшению темнового тока.

Однако, если отрицательное напряжение использовать, как описано выше, чрезмерное уменьшение отрицательного напряжение на затворе транзистора, то есть отрицательное увеличение напряжения на затворе транзистора, приводит к дополнительной нагрузке на пиксель и к оксидной пленке на затворе в его цепи управления. Кроме того, ухудшаются характеристики транзистора, например, из-за тепловых носителей, которые существенно влияют на надежность (срок службы продукта). С другой стороны, увеличение отрицательного напряжения (отрицательное уменьшение напряжение) с учетом повышения надежности приводит к недостаточному предотвращению утечки, усилению шумов, связанных с темновым током в случае длительного, исчисляемого часами, времени накопления. Таким образом, в настоящее время, невозможно в достаточной степени одновременно удовлетворить требования к надежности и уменьшению явления утечки. Поэтому трудно оптимизировать отрицательное напряжение на постоянном уровне.

Возможные решения по использованию постоянного уровня отрицательного напряжения могли бы состоять в увеличении толщины оксидной пленки на затворе транзисторов, к которым прикладывают отрицательное напряжение для улучшения надежности (долговечности). Однако это приводит к увеличенному количеству этапов производства, в результате чего увеличиваются затраты.

Настоящее изобретение было выполнено с учетом описанных выше задач, и цель настоящего изобретения состоит в уменьшении темнового тока, вызванного утечкой, при одновременном обеспечении надежности элемента, используя простую компоновку.

Сущность изобретения

В варианте осуществления настоящего изобретения при запуске единичного пикселя из сторон нижнего и высокого уровня сигналов управления, выполненных с возможностью импульсного запуска каждого из транзисторов модуля выведения сигнала, регулирует уровень напряжения подлежащей регулированию стороны, который пропорционален сигнальному заряду или полярности транзистора так, что чем больше время накопления сигнального заряда, тем выше уровень напряжения. Если не накоплен никакой сигнальный заряд, время накопления равно нулю. Поэтому уровень напряжения на подлежащей регулированию стороне регулируют до низкого напряжения.

Что касается темнового тока, вызванного явлением утечки, при котором происходит утечка сигнального заряда, генерируемого модулем генерирования заряда, на сторону вывода сигнала, то, чем больше время накопления заряда, тем больше темновой ток. В результате также возникает проблема шумов. С другой стороны, такой темновой ток, вызванный явлением утечки, уменьшается при увеличении уровня напряжения на подлежащей регулированию стороне.

В варианте осуществления настоящего изобретения, поэтому, уровень напряжения на подлежащей регулированию стороне регулируют так, что чем больше время накопления сигнального заряда, тем выше уровень напряжения. На подлежащей регулированию стороне устанавливают высокий уровень напряжения только при длительном времени накопления заряда, что имеет место, когда темновой ток, вызванный явлением утечки, становится проблемой. На подлежащей регулированию стороне устанавливают низкий уровень напряжения, когда время накопления заряда небольшое или когда не снимают изображение, и в этом случае темновой ток, связанный с явлением утечки, не становится проблемой.

Поскольку на подлежащей регулированию стороне устанавливают уровень высокого напряжения только при длительном времени накопления заряда, что имеет место, когда темновой ток, связанный с явлением утечки, становится проблемой, становится возможным подавлять нагрузку на пиксели и на оксидную пленку затвора их цепей управления и снижать ухудшение характеристик транзистора, даже если подавляется темновой ток.

Полупроводниковое устройство формирования изображения, в котором применяется описанная выше компоновка, может быть выполнено в форме одной микросхемы или модуля, имеющего блок матрицы пикселей (блок формирования изображения) и блок обработки сигналов или оптическую систему, упакованные вместе. Кроме того, описанная выше компоновка также применима не только для полупроводникового устройства формирования изображения, но также и для устройства формирования изображения. В этом случае устройство формирования изображения обеспечивает те же предпочтительные результаты, что и полупроводниковое устройство формирования изображения. Под устройством формирования изображения понимается, например, камера (или система камеры) или портативное устройство, имеющее функцию формирования изображения. С другой стороны, термин "формирование изображения" включает в себя не только съемку изображения во время нормального фотографирования с помощью камеры, но также, в более широком смысле, детектирование отпечатков пальцев и т.п.

В варианте осуществления настоящего изобретения уровень напряжения на подлежащей регулированию стороне регулируют так, что чем дольше время накопления сигнального заряда, тем выше уровень напряжения. Это позволяет оптимально устанавливать уровень напряжения на подлежащей регулированию стороне таким образом, чтобы подавлять темновой ток, связанный с явлением утечки, при одновременном удовлетворении требования надежности элемента. Становится возможным достичь совместимости между подавлением темнового тока и обеспечением надежности элемента. При этом требуется простая компоновка, выполненная с возможностью регулирования уровня напряжения сигнала управления в соответствии с временем накопления заряда. Такая компоновка может быть воплощена без увеличения толщины оксидной пленки затвора или иного отрицательного влияния на этапы изготовления транзистора, устраняя, таким образом, потребность в увеличении количества производственных этапов.

Краткое описание чертежей

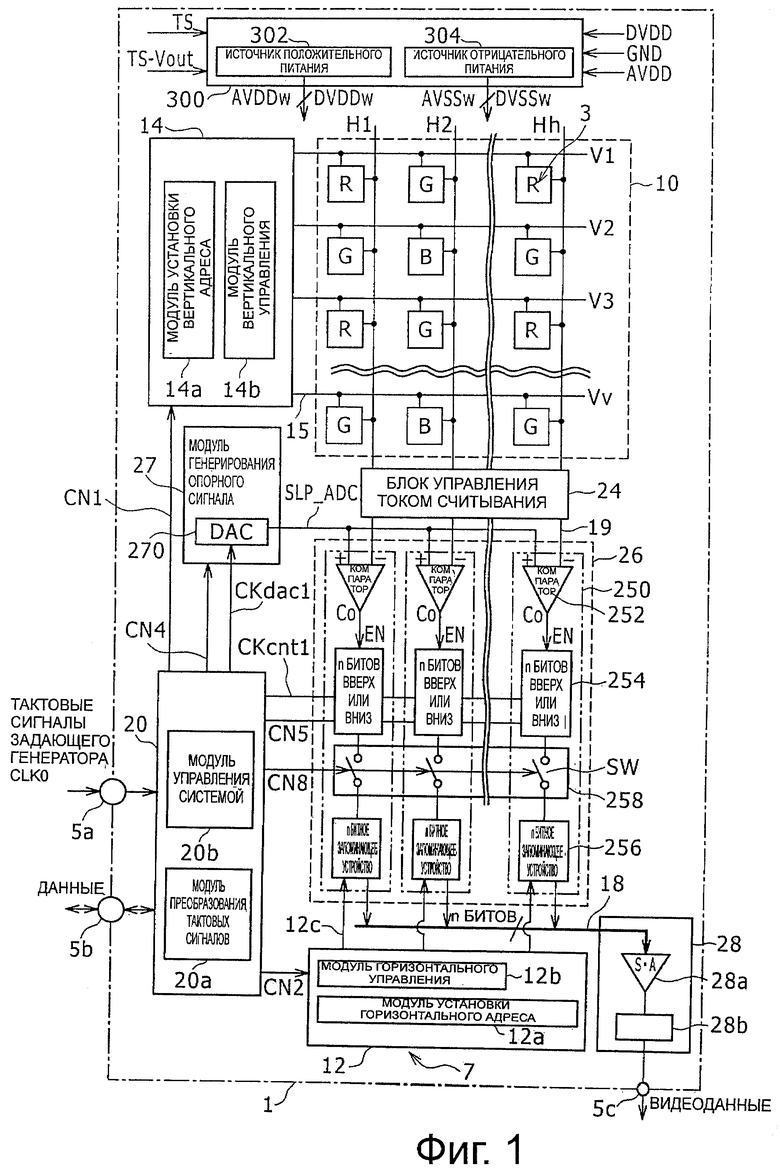

На фиг.1 представлена схема основной конфигурации полупроводникового устройства формирования изображения.

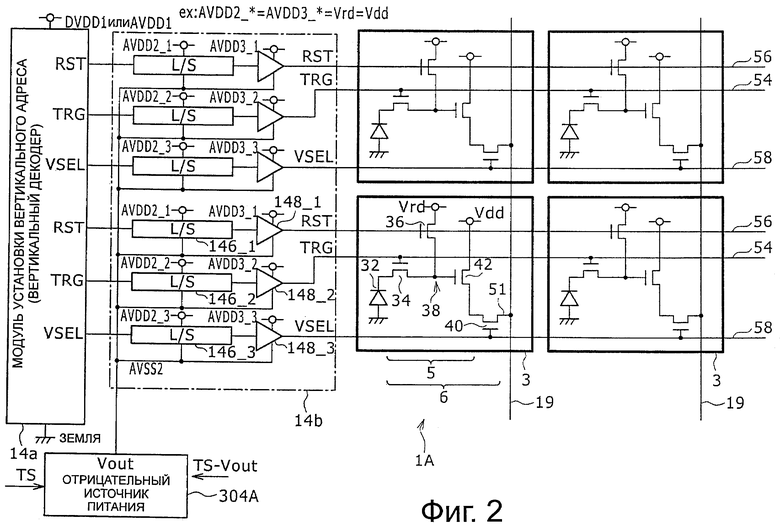

На фиг.2 показана схема, иллюстрирующая полупроводниковое устройство формирования изображения в соответствии с первым вариантом осуществления с фокусом на интерфейс между модулем вертикальной развертки и модулем матрицы пикселей.

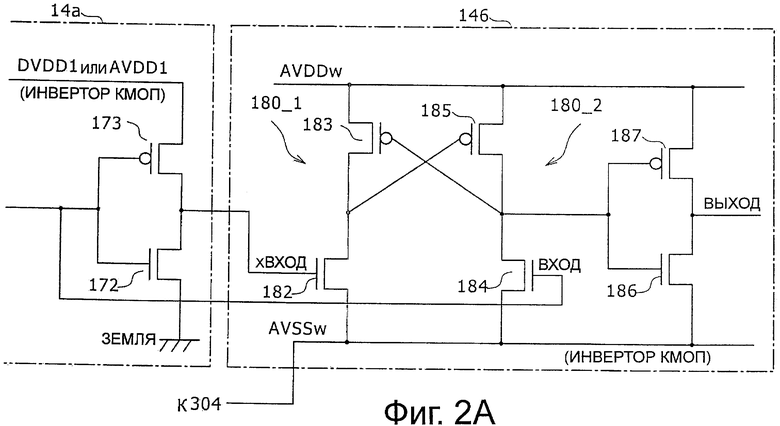

На фиг.2А показана схема, описывающая пример цепи участка интерфейса между модулем установки вертикального адреса и модулем вертикального управления вертикальной разверткой.

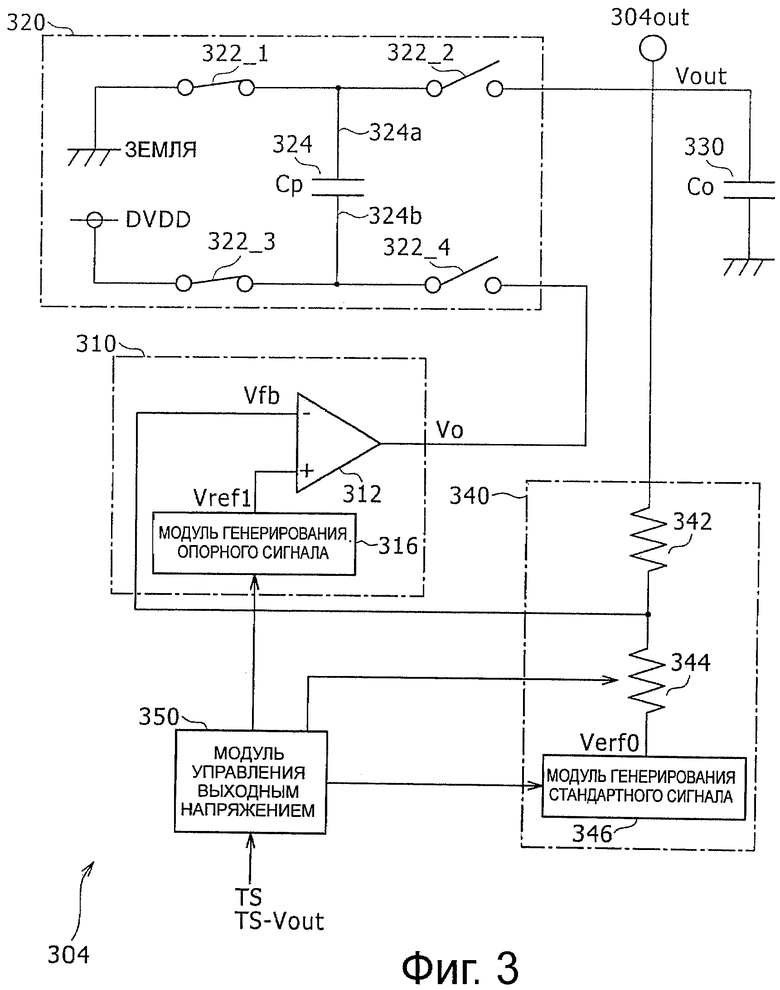

На фиг.3 показана схема, иллюстрирующая пример конфигурации отрицательного источника питания.

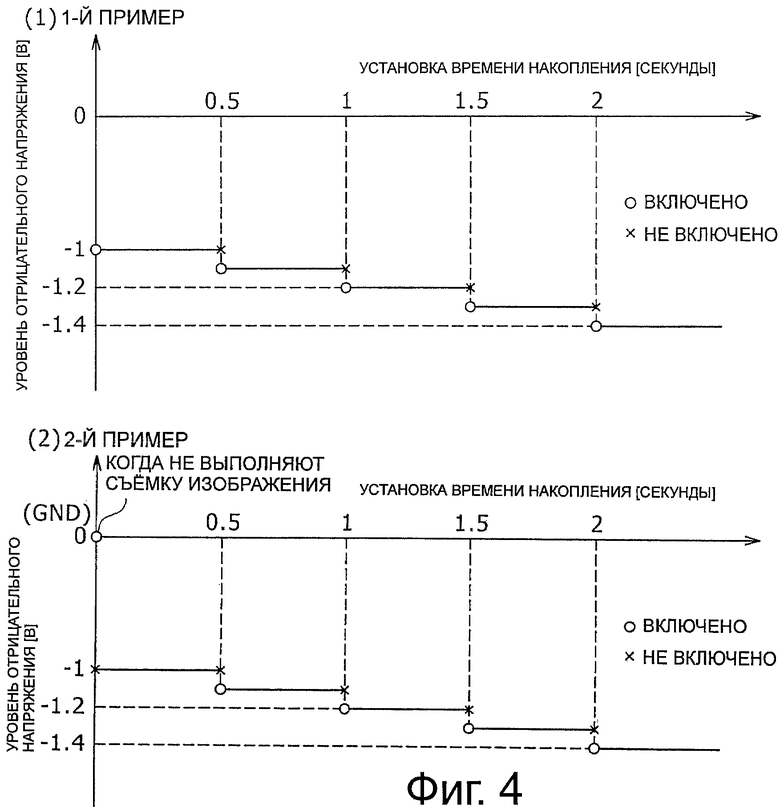

На фиг.4 показаны схемы, описывающие примеры регулирования отрицательного выходного напряжения Vout (пропорционального цифровому отрицательному напряжению DVSSw), выводимого из отрицательного источника питания.

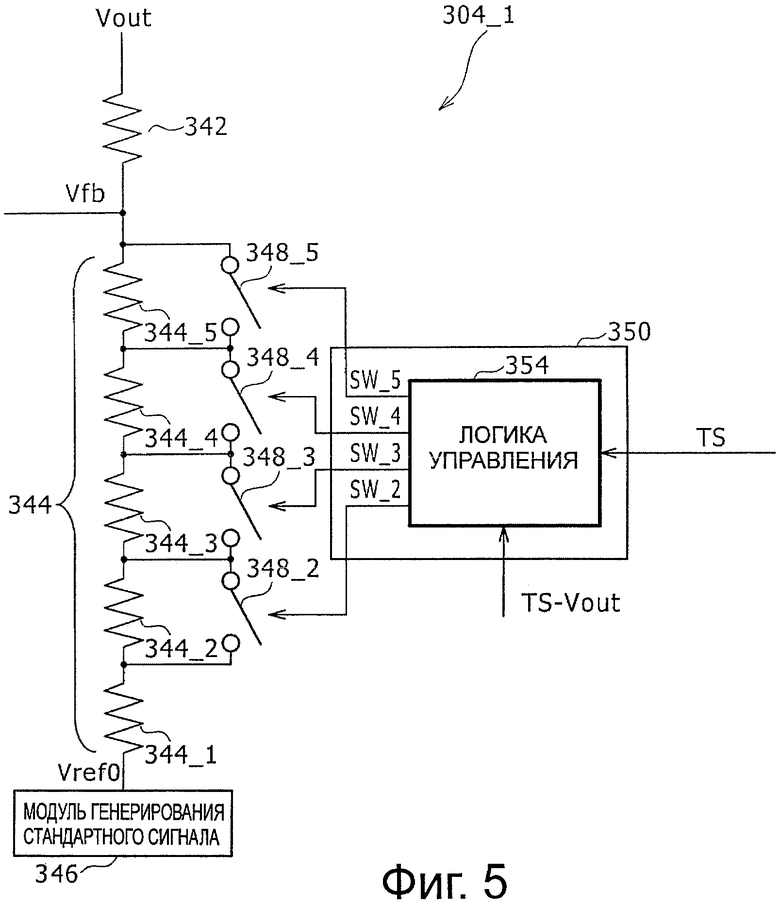

На фиг.5 показана схема, иллюстрирующая конфигурацию цепи в соответствии с первым примером, выполненным с возможностью обеспечения возможности регулирования отрицательного напряжения.

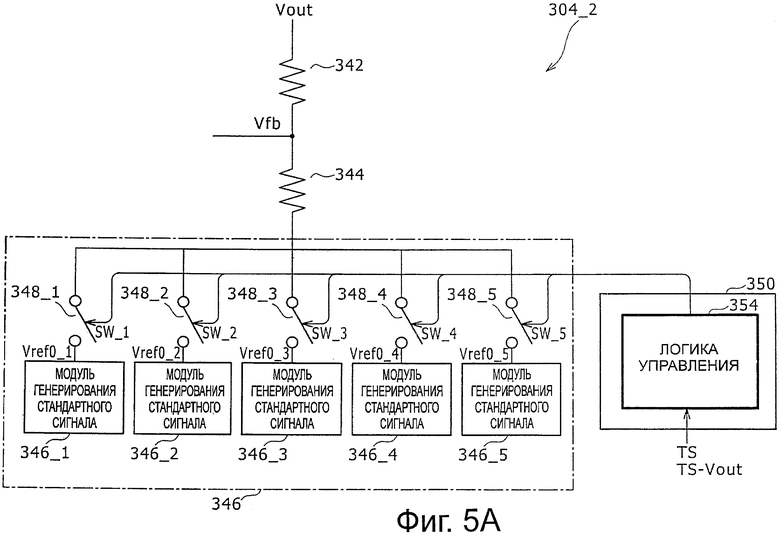

На фиг.5А показана схема, иллюстрирующая конфигурацию цепи в соответствии со вторым примером, выполненным с возможностью обеспечения возможности регулирования отрицательного напряжения.

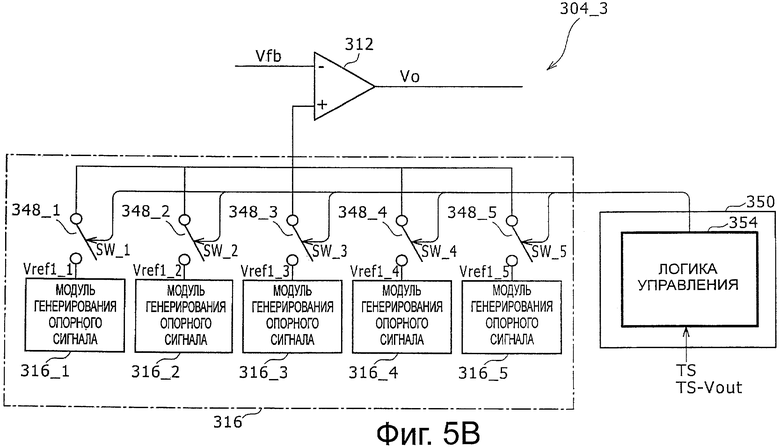

На фиг.5В показана схема, иллюстрирующая конфигурацию цепи в соответствии с третьим примером, выполненным с возможностью обеспечения возможности регулирования отрицательного напряжения.

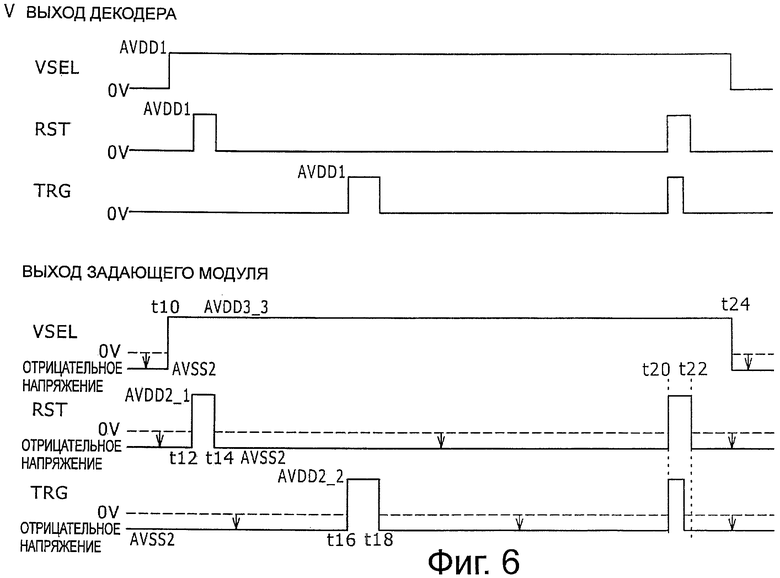

На фиг.6 показана временная диаграмма, иллюстрирующая пример синхронизации операций импульсов управления, выполненных с возможностью управления единичным пикселем.

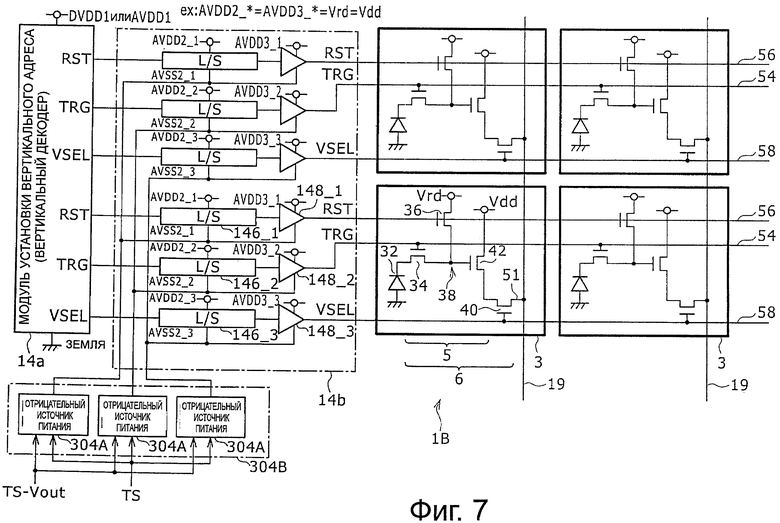

На фиг.7 показана схема, иллюстрирующая полупроводниковое устройство формирования изображения в соответствии со вторым вариантом осуществления, с фокусом на интерфейс между модулем вертикальной развертки и модулем матрицы пикселей.

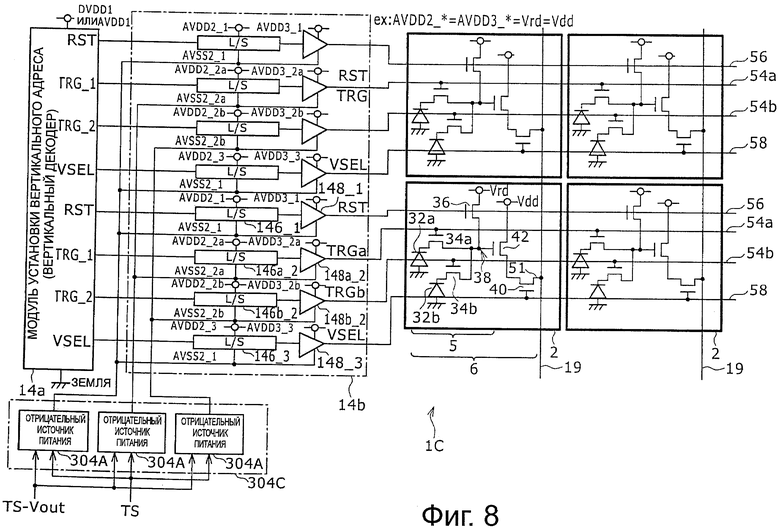

На фиг.8 показана схема, иллюстрирующая полупроводниковое устройство формирования изображения в соответствии с третьим вариантом осуществления, с фокусом на интерфейс между модулем вертикальной развертки и модулем матрицы пикселей.

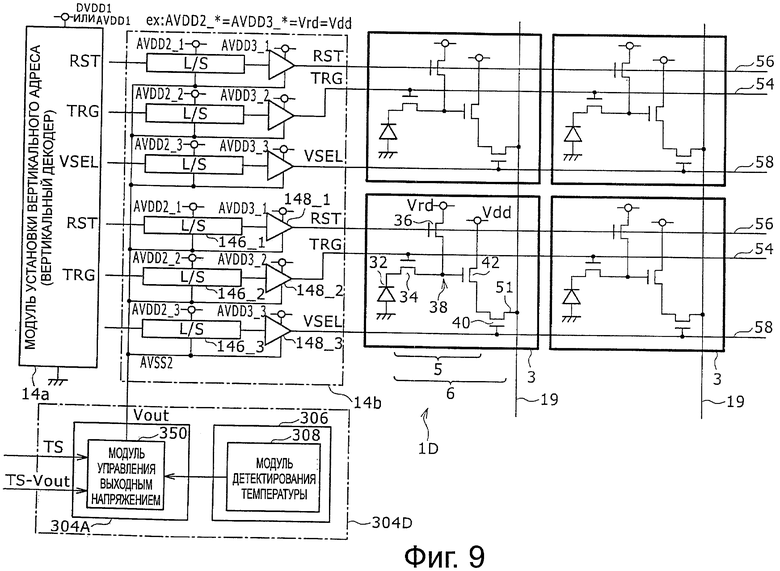

На фиг.9 показана схема, иллюстрирующая полупроводниковое устройство формирования изображения в соответствии с четвертым вариантом осуществления, с фокусом на интерфейс между модулем вертикальной развертки и модулем матрицы пикселей.

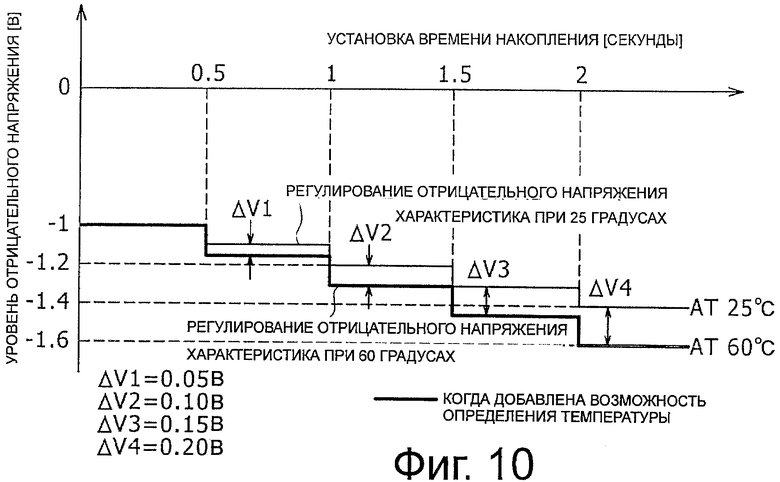

На фиг.10 показаны схемы, описывающие примеры регулирования отрицательного выходного напряжения Vout (пропорционального цифровому отрицательному напряжению DVSSw), выводимому из отрицательного источника питания в соответствии с четвертым вариантом осуществления.

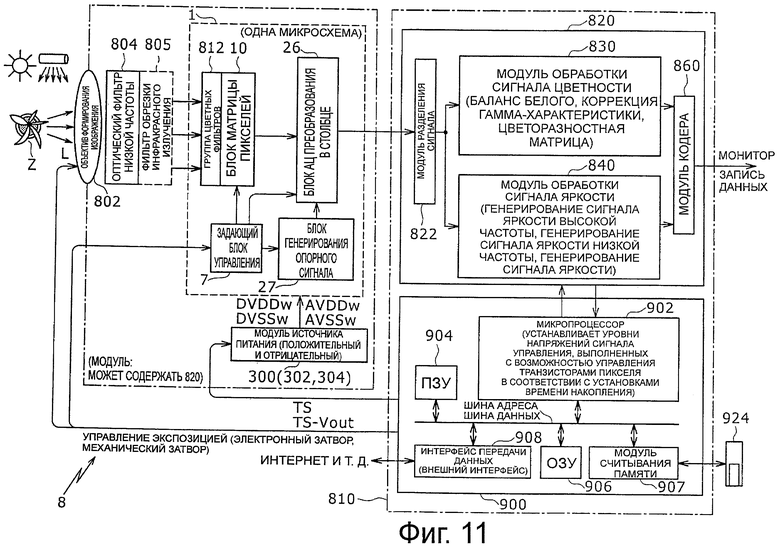

На фиг.11 показана схема конфигурации устройства формирования изображения (пятый вариант осуществления).

Подробное описание изобретения

Предпочтительные варианты осуществления настоящего изобретения будут описаны ниже со ссылкой на приложенные чертежи. В случае когда требуется сделать различие между функциональными элементами в разных вариантах осуществления, такие элементы будут обозначены номерами ссылочных позиций, такими как заглавные буквы А, В, С и так далее. В случае когда не требуется представить какое-либо определенное различие между ними для описания, такие номера ссылочной позиции будут опущены. То же относится к чертежам.

Следует отметить, что ниже будет описан случай, в котором полупроводниковое устройство формирования изображения типа КНОП, как пример полупроводникового устройства формирования изображения с адресом X-Y, используется в качестве устройства. Кроме того, если только не будет указано другое, следующее описание приведено на основе предположения, что все единичные пиксели полупроводникового устройства формирования изображения типа КНОП включают в себя транзисторы n-МОП (n-канальный МОП) и что сигнальные заряды являются отрицательными (электроны). Однако это представляет собой просто пример, и целевые устройства не ограничиваются полупроводниковыми устройствами формирования изображения типа МОП. Модули пикселя могут включать в себя транзисторы p-МОП (p-канальные МОП). Сигнальные заряды могут быть положительными (дырки). Все варианты осуществления, описанные ниже, в равной степени применимы для всех полупроводниковых устройств, предназначенных для детектирования распределения физической величины и другого электронного оборудования, которое включает в себя линейную или матричную компоновку множества модулей пикселей, чувствительных к подаваемым извне электромагнитным волнам, таким как свет и излучение, и из которых может быть считано распределение физической величины, преобразованной в электрический сигнал модульными компонентами, в форме электрического сигнала с произвольным выбором, с использованием управления адресом.

Полупроводниковое устройство формирования изображения: основная конфигурация

На фиг.1 показана схема основной конфигурации полупроводникового устройства формирования изображения типа КНОП (датчик изображения КНОП), которое представляет собой вариант осуществления полупроводникового устройства формирования изображения в соответствии с настоящим изобретением.

Полупроводниковое устройство 1 формирования изображения имеет блок 10 матрицы пикселей, который включает в себя множество единичных пикселей 3, расположенных двумерно в форме матрицы. Устройство 1 может содержать блок 10 матрицы пикселей, выполненный с возможностью формирования цветного изображения, используя, например, фильтр разделения цветов, имеющий цветные фильтры R, G и В, расположенные в виде шаблона Байера.

Хотя на фиг.1 некоторые строки и столбцы исключены для упрощения, от нескольких десятков до тысяч единичных пикселей 3 на практике предусмотрены в каждой из строк и столбцов. Как описано ниже, каждый из модульных пикселей 3 имеет, например, в дополнение к фотодиоду, используемому в качестве элемента приема света (блок генерирования заряда), который представляет собой пример блока детектирования, встроенный в пиксель усилитель, который включает в себя от трех до четырех транзисторов, с целью передачи, сброса и усиления заряда. Единичные пиксели 3 выводят напряжение Vx сигнала пикселя через вертикальную линию 19 сигнала по столбцам. Напряжение Vx сигнала пикселя содержит уровень Srst сброса (компонент Р-фазы) и уровень Ssig сигнала (компонент D-фазы).

Полупроводниковое устройство 1 формирования изображения дополнительно имеет блок 26 аналого-цифрового преобразования в столбце. Блок 26 имеет блок 250 АЦ преобразования, расположенный параллельно столбцам. Блоки 250 АЦ преобразования выполняют обработку CDS (коррелированнную двойную выборку) и цифровое преобразование. Термин "параллельный столбцам" относится к тому факту, что множество функциональных блоков обработки CDS, блоков функции цифрового преобразования (блоков АЦ преобразования) и других блоков предусмотрено параллельно каждой из вертикальных линий 19 сигнала (пример линий сигнала столбца) в вертикальных столбцах. Такая схема считывания называется схемой считывания по столбцам.

Полупроводниковое устройство 1 формирования изображения также дополнительно включает в себя блок 7 управления запуском, блок 24 управления током считывания, блок 27 генерирования опорного сигнала и выходной блок 28. Блок 24 управления током считывания подает рабочий ток (ток считывания) для считывания сигналов пикселей в единичные пиксели 3. Блок 27 генерирования опорного сигнала подает опорный сигнал SLP_ADC для АЦ преобразования в блок 26 АЦ преобразования в столбце.

Блок 7 управления приводом включает в себя блок 12 горизонтальной развертки (схему сканирования по столбцам), блок 14 вертикальной развертки (схему сканирования по строкам) и блок 20 управления передачей данных/синхронизацией, который обеспечивает функции схемы управления для последовательного считывания сигналов из блока 10 матрицы пикселей.

Блок 12 горизонтального сканирования имеет модуль 12а установки горизонтального адреса, модуль 12b управления горизонтальной разверткой и другие блоки. Модуль 12а установки горизонтального адреса управляет адресами в столбцах и сканированием по столбцам. Блок 14 вертикальной развертки имеет модуль 14а установки вертикального адреса, модуль 14b управления вертикальной разверткой и другие блоки. Модуль 14а установки вертикального адреса управляет адресами в строке и сканированием по строкам. Модули 12 и 14 горизонтальной и вертикальной развертки начинают свой выбор строк и столбцов (развертку) в ответ на сигналы CN1 и CN2 управления, подаваемые из блока 20 управления передачей данных/синхронизацией.

Блок 20 включает в себя функциональный блок генератора синхронизации (пример устройства управления адресом считывания). Этот функциональный блок передает тактовый сигнал, который является синхронным с сигналом главного генератора тактовых импульсов CLK0, подаваемым через разъем 5а в различные блоки (такие как блок 12 горизонтальной развертки, блок 14 вертикальной развертки и блок 26 АЦ преобразования в столбцах) устройства. Тот же блок 20, кроме того, включает в себя функциональный блок интерфейса передачи данных. Этот функциональный блок принимает сигнал главного генератора тактовых импульсов CLK0 из внешнего основного блока управления через разъем 5а. Тот же функциональный блок дополнительно принимает данные, предназначенные для указания, например, используемого режима работы, из внешнего основного блока управления через разъем 5b. Такой функциональный блок также выводит во внешний основной блок управления информацию, содержащую данные о полупроводниковом устройстве 1 формирования изображения.

Например, блок 20 управления передачей данных/синхронизации имеет модуль 20а преобразования тактовых импульсов и модуль 20b управления системой, и другие модули. Модуль 20а преобразования тактовых импульсов имеет функцию преобразования тактовых импульсов, выполненную с возможностью генерирования внутренней тактовых импульсов. Модуль 20b управления системой управляет не только функцией передачи данных, но также и различными блоками. Модуль 20а преобразования тактовых импульсов содержит умножитель частоты, выполненный с возможностью генерирования импульсов с более высокой частотой, чем тактовая частота главного генератора тактовых импульсов CLK0, подаваемых через разъем 5а, на основе этой тактовой частоты генерируя внутренние тактовые частоты, такие как тактовые частоты CKcnt1 и CKdac1 подсчета.

Блок 28 вывода имеет усилитель 28а считывания (S·A) и блок 28b интерфейса (блок IF). Усилитель 28а считывания детектирует сигнал (малый по амплитуде, хотя и цифровой) в горизонтальной линии 18 сигнала. Блок 28b интерфейса обрабатывает интерфейс между полупроводниковым устройством 1 формирования изображения и внешним оборудованием. Выход блока 28b интерфейса подключен к выходному разъему 5 с таким образом, что видеоданные выводят в схему на последующем этапе. Выходной блок 28 может иметь блок цифровых операций между усилителем 28а считывания и блок 28b интерфейса для выполнения различных типов цифровых операций.

Каждый из единичных пикселей 3 соединен с блоком 14 вертикальной развертки через линию 15 управления строками, выполненную с возможностью выбора строк и с одним из блоков 250 АЦ преобразования, предусмотренных по одному для каждого из вертикальных столбцов блока 26 АЦ преобразования в столбце через линию 19 вертикального сигнала. Здесь линии 15 управления строками относятся к проводам, которые обычно выходят из блока 14 вертикальной развертки и подведены к пикселям.

Различные схемы АЦ преобразования возможны для использования в блоках 250 АЦ преобразования с точки зрения размеров схемы, скорости обработки (улучшение скорости), разрешающей способности и других факторов. В качестве примера используется схема АЦ преобразования, работающая на основе сравнения с опорным сигналом, интегрирования наклона или сравнения с пилообразным сигналом. При АЦ преобразовании на основе сравнения с опорным сигналом, эффективный период для операции подсчета определяют на основе времени от начала (начала сравнения) до конца (конца сравнения) преобразования. Аналоговый целевой сигнал преобразуют в цифровые данные на основе сигнала EN включения подсчета, который указывает эффективный период.

Поэтому блок 27 генерирования опорного сигнала имеет блок 270 АЦ преобразования (ЦАП: цифро-аналоговый преобразователь), который генерирует опорный сигнал SLP_ADC с наклоном (скоростью изменения), обозначенным данными CN4 управления из блока 20 управления передачей данных/синхронизации. Блок 270 генерирует опорный сигнал из исходного значения, указанного данными CN4 управления, из блока 20 управления передачей данных/синхронизации, синхронно с тактовой частотой подсчета CKdac1. Тактовая частота подсчета CKdac1 может быть той же, что и тактовая частота подсчета CKcnt1 для блока 254 счетчика.

Каждый из блоков 250 АЦ преобразования включает в себя блок 252 сравнения (СОМР) и блок 254 счетчика, который может переключаться между режимами прямого подсчета и обратного подсчета. В этом примере каждый из блоков 250 дополнительно включает в себя блок 258 переключателя и блок 256 сохранения данных в последующем каскаде блока 254 счетчика. Блок 252 сравнения сравнивает опорный сигнал SLP_ADC, генерируемый блоком 27 генерирования опорного сигнала, с напряжением Vx сигнала аналогового пикселя, полученным из модульных пикселей 3 в выбранных столбцах через вертикальную линию 19 сигнала (H1, Н2, …, Hh). Блок 254 счетчика подсчитывает активную длительность сигнала EN включения подсчета с тактовой частотой подсчета CKcnt1, и содержит результат подсчета. Сигнал EN включения подсчета имеет постоянное соотношение с выходным сигналом Со сравнения блока 252 сравнения.

Блок 20 управления передачей данных/синхронизацией подает сигнал CN5 управления в блок 254 счетчика каждого из блоков 250 АЦ преобразования. Сигнал управления задает информацию управления. Такая информация управления включает в себя информацию о том, работает ли блок 254 счетчика в режиме прямого или обратного подсчета для подсчета Р- и D-фаз. Такая информация управления также включает в себя информацию об установке и переустановке исходного значения Dini для подсчета Р-фаз и другую информацию.

На входной вывод (+), один из двух выводов каждого из блоков 252 сравнения, подают опорный сигнал SLP_ADC, генерируемый блоком 27 генерирования опорного сигнала, как и на другие входные выводы (+). Входной вывод (-), другой из двух его выводов, подключен к ассоциированной линии из вертикальных линий 19 сигнала, расположенных в вертикальных столбцах, на которые подают напряжение Vx сигнала пикселя из блока 10 матрицы пикселей.

На вывод СК тактовой частоты блока 254 счетчика, вместе с другими выводами СК тактовой частоты, подают тактовую частоту CKcnt1 подсчета из блока 20 управления передачей данных/синхронизацией. Если блок 256 сохранения данных не предусмотрен, в блок 254 счетчика, как и в другие блоки 254 счетчика, подают импульсы управления из блока 12 горизонтальной развертки через линию 12с управления. Каждый из блоков 254 счетчика имеет функцию фиксации для удержания результатов подсчета и удержания выходного значения подсчета до тех пор, пока не поступит команда в виде импульса управления, подаваемого через линию 12с управления.

В настоящем варианте осуществления обработка CDS заканчивается блоками 250 АЦ преобразования. Однако данные Р-фазы на уровне Srst сброса и данные D-фазы на уровне Ssig сигнала могут быть переданы отдельно в выходной блок 28 так, что обработка CDS выполняется блоками цифровых операций, предусмотренными в последующем каскаде блоков 250 АЦ преобразования. Настоящий заявитель предложил различные схемы АЦ преобразования на основе сравнения с опорным сигналом, выполненные с возможностью выполнения АЦ преобразования и обработки CDS, используя блоки 250 АЦ преобразования, и эти схемы могут, в принципе, использоваться во всех вариантах осуществления.

Полупроводниковое устройство 1 формирования изображения в соответствии с настоящим вариантом осуществления выполнено в форме устройства в одной микросхеме (предусмотрено на одной полупроводниковой подложке), в которой соответствующие компоненты блока 7 управления запуском, такие как блоки 12 и 14 горизонтальной и вертикальной развертки сформированы интегрально с блоком 10 матрицы пикселей на одном кремниевом кристалле или в другой полупроводниковой области, используя ту же технологию, что и технология производства полупроводниковых интегральных микросхем.

Полупроводниковое устройство 1 формирования изображения может быть выполнено в форме одной микросхемы и при этом его компоненты сформированы интегрально в полупроводниковой области, как описано выше. В качестве альтернативы, однако, устройство 1 может быть выполнено в форме модуля, выполненного с возможностью формирования изображения, имеющего в дополнение к блоку 10 матрицы пикселей, блоку 7 управления запуском, блоку 26 АЦ преобразования столбца и другим блокам обработки сигналов, оптическую систему, такую как объектив формирования изображения, оптический фильтр низкой частоты или фильтр обрезки инфракрасного излучения, упакованные вместе, хотя иллюстрация этого здесь не приведена.

На выходной стороне каждого из блоков 250 АЦ преобразования, выход блока 254 счетчика, например, может быть соединен с горизонтальной линией 18 сигнала. В качестве альтернативы блок 256 сохранения данных, используемый в качестве запоминающего устройства, и блок 258 переключателя могут быть предусмотрены в последующем каскаде блока 254 счетчика, как показано на чертеже. Блок 254 счетчика имеет функцию фиксации для удержания результата подсчета блока 254 счетчика. Блок 258 переключателя предусмотрен между блоком 254 счетчика и блоком 256 сохранения данных. Блок 258 переключателя имеет переключатель SW для каждого из вертикальных столбцов.

В конфигурации, включающей в себя блоки 256 сохранения данных, на переключатель SW, как и на другие переключатели SW вдоль вертикальных столбцов, подают импульс CN8 команды передачи памяти в качестве импульса управления, в определенный момент времени, из блока 20 управления передачей данных/синхронизацией. При подаче импульса CN8 команды передачи памяти переключатели SW 258 блока переключателя передают значения подсчета ассоциированных блоков 254 счетчика в блоки 256 сохранения данных. Блоки 256 сохранения данных удерживают и сохраняют переданные значения подсчета. В блоки 256 подают импульс управления из блока 12 горизонтальной развертки через линию 12с управления. Те же блоки 256 удерживают значения подсчета из блоков 254 счетчика до тех пор, пока не поступит команда в виде импульса управления, подаваемого через линию 12с управления.

Блок 12 горизонтальной развертки выполнен с возможностью использования в качестве блока сканирования считывания, который считывает значения подсчета из блоков 256 сохранения данных параллельно с обработкой, выполняемой блоками 252 сравнения и блоками 254 счетчика блоков 26 АЦ преобразования столбцов. Выходы блоков 256 сохранения данных подключены к горизонтальным линиям 18 сигнала. Каждая из горизонтальных линий 18 сигнала имеет такую же ширину или в два раза большую ширину (например, для дополнительного выхода), что и битовая ширина блока 250 АЦ преобразования. Те же линии 18 подключены к блоку 28 выхода, имеющему усилители 28а считывания, ассоциированные с выходными линиями. Следует отметить, что блоки 254 счетчика, блоки 256 сохранения данных, блок 258 переключателя и горизонтальные линии 18 сигналов, каждый выполнен с возможностью обработки n битов.

Полупроводниковое устройство 1 формирования изображения в соответствии с настоящим вариантом осуществления управляется двумя источниками питания, один из них цифровой и другой аналоговый. Четыре вывода питания (не показаны), а именно вывод питания для цифрового положительного напряжения DVDD, другой для цифрового напряжения DVSS заземления, еще один для аналогового положительного напряжения AVDD и еще один другой для аналогового напряжения AVSS заземления, предусмотрены в полупроводниковой микросхеме, в которой сформировано полупроводниковое устройство 1 формирования изображения.

Полупроводниковое устройство 1 формирования изображения включает в себя модуль 300 источника питания, выполненный с возможностью генерирования напряжений источника питания на основе установки ST времени накопления, подаваемой в виде команды из модуля 20 управления передачей данными/синхронизацией и информации TS-Vout установки напряжения для регулировки вручную. Напряжения источника питания подают в разные модули. Модуль 300 источника питания включает в себя положительный источник 302 питания и отрицательный источник 304 питания. Положительный источник 302 питания генерирует цифровое положительное напряжение DVDDw или аналоговое положительное напряжение AVDDw путем увеличения цифрового положительного напряжения DVDD или аналогового положительного напряжения AVDD. Отрицательный источник 304 питания генерирует цифровое отрицательное напряжение DVSSw или аналоговое отрицательное напряжение AVSSw на основе цифрового положительного напряжения DVDD. Таким образом, полупроводниковое устройство 1 формирования изображения выполнено в виде так называемого устройства на одной микросхеме, которое сформировано интегрально в полупроводниковой области, изготовленной, например, из монокристаллического кремния, с использованием тех же технологий, которые применяются для производства полупроводниковых интегральных схем. То же устройство 1 включает в себя модуль 300 источника питания и другие компоненты, такие как модуль 7 управления запуском и выходной модуль 28 вместе с модулем 10 матрицы пикселей.

В настоящем варианте осуществления цифровое положительное напряжение DVDD или аналоговое положительное напряжение AVDD увеличивают с помощью источника 302 положительного питания, и, кроме того, цифровое отрицательное напряжение DVSSw или аналоговое отрицательное напряжение AVSSw генерируют, используя отрицательный источник 304 питания, таким образом, генерируя разные уровни напряжения питания в полупроводниковом устройстве 1 формирования изображения (в полупроводниковой микросхеме). Такая компоновка позволяет создавать множество напряжений источника питания в микросхеме, даже если только одно напряжение источника питания подано снаружи в полупроводниковую микросхему. Использование цифрового отрицательного напряжения DVSS уменьшает шумы, которые формируют темновой ток.

Следует отметить, что здесь как положительные, так и отрицательные источники 302 и 304 питания встроены в полупроводниковое устройство 1 формирования изображения в качестве примера. Однако положительные и отрицательные источники 302 и 304 питания могут быть предусмотрены в области, отдельной от полупроводниковой области, в которой расположены модуль 10 матрицы пикселей, модуль 7 управления запуском и другие компоненты (см. устройство 8 формирования изображения, которое будет описано ниже).

Интерфейс между модулем матрицы пикселей и модулем вертикальной развертки: первый вариант осуществления

На фиг.2 показана схема, иллюстрирующая полупроводниковое устройство 1А формирования изображения в соответствии с первым вариантом осуществления, который фокусируется на интерфейсе между модулем 14 вертикальной развертки и модулем 10 матрицы пикселей. На фиг.2А показан схема, описывающая пример схемы участка интерфейса между модулем 14а установки вертикального адреса и модулем 14b управления вертикальной разверткой.

Единичный пиксель 3 включает в себя четыре транзистора (транзистор 34 выбора считывания, транзистор 36 сброса, транзистор 40 вертикального выбора и усилительный транзистор 42), каждый из которых имеет разные функции, в качестве основных элементов, в дополнение к блоку 32 генерирования заряда. Транзистор 34 выбора считывания, транзистор 36 сброса и усилительный транзистор 42 составляют, вместе с плавающей диффузионной областью 38, блок 5 генерирования сигнала пикселя (блок выходного сигнала). Затем, блок 5 генерирования сигнала пикселя и транзистор 40 вертикального выбора составляют блок 6 выходного сигнала. Тот же блок 6 генерирует и выводит напряжение Vx сигнала пикселя для сигнального заряда, генерируемого блоком 32 генерирования заряда. Транзисторы 34, 36, 40 и 42 также могут совместно называться транзисторами пикселя.

Затвор транзистора 34 выбора считывания (транзистор передачи/транзистора считывания), составляющего блок передачи, соединен вместе с затворами таких же транзисторов 34 в одной строке, с проводом 54 передачи. Этими затворами управляют с помощью сигнала TRG передачи. Затвор транзистора 36 сброса, составляющий блок инициализации, соединен вместе с затворами таких же транзисторов 36 в одной строке с проводом 56 сброса. Этими затворами управляют с помощью сигнала RST сброса. Затвор транзистора 40 вертикального выбора (транзистор выбора) соединен вместе с затворами таких же транзисторов 40 в одной строке с вертикальной линией 58 выбора. Этими затворами управляют с помощью сигнала VSEL вертикального выбора. Провод 54 передачи, провод 56 сброса и вертикальная линия 58 выбора представляют собой линии 15 управления строкой, показанные на фиг.1.

Обычно двоичный импульс, который является активным при высоком уровне (уровне источника напряжения), и неактивным при низком уровне (опорный уровень), используется для всех сигналов, то есть в качестве сигнала TRG передачи, сигнала RST сброса и сигнала VSEL вертикального выбора. Уровень напряжения источника питания составляет, например, приблизительно 3 В. Опорный уровень составляет, например, от 0,4 до 0,7 В или уровень заземления, то есть 0 В. Однако некоторые или все импульсы могут иметь отрицательный потенциал приблизительно -1 В, в зависимости от обстоятельств.

Блоки 32 генерирования заряда, пример блока детектирования, которые включают в себя фотодиод PD или другой элемент DET восприятия света, каждый имеет один конец (сторону анода) элемента DET восприятия света, соединенный с опорным потенциалом Vss на стороне низкого потенциала (отрицательный потенциал, например, приблизительно -1 В). Каждый из блоков 32 имеет другой конец (сторону катода) элемента DET восприятия света, соединенный с входным выводом (обычно истоком) транзистора 34 выбора считывания. Следует отметить, что опорный потенциал Vss может представлять собой потенциал GND заземления. Выходной вывод транзистора 34 выбора считывания (обычно сток) соединен с соединительным узлом, с которым соединены транзистор сброса 36, плавающая диффузионная область 38 и усилительный транзистор 42. Исток транзистора 36 сброса соединен с плавающей диффузионной областью 38, и его сток соединен с источником Vrd питания сброса (обычно используется также как источник Vdd питания для аналоговых схем = AVDD).

Сток транзистора 40 вертикального выбора, например, соединен с истоком усилительного транзистора 42, его исток соединен с линией 51 пикселей, а его затвор (в частности, называется затвором SELV вертикального выбора) соединен с линией 58 вертикального выбора. Линия 51 пикселей соединена, вместе с другими линиями 51 пикселя в том же столбце, с вертикальной линией 19 сигнала. Затвор усилительного транзистора 42 соединен с плавающей диффузионной областью 38, его сток соединен с источником Vdd питания, а его исток соединен с линией 51 пикселей и, кроме того, с вертикальной линией 19 сигнала через транзистор 40 вертикального выбора. Следует отметить, что настоящий вариант осуществления не ограничен такой конфигурацией. В качестве альтернативы, транзистор 40 вертикального выбора и усилительный транзистор 42 можно поменять местами таким образом, что сток транзистора 40 вертикального выбора будет соединен с источником Vdd питания, и его исток будет соединен со стоком усилительного транзистора 42, так что исток усилительного транзистора 42 будет соединен с линией 51 пикселя.

Один конец линии 19 вертикального сигнала продолжается в направлении блока 26 АЦ преобразования в столбце. Та же линия 19 подключена к блоку 24 управления током считывания вдоль ее пути. Хотя подробная иллюстрация этого опущена, блок 24 управления током считывания имеет нагрузочный МОП транзистор вдоль каждого вертикального столбца и составляет, вместе с блоком источника опорного тока, схему токового зеркала, в которой затворы нагрузочных МОП транзисторов соединены вместе. Эта схема токового зеркала используется как источник тока для вертикальных линий 19 сигнала. Блок 24 также составляет, вместе с усилительным транзистором 42, истоковый повторитель, который подает приблизительно постоянный рабочий ток (ток считывания).

В модуль 14 вертикальной развертки подают, в качестве напряжения источника питания, цифровое положительное напряжение DVDDw или аналоговое положительное напряжение AVDDw на его положительный вывод питания из источника 302 положительного питания. В тот же модуль 14 подают, в качестве напряжения источника питания, цифровое отрицательное напряжение DVSSw или аналоговое отрицательное напряжение AVSSw на его вывод отрицательного питания от источника 304 отрицательного питания (x: любое число от 1 до 3). С другой стороны, его стандартный вывод соединен со стандартным потенциалом (заземлен). Например, модуль 14а установки вертикального адреса выполнен с возможностью, например, использования декодера. В тот же модуль 14а подают цифровое положительное напряжение DVDD1 или аналоговое положительное напряжение AVDD1 на его вывод положительного питания от положительного источника 302 питания, который представляет собой его стандартный вывод, соединенный со стандартным потенциалом (заземлен).

Модуль 14b управления вертикальной разверткой включает в себя модули 146 сдвига уровня (L/S) и задающие модули 148 для линий управления строкой (провод 54 передачи, провод 56 сброса и линии 58 вертикального выбора) в каждом ряду. Выводы положительного источника питания модулей 146 сдвига уровня и задающих модулей 148 соединены с непоказанным положительным источником 302 питания, и их выводы отрицательного питания соединены с источником 304 отрицательного питания (подробное описание будет приведено ниже).

Например, модуль 14а установки вертикального адреса включает в себя инвертор КМОП в его выходном каскаде, как показано на фиг.2А. Инвертор КМОП состоит из двух МОП транзисторов, соединенных последовательно, то есть МОП транзистора с n-каналом (nMOS172), предусмотренного на стороне заземления, и МОП транзистора с p-каналом (pMOS173), предусмотренного на стороне положительного питания, для получения комплементарного выходного импульса. Входная сторона инвертора КМОП используется как неинвертируемый вход IN модуля 146 сдвига уровня, и выход инвертора КМОП используется в качестве инвертированного входа xIN модуля 146 сдвига уровня.

Модули 146 сдвига уровня каждый представляет собой модуль ступенчатого сдвига уровня, который включает в себя первый и второй схемные блоки 180_1 и 180_2 и инвертор КМОП. Первый и второй схемные блоки 180_1 и 180_2 составляют дифференциальную пару. В каждый из схемных блоков 180_1 и 180_2 подают аналоговое положительное напряжение AVDDw на их вывод положительного питания из источника 302 положительного питания и аналоговое отрицательное напряжение AVSSw на их вывод отрицательного питания из источника 304 отрицательного питания. Аналоговое положительное напряжение AVDDw выше, чем цифровое положительное напряжение DVDD1 или аналоговое положительное напряжение AVDD1, подаваемое в модуль 14а установки вертикального адреса.

Первый схемный блок 180_1 состоит из nМОП182 на стороне отрицательного питания и рМОП183 на стороне положительного питания, соединенных последовательно. Второй схемный блок 180_2 состоит из nМОП184 на стороне отрицательного питания и рМОП185 на стороне положительного питания, соединенных последовательно. Первый и второй схемные блоки 180_1 и 180_2 соединены перекрестно, при этом сток nМОП182 первого схемного блока 180_1 соединен с затвором рМОП185 второго схемного блока 180_2, а сток nМОП184 второго схемного блока 180_2 соединен с затвором рМОП183 первого схемного блока 180_1. Инвертор КМОП состоит из nМОП186 стороны отрицательного питания и рМОП187 стороны положительного питания, соединенных последовательно. Выход (точка соединения между nМОП184 и рМОП185) второго схемного блока 180_2 соединен с затворами nМОП186 и рМОП187.

Инвертированный входной сигнал xIN подается на затвор nМОП182, а неинвертированный входной сигнал IN подается на затвор nМОП184. Выходной импульс (с амплитудой в диапазоне от приблизительно AVSSw до AVDDw), противоположный по логике инвертированному входному сигналу xIN, получают со стока nМОП182. Этот выходной импульс подают на затвор рМОП185. Выходной импульс (с амплитудой в диапазоне от приблизительно AVSSw до AVDDw), противоположный по логике неинвертированному входному сигналу IN, получают со стока nМОП184. Этот выходной импульс подают на затвор рМОП183. Таким образом, каждый модуль 146 сдвига уровня имеет комплементарный (дифференциальный) входной интерфейс в своем входном каскаде и выполнен с возможностью использования перекрестной положительной обратной связи в выходном каскаде, благодаря комплементарному входному импульсу, подаваемому на затворы nМОП182 и nМОП184.

Неинвертированный входной сигнал IN подают во второй схемный блок 180_2 и инвертируют по логике, а также дополнительно инвертируют по логике с помощью инвертора КМОП (nМОП186 и рМОП187). Это обеспечивает выходной импульс, идентичный по логике входному, но преобразованный по уровню напряжения. В настоящем примере в каждый из модуля 146 сдвига уровня подают цифровое положительное напряжение DVDD1 (или аналоговое положительное напряжение AVDD1) с высоким уровнем и входной импульс GND (импульс TRG передачи, импульс RST сброса и импульс VSEL вертикального выбора) на низком уровне из модуля 14а установки вертикального адреса. Затем каждый из модулей 146 сдвига уровня преобразует входной импульс, изменяя его высокий уровень в аналоговое положительное напряжение AVDDw, а низкий уровень в аналоговое отрицательное напряжение AVSSw, и выводят этот преобразованный импульс. Импульсы, преобразованные по уровню напряжения модулями 146 сдвига уровня, подают в ассоциированные транзисторы 34, 36 и 42 единичного пикселя 3 через задающие модули 148.

В модуль 14b управления вертикальной разверткой полупроводникового устройства 1А формирования изображения в соответствии с первым вариантом осуществления подают следующие напряжения на выводы питания модулей 146 сдвига уровня и задающие модули 148. Вначале, аналоговое положительное напряжение AVDD2_1 подают на вывод положительного питания модуля 146_1 сдвига уровня для импульса RST сброса от источника 302 положительного питания. Аналоговое положительное напряжение AVDD2_2 подают на вывод положительного питания модуля 146_2 сдвига уровня для импульса TRG передачи от источника 302 положительного питания. Аналоговое положительное напряжение AVDD2_3 подают на вывод положительного питания модуля 146_3 сдвига уровня для импульса VSEL вертикального выбора из источника 302 положительного питания.

Аналоговое положительное напряжение AVDD3_1 подают на вывод положительного питания задающего модуля 148_1 для импульса RST сброса от источника 302 положительного питания. Аналоговое положительное напряжение AVDD3_2 подают на вывод положительного питания задающего модуля 148_2 для импульса TRG передачи от источника 302 положительного питания. Аналоговое положительное напряжение AVDD3_3 подают на вывод положительного питания задающего модуля 148_3 для импульса VSEL вертикального выбора от источника 302 положительного питания.

Цифровое положительное напряжение DVDD1 (или аналоговое положительное напряжение AVDD1) для модуля 14а установки вертикального адреса, аналоговые положительные напряжения AVDD2_1, AVDD2_2 и AVDD2_3 для модулей 146 сдвига уровня и аналоговые положительные напряжения AVDD3_1, AVDD3_2 и AVDD3_3 для задающих модулей 148 обрабатывают, например, следующим образом. Вначале положительный источник питания для модуля 14а установки вертикального адреса может быть цифровым или аналоговым. В модуле 14b вертикального управления, с другой стороны, все напряжения AVDD2_1, AVDD2_2, AVDD2_3, AVDD3_1, AVDD3_2 и AVDD3_3 являются общими. Естественно, что это представляет собой только пример, и он может быть модифицирован соответствующим образом, как описано в повторно опубликованной заявке на патент № WO 2003/085964.

Кроме того, в модуле 14b вертикального управления, в соответствии с первым вариантом осуществления, все выводы отрицательного питания модулей 146 сдвига уровня и задающих модулей 148 соединены вместе с источником 304А отрицательного питания, независимо от того, какой из импульса RST сброса, импульса TRG передачи и импульса VSEL вертикального выбора используются модулями уровня 146 сдвига и задающими модулями 148, что подается одинаковое аналоговое отрицательное напряжение AVSS2. Источник 304А отрицательного питания в соответствии с первым вариантом осуществления принимает информацию установки времени накопления (установка TS времени накопления) от внешнего основного модуля управления, который генерирует (регулирует) выходное напряжение Vout на основе этой информации. Поэтому аналоговое отрицательное напряжение AVSS2 регулируют до уровня отрицательного напряжения, пропорционального установке TS накопленного времени.

Пример конфигурации источника отрицательного питания

На фиг.3 показана схема, иллюстрирующая пример конфигурации источника 304 отрицательного питания. В источнике 304 отрицательного питания используется схема подкачки заряда. Более конкретно, источник 304 отрицательного питания включает в себя модуль 310 усиления ошибки, модуль 320 генерирования напряжения источника, сглаживающий конденсатор 330, модуль 340 обратной связи и модуль 350 управления выходным напряжением. Максимальный отрицательный уровень аналогового отрицательного напряжения AVSSw, пропорциональный выходному напряжению Vout, должен быть установлен на уровень, при котором не происходит пробой устройства (в частности, транзисторов в единичных пикселях 3 модуля 10 матрицы пикселей).

Модуль 320 генерирования напряжения источника питания генерирует выходное напряжение Vout на основе выхода модуля 310 усиления ошибки. Модуль 350 управления выходным напряжением управляет модулем 310 усиления ошибки и модулем 340 обратной связи на основе установки TS времени накопления, регулируя выходное напряжение Vout, генерируемое модулем 320 генерирования напряжения источника питания.

Модуль 310 усиления ошибки включает в себя усилитель 312 ошибки и модуль 316 генерирования опорного сигнала. Усилитель 312 ошибки включает в себя, например, операционный усилитель. Модуль 316 генерирования опорного сигнала генерирует опорное напряжение Vref1 (опорный сигнал). В усилитель 312 ошибки подают опорное напряжение Vref1 на его неинвертируемый входной вывод (+) из модуля 316 генерирования опорного сигнала и напряжение Vfb обратной связи (сигнал обратной связи) на его инвертируемый входной вывод (-) из модуля 340 обратной связи.

Модуль 320 генерирования напряжения источника питания включает в себя переключатели 322_1-322_4 и конденсатор 324 накачки емкостью Ср. Один вывод переключателя 322_1 заземлен, а другой его вывод соединен с одним выводом 324а конденсатора 324 накачки и одним выводом переключателя 322_2. Другой вывод переключателя 322_2 соединен с выходным выводом 304out источника 304 отрицательного питания, который представляет собой точку соединения между одним концом сглаживающего конденсатора 330 и модулем 340 обратной связи. Другой вывод сглаживающего конденсатора 330 заземлен.

На один вывод переключателя 322_3 подают цифровое положительное напряжение DVDD, а другой его вывод соединен с другим выводом 324b конденсатора 324 накачки и с одним выводом переключателя 322_4. Другой вывод переключателя 322_4 соединен с выходным выводом усилителя 312 ошибки.

Модуль 340 обратной связи включает в себя первый и второй резистивные элементы 342 и 344 и модуль 346 генерирования стандартного сигнала. Тот же модуль 346 генерирует стандартное напряжение Vref0 (стандартный сигнал). Один вывод первого резистивного элемента 342 соединен с выходным выводом 304out, а другой его вывод соединен с одним выводом второго резистивного элемента 344. Стандартное напряжение Vref0 подают на другой вывод второго резистивного элемента 344 из модуля 346 генерирования стандартного сигнала. Модуль 340 обратной связи соответственно делит напряжение между стандартным напряжением Vref0 и выходным напряжением Vout (отрицательное напряжение) выходного вывода 304out, используя резистивные элементы 342 и 344, генерируя напряжение Vfb обратной связи. Усилитель 312 сигнала ошибки модуля 310 усиления ошибки усиливает разность между напряжением Vfb обратной связи и опорным напряжением Vref1, генерируя напряжение Vo управления (попадающее в диапазон от 0 V до цифрового положительного напряжения DVDD) и подает это напряжение Vo на выключатель 322_4. Цепь с отрицательной обратной связью сформирована в целом.

Здесь вначале переключатели 322_1 и 322_3 замкнуты и переключатели 322_2 и 322_4 разомкнуты. В результате этого соединяется цифровое положительное напряжение DVDD и заземление (GND) через конденсатор 324 накачки, в результате чего происходит заряд конденсатора 324. Затем переключатели 322_1 и 322_3 размыкают и выключатель 322_4 замыкают. В результате этого другой вывод 324b конденсатора 324 накачки соединяется с выходным выводом усилителя 312 ошибки. Поскольку напряжение Vo управления больше, чем 0, но меньше, чем цифровое положительное напряжение DVDD, на один вывод 324а конденсатора 324 накачки поступает отрицательное напряжение относительно земли. Если в это время переключатель 322_2 замкнут, заряд, накопленный в конденсаторе 324 накачки, разделяется по емкости между конденсатором 324 накачки и сглаживающим конденсатором 330, создавая отрицательный заряд, сохраняемый в сглаживающем конденсаторе 330. В результате отрицательное выходное напряжение Vout генерируется на выходном выводе 304 out. Отрицательное выходное напряжение Vout пропорционально аналоговому отрицательному напряжению AVSSw.

Это выходное напряжение Vout зависит от напряжения Vo управления. С другой стороны, напряжение Vo управления задается опорным напряжением Vref1 и напряжением Vfb обратной связи. Напряжение Vfb обратной связи задается выходным напряжением Vout, отношением сопротивления между резистивными элементами 342 и 344 и стандартным напряжением Vref0. Источник 304 отрицательного питания формирует в целом цепь с отрицательной обратной связью. В результате выходное напряжение Vout удерживают при постоянном уровне на основе соотношения сопротивлений между резистивными элементами 342 и 344, стандартного напряжения Vref0 и опорного напряжения Vref1. Другими словами, выходное напряжение Vout можно регулировать путем регулирования соотношения сопротивления между резистивными элементами 342 и 344, стандартного напряжения Vref0 или опорного напряжения Vref1 (или используя два или более из этих параметров).

Основы регулирования отрицательного напряжения

На фиг.4 показаны схемы, описывающие примеры регулирования отрицательного выходного напряжения Vout (пропорционально аналоговому отрицательному напряжению AVSSw), выводимого из источника 304 отрицательного питания. В настоящем варианте осуществления источник 304 отрицательного питания выполнен так, что выходное напряжение Vout на выходном выводе 304out можно регулировать. Однако его регулирование осуществляют в соответствии с установкой времени накопления во время съемки изображения. Основной принцип состоит в том, чтобы обеспечить для стороны низкого и высокого уровня каждого из сигналов управления (импульс TRG передачи, импульс RST сброса и импульс VSEL вертикального выбора), выполненных с возможностью импульсного запуска одного из транзисторов 34, 36 и 42 выходного модуля 6 сигнала, регулирование уровня напряжения, соответствующего полярности сигнального заряда, на той стороне, чтобы с увеличением времени накопления сигнального заряда повышался уровень напряжения.

В настоящем варианте осуществления каждый из транзисторов выходного модуля 6 сигнала включает в себя транзистор NMOП, и сигнальный заряд является отрицательным (электроны). Поэтому, чем больше время накопления, тем до более высокого уровня регулируют отрицательный уровень выходного напряжения Vout (аналоговое отрицательное напряжение AVSSw) источника 304 отрицательного питания, соответствующего полярности отрицательного заряда. Уровни напряжений сигналов управления, предназначенных для управления транзисторами пикселей, устанавливают совместно с установкой времени накопления заряда.

Это основано на том факте, что, хотя шумы, связанные с темновыми токами, увеличиваются при более длительном времени накопления, например, в случае съемки изображения в условиях низкой освещенности, темновой ток может быть уменьшен в результате увеличения отрицательного уровня цифрового отрицательного напряжения DVSSw (в частности, для транзистора 34 выбора считывания).

Чем дольше время накопления заряда, тем большей проблемой становится темновой ток. Однако увеличение уровня отрицательного напряжения при более длительном времени накопления заряда может уменьшить темновой ток, обеспечивая улучшенное отношение "сигнал-шум" и, таким образом, улучшенное качество изображения. Если сосредоточиться на транзисторе 34 выбора считывания, использование отрицательного напряжения позволяет обеспечить большую амплитуду на затворе передачи, что позволяет увеличивать величину насыщения сигнала модулей 32 генерирования заряда (фотодиодов) и расширить динамический диапазон. Уменьшение темнового тока само по себе способствует улучшенному динамическому диапазону.

Как показано на фиг.4(1), например, выходное напряжение Vout (уровень отрицательного напряжения) на выходном выводе 304out относительно установки TS времени накопления составляет -1,0 В, когда 0 секунд ≤TS<0,5 секунды, -1,1 В, когда 0,5 секунды ≤TS<1,0 секунды, -1,2 В, когда 1,0 секунды ≤TS<1,5 секунды, -1,3 V, когда 1,5 секунды ≤TS<2 секунд, и -1,4 В, когда 2,0 секунды ≤TS. Таким образом, чем дольше время накопления, тем выше отрицательное напряжение.

Следует отметить, что, хотя уровень отрицательного напряжения регулируют здесь на пяти каскадах, уровень отрицательного напряжения можно регулировать на четырех или меньшем количестве каскадов или на шести или большем количестве каскадов. Само собой разумеется, что количество элементов, таких как переключатели 318 и 348, модуль 316 генерирования опорного сигнала и модуль 346 генерирования стандартного сигнала, и количество линий управления, выполненных с возможностью управления переключателями 318 и 348, увеличивается или уменьшается при изменении количества каскадов. Естественно, что возможно адаптировать конфигурацию для бесшагового регулирования уровня отрицательного напряжения.

Кроме того, во время съемки изображения, когда сигнальный заряд не накапливается, время накопления равно нулю. Поэтому отрицательный уровень напряжения может быть малым. В результате нет необходимости иметь отрицательный уровень напряжения. Как показано на фиг.4 (2), поэтому, уровень напряжения может быть равным стандартному напряжению (земля = 0 В в настоящем примере). Если напряжение во время съемки изображения используется как стандартный потенциал, становится возможным непосредственно подавлять нагрузку на пиксели и транзисторы их цепей управления и снижать ухудшение характеристик.

Следует отметить, что взаимосвязь между установкой TS времени накопления и выходным напряжением Vout, как показано на фиг.4, может быть установлена и зарегистрирована заранее для использования в качестве фиксированной взаимосвязи. В качестве альтернативы взаимосвязь может быть изменена соответствующим образом на основе информации TS-Vout установки напряжения, подаваемой из внешнего основного модуля управления. Темновой ток возникает в разных обстоятельствах, если изменяется температура окружающей среды. Однако, если будут предприняты меры противодействия, такие как описано выше, становится возможно соответствующим образом изменять (регулировать вручную) выходное напряжение Vout относительно времени накопления с помощью непоказанной панели управления устройством 8 формирования изображения в соответствии с положением вещей, даже когда модуль 300 источника питания не имеет функции автоматического регулирования выходного напряжения Vout в соответствии с условиями окружающей среды.

Регулирование отрицательного напряжения: первый пример

На фиг.5 показана схема, иллюстрирующая конфигурацию цепей источника 304 отрицательного питания в соответствии с первым примером, который выполнен с возможностью обеспечения регулирования отрицательного напряжения, показанного на фиг.4. Этот первый пример разработан для регулирования напряжения Vfb обратной связи путем регулирования соотношения сопротивлений между резистивными элементами 342 и 344, при одновременном поддержании постоянными стандартного напряжения Vref0 и опорного напряжения Vref1, регулируя, таким образом, выходное напряжение Vout.

Более конкретно, второй резистивный элемент 344 включает в себя комбинацию резистивных элементов и переключателей. Сопротивление R_344 второго резистивного элемента 344 регулируют путем управления операцией включения/выключения переключателей, регулируя, таким образом, напряжение Vfb обратной связи и выходное напряжение Vout. Множество резистивных элементов может быть расположено по-разному, включая в себя последовательные цепи, параллельные цепи и последовательно-параллельные цепи. Переключатели выполнены с возможностью изменения соответствующим образом составного сопротивления для различных конфигураций цепей резистора. Для упрощения описания, ниже будет приведено описание примера, в котором второй резистивный элемент 344 включает в себя множество резистивных элементов, которые расположены каскадами.

Вначале в источнике 304_1 отрицательного питания в соответствии с первым примером второй резистивный элемент 344 включает в себя множество вторых резистивных элементов 344_1-344_х (где х=1-5 на чертеже), которые расположены каскадами. Переключатель 348_х соединен параллельно с каждым из вторых резистивных элементов 344_х на стороне стандартного модуля 346 генерирования сигнала, отличных от второго резистивного элемента 344_1. Модуль 350 управления выходным напряжением включает в себя логику 354 управления, выполненную с возможностью управления переключателями 348_х. В каждый из переключателей 348_х подают сигнал SW_x управления переключателем на их входной вывод управления из логики 354 управления.

Логика 354 управления управляет тем, который из переключателей 348_х следует включить в соответствии с установками времени накопления (электронного затвора), подаваемыми извне. Это обеспечивает возможность регулирования сопротивления R344 второго резистивного элемента 344 в соответствии с установками времени накопления, регулируя, таким образом, выходное напряжение Vout в соответствии с установкой времени накопления.

Таким образом, модуль 350 управления выходным напряжением изменяет сопротивление R_344 в соответствии с установкой времени накопления, используя переключатели 348_х, предусмотренные во втором резистивном элементе 344, изменяя, таким образом, отношение сопротивления между резистивными элементами 342 и 344 и устанавливая, таким образом, отрицательное напряжение в соответствии с установкой времени накопления, как показано на фиг.4. Как описано выше, используя схему, выполненную с возможностью определения отрицательного напряжения путем регулирования напряжения Vfb обратной связи, которое осуществляется путем регулирования соотношения сопротивлений между резистивными элементами 342 и 344 модуля 340 обратной связи, становится возможным непосредственно регулировать с помощью схемы с малыми размерами уровень отрицательного напряжения в соответствии с установкой времени накопления, без отрицательного влияния на потребление энергии.

В настоящем примере регулируют напряжение Vfb обратной связи путем регулирования соотношения сопротивлений между резистивными элементами 342 и 344. В качестве альтернативы, однако, возможно принять конфигурацию для непрерывного регулирования напряжения Vfb обратной связи (уровень отрицательного напряжения), путем использования переменного резистивного элемента (например, используя рабочее сопротивление полупроводникового элемента), сопротивление которого можно регулировать непрерывно. Следует отметить, однако, что на сопротивление такого переменного резистивного элемента обычно влияют условия окружающей среды, такие как температура, в результате чего получается худшая точность при управлении напряжением Vfb обратной связи, то есть выходным напряжением Vout. В этом отношении, если второй резистивный элемент 344 эквивалентно включает в себя множество вторых резистивных элементов 344_х и множество переключателей SW_х и если операциями включения/выключения переключателей SW_x управляют с помощью модуля 350 управления выходным напряжением, такая компоновка является предпочтительной в том, что она обеспечивает более высокую точность при управлении напряжением Vfb обратной связи и выходным напряжением Vout.

Регулирование отрицательного напряжения: второй пример

На фиг.5А показана схема, иллюстрирующая конфигурацию схемы источника 304 отрицательного питания в соответствии со вторым примером, выполненным с возможностью обеспечения возможности регулирования отрицательного напряжения, показанного на фиг.4. Второй пример разработан для регулирования напряжения Vfb обратной связи и выходного напряжения Vout путем регулирования стандартного напряжения Vref0, при одновременном поддержании постоянными опорного напряжения Vref1 и соотношения сопротивлений между резистивными элементами 342 и 344.

Более конкретно, модуль 346 генерирования стандартного сигнала источника 304_2 отрицательного питания в соответствии со вторым примером включает в себя комбинацию из модулей 346_х генерирования стандартного сигнала, выполненных с возможностью генерирования отличающихся друг от друга стандартных напряжений Vref0_x, и переключателей 348_х (где х=1-5 на чертеже). Модули 346_х генерирования стандартного сигнала и переключатели 348_х соединены последовательно. Модуль 350 управления выходным напряжением включает в себя логику 354 управления, выполненную с возможностью управления переключателями 348_х. На входной вывод управления каждого из переключателей 348_х подают сигнал SW_х управления переключателем из логики 354 управления.

Логика 354 управления управляет тем, какой из переключателей 348_х требуется включить в соответствии с установкой времени накопления (электронного затвора), подаваемой извне. Это обеспечивает возможность регулирования стандартного напряжения Vref0 модуля 346 генерирования стандартного сигнала в соответствии с установкой времени накопления, регулируя, таким образом, выходное напряжение Vout в соответствии с установкой времени накопления.

Таким образом, модуль 350 управления выходным напряжением изменяет стандартное напряжение Vref0 в соответствии с установкой времени накопления, используя модули 346_х генерирования стандартного сигнала, выполненные с возможностью генерирования отличающихся друг от друга стандартных напряжений и переключателей 348_х, устанавливая, таким образом, отрицательное напряжение в соответствии с установкой времени накопления, как показано на фиг.4. Как описано выше, используя схему, выполненную с возможностью определения отрицательного напряжения путем регулирования стандартного напряжения Vref0 модуля 340 обратной связи, становится возможным непосредственно регулировать, используя схему с малыми размерами, уровень отрицательного напряжения в соответствии с установкой времени накопления, без отрицательного влияния на потребление энергии. Кроме того, этот пример применим независимо от используемой структуры пикселя.

Регулирование отрицательного напряжения: третий пример

На фиг.5В показана схема, иллюстрирующая конфигурацию цепи источника 304 отрицательного питания в соответствии с третьим примером, выполненным с возможностью обеспечения возможности регулирования отрицательного напряжения, показанного на фиг.4. Этот третий пример разработан для регулирования напряжения Vo управления путем регулирования опорного напряжения Vref1, при одновременном поддержании постоянными стандартного напряжения Vref0 и соотношения сопротивлений между резистивными элементами 342 и 344, регулируя, таким образом, выходное напряжение Vout.

Более конкретно, модуль 310 усиления ошибки источника 304_3 отрицательного питания в соответствии с третьим примером включает в себя комбинацию модулей 316_х генерирования опорного сигнала, выполненную с возможностью генерирования отличающихся друг от друга опорных напряжений Vref1_x, и переключателей 318_х (где х=1-5 на чертеже). Модули 316_х генерирования опорного сигнала и переключатели 318_х включены последовательно. Модуль 350 управления выходным напряжением включает в себя логику 354 управления, выполненную с возможностью управления переключателями 318_х. В каждый из переключателей 318_х подают сигнал SW_x управления переключением на его входной вывод управления из логики 354 управления.

Логика 354 управления управляет тем, какой из переключателей 318_х следует включить в соответствии с установкой времени накопления (электронным затвором), подаваемой извне. Это позволяет регулировать опорное напряжение Vref1 модуля 316 генерирования опорного сигнала в соответствии с установкой времени накопления, регулируя, таким образом, выходное напряжение Vout в соответствии с установкой времени накопления.

Таким образом, модуль 350 управления выходным напряжением изменяет опорное напряжение Vref1 в соответствии с установкой времени накопления, используя модули 316_х, выполненные с возможностью генерирования отличающихся друг от друга опорных напряжений Vref1_х и переключателей 318_х, устанавливая, таким образом, отрицательное напряжение в соответствии с установкой времени накопления, как показано на фиг.4. Как описано выше, используя схему, выполненную с возможностью определения отрицательного напряжения путем регулирования опорного напряжения Vref1 модуля 310 усиления ошибки, становится возможным непосредственно регулировать, с использованием схемы с малыми размерами, уровень отрицательного напряжения в соответствии с установкой времени накопления, без отрицательного влияния на потребление энергии. Кроме того, данный пример применим независимо от используемой структуры пикселя.

Следует отметить, что, хотя это и не показано на чертежах, примеры конфигурации, показанные на фиг.5-5В (с первого по третий примеры), могут быть скомбинированы в соответствии с необходимостью.

Пример задающей синхронизации

На фиг.6 показана временная диаграмма, иллюстрирующая пример синхронизации операций импульсов управления, выполненных с возможностью управления модульным пикселем 3. Модуль 14а установки вертикального адреса изменяет импульс VSEL вертикального выбора для выбранной строки до активного высокого уровня, включая, таким образом, транзистор 40 вертикального выбора (t10). В этих условиях тот же самый модуль 14а изменяет импульс сброса RST на активный высокий уровень на заданный промежуток времени, включая, таким образом, транзистор 36 сброса (t12-t14). Затем тот же модуль 14а изменяет импульс TRG передачи на активный высокий уровень на заданный промежуток времени, включая, таким образом, транзистор 34 выбора считывания. Это обеспечивает возможность переноса сигнального заряда, накопленного в модуле 32 генерирования заряда, в плавающую диффузионную область 38 (t16-t18).

Когда такой перенос сигнального заряда закончен, модуль 14а установки вертикального адреса изменяет импульс TRG передачи и импульс RST сброса на активный высокий уровень практически одновременно, включая, таким образом, транзистор 34 выбора считывания и транзистор 36 сброса. Это приводит к разряду ненужного заряда из модуля 32 генерирования заряда (t20-t22). Затем тот же модуль 14а изменяет импульс VSEL вертикального выбора для выбранной строки на неактивный низкий уровень и переходит к следующей строке. В результате напряжение Vx сигнала пикселя вертикальной линии 19 сигнала устанавливается на уровень Srst сброса на промежутке времени от t14 до t16. Напряжение Vx сигнала пикселя вертикальной линии 19 сигнала устанавливается на уровень Ssig сигнала на промежуток периода времени от t18 до t20.

Эти импульсы TRG, RST и VSEL управления подают в модули 146 сдвига уровня. В модули 146 сдвига уровня подают в качестве напряжений источника питания цифровое положительное напряжение DVDDw от источника 302 положительного питания и аналоговое отрицательное напряжение AVSSw от источника 304 отрицательного питания. Высокий и низкий уровни каждого из импульсов TRG, RST и VSEL управления сдвигают соответственно до аналогового положительного напряжения AVDDw и аналогового отрицательного напряжения AVSSw, управляя модульным пикселем 3 через задающие модули 148.

Здесь модуль 350 управления выходным напряжением регулирует отрицательное выходное напряжение Vout отрицательного источника 304 питания в соответствии с установкой времени накопления (электронный затвор), подаваемой извне. В результате аналоговое отрицательное напряжение AVSSw изменяется в соответствии с установками времени накопления, как показано на фиг.4.

Например, для датчика изображения КМОП для накопления кадра, требуется 0,1 секунды при частоте кадров десять кадров/секунду и 0,02 секунды для датчика изображения КМОП при частоте кадров 50 кадров/секунду, чтобы выполнить эти операции. Поэтому, длительное время накопления, составляющее одну или две секунды, используется редко и ограничено, например, съемкой изображения в темном помещении ночью. Поэтому уменьшение отрицательного напряжения (увеличение значения на стороне минуса) только в течение этого периода практически не оказывает влияния на характеристики транзистора, такие как нагрузка на оксидную пленку затвора и деградация характеристик транзистора, в результате, например, горячих носителей, обеспечивая, таким образом, сниженные шумы (белые точки), связанные с темновым током.

Как описано выше, когда установлено длительное время накопления, компоновка в соответствии с первым вариантом осуществления управляет отрицательным напряжением в соответствии с длительным временем накопления, подавляя, таким образом, шумы, связанные с темновым током. Кроме того, только отрицательным уровнем напряжения управляют в соответствии с установкой времени накопления, при этом оказывается малое отрицательное влияние на увеличение размеров схемы или потребление тока.

Интерфейс между модулем матрицы пикселей и модулем вертикальной развертки: второй вариант осуществления

На фиг.7 показана схема, иллюстрирующая полупроводниковое устройство 1В формирования изображения в соответствии со вторым вариантом осуществления, который сосредоточен на интерфейсе между модулем 14 вертикальной развертки и модулем 10 матрицы пикселей.

Вначале, что касается модуля 14b вертикального управления полупроводникового устройства 1В формирования изображения в соответствии со вторым вариантом осуществления, сторона положительного напряжения является той же, что и в соответствии с первым вариантом осуществления. В отличие от этого, источник 304В отрицательного питания в соответствии со вторым вариантом осуществления включает в себя источник 304А отрицательного питания в соответствии с первым вариантом осуществления для каждого из импульсов RST, TRG и VSEL. В каждый из источников 304А отрицательного питания подают информацию об установке времени накопления из внешнего основного модуля управления таким образом, что каждое из аналоговых отрицательных напряжений AVSS2_k (где k - равно 1-3) регулируют до уровня отрицательного напряжения, соответствующего установке времени накопления.

Вначале, что касается стороны отрицательного напряжения, выводы отрицательного питания модуля 146 сдвига уровня и задающего модуля 148 для каждого импульса RST сброса, импульса TRG передачи и импульса VSEL вертикального выбора соединяют вместе так, чтобы подать аналоговое отрицательное напряжение AVSS2. С другой стороны, в модули 146 сдвига уровня и задающие модули 148 для импульсов RST, TRG и VSEL подают разные аналоговые отрицательные напряжения AVSS2_1, AVSS2_2 и AVSS2_3. Оптимизация уровней напряжения путем подачи разных отрицательных напряжений в транзисторы 34, 36 и 42 обеспечивает уменьшенную нагрузку и оптимальные характеристики.

Например, транзистор 34 выбора считывания, транзистор 36 сброса и транзистор 40 вертикального выбора, составляющие модульный пиксель 3, каждый имеет оптимальные характеристики. В результате эти транзисторы могут отличаться по размерам затвора (W/L) и пороговому напряжению Vth. В этом случае подача одинакового аналогового отрицательного напряжения AVSSw, независимо от того, какие из импульсов RST, TRG и VSEL модулей 146 сдвига уровня и задающих модулей 148 используются, как в и первом варианте осуществления, не позволяет оптимизировать уровни отрицательного напряжения для транзисторов.

В отличие от этого, подача разных аналоговых отрицательных напряжений AVSSw_k, каждое из которых оптимизировано по уровню отрицательного напряжения для одного из импульсов RST, TRG и VSEL, как во втором варианте осуществления, позволяет выполнить оптимизацию установок отрицательного напряжения независимо от характеристик транзисторов, составляющих модульный пиксель 3. Это обеспечивает уменьшенную нагрузку и оптимальные характеристики, такие как величина тока утечки транзистора, когда они находятся в выключенном состоянии, для каждого из транзисторов.

Интерфейс между модулем матрицы пикселей и модулем вертикальной развертки: третий вариант осуществления

На фиг.8 показана схема, иллюстрирующая полупроводниковое устройство 1С формирования изображения в соответствии с третьим вариантом осуществления, который сосредоточен на интерфейсе между модулем 14 вертикальной развертки и модулем 10 матрицы пикселей. В третьем варианте осуществления модуль 10 матрицы пикселей имеет группы 2 единичных пикселей, расположенные в форме матрицы. Каждая из групп 2 единичных пикселей имеет структуру совместного использования пикселя, в которой некоторые из компонентов единичного пикселя 3 совместно используются множеством единичных пикселей 3.

Единичные пиксели 3, составляющие группу 2 модульных пикселей в блоке 10 матрицы пикселей выполнены так же, как и обычный датчик изображения КМОП. Здесь структура совместного использования с двумя пикселями показана, как пример, в котором одна группа из 2 единичных пикселей сформирована как комбинация из двух единичных пикселей 3. Следует отметить, что конфигурация из единичных пикселей 3 и конфигурация из группы 2 единичных пикселей, сформированная путем комбинирования единичных пикселей 3, представляют собой просто пример. Настоящий вариант осуществления не ограничен этим. Например, в конфигурации, показанной на фиг.8, настоящий вариант осуществления не ограничен группой из 2 единичных пикселей, состоящей из двух модульных пикселей 3. Вместо этого, та же группа 2 может быть составлена из трех, четырех или восьми единичных пикселей 3.

С точки зрения конфигурации схемы группа 2 единичных пикселей имеет два блока 32а, 32b генерирования заряда. Одни и те же блоки 32 совместно используют транзистор 36 сброса, плавающую диффузионную область 38 и усилительный транзистор 42, за исключением транзистора 34 выбора считывания. Следует отметить, что здесь предполагается, что пиксели, совместно использующие компоненты, расположены рядом друг с другом. Эти пиксели могут быть расположены рядом друг с другом по вертикали, по горизонтали или, как по вертикали, так и по горизонтали (то есть, по диагонали) на экране, когда единичные пиксели 3 расположены в виде квадратной решетки. В настоящем варианте осуществления предполагается, что одна группа 2 единичных пикселей состоит из двух единичных пикселей 3, расположенных в направлении строки (в вертикальном направлении).