Область техники, к которой относится изобретение

Настоящее изобретение относится к твердотельному устройству формирования изображения, которое может быть использовано для сканирующего устройства, видеокамеры, цифровой фотокамеры, и тому подобного.

Уровень техники

В последние годы КМОП-датчик изображения широко использовался для цифровой камеры, цифровой записывающей видеокамеры, камерного модуля для портативного телефона, и тому подобного. В связи с потребностями в уменьшении количества деталей, снижении энергопотребления и тому подобном исследовался КМОП-датчик изображения, содержащий схемы А/Ц (аналого-цифрового) преобразования. В качестве формата КМОП-датчика изображения имеется формат, называемый А/Ц преобразованием столбцов, предусматривающий схемы А/Ц преобразования для каждого столбца в расположении элементов изображения. Предлагались различные форматы А/Ц преобразования, чтобы использовать для А/Ц преобразования столбцов, и среди них известны форматы А/Ц преобразования комплексного типа, раскрытые в опубликованных заявках на патент Японии № 2002-232291 и № 2005-348325. Если преобразования выполняются в два этапа для битов старшего разряда и для битов младшего разряда, как в А/Ц преобразователе комплексного типа, раскрытом в опубликованной заявке на патент Японии № 2002-232291, тогда время преобразования становится пропорциональным 2×2N/2, и способ обладает особенностью, способной сократить время преобразования по сравнению, например, с форматом со сравнением входного сигнала с треугольной волной.

Формат А/Ц преобразования, раскрытый в опубликованной заявке на патент Японии № 2005-348325, выполняет А/Ц преобразование, удерживая сигнал от элемента изображения в запоминающем устройстве, с последующей зарядкой и разрядкой посредством постоянного сигнала. Поскольку формат А/Ц преобразования, раскрытый в опубликованной заявке на патент Японии № 2005-348325, также выполняет А/Ц преобразование в два этапа для битов старшего разряда и для битов младшего разряда, формат А/Ц преобразования может сократить время, необходимое для А/Ц преобразования по сравнению с временем формата преобразования со сравнением входного сигнала с треугольной волной.

Однако при использовании А/Ц преобразователя, раскрытого в опубликованной заявке на патент Японии № 2002-232291, для А/Ц преобразования столбцов, возникает следующая проблема. Если имеется несоответствие в соотношении величины изменения электрического заряда, удерживаемого в конденсаторе, за такт преобразования битов старшего разряда (единичная интегральная величина для преобразования битов старшего разряда) к величине изменения электрического заряда, удерживаемого в конденсаторе, за такт преобразования битов младшего разряда (единичная интегральная величина для преобразования битов младшего разряда), возникает дифференцированная линейная погрешность. Например, если А/Ц преобразование 12 битов выполняется поэтапно для цифр старшего разряда в размере 6 битов и для цифр младшего разряда в размере 6 битов, в идеале требуется, чтобы единичная интегральная величина для преобразования битов старшего разряда была в 64 раза больше, чем единичная интегральная величина для преобразования битов младшего разряда, но в реальной схеме возникает погрешность вследствие относительной точности элементов, составляющих схему, и тому подобного. На относительную точность элементов влияет, например, разброс, который случается при производстве элементов.

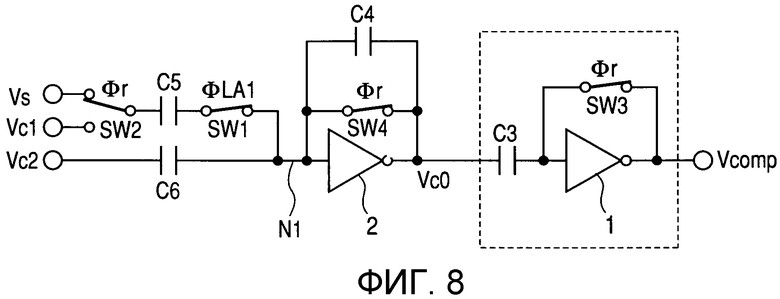

На Фиг. 8 приводится Фиг. 5 из опубликованной заявки на патент Японии № 2002-232291. Некоторые из позиционных обозначений удалены для упрощения. А/Ц преобразователь, продемонстрированный на Фиг. 8, усиливает сигнал Vc1, который является сигналом с изменяющейся ступенчатой волной, с коэффициентом усиления C5/C4 для преобразования битов старшего разряда, а с другой стороны, усиливает сигнал Vc2, который имеет тот же градиент, что и сигнал Vc1, и полярность, обратную полярности сигнала Vc1, с коэффициентом усиления C6/C4 для преобразования битов младшего разряда. Единичная интегральная величина для преобразования битов старшего разряда в C5/C6 раз больше, чем единичная интегральная величина для преобразования битов младшего разряда. Однако поскольку конденсаторные элементы C5 и C6 являются элементами, различающимися для каждого столбца, относительная точность конденсаторных элементов C5 и C6 является разной в каждом столбце. Таким образом, можно предположить, что значение C5/C6 немного отличается для каждого столбца. В частности, если горизонтальные размеры столбцов в расположении элементов изображения уменьшаются в связи с уменьшением размеров элементов изображения, то размеры конденсаторных элементов, которые можно реализовать в столбцах, то есть значения конденсаторов, становятся меньше, и, следовательно, относительная точность конденсаторных элементов в целом ухудшается. Если погрешность соотношения единичной интегральной величины для преобразования битов старшего разряда к единичной интегральной величине для преобразования битов младшего разряда между столбцами перестает быть пренебрежимо малой относительно заданной точности линейности, возникает необходимость хранения поправочного коэффициента в каждом столбце и выполнения корректирующих операций. Это приводит к проблеме, состоящей в том, что обработка корректировки линейности становится очень большой нагрузкой, особенно в том случае, когда количество битов преобразования возрастает.

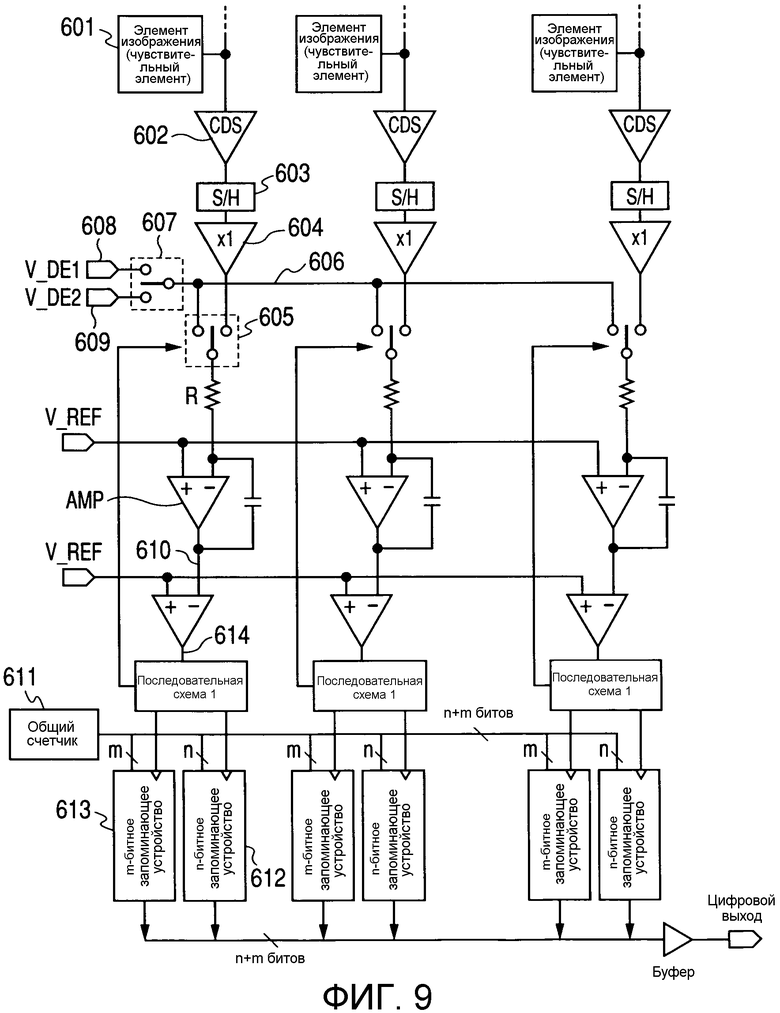

В то же время, Фиг. 9 является ссылкой на Фиг. 6 из опубликованной заявки на патент Японии № 2005-348325. Позиционные обозначения заново добавлены для описания. В конфигурации, изображенной на Фиг. 9, ток, обусловленный разностью потенциалов между постоянным напряжением V_DE1 или V_DE2 и электрическим потенциалом на инвертирующем входном конце (-) операционного усилителя Amp и величиной сопротивления R, протекает через сопротивление R. Электрический потенциал на инвертирующем входном конце операционного усилителя Amp в идеале становится равным электрическому потенциалу на его не-инвертирующем входном конце (+) вследствие его мнимого заземления. Однако в реальной схеме два входных конца операционного усилителя Amp имеют разный электрический потенциал, поскольку характеристики элементов, составляющих операционный усилитель Amp, не обязательно являются идеальными. Следовательно, эта разница проявляется как смещение. То есть, идеальное интегрирование не выполняется из-за смещения, вызванного элементами, составляющими операционный усилитель Amp.

Если разрешение А/Ц преобразователя невысоко, расхождение соотношения с его идеальным значением не оказывает существенного влияния. Однако если разрешение становится выше, расхождение с идеальным значением перестает быть пренебрежимо малым, и порождается проблема, которая состоит в том, что не могут быть получены точные результаты А/Ц преобразования.

Раскрытие Изобретения

Твердотельное устройство формирования изображения согласно настоящему изобретению обеспечивает твердотельное устройство формирования изображения, решающее вышеуказанные проблемы, и систему формирования изображения, использующую твердотельное устройство формирования изображения.

Твердотельное устройство формирования изображения в соответствии с одним аспектом настоящего изобретения представляет собой твердотельное устройство формирования изображения, которое содержит: область элементов изображения, включающую в себя множество элементов изображения, размещенных в матрице, причем каждый элемент изображения выводит аналоговый сигнал; множество схем А/Ц преобразования, каждая из которых размещается соответственно каждому столбцу из множества элементов изображения для А/Ц преобразования аналогового сигнала в цифровой сигнал, при этом твердотельное устройство формирования изображения содержит схему генерирования опорного сигнала для подачи, совместно на множество схем А/Ц преобразования по меньшей мере двух опорных сигналов, чьи уровни сигнала изменяются в разных направлениях электрического потенциала, и схема А/Ц преобразования содержит: усилитель; входной конденсатор, один конец которого принимает аналоговый сигнал и опорный сигнал, подаваемый от схемы генерирования опорного сигнала, а другой конец подключен к одному входному концу усилителя; конденсатор обратной связи, подключенный между одним входным концом и выходным концом усилителя; сравнивающее устройство для сравнения со сравниваемым уровнем выхода от выходного конца усилителя; и соединительный конденсатор, один конец которого подключен к выходному концу усилителя, а другой конец подключен к одному входному концу сравнивающего устройства.

Согласно настоящему изобретению точность линейности А/Ц преобразователя может быть повышена, и можно снизить ухудшение точности А/Ц преобразования для А/Ц преобразователя вследствие влияния смещения, даже если разрешение А/Ц преобразователя повышается.

Дополнительные признаки настоящего изобретения станут очевидными благодаря последующему описанию иллюстративных вариантов осуществления со ссылкой на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

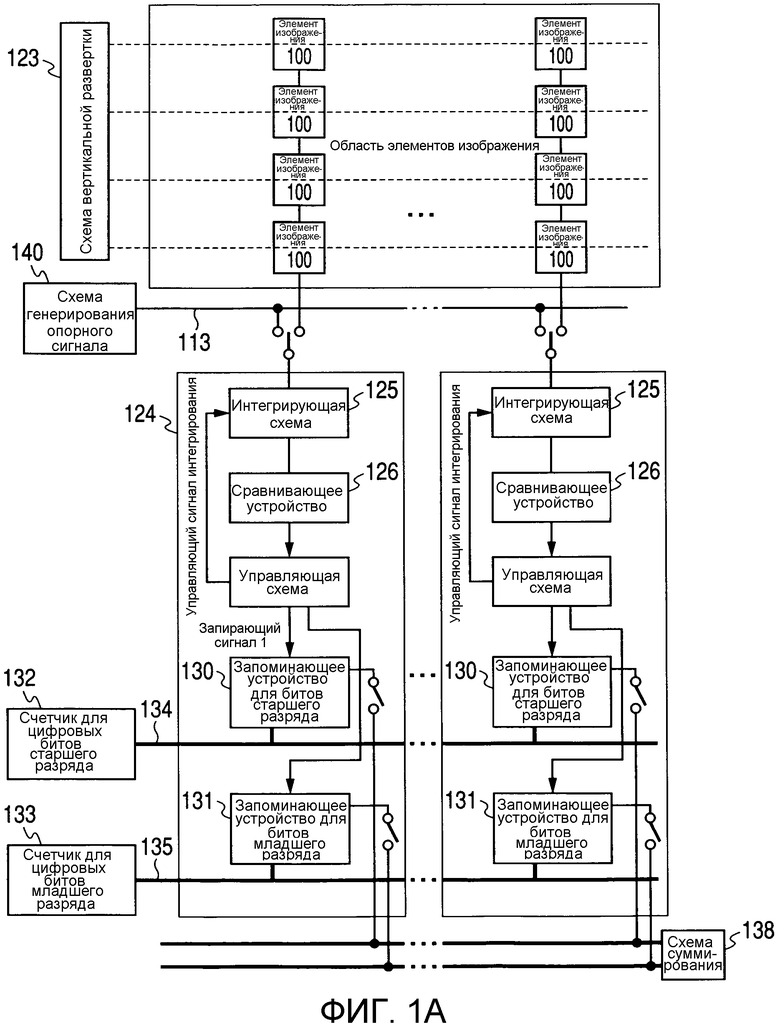

Фиг. 1A является функциональной схемой твердотельного устройства формирования изображения согласно первому варианту осуществления настоящего изобретения.

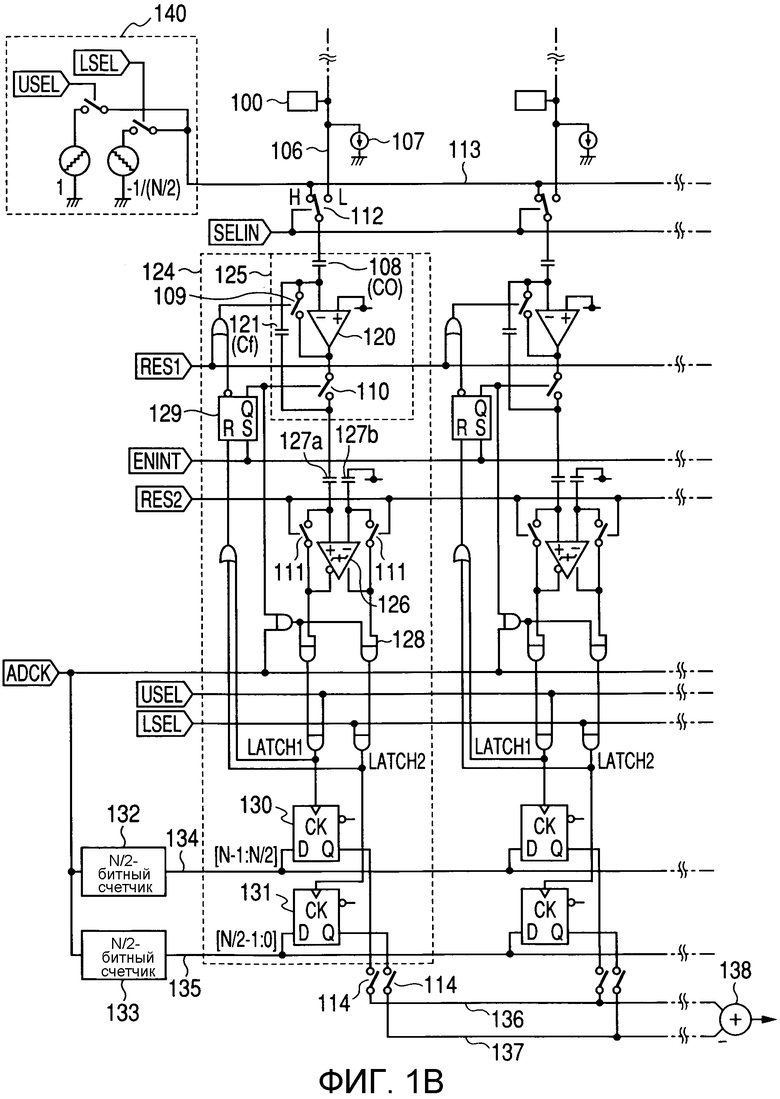

Фиг. 1B является схематическим представлением, демонстрирующим часть эквивалентной схемы твердотельного формирования изображения.

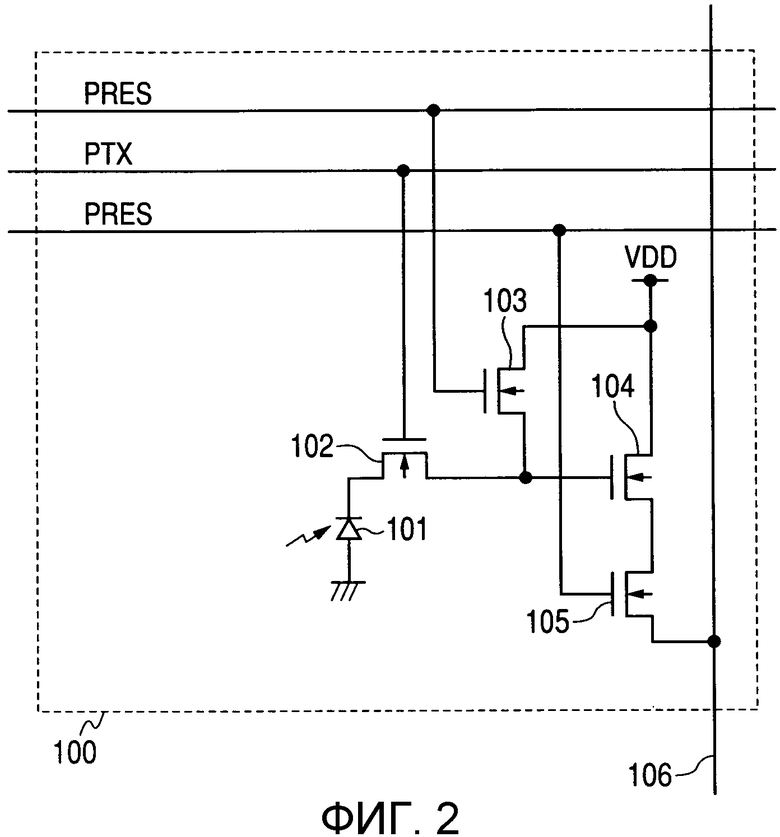

Фиг. 2 является схематическим представлением эквивалентной схемы единичного элемента изображения твердотельного устройства формирования изображения согласно первому и второму вариантам осуществления настоящего изобретения.

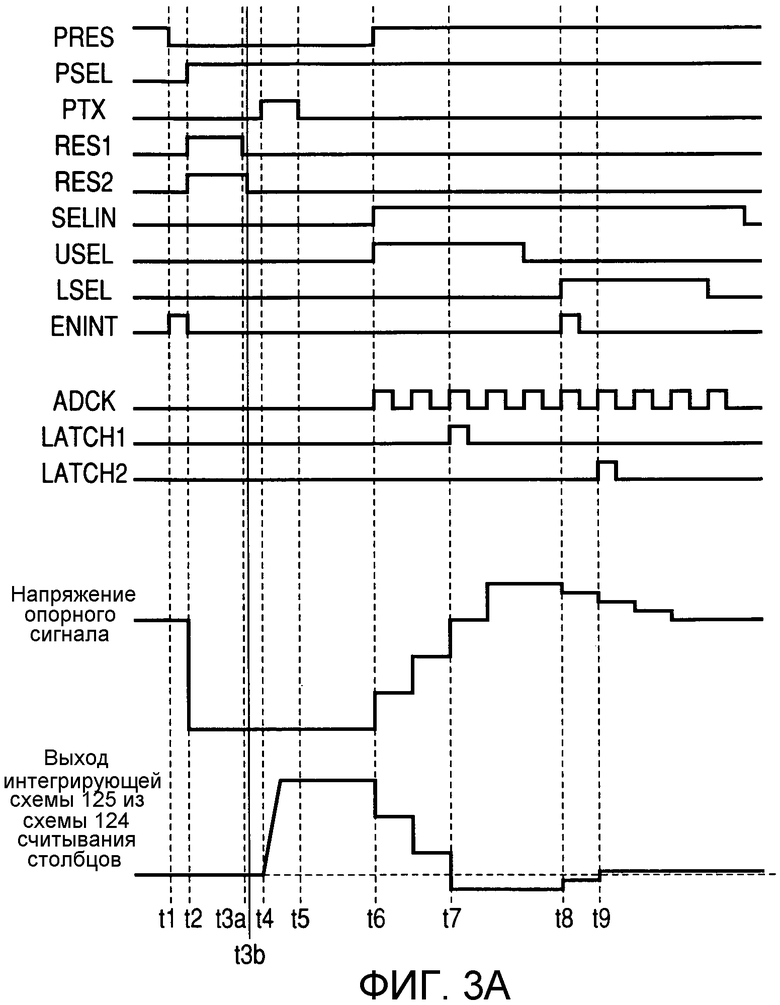

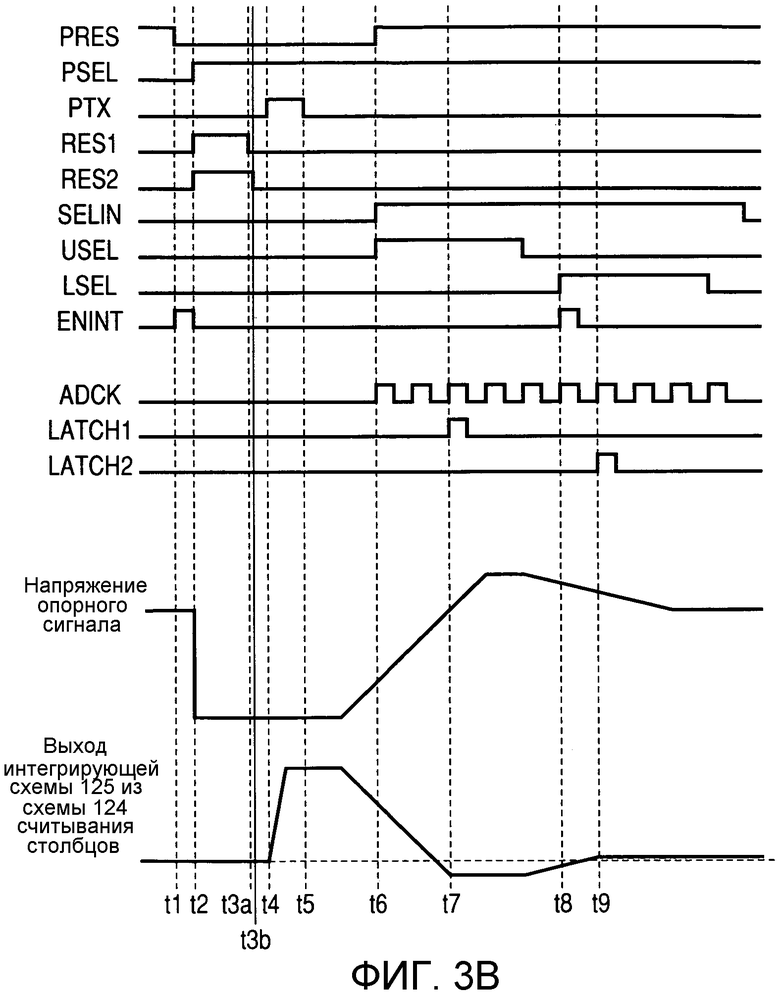

Фиг. 3A и 3B являются временными диаграммами твердотельного устройства формирования изображения согласно первому варианту осуществления настоящего изобретения.

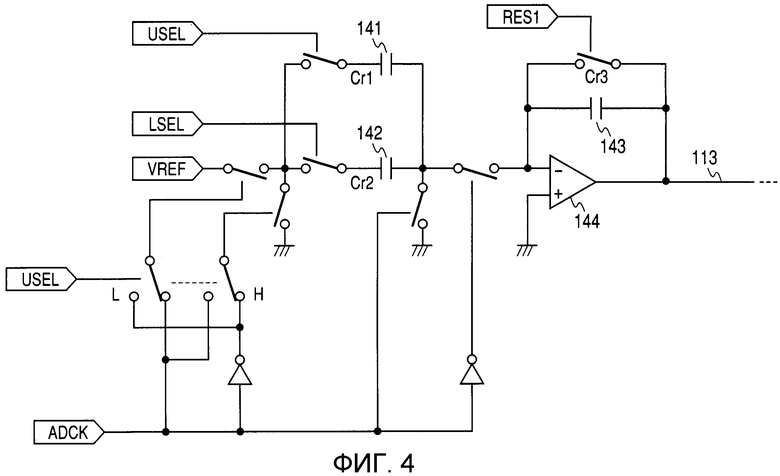

Фиг. 4 является схематическим представлением эквивалентной схемы для схемы генерирования опорного сигнала согласно первому варианту осуществления настоящего изобретения.

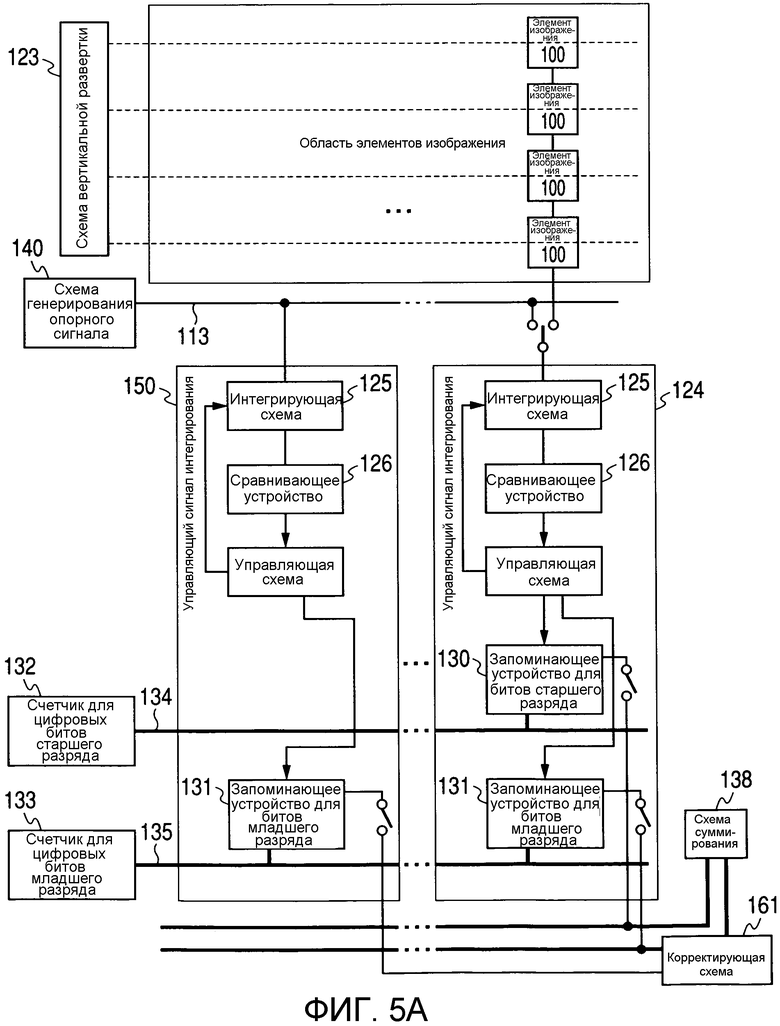

Фиг. 5A является функциональной схемой твердотельного устройства формирования изображения согласно второму варианту осуществления настоящего изобретения.

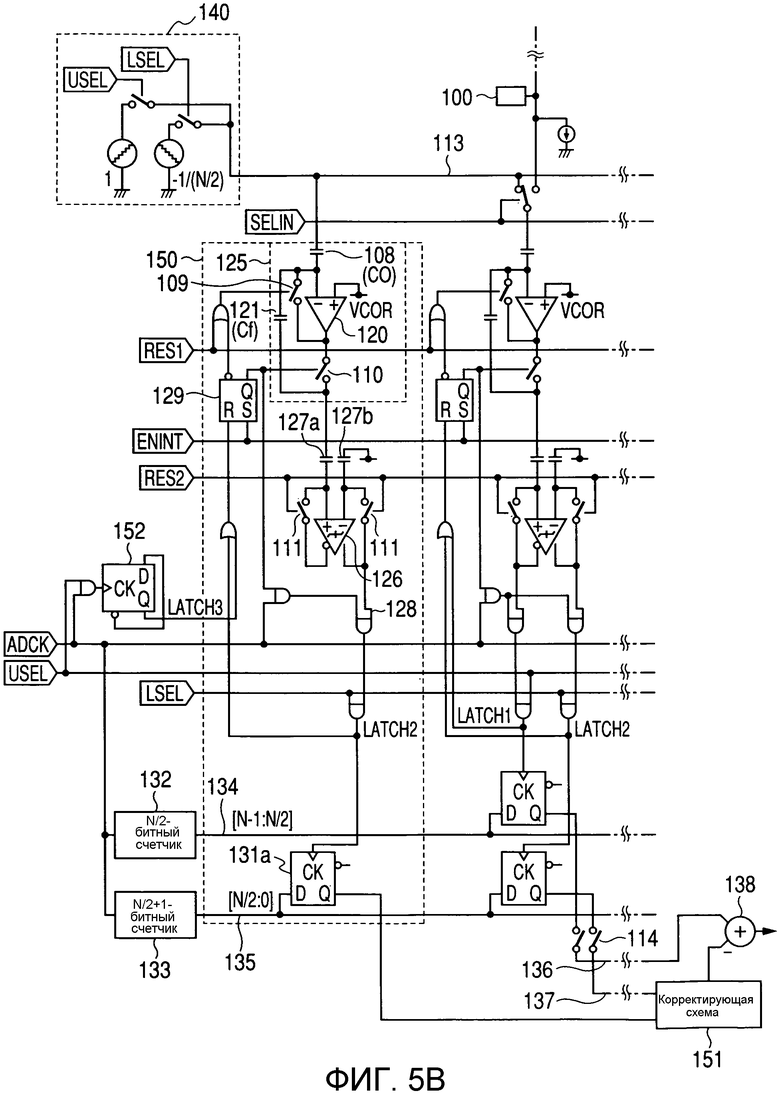

Фиг. 5B является схематическим представлением, демонстрирующим часть эквивалентной схемы твердотельного устройства формирования изображения.

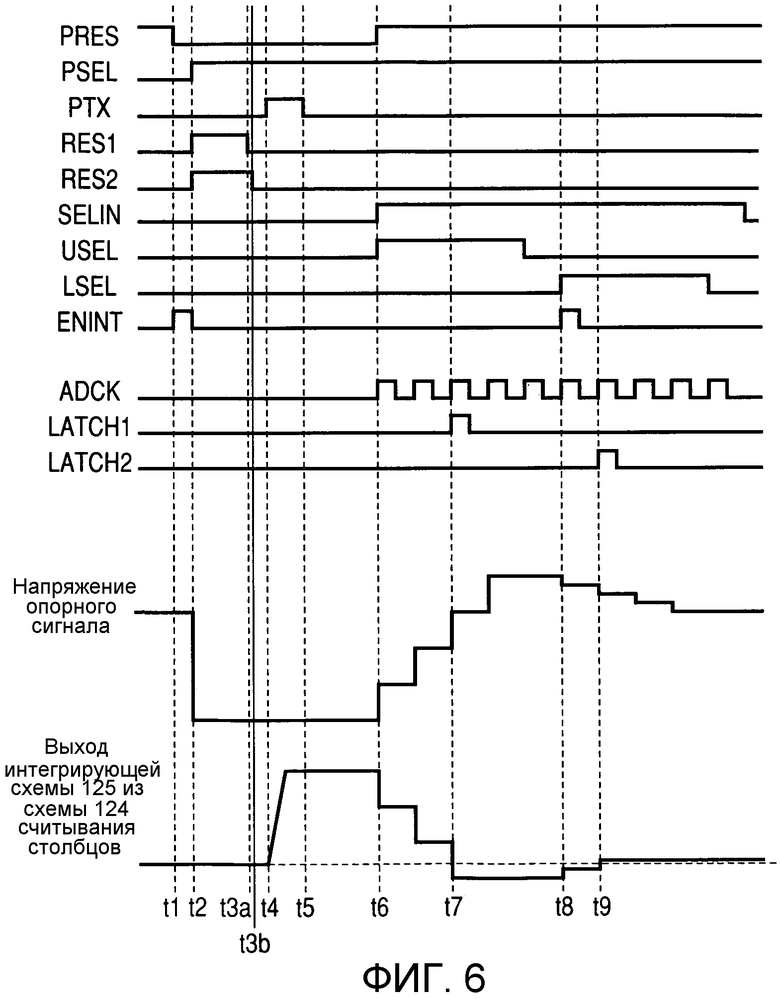

Фиг. 6 является временной диаграммой твердотельного устройства формирования изображения согласно второму варианту осуществления настоящего изобретения.

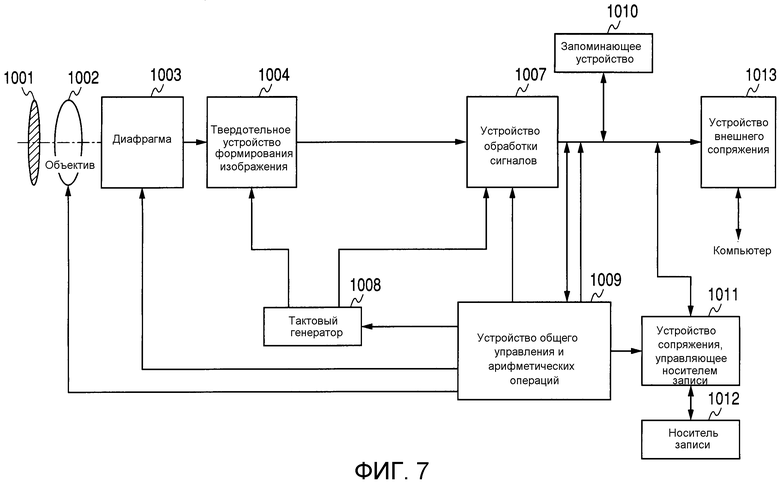

Фиг. 7 является схематическим представлением, демонстрирующим пример конфигурации системы формирования изображения согласно третьему варианту осуществления.

Фиг. 8 является принципиальной схемой, демонстрирующей модуль А/Ц преобразования согласно опубликованной заявке на патент Японии № 2002-232291.

Фиг. 9 является схематическим представлением, цитирующим Фиг. 6 из опубликованной заявки на патент Японии № 2005-348325.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

(Первый вариант осуществления)

Твердотельное устройство формирования изображения согласно первому варианту осуществления, к которому может применяться настоящее изобретение, будет описано со ссылкой на прилагаемые чертежи.

Сначала описываются основные принципы твердотельного устройства формирования изображения согласно настоящему варианту осуществления, со ссылкой на функциональную схему, изображенную на Фиг. 1A. Твердотельное устройство 1 формирования изображения включает в себя область элементов изображения, в которой множество элементов 100 изображения размещаются в матрице, и каждый элемент 100 изображения имеет конфигурацию, проиллюстрированную посредством эквивалентной схемой на Фиг. 2. Выходные сигналы от элементов 100 изображения являются входными для схем 124 считывания столбцов, предусмотренных в соответствующих столбцах, как аналоговые сигналы через вертикальные выходные линии 106. Каждая из множества схем 124 считывания столбцов включает в себя схему А/Ц преобразования, включающую в себя интегрирующую схему 125 и сравнивающее устройство 126, а также запоминающие устройства 130 и 131, хранящие результаты А/Ц преобразования битов старшего разряда и результаты А/Ц преобразования битов младшего разряда соответственно. Интегрирующая схема 125 включает в себя входной конденсатор 108, переключатель 109, усилитель 120, конденсатор 121 обратной связи и переключатель 110. Один конец входного конденсатора 108 принимает аналоговый сигнал от элемента изображения и опорный сигнал от схемы 140 генерирования опорного сигнала, которая будет описан позже, а другой конец входного конденсатора 108 подключается к входному концу усилителя 120. Результаты А/Ц преобразования, хранящиеся в запоминающем устройстве 130 для битов старшего разряда и в запоминающем устройстве 131 для битов младшего разряда, выводятся на выходные линии 136 и 137 битов соответственно через переключатели 114 выбора столбца и выводятся будучи синтезированными в N-битный цифровой сигнал при помощи схемы 138 суммирования, которая является устройством сложения. Хотя в данном документе используется схема 138 суммирования, схема вычитания может использоваться вместо схемы 138 суммирования, в зависимости от полярностей сигналов.

Фиг. 2 показывает пример каждого из элементов 100 изображения в виде эквивалентной схемы. Ссылочная позиция 101 указывает на фотодиод, который выполняет фотоэлектрическое преобразование соответственно падающему свету для накапливания полученного электрического заряда, и катод фотодиода 101 подключается к передаточному МОП-транзистору 102. Если передаточный МОП-транзистор 102 принимает сигнал PTX высокого уровня, то электрический заряд, накопленный в фотодиоде 101, переносится на узел, к которому подключен затвор усиливающего МОП-транзистора 104. Если переключающий МОП-транзистор 105 переводится в свое проводящее состояние по сигналу PSEL, то усиливающий МОП-транзистор 104 формирует схему истокового повторителя с источником 107 постоянного тока, предусмотренным для каждой из вертикальных выходных линий 106. Таким образом, электрический потенциал, соответствующий электрическому потенциалу на затворе усиливающего МОП-транзистора 104, появляется на вертикальной выходной линии 106 как сигнал. Позиционное обозначение 103 указывает на возвратный МОП-транзистор. Если возвратный МОП-транзистор 103 переводится в его проводящее состояние по сигналу PRES, то возвратный МОП-транзистор 103 возвращает узлу, к которому подключен затвор усиливающего МОП-транзистора 104, напряжение VDD источника питания.

Работа твердотельного устройства формирования изображения согласно настоящему варианту осуществления подробно описывается со ссылкой на схематическое представление эквивалентной схемы, изображенное на Фиг. 1B, и на временную диаграмму, изображенную на Фиг. 3A. Ссылочная позиция каждого сигнального импульса соответствует ссылочной позиции каждого конца на Фиг. 1B или Фиг. 2. Помимо этого, Фиг. 3A и 3B демонстрируют опорный сигнал, который подается на проводку 113 подачи опорного сигнала как пилообразное напряжение сигнала. Кроме того, продемонстрирован также выход интегрирующей схемы 125, включенной в состав каждой схемы 124 считывания столбцов. Попутно предполагается, что переключатели, продемонстрированные на Фиг. 1B и 2, включаются по входному сигналу высокого уровня, то есть, приводятся в свои проводящие состояния, и что переключатели выключаются по входному сигналу низкого уровня, то есть, приводятся в свои непроводящие состояния. Помимо этого, что касается избирательных переключателей 112 на Фиг. 1B, цепи, которые подключаются по высокому уровню или низкому уровню импульса, обозначены через "H" или "L", соответственно.

Предполагается, что предварительно заданное время экспозиции истекло до операции считывания сигнала элемента изображения, и что электрический заряд, полученный в результате фотоэлектрического преобразования, накапливается в фотодиоде 101. Кроме того, предполагается, что входные избирательные переключатели 112 подключаются между усиливающим МОП-транзистором 104 и вертикальными выходными линиями 106. Импульсы PRES, PTX и PSEL подаются от схемы 123 вертикальной развертки на элементы 100 изображения, в этом описании.

Сначала, в момент t1 времени, импульс PRES возврата элемента изображения переходит с высокого уровня на низкий уровень, тем самым, отпуская затвор усиливающего МОП-транзистора 104 в исходное состояние. В это время напряжение сразу после завершения возврата, то есть напряжение, соответствующее темновому состоянию, удерживается в конденсаторе (в дальнейшем в этом документе именуется CFD) плавающей диффузионной области (в дальнейшем именуется FD-область), подключенном к электроду затвора. Помимо этого, в момент t1 времени, пусковой сигнал ENIT интегрирования переходит на высокий уровень, тем самым устанавливая RS-триггер 129.

Далее, в момент t2 времени, когда импульс PSEL выбора строки переходит на высокий уровень, темновой выход, соответствующий темновому времени, который удерживается в плавающем диффузионном состоянии, появляется на вертикальной выходной линии 106, благодаря схеме истокового повторителя, сформированной усиливающим МОП-транзистором 104 и источником 107 постоянного тока. С другой стороны, когда импульс RES1 переходит на высокий уровень в момент t2 времени, переключатель 109 включается, и, следовательно, операционный усилитель 120 в каждой из интегрирующих схем 125 переводится в свое состояние повторителя напряжения. Хотя выход операционного усилителя 120 в это время включает в себя свою собственную составляющую смещения, соответственно, выход становится практически таким же, как опорное напряжение VC0R.

Когда импульс RES1 переходит с высокого уровня на низкий уровень в момент t3a времени, переключатель 109 переводится из состояния "включено" в состояние "выключено", и темновой выход на вертикальной выходной линии 106 отсекается входным конденсатором 108.

Импульс RES2 переходит с высокого уровня на низкий уровень в момент t3b времени, сразу после изменения импульса RES1, и переключатель 111 выключается. Затем, уровень возврата, включающий в себя составляющую темнового выхода и составляющую смещения операционного усилителя 120, удерживается в соединительном конденсаторе 127a. Так как электрический потенциал на положительном входном конце (+) сравнивающего устройства 126 равен электрическому потенциалу отрицательного входного конца (-) вследствие мнимого заземления, можно провести сравнение между сигналом, подаваемым на вход положительного входного конца, и сравниваемым уровнем, то есть сигналом, который подается на вход отрицательного конца через соединительный конденсатор 127b. Если разностное напряжение между сигналом, подаваемым на вход положительного входного конца, и сигналом, подаваемым на вход отрицательного входного конца, является положительным, то сравнивающее устройство 126 работает таким образом, чтобы выводить высокий уровень от положительного выходного конца и низкий уровень от отрицательного выходного конца. С другой стороны, если разностное напряжение является отрицательным, сравнивающее устройство 126 работает таким образом, чтобы выводить высокий уровень от отрицательного выходного конца и низкий уровень от положительного выходного конца.

Далее, импульс PTX передачи переходит на высокий уровень на период от момента t4 времени до момента t5 времени, тем самым, включая передаточный МОП-транзистор 102, и электрический заряд, накопленный в фотодиоде 101, переносится на узел затвора усиливающего МОП-транзистора 104. Электрическим зарядом, который должен переноситься, служат электроны, в этом описании. Если абсолютная величина перенесенного электрического заряда обозначается через Q, то потенциал затвора усиливающего МОП-транзистора 104 понижается на Q/CFD, и электрический потенциал вертикальной выходной линии 106 также изменяется в соответствии с понижением потенциала затвора. Электрический потенциал вертикальной выходной линии в это время именуется выходом освещенного состояния. Если коэффициент усиления схемы истокового повторителя обозначается через Gsf, то измененная величина ΔVv1 электрического потенциала Vv1 вертикальной выходной линии 106 от темнового выхода может быть выражена следующим уравнением.

Изменение потенциала вертикальной выходной линии 106 усиливается схемой инвертирующего усилителя, включающей в себя операционный усилитель 120, входной конденсатор 108 и конденсатор 121 обратной связи, и сигнал Vs, выраженный следующим уравнением, удерживается в конденсаторе 121 обратной связи.

В данном случае C0 обозначает величину емкости входного конденсатора 108, а Cf обозначает величину емкости конденсатора 121 обратной связи. Помимо этого, коэффициент усиления схемы инвертирующего усилителя равен - C0/Cf.

Затем, в момент t6 времени, операция вступает в этап выполнения А/Ц преобразования сигнала Vs. Сначала входной избирательный переключатель 112 переключается на сторону проводки 113 подачи опорного сигнала. Скачкообразно нарастающий сигнал для преобразования битов старшего разряда, который является опорным сигналом, подается от схемы 140 генерирования опорного сигнала на проводку 113 подачи опорного сигнала. Несмотря на то, что в данном случае в качестве нарастающего сигнала используется сигнал, имеющий скачкообразное и монотонное изменение уровня сигнала, синхронно с сигналом ADCK, который будет описан позже, в качестве нарастающего сигнала может использоваться сигнал, имеющий не скачкообразное, а гладкое и монотонное изменение уровня сигнала, например. Попутно, монотонное изменение означает, например, что уровень сигнала не изменяется в направлении понижения при скачкообразном повышении уровня. То есть, когда сигнал изменяется монотонно, он может включать в себя период, в котором уровень не изменяется со временем. Схема 140 генерирования опорного сигнала включает в себя переключатели и конденсаторное интегрирующее устройство, как продемонстрировано на Фиг. 4. После преобразования битов старшего разряда импульс USEL становится импульсом высокого уровня, а импульс LSEL становится импульсом низкого уровня, тем самым, генерируя нарастающий сигнал, увеличивающийся на (Cr1/Cr3)×VREF за каждый период сигнала ADCK. С другой стороны, после преобразования битов младшего разряда импульс LSEL становится импульсом высокого уровня, а импульс USEL становится импульсом низкого уровня, тем самым, генерируя спадающий сигнал, который является другим опорным сигналом, уменьшающийся на (Cr2/Cr3)×VREF. То есть, направления, в которых изменяются уровни спадающего сигнала и нарастающего сигнала, отличаются друг от друга. Помимо этого, электрический заряд конденсатора Cr3 может сбрасываться для инициализации, применяя высокий уровень импульса RES1. Несмотря на то, что в данном случае демонстрируется вариант подачи на вход такого же импульса, как импульс RES1, подаваемый на схему 124 считывания столбцов, импульс, отличный от подаваемого на вход схемы 124 считывания столбцов, может подаваться на вход схемы 140 генерирования опорного сигнала. Несмотря на то, что в данном случае в качестве спадающего сигнала используется сигнал, имеющий скачкообразное и монотонное изменение уровня сигнала, синхронно с сигналом ADCK, в качестве нарастающего сигнала может использоваться сигнал, имеющий не скачкообразное, а гладкое и монотонное изменение уровня сигнала, например. Попутно, монотонное изменение означает, например, что при скачкообразном повышении уровня, уровень не изменяется в направлении понижения. То есть, может присутствовать период, в течение которого уровень не изменяется со временем.

Когда нарастающий сигнал для преобразования битов старшего разряда подается на вход интегрирующей схемы 125, начиная с момента t6 времени, начинается интегрирование. Нарастающий сигнал для преобразования битов старшего разряда инверсно усиливается с коэффициентом усиления, равным - (C0/Cf), и в результате выход интегрирующей схемы 125 понижается на (C0/Cf)×(Cr1/Cr3)×VREF за каждый такт сигнала ADCK. Выход интегральной схемы 125 подается на вход положительного входного конца сравнивающего устройства 126 через соединительный конденсатор 127a. Поскольку уровень возврата, отобранный в момент t3b времени, удерживается в соединительном конденсаторе 127a, только измененный уровень, полученный путем установления уровня возврата, исходя из выхода интегрирующей схемы 125, подается на вход сравнивающего устройства 126. То есть, даже если элементы, составляющие интегрирующую схему 125, не имеют идеальных характеристик, составляющие смещения интегрирующей схемы 125 не подаются на вход сравнивающего устройства 126, и, следовательно, может быть выполнено А/Ц преобразование с высокой точностью. Измененный уровень сигнала, подаваемого на вход положительного входного конца сравнивающего устройства 126 через соединительный конденсатор 127a, сравнивается с опорным напряжением, подаваемым на вход отрицательного входного конца сравнивающего устройства 126 через соединительный конденсатор 127b. Далее, запирающий сигнал latch1 выводится в момент t7 времени, когда выход интегральной схемы 125 становится меньше уровня возврата. Запирающий сигнал latch1 передается в запоминающее устройство 130 для битов старшего разряда, и значение счетчика, подаваемое от счетчика 132 для битов старшего разряда на запоминающее устройство 130 для битов старшего разряда в это время, помещается в запоминающее устройство 130 для битов старшего разряда. В то же время, запирающий сигнал latch1 подается также на конец сброса RS-триггера 129, чтобы остановить операцию интегрирования интегрирующей схемы 125. Предполагая, что значение счетчика в это время равно CU, выход понижается на CU×(C0/Cf)×(Cr1/Cr3)×VREF в ходе операции интегрирования, и вызывается состояние, в котором CU×(C0/Cf)×(Cr1/Cr3)×VREF-Vs удерживается в конденсаторе 121 обратной связи как остаточное напряжение. Момент времени, когда операция интегрирования прекращается, отличается в каждом столбце в зависимости от сигнала Vs элемента изображения. Импульс USEL обращается в импульс низкого уровня после окончания операций интегрирования в отношении всех столбцов, и счетчик для битов старшего разряда останавливается.

Далее, в момент t8 времени, импульс LSEL переходит на высокий уровень, а импульс USEL переходит на низкий уровень, и начинается этап выполнения А/Ц преобразования битов младшего разряда. Спадающий сигнал для преобразования битов младшего разряда имеет полярность, обратную полярности нарастающего сигнала для выполнения преобразования цифровых битов старшего разряда, и уровень, уменьшающийся на (Cr2/Cr3)×VREF, подается от схемы 140 генерирования опорного сигнала на интегрирующую схему 125. Пусковой сигнал ENINT интегрирования снова подается на вход, и начинается операция интегрирования в интегрирующей схеме 125. Спадающий сигнал для преобразований битов младшего разряда инверсно усиливается с коэффициентом усиления - (C0/Cf), а выход интегрирующей схемы 125 повышается на (C0/Cf)×(Cr2/Cr3)×VREF за каждый такт сигнала ADCK. В сравнивающем устройстве 126 измененный уровень выхода интегрирующей схемы 125 вследствие уровня возврата, удерживаемого в соединительном конденсаторе 127a, сравнивается с опорным уровнем, подаваемым на вход сравнивающего устройства 126 через соединительный конденсатор 127b. Затем, в момент t9 времени, в который выход интегрирующей схемы 125 становится больше опорного напряжения, выводится запирающий сигнал latch2. Запирающий сигнал latch2 передается в запоминающее устройство 131 для битов младшего разряда, и значение счетчика, подаваемое от счетчика 133 для битов младшего разряда на запоминающее устройство 131 для битов младшего разряда в это время, помещается в запоминающее устройство 131 для битов младшего разряда. В то же время запирающий сигнал latch2 подается также на конец сброса RS-триггера 129, чтобы остановить операцию интегрирования интегрирующей схемы 125. Остановка операции интегрирования не является необходимой. Помимо этого, в данной временной точке остаток стал меньше единичной интегральной величины для преобразования битов младшего разряда, то есть меньше интегральной величины, соответствующей 1 младшему значащему биту.

Соотношение единичной интегральной величины для преобразования битов старшего разряда к единичной интегральной величине для преобразования битов младшего разряда в идеале должно быть 2N/2 в случае выполнения А/Ц преобразования N-битных данных в два этапа для цифр старшего разряда в размере N/2 битов и для цифр младшего разряда в размере N/2 битов. С другой стороны, соотношение единичной интегральной величины для преобразования битов старшего разряда к единичной интегральной величине для преобразования битов младшего разряда в схеме согласно настоящему варианту осуществления определяется следующим уравнением.

То есть, независимо от значений конденсаторов C0 и C1, предусмотренных в каждом столбце, соотношение определяется только соотношением между величинами Cr1 и Cr2 емкости в схеме 140 генерирования опорного сигнала. Следовательно, можно снизить погрешности между столбцами, которые обычно создавали проблему. Существует общая тенденция, что относительная точность конденсаторов улучшается по мере того, как размеры конденсаторных элементов становятся больше, то есть величины емкости становятся больше. Конденсаторы C0 и Cf предусмотрены в схеме 124 считывания столбцов и их размеры ограничиваются шагом элементов изображения, величины емкости конденсаторов Cr1 и Cr2, предусмотренных в схеме 140 генерирования опорного сигнала, могут быть легко увеличены и полезны в том смысле, что это способно улучшить точность А/Ц преобразования.

Помимо этого, если разрешение N для А/Ц преобразования относительно мало, это к тому же позволяет избавиться от исполнения коррекции, увеличивая конденсаторы Cr1 и Cr2. В этом случае, преобразованное N-битовое цифровое значение может быть получено путем сложения вместе результатов А/Ц преобразования, сохраненных в запоминающем устройстве 130 для битов старшего разряда и в запоминающем устройстве 131 для битов младшего разряда, при помощи схемы 138 суммирования. Если счетная схема 133 для битов младшего разряда является суммирующим счетчиком, то выполняется обработка вычитания. Как вариант, счетная схема 133 для битов младшего разряда может иметь конфигурацию вычитающего счетчика для выполнения обработки сложения (или вычитания) посредством схемы 138 сложения (или вычитания).

Помимо этого, особенность, характерная для настоящего варианта осуществления, должна также усиливать сигнал Vs элемента изображения с коэффициентом усиления C0/Cf при помощи интегрирующей схемы 125 в схеме 124 считывания столбцов, и, следовательно, влияние соотношения C0/Cf не проявляется в конечном результате после А/Ц преобразования. То есть, может быть получен превосходный сигнал изображения, имеющий небольшие отклонения коэффициента усиления между столбцами.

Попутно, хотя счетные схемы 132 и 133 обычно используются для множества столбцов в настоящем варианте осуществления, счетные схемы 132 и 133 могут быть независимо предоставлены для каждого столбца.

Например, если твердотельное устройство формирования изображения реализуется таким образом, что если обычный сигнал ADCK подается на тактовый вход счетной схемы 132 для битов старшего разряда во время преобразования битов старшего разряда и если сигнал переноса счетной схемы 133 для битов младшего разряда подается на тактовый вход во время преобразования битов младшего разряда, то может выполняться вычитание остатка.

Несмотря на то, что сигнал, изменяющийся скачкообразно синхронно с сигналом ADCK, подается на вход как опорный сигнал в варианте, изображенном на Фиг. 3A, опорный сигнал может быть сигналом, изменяющимся наклонно, как продемонстрировано на Фиг. 3B, например.

(Второй Вариант осуществления)

Твердотельное устройство формирования изображения согласно второму варианту осуществления, к которому может применяться настоящее изобретение, будет описано со ссылкой на Фиг. 5A и 5B. Твердотельное устройство формирования изображения в настоящем варианте осуществления применимо для формата А/Ц преобразования столбцов для относительно высокого разрешения. Фиг. 5A является функциональной схемой, демонстрирующей основные принципы твердотельного устройства формирования изображения, а Фиг. 5B демонстрирует часть эквивалентной схемы твердотельного устройства формирования изображения. Второй вариант осуществления отличается от первого варианта осуществления тем, что он дополнительно содержит измерительную схему 150 для измерения соотношения единичной интегральной величины для временного периода преобразования битов старшего разряда к единичной интегральной величине для временного периода преобразования битов младшего разряда, каковое соотношение определяется схемой 140 генерирования опорного сигнала, и что он дополнительно содержит корректирующую схему 151 для исполнения коррекции на основе измеренного результата. Кроме того, запоминающее устройство 131a для битов младшего разряда изменяется от N/2 битов в схеме 124 считывания столбцов в первом варианте осуществления до (N/2)+1 битов, и добавляется избыточный бит. Измерительная схема 150 имеет конфигурацию, аналогичную схеме 124 считывания столбцов для считывания сигнала элемента изображения, такая схема 124 была описана по отношению к первому варианту осуществления, но измерительная схема 150 выполняется без входных избирательных переключателей 112 и с возможностью приема только опорного сигнала. Помимо этого, измерительная схема 150 исключает запоминающее устройство 130 для битов старшего разряда. Кроме того, измерительная схема 150 не включает в себя схему для генерирования запирающего сигнала latch1, но включает в себя по-новому добавленный однобитный счетчик 152 для генерирования запирающего сигнала latch3. Попутно, описание будет основываться на предположении, что конфигурация элемента изображения является той же, что и в первом варианте осуществления.

Фиг. 6 демонстрирует временную диаграмму работы твердотельного устройства формирования изображения, включающего в себя измерительную схему 150. Измерительная схема 150 в настоящем варианте осуществления выполняет измерение параллельно с работой схемы 124 считывания столбцов для считывания обычного сигнала элемента изображения. В период считывания сигнала элемента изображения от момента t1 времени до момента t6 времени измерительная схема 150 выполняет только операцию возврата для интегрирующей схемы 125 на основании импульса RES1 и выборку уровня возврата при помощи сравнивающего устройства 126 на основании импульса RES2. В момент t6 времени на вход подается опорный сигнал для преобразования битов старшего разряда, и начинается интегрирование, подобно схеме 124 считывания столбцов, но операция интегрирования останавливается однобитным счетчиком 152 в момент t10 времени после одного такта. Следовательно, электрический заряд, точно равный единичной интегральной величине для преобразования битов старшего разряда, удерживается в конденсаторе 121 обратной связи.

Далее, единичная интегральная величина для преобразования битов старшего разряда, интегрированная на этапе преобразования битов младшего разряда, каковой этап начинается с момента t8 времени, подвергается А/Ц преобразованию. В рамках подготовки к варианту, когда единичная интегральная величина во временном периоде преобразования битов старшего разряда превышает (N/2)×LSB (младший значащий бит), что является идеальным значением, запоминающее устройство 131a для битов младшего разряда изменяется, чтобы быть (N/2+1)-битным, включающим в себя избыточный бит, добавленный к N/2 битам запоминающего устройства 131 для битов младшего разряда в схеме 124 считывания столбцов.

Результат А/Ц преобразования записывается в запоминающее устройство 131a для битов младшего разряда в момент t9 времени, в который запирающий сигнал latch2 выводится, а затем подается на вход корректирующей схемы 151. Результат А/Ц преобразования битов младшего разряда от схемы 124 считывания столбцов подается на вход корректирующей схемы 151, и выполняется его корректировка на основе измеренного результата от измерительной схемы 150. После корректировки результат А/Ц преобразования битов младшего разряда синтезируется с результатом А/Ц преобразования битов старшего разряда в схеме 138 суммирования, и становится выходом А/Ц преобразования, то есть цифровым выходом.

Описаны особенности, характерные для настоящего варианта осуществления. В настоящем варианте осуществления измерительная схема 150 измеряет погрешность соотношения интегральной величины для преобразования битов старшего разряда к интегральной величине для преобразования битов младшего разряда, каковая погрешность генерируется схемой 140 генерирования опорного сигнала. Корректирующая схема 151 корректирует результат А/Ц преобразования, тем самым, давая возможность получить выход А/Ц преобразования, имеющий более высокую точность линейности.

Помимо этого, в твердотельном устройстве формирования изображения настоящего варианта осуществления период, в котором схема 124 считывания столбцов выполняет А/Ц преобразование, и период измерения, в котором измерительная схема 150 выполняет измерение, перекрывают друг друга. Следовательно, например, если соотношение единичной интегральной величины при преобразовании битов старшего разряда к единичной интегральной величине для преобразования битов младшего разряда изменяется в зависимости от температуры, то влияние, возникающее в зависимости на температуры, может быть последовательно скорректировано. Следовательно, А/Ц преобразование может выполняться с высокой точностью устойчиво к изменениям окружающей среды. Попутно, измерение соотношения интегральной величины для преобразования битов старшего разряда к интегральной величине для преобразования битов младшего разряда может, конечно, выполняться сразу после включения питания или на раннем этапе в начале фотосъемки, а также это соотношение может измеряться посредством удлинения времени интегрирования на 2 такта или больше.

Попутно, хотя в настоящем варианте осуществления выполняется коррекция цифрового сигнала от схемы 124 считывания столбцов, можно также выполнить коррекцию схемы 140 генерирования опорного сигнала. Например, в схеме 140 генерирования опорного сигнала, сконфигурированной, как продемонстрировано на Фиг. 4, посредством реализации конденсаторной матрицы, выполненной с возможностью тонкой регулировки значения конденсатора Cr2 или Cr1, и управления их подключением, может корректироваться соотношение единичной интегральной величины для преобразования битов старшего разряда к единичной интегральной величине для преобразования битов младшего разряда.

Помимо этого, в примерах конфигурации, продемонстрированных на Фиг. 1B и 5, соединительный конденсатор 127b подключается к отрицательному входному концу сравнивающего устройства 126. Этот соединительный конденсатор 127b имеет величину емкости, равную величине емкости соединительного конденсатора 127a, и предназначен для регулирования симметричности между отрицательным входным концом и положительным входным концом. Следовательно, если нет существенного требования симметричности, соединительный конденсатор 127b может быть опущен.

Несмотря на то, что в данном документе в качестве примера описывался скачкообразно изменяющийся опорный сигнал, опорный сигнал может быть сигналом, изменяющимся наклонно, аналогично первому варианту осуществления.

(Третий Вариант осуществления)

Фиг. 7 является схематическим представлением, демонстрирующим конфигурацию системы 1000 формирования изображения, использующей твердотельное устройство формирования изображения каждого из вышеупомянутых вариантов осуществления, к которому применяется настоящее изобретение. 1001 обозначает экран, используемый в качестве защиты объектива, и этот экран служит также основным переключателем, и 1002 обозначает объектив, который является оптической системой для предоставления оптического изображения объекта на твердотельное устройство 1004 формирования изображения. Количество света, проходящего через объектив 1002, может изменяться при помощи диафрагмы 1003. Твердотельное устройство 1004 формирования изображения (соответствующее твердотельному устройству формирования изображения, описанному в каждом из вышеупомянутых вариантов осуществления) преобразует оптическое изображение, сформированное объективом 1002, в данные изображения. Устройство 1007 обработки сигналов выполняет различные коррекции данных изображения на выходе твердотельного устройства 1004 формирования изображения и сжатие данных. Тактовый генератор 1008 выводит различные тактовые сигналы на устройство 1007 обработки сигналов. Попутно, каждая из схем 1007 и 1008 может формироваться на том же кристалле, что и твердотельное устройство 1004 формирования изображения. Система 1000 формирования изображения включает в себя устройство 1009 общего управления и арифметических операций для управления различными операциями и системой 1000 формирования изображения в целом, запоминающее устройство 1010 для временного хранения данных изображения, и устройство 1011 сопряжения, управляющее носителем записи для выполнения записи на носитель записи или считывания с него. Кроме того, система 1000 формирования изображения включает в себя носитель 1012 записи для выполнения записи или считывания данных изображения, к которому может присоединяться, и отсоединяться от него, полупроводниковое запоминающее устройство и тому подобное, и устройство 1013 внешнего сопряжения для установления связи с внешним компьютером и тому подобным.

Далее описывается работа системы 1000 формирования изображения, продемонстрированной на Фиг. 7. Когда экран 1001 открыт, включается основной источник питания, а затем еще включается источник питания системы управления, такой как устройство 1009 общего управления и арифметических операций. Кроме того, следом включается источник питания схемы системы фотосъемки, такой как твердотельное устройство 1004 формирования изображения.

Затем выполняется операция управления величиной экспозиции. Устройство 1009 общего управления и арифметических операций открывает диафрагму 1003, и выходной сигнал от твердотельного устройства 1004 формирования изображения в это время подается на вход устройства 1007 обработки сигналов. Устройство 1007 обработки сигналов заставляет устройство 1009 общего управления и арифметических операций выполнить операцию для получения экспозиции на основе сигнала. Яркость объекта определяется на основе результата этой операции, и устройство 1009 общего управления и арифметических операций управляет диафрагмой. Определение может выполняться, например, посредством сравнения результата операции с данными, заранее сохраненными в устройстве 1009 общего управления и арифметических операций.

Следующим этапом, устройство 1009 общего управления и арифметических операций выделяет высокочастотные составляющие, чтобы выполнить операцию получения расстояния от системы 1000 формирования изображения до объекта на основе выходного сигнала от твердотельного устройства 1004 формирования изображения.

После этого, устройство 1009 общего управления и арифметических операций перемещает объектив 1002 и определяет, находится объектив 1002 в фокусе в таком положении или нет. Если устройство 1009 общего управления и арифметических операций определяет, что объектив 1002 не в фокусе, то устройство 1009 общего управления и арифметических операций снова перемещает объектив 1002, чтобы выполнить измерение расстояния. Определение может выполняться, например, посредством сравнения данных, заранее сохраненных в устройстве 1009 общего управления и арифметических операций.

Следующим этапом, после определения нахождения в фокусе, начинается основная экспозиция. По окончании экспозиции выходной сигнал изображения от твердотельного устройства 1004 формирования изображения обрабатывается устройством 1007 обработки сигналов, а затем удерживается в запоминающем устройстве 1010 при помощи устройства 1009 общего управления и арифметических операций. После этого данные, удерживаемые в запоминающем устройстве 1010, записываются на съемный носитель 1012 записи, такой как полупроводниковое запоминающее устройство, через посредство устройства 1011 сопряжения, управляющего носителем записи, при помощи устройства 1009 общего управления и арифметических операций. Помимо этого, данные могут подаваться на вход компьютера или чего-то подобного, непосредственно через устройство 1013 внешнего сопряжения.

Все описанные выше варианты осуществления являются иллюстративными, и конкретные конфигурации вариантов осуществления могут изменяться без отступления от сущности и объема настоящего изобретения.

(Другие)

Схема 140 генерирования опорного сигнала, описанная в вышеприведенных вариантах осуществления, не ограничивается той, которая имеет конфигурацию, продемонстрированную на Фиг. 4. Схема может конфигурироваться произвольно при условии, что она может подавать по меньшей мере два опорных сигнала, имеющих уровни сигнала, изменяющиеся в направлениях, отличных друг от друга. То есть, может быть выбрана схема, генерирующая три или более различных опорных сигналов.

Помимо этого, рассматривается следующий вариант. А именно, разрешение схемы А/Ц преобразования составляет N битов; цифры старшего разряда в размере m битов из числа этих N битов подвергаются А/Ц преобразованию на основе одного опорного сигнала; и цифры младшего разряда в размере n битов из числа этих N битов подвергаются операции А/Ц преобразования на основе другого опорного сигнала. В данном случае, N=m+n. Соотношение величины изменения опорного сигнала за единичный временной интервал опорного сигнала, который используется для А/Ц преобразования цифр младшего разряда в размере n битов, к величине изменения за единичный временной интервал, то есть за скачок, опорного сигнала, который используется для А/Ц преобразования цифр старшего разряда в размере m битов, при этом сигнале привязки по времени, равно 1/2n.

Помимо этого, хотя в вышеупомянутых вариантах осуществления продемонстрирована только конфигурация, в которой одна схема генерирования опорного сигнала совместно подает опорный сигнал на все А/Ц преобразователи, может быть предусмотрено множество схем генерирования опорного сигнала, например, и соответствующие схемы генерирования опорного сигнала могут подавать опорные сигналы на множество различных А/Ц преобразователей. Выражаясь конкретнее, возможно реализовать разные схемы генерирования опорного сигнала, которые будут подключаться к нечетным столбцам и к четным столбцам элементов изображения, или реализовать разные схемы генерирования опорного сигнала, которые будут подключаться к левой и правой сторонам областей элементов изображения.

В то время как настоящее изобретение было описано со ссылкой на иллюстративные варианты осуществления, нужно понимать, что настоящее изобретение не ограничивается раскрытыми иллюстративными вариантами осуществления. Объем последующей формулы изобретения должен получить самое широкое толкование, чтобы охватить все изменения, эквивалентные структуры и функции.

Настоящая заявка претендует на привилегии, предоставляемые в связи с подачей Заявки на Патент Японии номер 2008-084109, зарегистрированной 27 марта 2008, которая включается в настоящую заявку путем ссылки во всей полноте.

Изобретения относятся к твердотельному устройству формирования изображения и могут быть использованы для сканирующего устройства, видеокамеры, цифровой фотокамеры. Техническим результатом является повышение точности аналого-цифрового преобразования. Устройство содержит множество элементов изображения, размещенных в матрице, причем каждый элемент изображения выводит аналоговый сигнал; множество схем аналого-цифрового (А/Ц) преобразования, каждая из которых размещена соответственно каждому столбцу из множества элементов изображения для А/Ц преобразования аналогового сигнала в цифровой сигнал, схему генерирования опорного сигнала для подачи, совместно на множество схем А/Ц преобразования, по меньшей мере двух опорных сигналов, чьи уровни сигнала изменяются в разных направлениях электрического потенциала, схема А/Ц преобразования содержит усилитель, входной конденсатор, один конец которого принимает по меньшей мере два опорных сигнала, подаваемых от схемы генерирования опорного сигнала, и аналоговый сигнал, а другой конец соединен с одним входным концом усилителя; конденсатор обратной связи, соединенный между упомянутым одним входным концом и выходным концом усилителя, сравнивающее устройство для сравнения выхода от выходного конца усилителя со сравниваемым уровнем. 3 н. и 15 з.п. ф-лы, 12 ил.

1. Твердотельное устройство формирования изображения, содержащее:

область элементов изображения, включающую в себя множество элементов изображения, размещенных в матрице, причем каждый элемент изображения выводит аналоговый сигнал;

множество схем аналого-цифрового (А/Ц) преобразования, каждая из которых размещена соответственно каждому столбцу из множества элементов изображения для А/Ц преобразования аналогового сигнала в цифровой сигнал, при этом

твердотельное устройство формирования изображения содержит

схему генерирования опорного сигнала для подачи совместно на множество схем А/Ц преобразования по меньшей мере двух опорных сигналов, чьи уровни сигнала изменяются в разных направлениях электрического потенциала, и

схема А/Ц преобразования содержит:

усилитель;

входной конденсатор, один конец которого принимает по меньшей мере два опорных сигнала, подаваемых от схемы генерирования опорного сигнала, и аналоговый сигнал, а другой конец соединен с одним входным концом усилителя;

конденсатор обратной связи, соединенный между упомянутым одним входным концом и выходным концом усилителя; и

сравнивающее устройство для сравнения выхода от выходного конца усилителя со сравниваемым уровнем.

2. Твердотельное устройство формирования изображения по п.1, в котором

аналоговый сигнал и по меньшей мере два опорных сигнала усиливаются с коэффициентом усиления, определяемым соотношением емкостей входного конденсатора и конденсатора обратной связи, и выводятся из усилителя.

3. Твердотельное устройство формирования изображения по п.1, дополнительно содержащее соединительный конденсатор, имеющий один конец, соединенный с выходным концом усилителя, и другой конец, соединенный с одним входным концом сравнивающего устройства, причем

соединительный конденсатор выполнен с возможностью удерживания сигнала, включающего в себя составляющую смещения усилителя.

4. Твердотельное устройство формирования изображения по п.2, дополнительно содержащее соединительный конденсатор, имеющий один конец, соединенный с выходным концом усилителя, и другой конец, соединенный с одним входным концом сравнивающего устройства, причем

соединительный конденсатор выполнен с возможностью удерживания сигнала, включающего в себя составляющую смещения усилителя.

5. Твердотельное устройство формирования изображения по п.3, в котором

сравнивающее устройство имеет другой входной конец, соединенный через конденсатор с источником питания для подачи сравниваемого уровня.

6. Твердотельное устройство формирования изображения по п.4, в котором

сравнивающее устройство имеет другой входной конец, соединенный через конденсатор с источником питания для подачи сравниваемого уровня.

7. Твердотельное устройство формирования изображения по п.1, в

котором схема А/Ц преобразования имеет разрешающую способность N битов, и N=m+n,

при этом аналоговый сигнал подвергается А/Ц преобразованию таким образом, что биты старшего разряда в размере m битов преобразуются на основании одного из двух опорных сигналов, подаваемых от схемы генерирования опорного сигнала, а биты младшего разряда в размере n битов преобразуются на основании другого из двух опорных сигналов, подаваемых от схемы генерирования опорного сигнала.

8. Твердотельное устройство формирования изображения по п.7, в котором

соотношение величины изменения одного опорного сигнала за единичный временной интервал к величине изменения другого опорного сигнала за единичный временной интервал равно 1/2n.

9. Твердотельное устройство формирования изображения по п.1, в котором

схема генерирования опорного сигнала содержит по меньшей мере первый конденсатор, второй конденсатор, третий конденсатор и операционный усилитель;

один конец первого конденсатора и один конец второго конденсатора соединены с одним входным концом операционного усилителя;

третий конденсатор соединен между упомянутым одним входным концом и выходным концом операционного усилителя;

схема генерирования опорного сигнала выполнена с возможностью генерирования одного из по меньшей мере двух опорных сигналов, уровень сигнала которых изменяется по отношению ко времени на основании соотношения емкостей первого конденсатора и третьего конденсатора, и

генерирования другого из по меньшей мере двух опорных сигналов, уровень сигнала которых изменяется по отношению ко времени на основании соотношения емкостей второго конденсатора и третьего конденсатора; и

напряжения, прилагаемые к другому концу первого конденсатора и к другому концу второго конденсатора, являются одинаковыми.

10. Твердотельное устройство формирования изображения по п.9, в котором другой конец первого конденсатора и другой конец второго конденсатора соединены с общим источником питания.

11. Твердотельное устройство формирования изображения по любому из пп.1-10, которое дополнительно содержит

измерительную схему, измеряющую величину изменения за единичный временной интервал электрического заряда, удерживаемого в конденсаторе обратной связи, на основании двух соответствующих опорных сигналов, подаваемых от схемы генерирования опорного сигнала; и

корректирующее устройство для коррекции выхода от схемы А/Ц преобразования на основании результата измерения при помощи измерительной схемы.

12. Твердотельное устройство формирования изображения по любому из пп.1-10, которое дополнительно содержит

измерительную схему, измеряющую величину изменения за единичный временной интервал электрического заряда, удерживаемого в конденсаторе обратной связи, на основании двух опорных сигналов, подаваемых от схемы генерирования опорного сигнала; и

корректирующее устройство для коррекции выхода от схемы генерирования опорного сигнала на основании результата измерения при помощи измерительной схемы.

13. Твердотельное устройство формирования изображения по п.11, в котором

период измерения при помощи измерительной схемы по меньшей мере частично перекрывается с периодом операции преобразования при помощи схемы А/Ц преобразования.

14. Твердотельное устройство формирования изображения по п.12, в котором

период измерения при помощи измерительной схемы по меньшей мере частично перекрывается с периодом операции преобразования при помощи схемы А/Ц преобразования.

15. Система формирования изображения, которая содержит:

твердотельное устройство формирования изображения по любому из пп.1-14;

оптическую систему для формирования изображения на области элементов изображения; и

устройство обработки сигналов для обработки выходного сигнала от твердотельного устройства формирования изображения.

16. Способ работы твердотельного устройства формирования изображения, причем твердотельное устройство формирования изображения содержит:

область элементов изображения, включающую в себя множество элементов изображения, размещенных в матрице,

множество схем аналого-цифрового (А/Ц) преобразования, каждая из которых размещена соответственно каждому столбцу из множества элементов изображения для А/Ц преобразования аналогового сигнала в цифровой сигнал,

схема А/Ц преобразования содержит интегрирующую схему, имеющую входной конденсатор,

при этом способ содержит:

этап интегрирования интегрирующей схемой сигнала на основании аналогового сигнала с первой операцией одного из зарядки или разрядки в ответ на вывод элементом изображения аналогового сигнала во входной конденсатор;

первый этап выполнения интегрирующей схемой второй операции другого из зарядки или разрядки с первым сигналом, подаваемым во входной конденсатор, причем уровень сигнала первого сигнала изменяется в заданном направлении;

этап сравнения сигнала, выводимого из интегрирующей схемы, после первого этапа, с сигналом сравниваемого уровня;

второй этап выполнения интегрирующей схемой первой операции со вторым сигналом, подаваемым во входной конденсатор, причем уровень сигнала второго сигнала изменяется в направлении, отличном от упомянутого заданного направления; и

этап сравнения сигнала, выводимого из интегрирующей схемы, после второго этапа, с сигналом сравниваемого уровня.

17. Способ по п.16, в котором

схема А/Ц преобразования имеет разрешающую способность N битов, и N=m+n,

схема А/Ц преобразования выполняет А/Ц преобразование m битов старшего разряда на основании первого сигнала и выполняет А/Ц преобразование n битов младшего разряда на основании второго сигнала.

18. Способ по п.16, в котором

интегрирующая схема имеет усилитель и конденсатор обратной связи, соединенный в электрическом пути между выходным концом и входным концом усилителя, и

операция зарядки или разрядки интегрирующей схемы выполняется конденсатором обратной связи.

| US 2007046795 A1, 01.03.2007 | |||

| JP 2002232291 A, 16.08.2002 | |||

| US 2006219866 A1, 05.10.2006 | |||

| ОДНОКРИСТАЛЬНЫЙ АДАПТИВНЫЙ ВИДЕОДАТЧИК | 2005 |

|

RU2299521C1 |

Авторы

Даты

2012-12-27—Публикация

2009-02-26—Подача