ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к полупроводниковому устройству, включающему в себя множество тонкопленочных транзисторов и защитных диодов ESD (от электростатического разряда).

УРОВЕНЬ ТЕХНИКИ

В последние годы, становятся широко распространенными жидкокристаллические устройства отображения и органические электролюминесцентные (EL) устройства отображения, которые включают в себя тонкопленочный транзистор (в дальнейшем, «TFT») для каждого пикселя. TFT изготавливаются посредством использования полупроводникового слоя, сформированного на подложке, такой как стеклянная подложка. Подложка, на которой сформированы TFT, указывается ссылкой как подложка активной матрицы.

Традиционно, TFT, использующие пленку аморфного кремния в качестве активного слоя (в дальнейшем, «TFT на аморфном кремнии») и TFT, использующие пленку поликристаллического кремния в качестве активного слоя (в дальнейшем, «TFT на поликристаллическом кремнии»), широко используются в качестве TFT.

Поскольку подвижность носителей пленки поликристаллического кремния более высока, чем у пленки аморфного кремния, TFT на поликристаллическом кремнии имеет более высокий ток включенного состояния, чем TFT на аморфном кремнии, и способен к работе с большим быстродействием. Ввиду этого, были сконструированы панели отображения, в которых не только TFT для пикселей, но также некоторые или все их TFT для периферийных схем, таких как формирователи, сформированы TFT на поликристаллическом кремнии. Формирователи, сформированные таким образом на изолирующей подложке (типично, стеклянной подложке), формирующей панель отображения, могут называться монолитными формирователями. Формирователи включают в себя затворный формирователь и истоковый формирователь, и только один из таковых может быть монолитным формирователем. В материалах настоящей заявки, панель отображения указывает ссылкой на часть жидкокристаллического устройства отображения или органического электролюминесцентного устройства отображения, включающего в себя участок отображения, и не включает в себя подсветку, обрамление, или тому подобное, жидкокристаллического устройства отображения.

Изготовление TFT на поликристаллическом кремнии требует сложных технологических процессов, таких как технологический процесс термического отжига или технологический процесс ионного легирования, а также технологический процесс лазерной кристаллизации для кристаллизации пленки аморфного кремния. Таким образом, в настоящее время, TFT на поликристаллическом кремнии, главным образом, используются в средних и малых устройствах отображения, и TFT на аморфном кремнии используются в больших устройствах отображения.

В последние годы, с ростом потребности в повышении качества изображения и снижения потребляемой мощности в дополнение к увеличению размера устройств отображения, были сделаны предложения (Патентный документ № 1, Патентный документ № 2 и Непатентный документ № 1) TFT, использующие пленку микрокристаллического кремния (µc-Si) в качестве активного слоя, который имеет более высокие рабочие характеристики и более низкие производственные затраты чем TFT на аморфном кремнии. Такой TFT называется «TFT на микрокристаллическом кремнии».

Пленка микрокристаллического кремния является пленкой кремния, имеющей микрокристаллические частицы в ней, и границы зерен микрокристаллических частиц, в основном, находятся в аморфной фазе. То есть, она является смешанным состоянием между кристаллической фазой микрокристаллических частиц и аморфной фазой. Размер каждой микрокристаллической частицы является меньшим, чем у каждой кристаллической частицы, включенной в пленку поликристаллического кремния. В пленке микрокристаллического кремния, каждая микрокристаллическая частица, например, имеет столбчатую форму, растущую из поверхности подложки.

Были предложены TFT, которые используют металл-оксид-полупроводник, такой как полупроводниковую пленку Zn-O (ZnO) или полупроводниковую пленку In-Ga-Zn-O (IGZO), в качестве нового материала для замены кремния. Патентный документ № 3 устанавливает, что можно, с использованием полупроводникового слоя ZnO, получать TFT, имеющий отношение токов включенного состояния/выключенного состояния (ON/OFF) 4,5×105, подвижность около 150 см2/Вс, и пороговое значение около 1,3 В. Эта подвижность является гораздо большей, чем у TFT на аморфном кремнии. Непатентный документ №2 устанавливает, что, используя полупроводниковый слой IGZO, можно получать TFT, имеющий подвижность приблизительно от 5,6 до 8,0 см2/Вс и пороговое значение приблизительно от -6,6 до -9,9 V. Подобным образом подвижность является гораздо большей, чем у TFT на аморфном кремнии.

Таким образом, с большими устройствами отображения, есть случаи, в которых некоторые или все из TFT для периферийной схемы, такой как формирователь, формируются на подложке активной матрицы в дополнение к TFT для пикселей с использованием аморфного кремния, микрокристаллического кремния, IGZO, и т.д.

С другой стороны, схема защиты от ESD (электростатического разряда) нормально предусмотрена на подложке активной матрицы для предотвращения электростатического повреждения в отношении элементов, линий, и т.д.

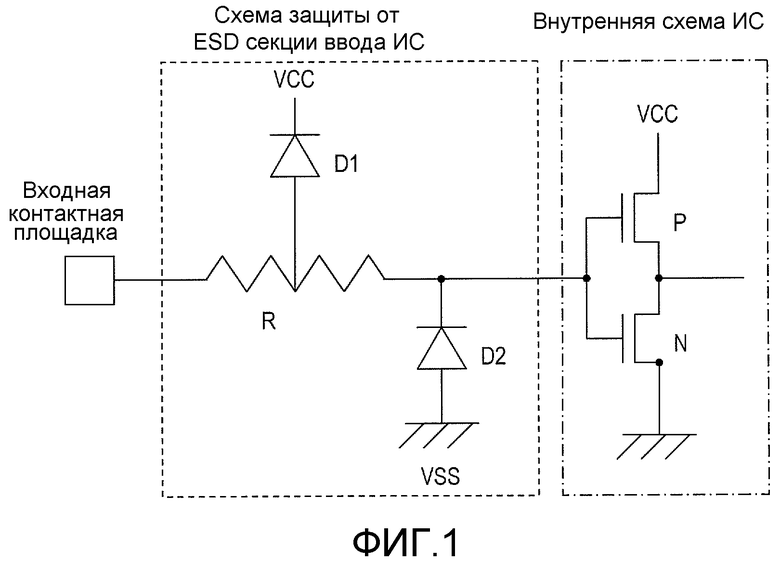

Фиг.1 - схема, показывающая пример схемы защиты от ESD, предусмотренной для внутренней схемы IC, имеющей CMOS (комплементарные элементы металл-оксид-полупроводник). Схема защиты от ESD, показанная на фиг.1, включает в себя защитный резистор R, сформированный между входным выводом CMOS, и два защитных диода D1 и D2 противоположных полярностей. Защитные диоды D1 и D2 оба присоединены к входной сигнальной линии CMOS.

Со схемой защиты от ESD, когда бросок напряжения ESD проникает на входной вывод, потенциал входного вывода увеличивается (+) или уменьшается (-). Если он увеличивается (+), защитный диод D1 включается, тем самым, шунтируя положительный заряд на линию VCC. Если он уменьшается (-), защитный диод D2 включается, тем самым, шунтируя положительный заряд на линию VSS. Величина электрического тока ограничивается защитным резистором R.

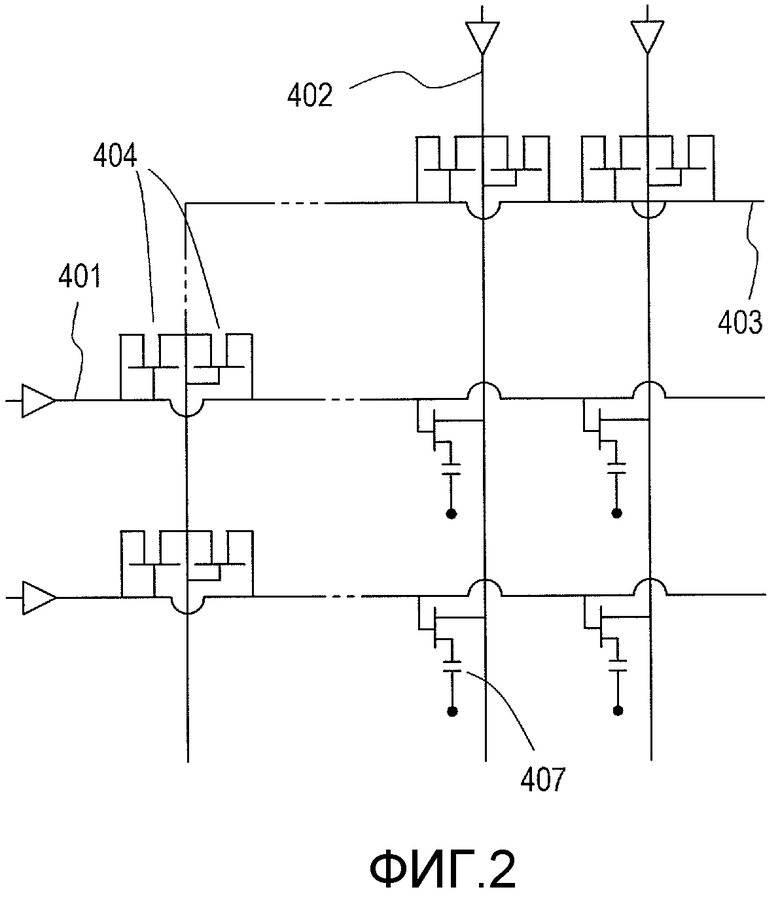

Патентный документ № 4 раскрывает подложку активной матрицы, включающую в себя множество затворных линий 401 и множество стоковых линий 402, пересекающих друг друга, с пиксельным тонкопленочным транзистором 407, предусмотренным на каждом пересечении, как показано на фиг.2, при этом, защитные диоды 404 от ESD предусмотрены между линией 403 опорного потенциала, на которую выдается опорный потенциал, и затворными линиями 401, и между линией 403 опорного потенциала и стоковыми линиями 402. Два диода 404 сформированы посредством использования одной и той же полупроводниковой пленки в качестве полупроводникового слоя пиксельного тонкопленочного транзистора 407 и имеют структуру, в которой исток и затвор TFT закорочены друг на друга. Диоды, имеющие такую структуру также указываются ссылкой как «диоды типа TFT». Электрод затвора одного из двух диодов 404 присоединен к затворной линии 401, а электрод затвора другого присоединен к линии 403 опорного потенциала. Поэтому, заряжается ли затворная 401 положительно или отрицательно по отношению к линии 403 опорного потенциала, можно обеспечивать электрический ток между затворной линией 401 и линией 403 опорного потенциала в таком направлении, чтобы нейтрализовать заряд. Поэтому, можно подавлять напряжение между затворной линией и линией стока, вызванное ESD, и предохранять тонкопленочный транзистор 407 от повреждения броском напряжения ESD.

Несмотря на то, что фиг.2 показывает диоды 404 типа TFT для защиты пиксельных тонкопленочных транзисторов 407, подобные диоды типа TFT могут использоваться для тонкопленочных транзисторов защитной схемы, например, используемых в схемах, таких как схемы формирователя.

СПИСОК ПРОТИВОПОСТАВЛЕННЫХ МАТЕРИАЛОВ

ПАТЕНТНАЯ ЛИТЕРАТУРА

Патентный документ № 1: Публикация № 6-196701 выложенного патента Японии

Патентный документ № 2: Публикация № 5-304171 выложенного патента Японии

Патентный документ № 3: Публикация № 2002-76356 выложенного патента Японии

Патентный документ № 4: Публикация № 63-220289 выложенного патента Японии

НЕПАТЕНТНАЯ ЛИТЕРАТУРА

Непатентный документ № 1: Zhongyang Xu, et al., «A Novel Thin-film Transistors With (mu)c-Si/a-Si Dual Active Layer Structure For AM-LCD» IDW'96 Proceedings of The Third International Display Workshops VOLUME 1, 1996, p.117-120 (Жонгянг Ксу, и другие, «Новейшие тонкопленочные транзисторы с двухслойной структурой активного слоя µc-Si/a-Si», Протоколы IDW'96 третьего международного симпозиума по устройствам отображения, том 1, 1996, стр. 117-120)

Непатентный документ № 2: Je-hun Lee, et al., «World's Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT», SID 08 DIGEST (USA), Society for Information Display, 2008, Volume 39, Issue 1, pp. 625-628 (Джи-хун Ли и другие, «Самая большая в мире (15-дюймовая) панель AMLCD XGA, использующая оксидные TFT IGZO», SID 08 DIGEST (США), Общество по отображению информации, 2008, том 39, вопрос 1, стр. 625-628)

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ПРОБЛЕМА

Как может быть видно из примера, показанного на фиг.1 и 2, схема защиты от ESD включает в себя по меньшей мере два диода, так что, заряжается ли линия, которая должна быть защищена, положительным зарядом или отрицательным зарядом, заряд может шунтироваться. Таким образом, есть проблема, что возрастает размер схемы.

Более точно, в тех случаях, когда диоды типа TFT, использующие полупроводниковую пленку, такую как пленка аморфного кремния, которая обладает относительно низкой подвижностью, используются в качестве защитных диодов от ESD, необходимо увеличивать ширину W канала диодов типа TFT, тем самым, дополнительно увеличивая размер защитного диода от ESD и, как результат, увеличивая участок обрамления устройства отображения.

Когда пытаются применять схему защиты от ESD к схеме сдвигового регистра, которая не имеет линий VDD, необходимо прокладывать трассы новой линии VDD снаружи, тем самым, дополнительно увеличивая размер схемы.

Настоящее изобретение было сделано ввиду проблем, описанных выше, и его цель состоит в том, чтобы предложить полупроводниковое устройство, включающее в себя множество тонкопленочных транзисторов и схему защиты от ESD для защиты тонкопленочных транзисторов от ESD, с размером схемы, уменьшенным от такового у традиционных технологий, наряду со сдерживанием повреждения тонкопленочных транзисторов, обусловленного ESD.

РЕШЕНИЕ ДЛЯ ПРОБЛЕМЫ

Полупроводниковое устройство по настоящему изобретению является полупроводниковым устройством, включающим в себя схему, включающую в себя множество тонкопленочных транзисторов и по меньшей мере один диод, при этом: множество тонкопленочных транзисторов имеют одинаковый тип проводимости; когда тип проводимости множества тонкопленочных транзисторов является N-типом, электрод катодной стороны по меньшей мере одного диода присоединяется к линии, присоединенной к затвору выбранного одного из множества тонкопленочных транзисторов; когда тип проводимости множества тонкопленочных транзисторов является P-типом, электрод анодной стороны по меньшей мере одного диода присоединяется к линии, присоединенной к затвору выбранного одного из множества тонкопленочных транзисторов; и другой диод, скомпонованный так, чтобы его направление протекания тока было противоположно по меньшей мере одному диоду, не сформирован на линии.

В предпочтительном варианте осуществления, пиковое значение напряжения схемы имеет значение 20 В или более.

Предпочтительно, чтобы полупроводниковые слои по меньшей мере одного тонкопленочного диода и выбранного одного из тонкопленочных транзисторов были сформированы из одной и той же полупроводниковой пленки.

Одна и та же полупроводниковая пленка может быть пленкой микрокристаллического кремния.

Схема может включать в себя регистр.

В предпочтительном варианте осуществления, сдвиговый регистр включает в себя множество каскадов, каждый последовательно выдает выходные сигналы; каждый из множества каскадов включает в себя первый транзистор для выдачи выходного сигнала и множество вторых транзисторов, чья область истока и область стока электрически присоединена к электроду затвора первого транзистора; и множество вторых транзисторов включает в себя многоканальный транзистор, имеющий активный слой, включающий в себя по меньшей мере две канальных области, область истока и область стока.

По меньшей мере один диод может включать в себя: электрод затвора, сформированный на подложке; слой изоляции затвора, сформированный на электроде затвора; по меньшей мере один полупроводниковый слой, сформированный на слое изоляции затвора и имеющий первую область и вторую область; первый электрод, предусмотренный в первой области и электрически присоединенный к первой области и электроду затвора; и второй электрод, предусмотренный во второй области и электрически присоединенный ко второй области.

По меньшей мере один полупроводниковый слой может включать в себя канальную область, перекрывающуюся с электродом затвора, со слоем изоляции затвора, вставленным между ними, и резистивную область, не перекрывающуюся с электродом затвора, со слоем изоляции затвора, вставленным между ними; и путь тока, включающий в себя канальную область и резистивную область, может быть сформирован между первым электродом и вторым электродом, в то время как диод находится во включенном состоянии.

ПОЛЕЗНЫЕ РЕЗУЛЬТАТЫ ИЗОБРЕТЕНИЯ

Согласно настоящему изобретению, в полупроводниковом устройстве, включающем в себя схему одноканальных TFT, можно подавлять рост утечки отключенного состояния TFT вследствие ESD наряду с подавлением увеличения размера схемы. Поэтому, можно предотвращать некорректную работу схемы.

Особенно эффективным является применение настоящего изобретения к подложке активной матрицы, которая включает в себя схему возбуждения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - схема, показывающая пример традиционной схемы защиты от ESD, предусмотренной во внутренней схеме ИС.

Фиг.2 - схема, показывающая традиционную подложку активной матрицы, имеющую схему защиты от ESD.

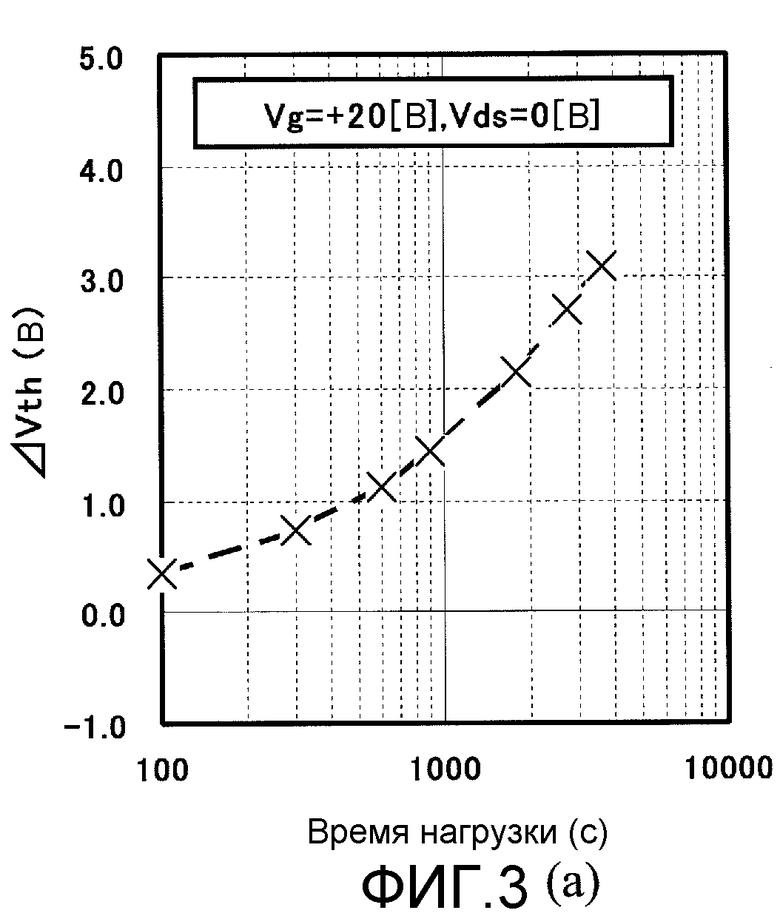

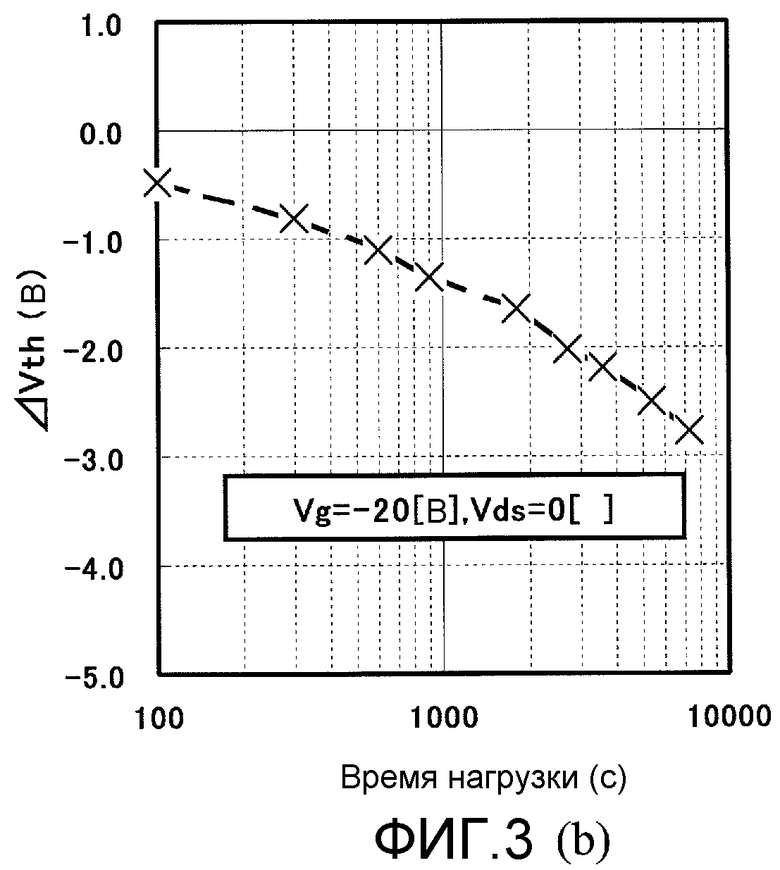

Фиг.3(a) и (b) - графики, показывающие результаты нагрузочных испытаний по зарядке затвора N-канального TFT на аморфном кремнии положительным зарядом (Vg=20 В) и результаты нагрузочных испытаний по зарядке затвора отрицательным напряжением (Vg=-20 В), соответственно.

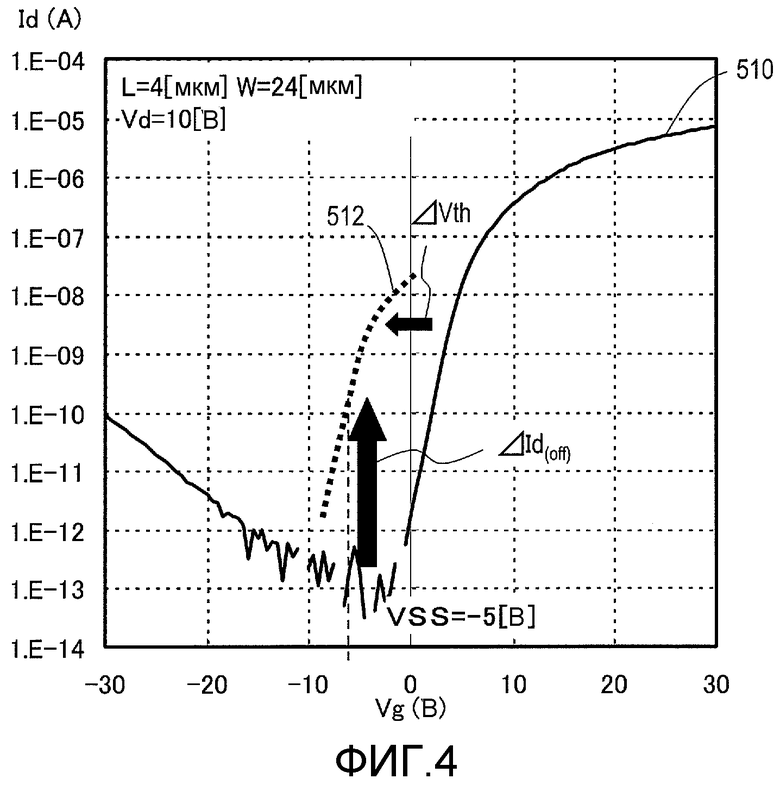

Фиг.4 - график, показывающий характеристики тока (Id) - напряжения (Vg) TFT на аморфном кремнии.

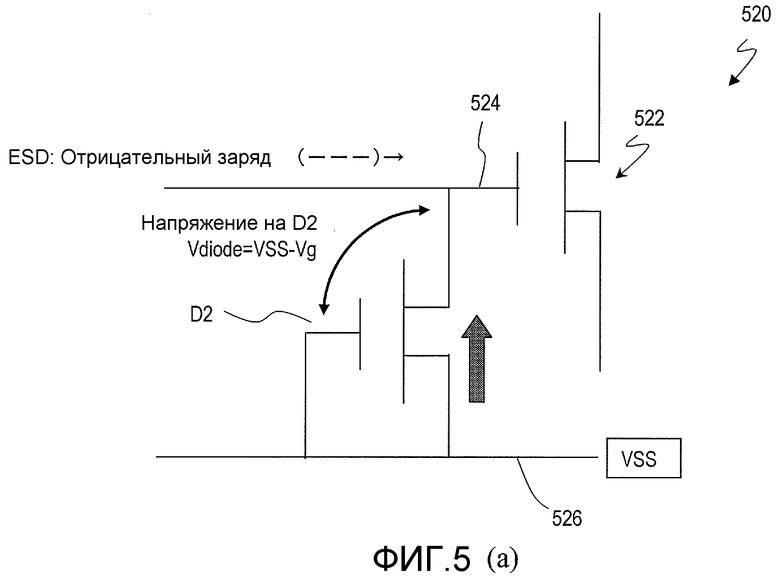

Фиг.5(a) и (b) - схемы, каждая иллюстрирует участок схемы 520 в первом варианте осуществления настоящего изобретения.

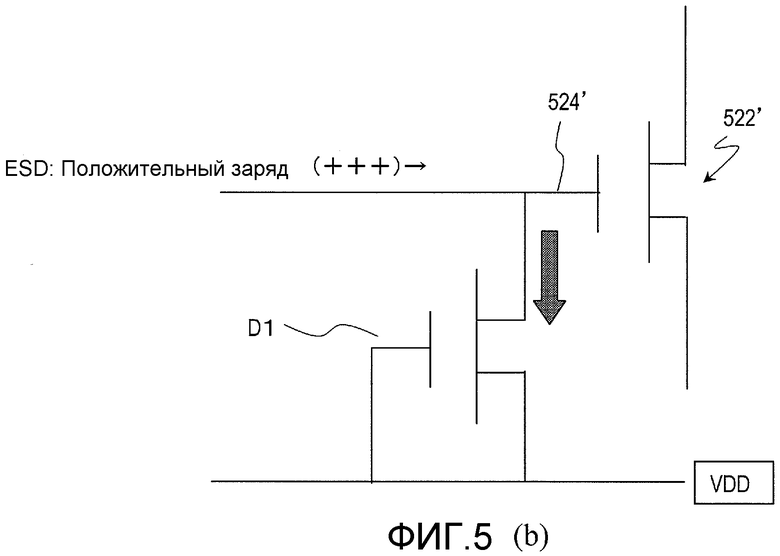

Фиг.6 - схематический вид в поперечном разрезе, показывающий защитный диод по первому варианту осуществления настоящего изобретения.

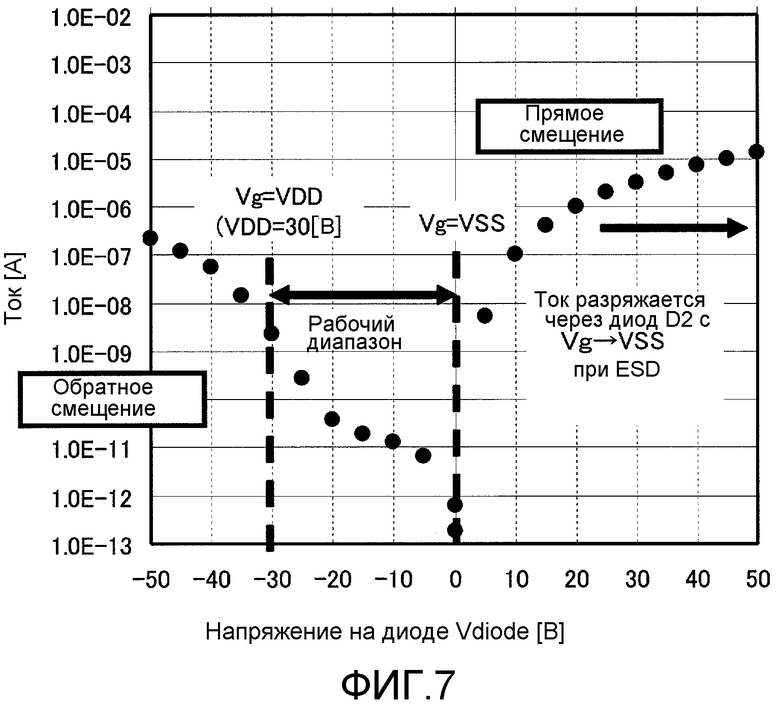

Фиг.7 - график, иллюстрирующий характеристики защитного диода D2 по первому варианту осуществления настоящего изобретения.

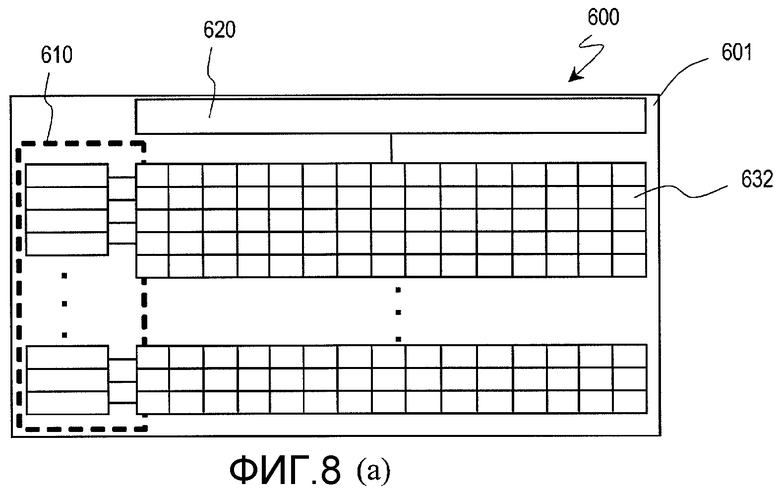

Фиг.8(a) - схематический вид сверху жидкокристаллической панели 600 отображения по варианту осуществления настоящего изобретения, а (b) - вид сверху, показывающий схематическую структуру одного пикселя.

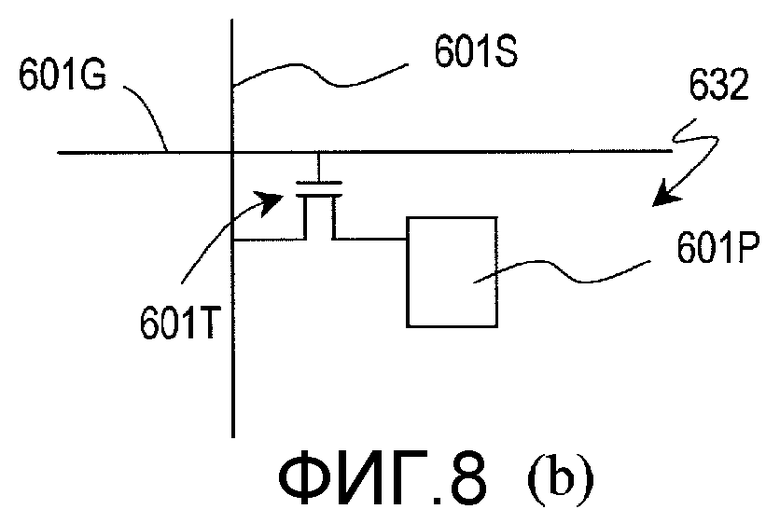

Фиг.9 - структурная схема, иллюстрирующая структуру сдвигового регистра 610B, включенного в затворный формирователь 610.

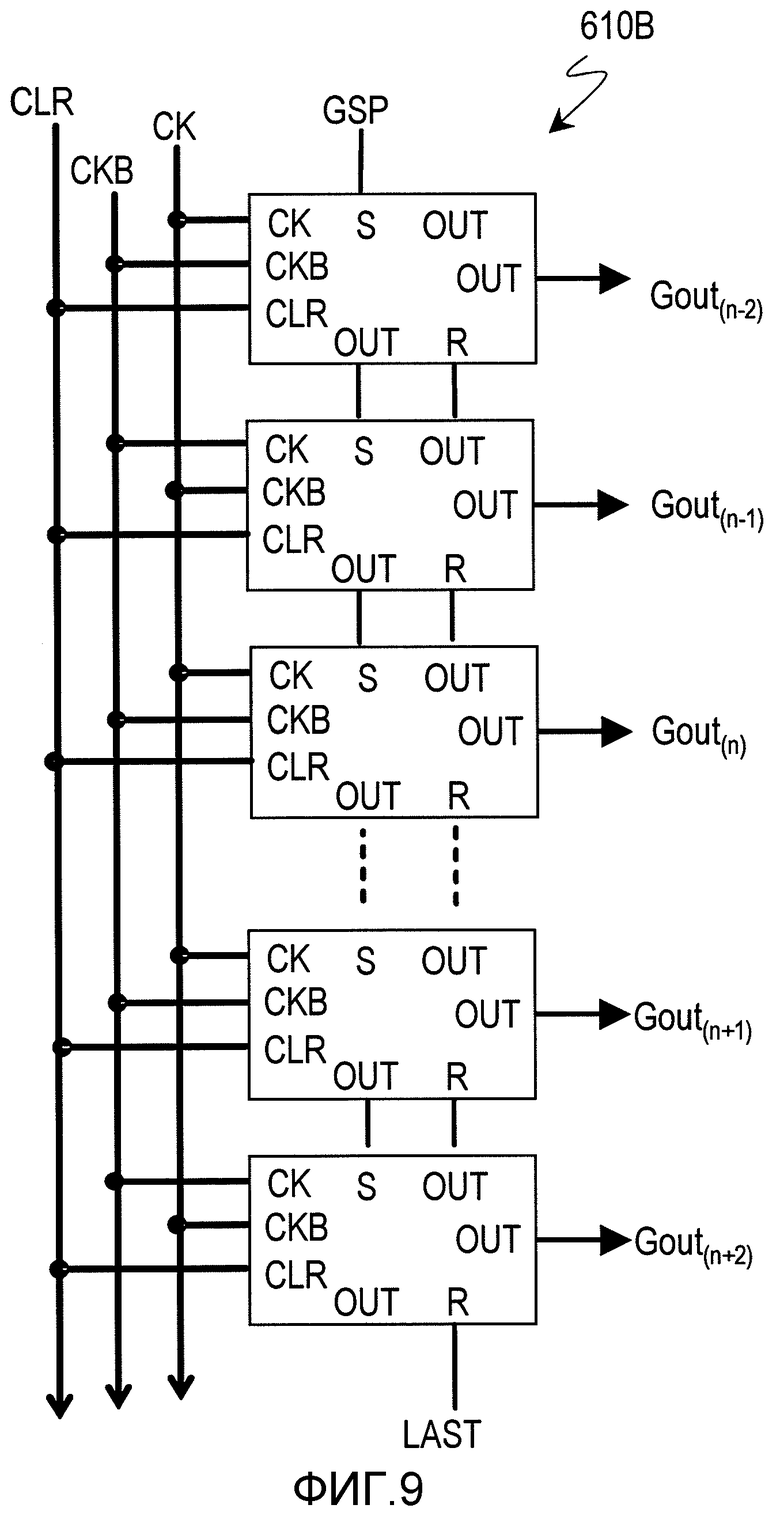

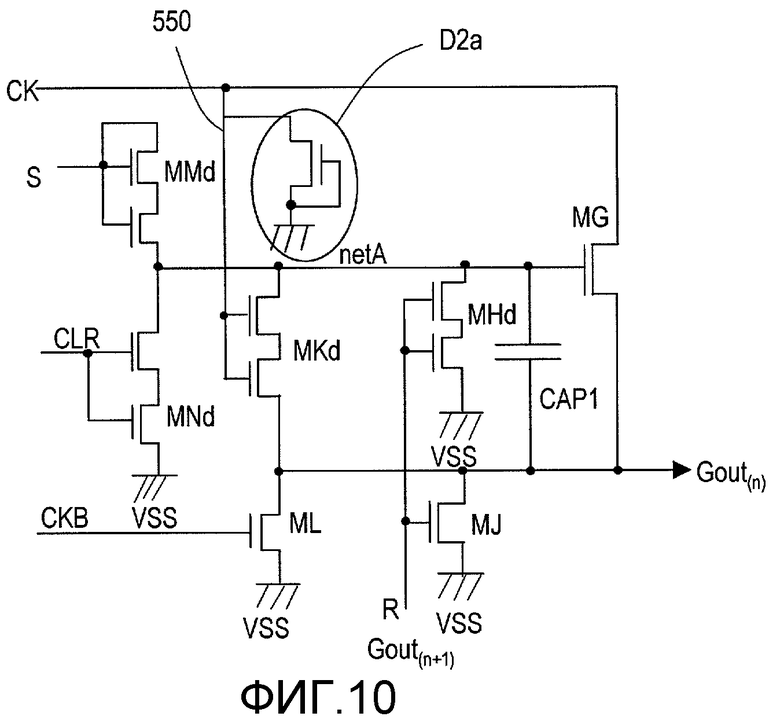

Фиг.10 - принципиальная схема одного каскада сдвигового регистра по варианту осуществления настоящего изобретения, который используется в одном из каскадов сдвигового регистра 610B.

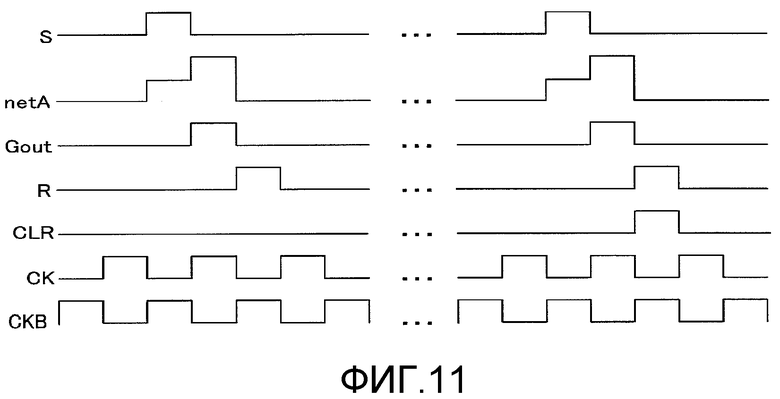

Фиг.11 - схема, показывающая формы сигналов входных/выходных сигналов на разных каскадах сдвигового регистра 610B и форму сигнала напряжения netA.

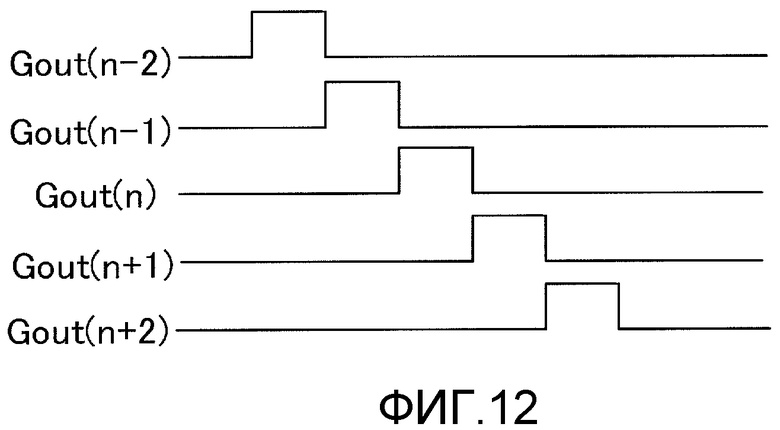

Фиг.12 - схема, показывающая формы сигналов выходных сигналов из пяти каскадов с n-2 по n+2 сдвигового регистра 610B.

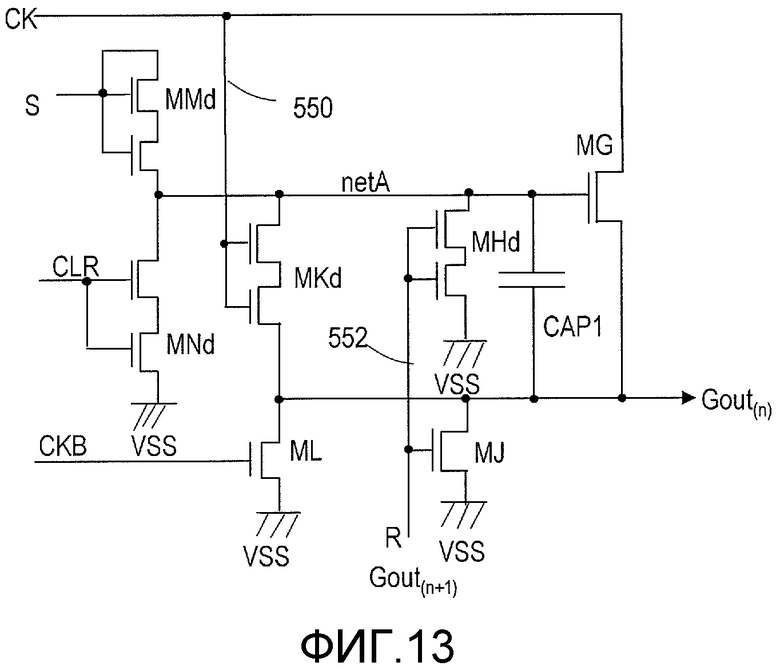

Фиг.13 - принципиальная электрическая схема, показывающая один из каскадов сдвигового регистра по справочному примеру.

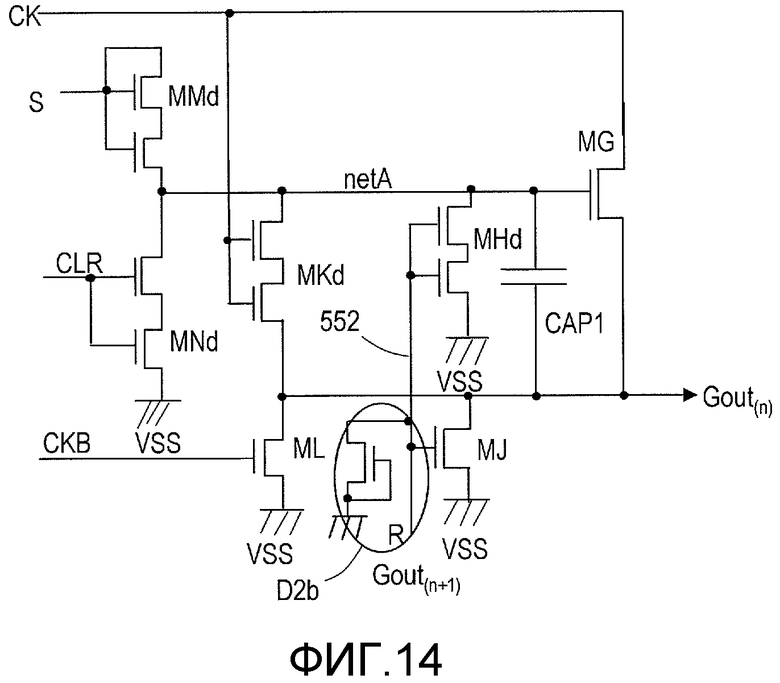

Фиг.14 - принципиальная схема, показывающая один каскад сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

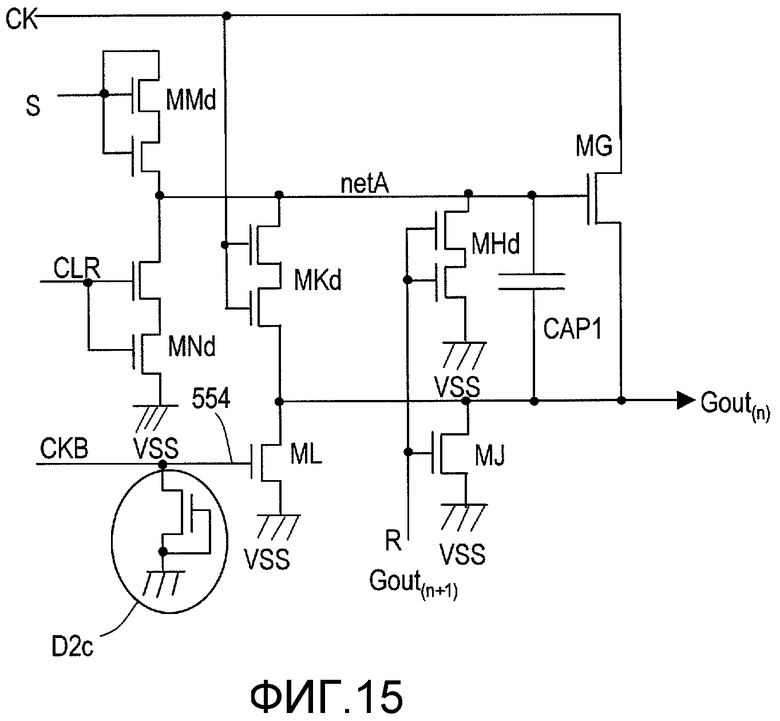

Фиг.15 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

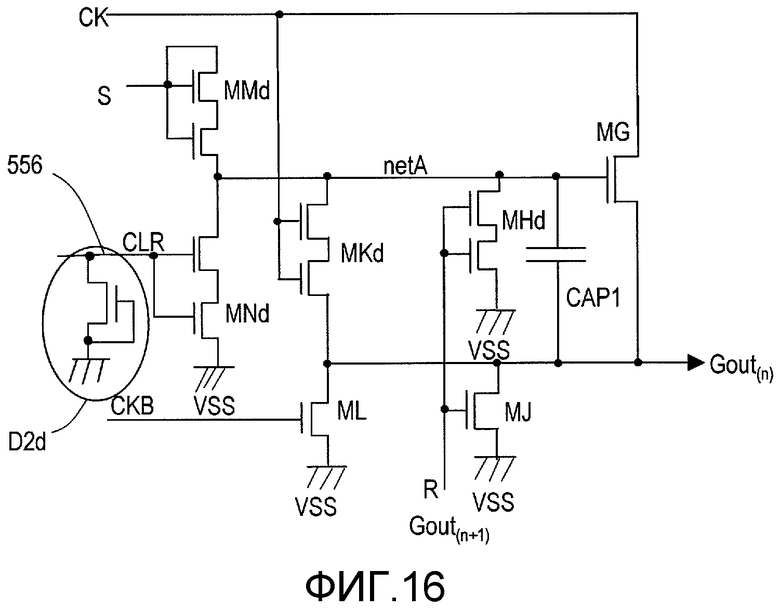

Фиг.16 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

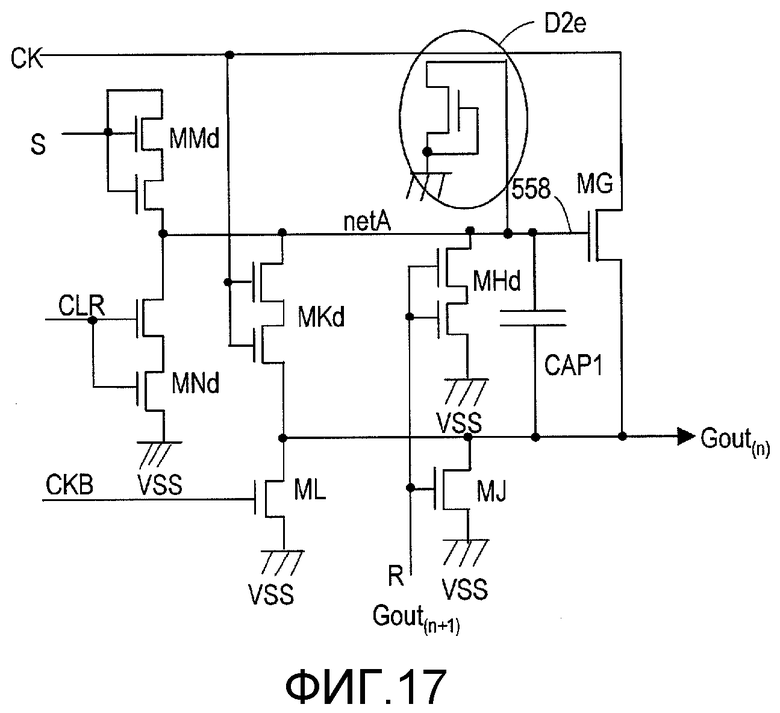

Фиг.17 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

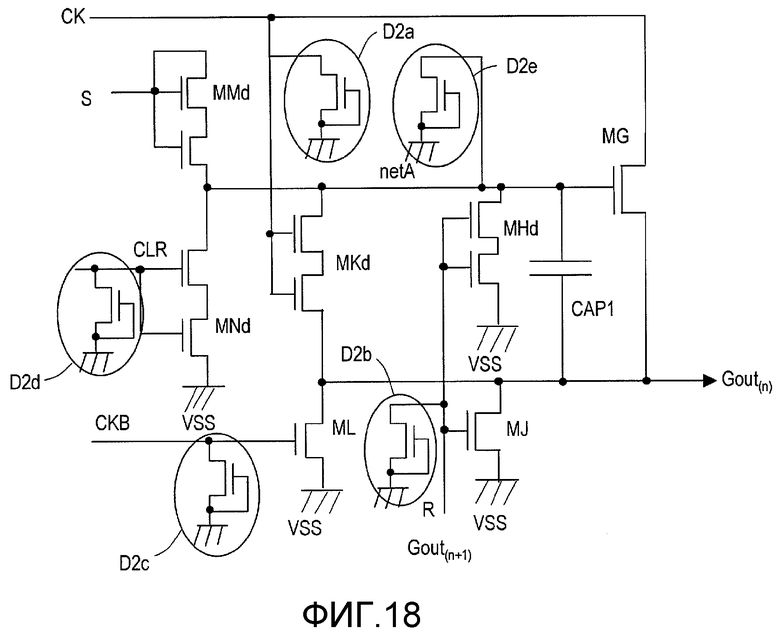

Фиг.18 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

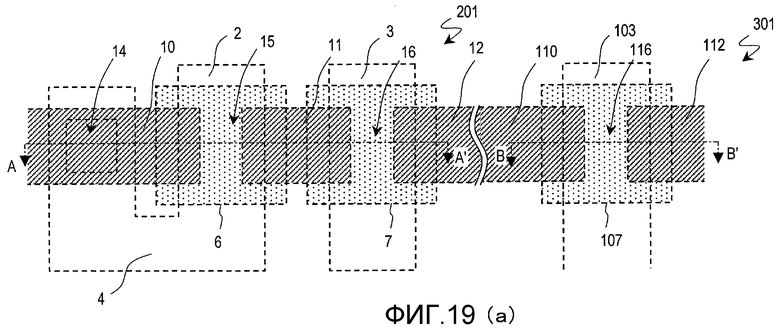

Фиг.19(a) и (b) - схемы, схематически показывающие полупроводниковое устройство по первому варианту осуществления настоящего изобретения, при этом, (a) - его вид сверху, и (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

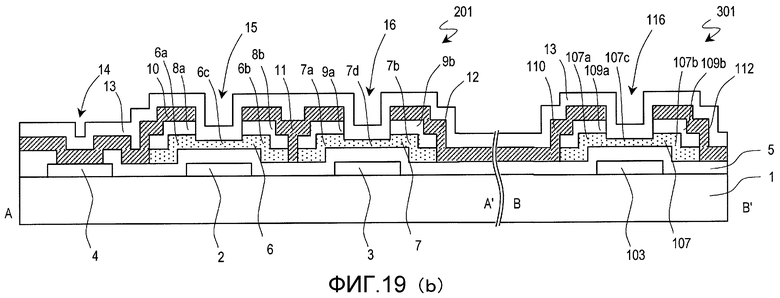

Фиг.20 - блок-схема последовательности операций способа, показывающая пример способа для изготовления полупроводникового устройства, показанного на фиг.19.

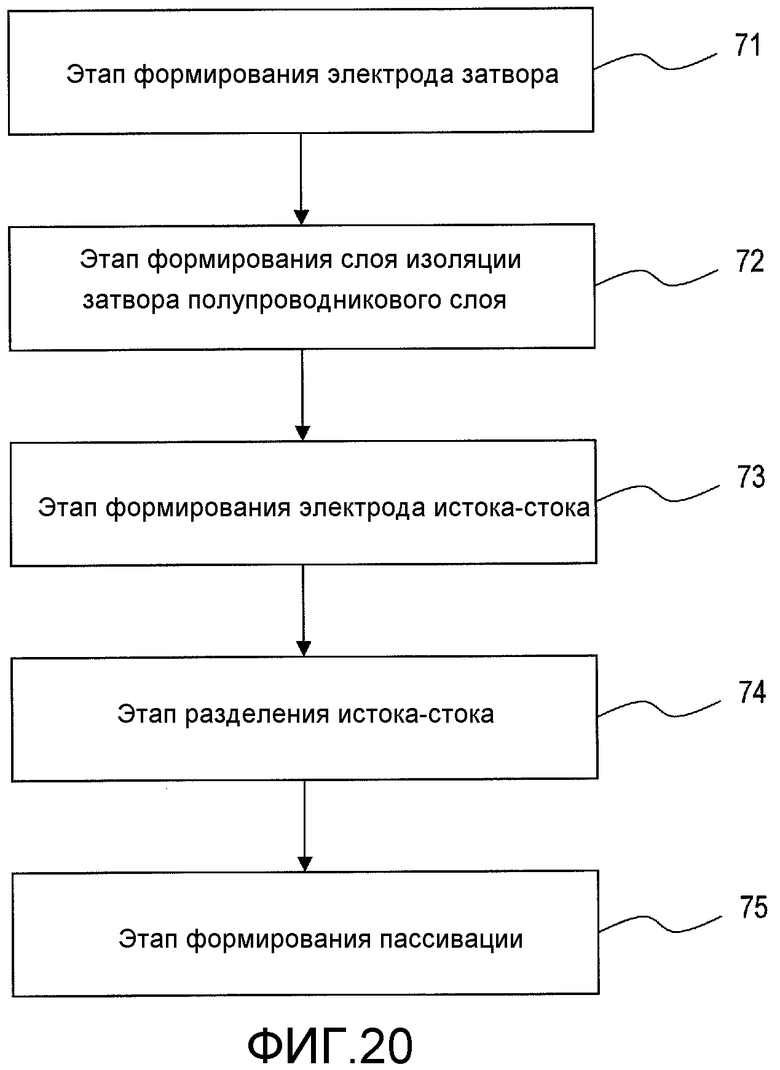

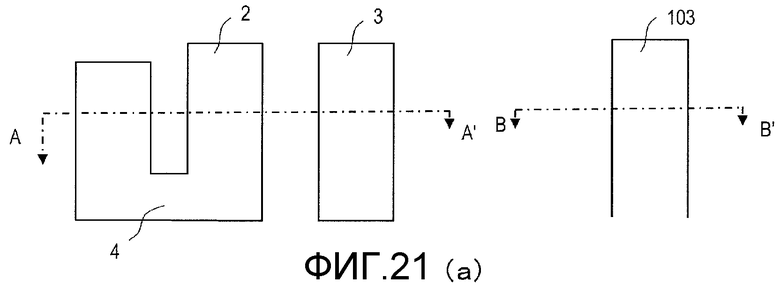

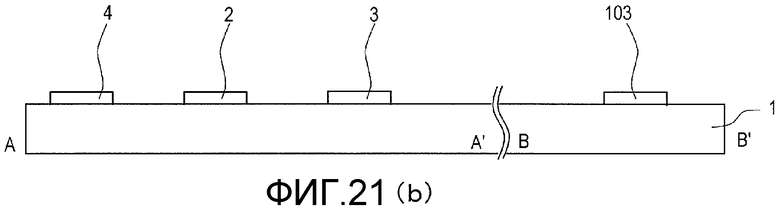

Фиг.21(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

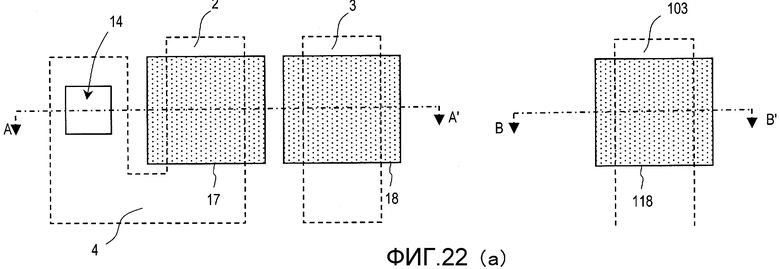

Фиг.22(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

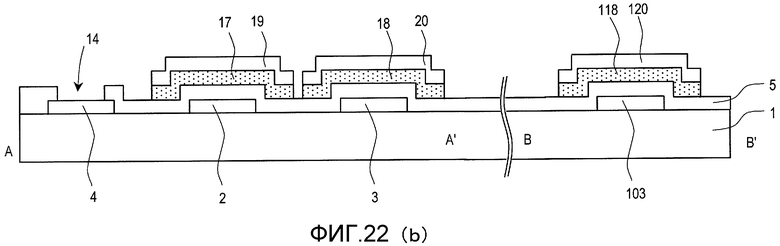

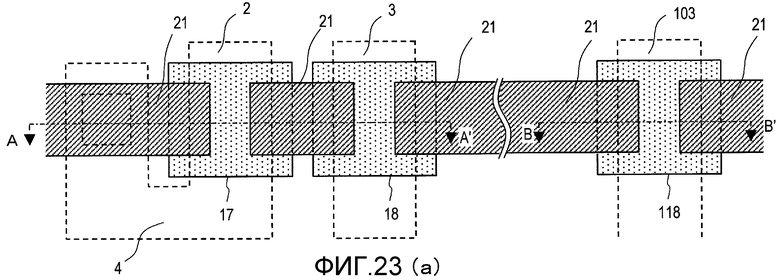

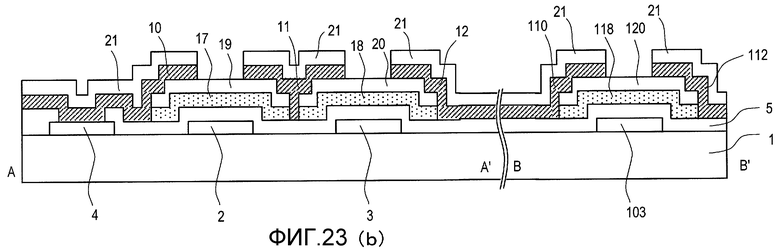

Фиг.23(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

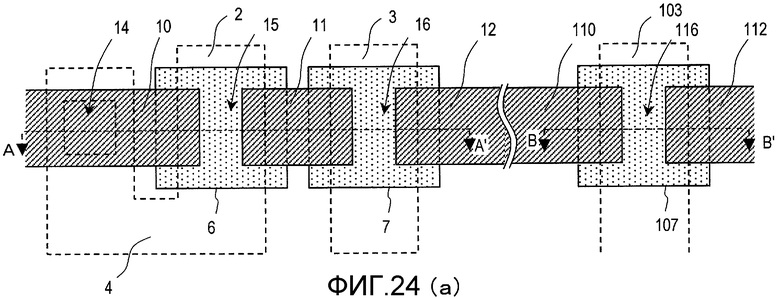

Фиг.21(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

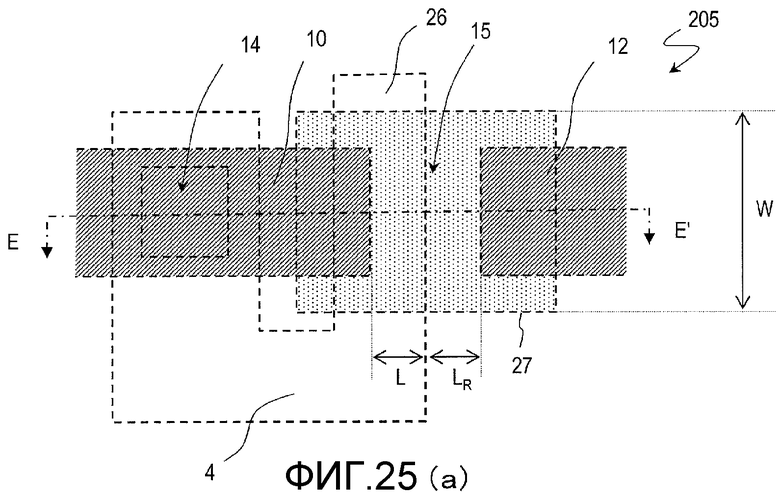

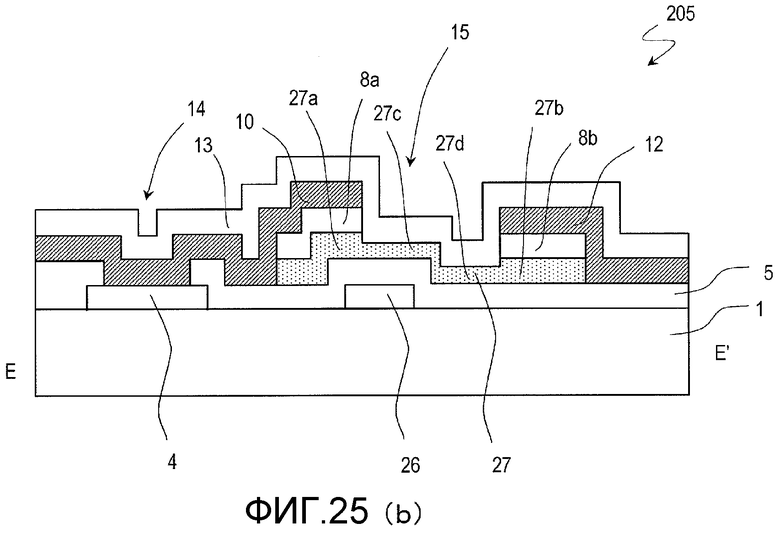

Фиг.25(a) - вид сверху, схематически показывающий еще один другой диод по первому варианту осуществления настоящего изобретения, а (b) - вид в поперечном разрезе, взятый вдоль линии E-E' по (a).

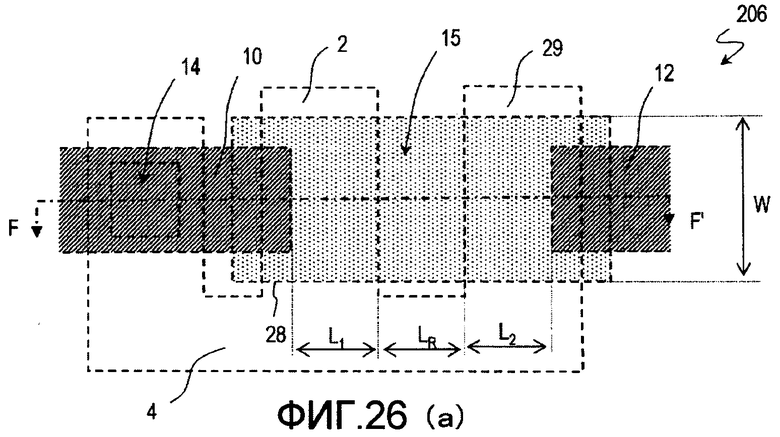

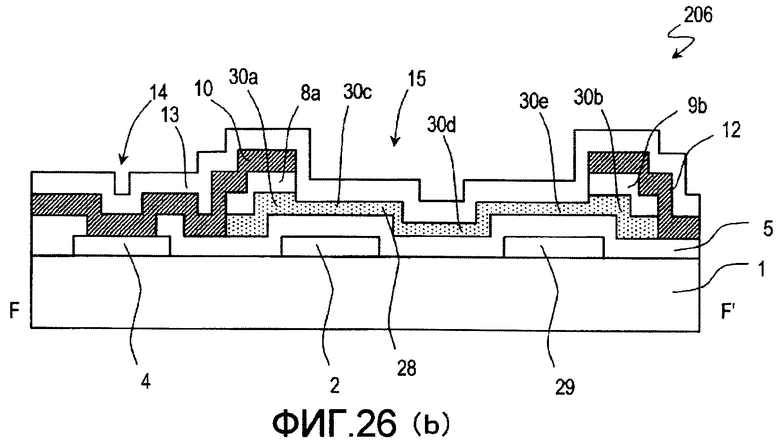

Фиг.25(a) - вид сверху, схематически показывающий еще один другой диод по первому варианту осуществления настоящего изобретения, а (b) - вид в поперечном разрезе, взятый вдоль линии F-F' по (a).

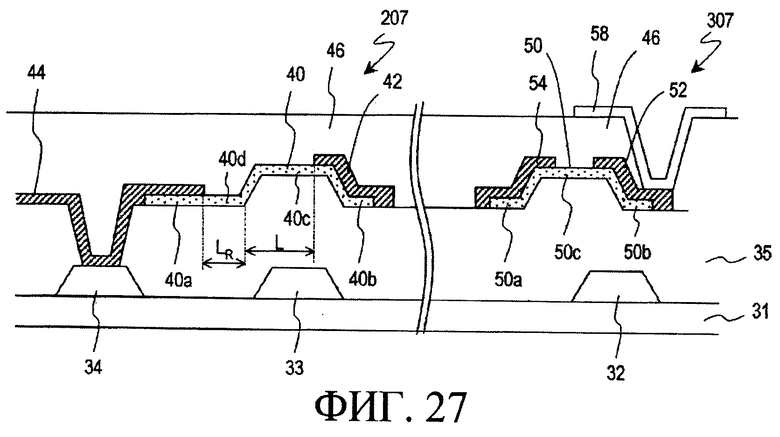

Фиг.27 - схематический вид в поперечном разрезе, показывающий еще одно другое полупроводниковое устройство по первому варианту осуществления настоящего изобретения.

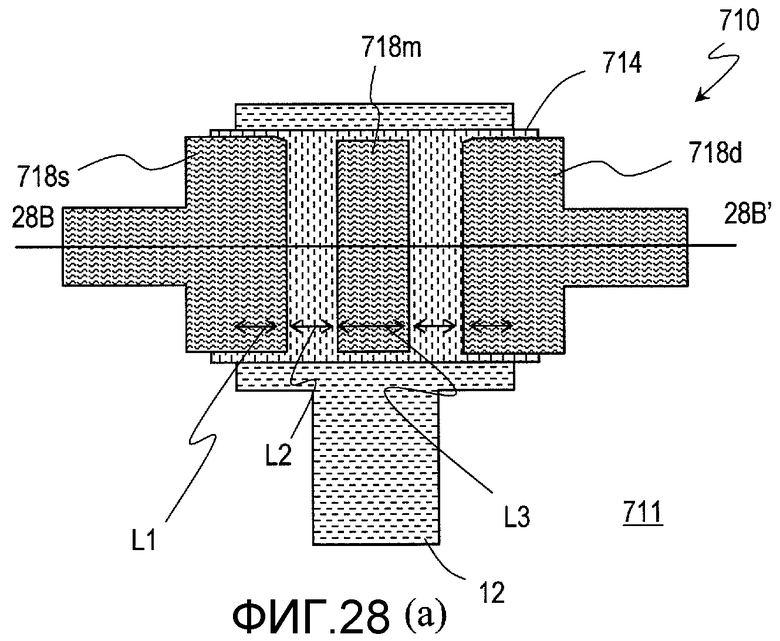

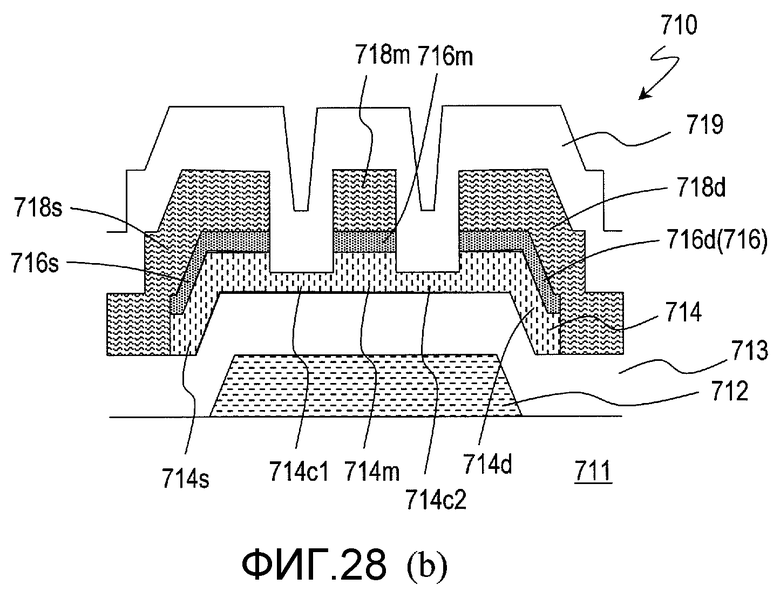

Фиг.28 - схематический вид сверху, показывающий тонкопленочный транзистор 710 по первому варианту осуществления настоящего изобретения, (b) - схематический вид в поперечном разрезе, взятый вдоль линии 28B-28B' по (a), а (c) - эквивалентная принципиальная электрическая схема тонкопленочного транзистора 710.

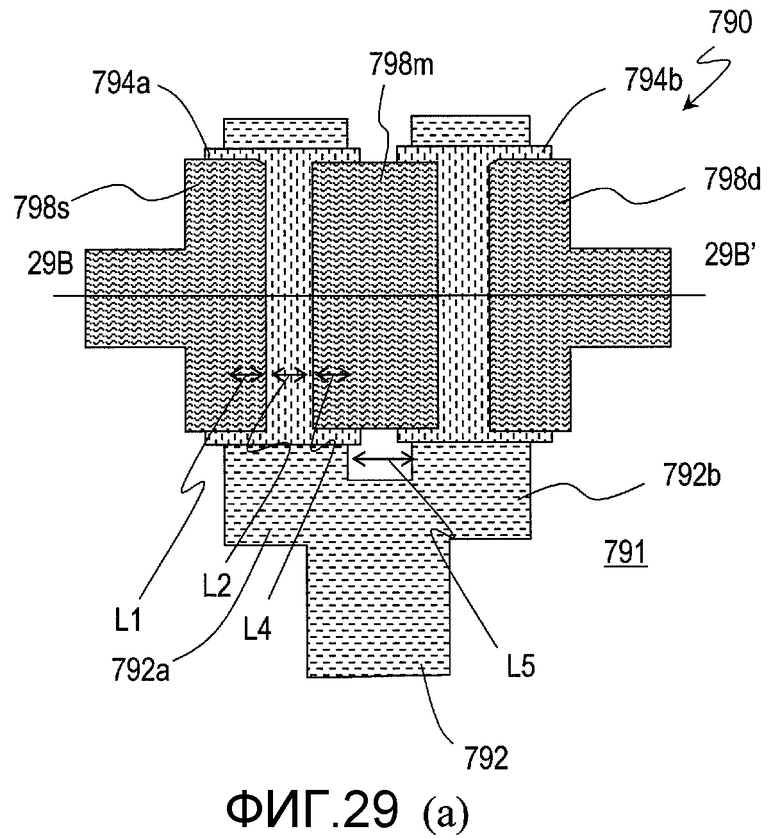

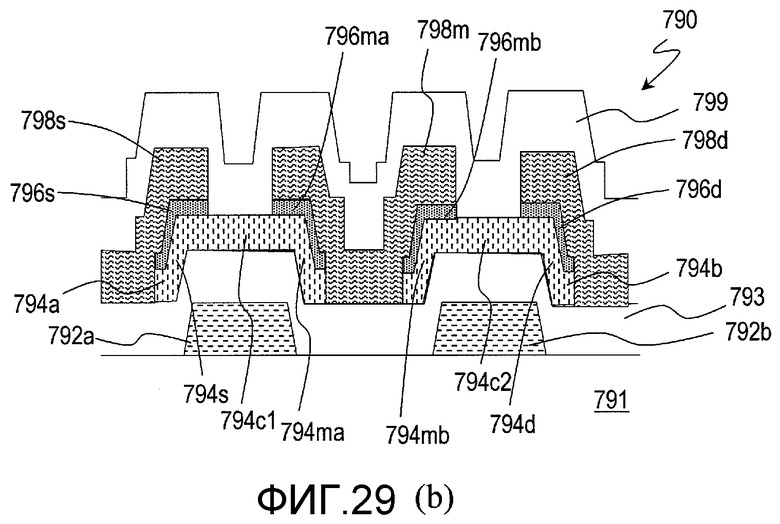

Фиг.29(a) - схематический вид сверху, показывающий еще один тонкопленочный транзистор 790, имеющий структуру с двумя затворами, а (b) - схематический вид в поперечном разрезе, взятый вдоль линии 29B- 29B' по (a).

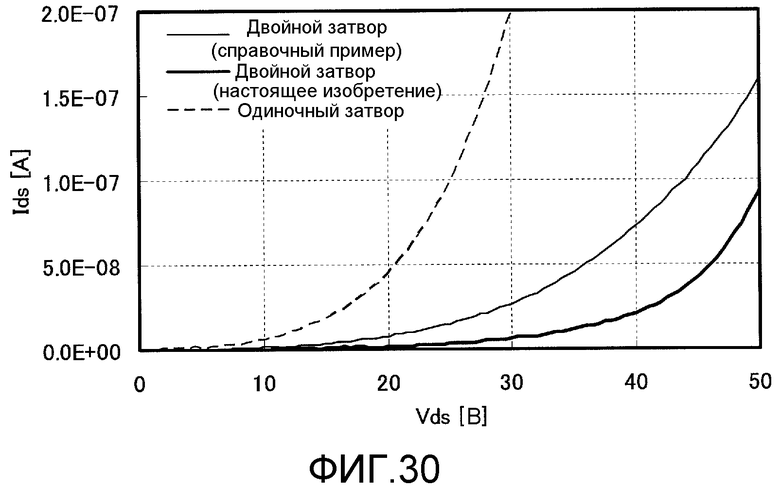

Фиг.30 - график, показывающий пример характеристик тока отключенного состояния тонкопленочного транзистора 710 и тонкопленочного транзистора 790.

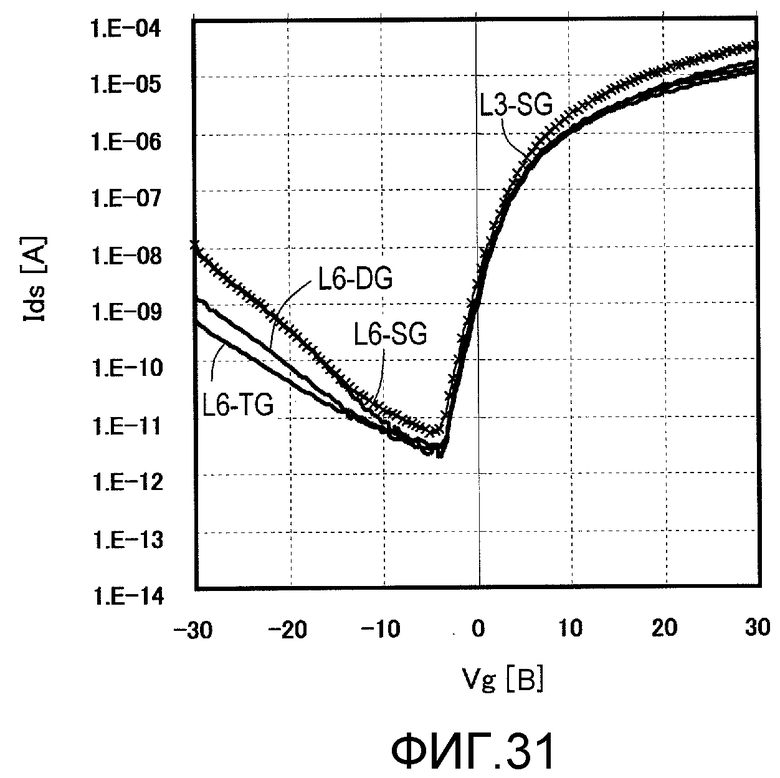

Фиг.31 - график, показывающий зависимость напряжения Vg (В) затвора и тока Ids (А) исток-сток для TFT, имеющих одноканальную структуру, двухканальную структуру и трехканальную структуру.

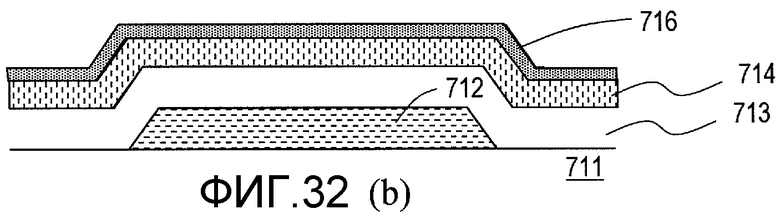

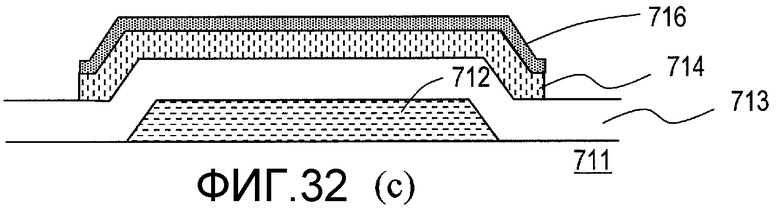

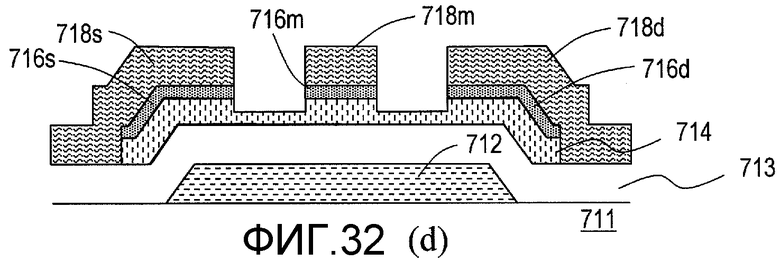

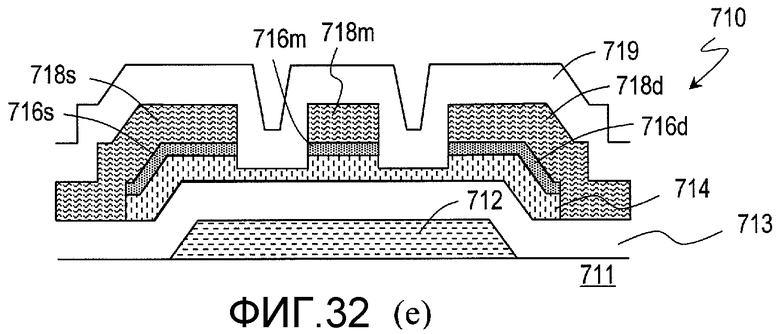

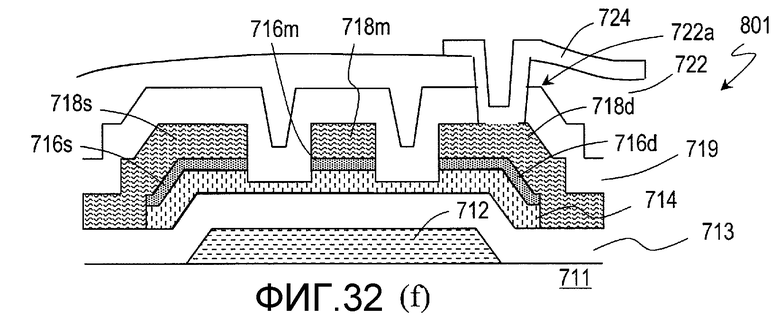

Фиг.32 (a)-(f) - схематические виды в поперечном разрезе, иллюстрирующие способ для изготовления подложки 801 активной матрицы, включающей в себя тонкопленочный транзистор 710.

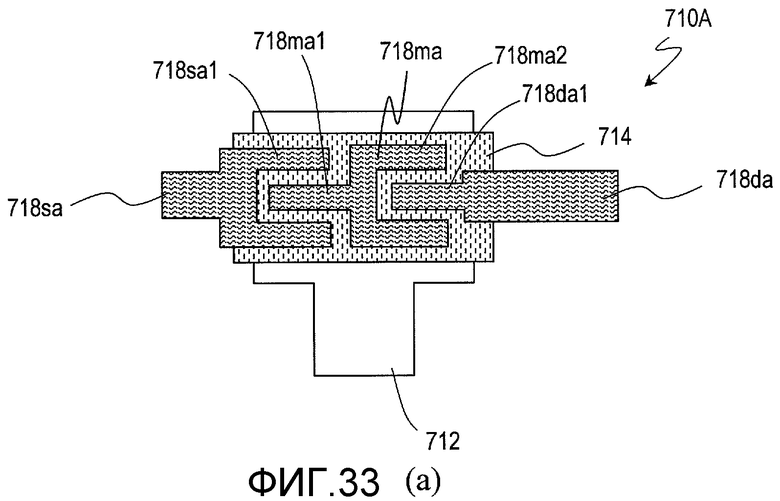

Фиг.33(a) - схематический вид с верху, показывающий тонкопленочный транзистор 710A по варианту осуществления настоящего изобретения, а (b) - схематический вид сверху, показывающий тонкопленочный транзистор 710B по варианту осуществления настоящего изобретения.

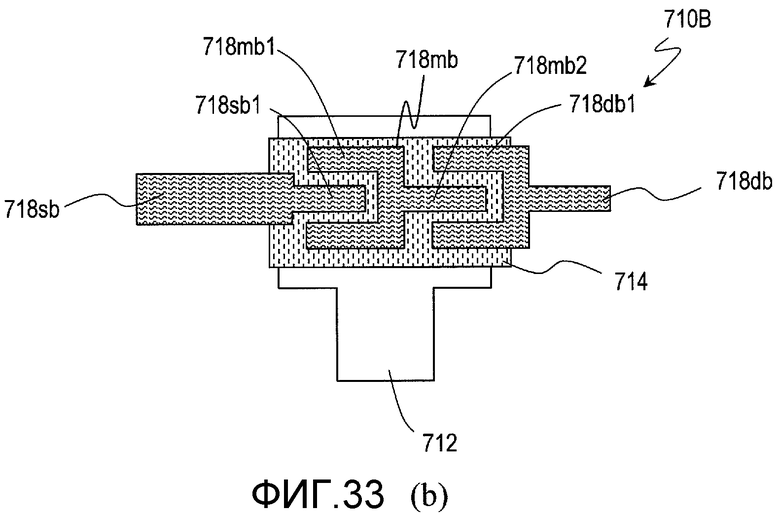

Фиг.34 - график, показывающий зависимость между напряжением Vg (В) затвора и током Ids (А) исток-сток для тонкопленочного транзистора 710A и тонкопленочного транзистора 710B.

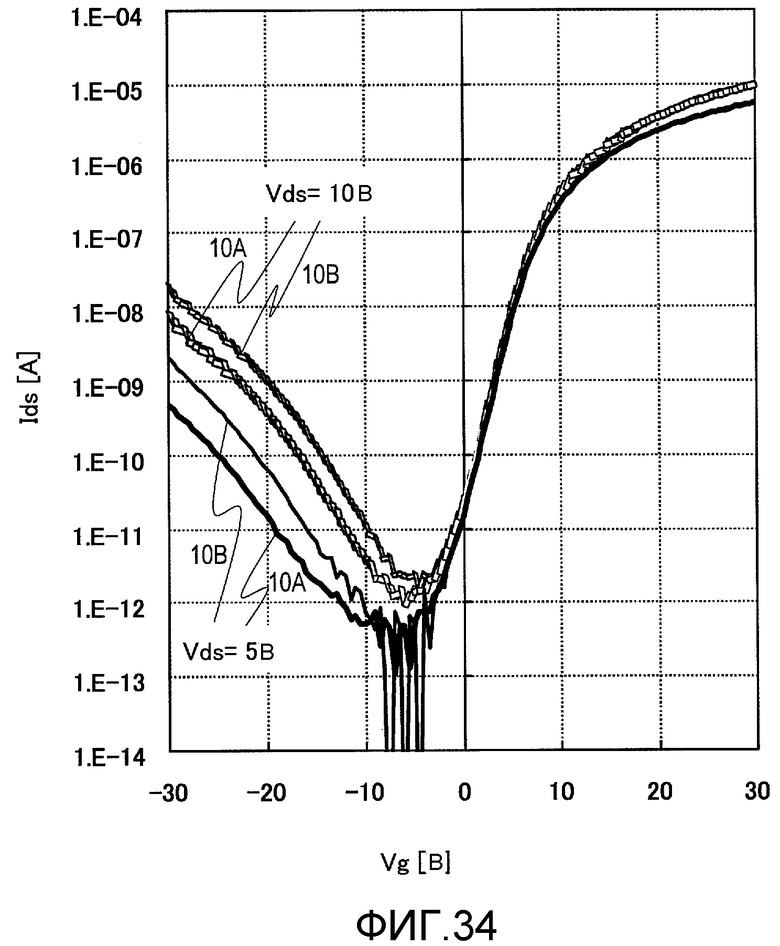

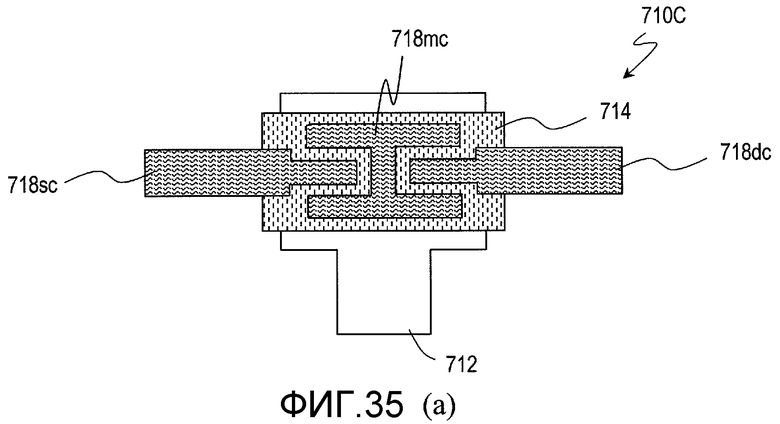

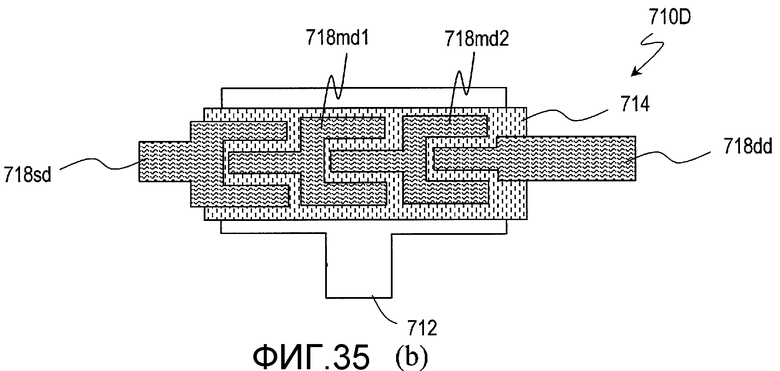

Фиг.35(a) - схематический вид с верху, показывающий тонкопленочный транзистор 710C по варианту осуществления настоящего изобретения, (b) - схематический вид сверху, показывающий тонкопленочный транзистор 710D по варианту осуществления настоящего изобретения, а (c) - схематический вид сверху, показывающий тонкопленочный транзистор 710E по варианту осуществления настоящего изобретения.

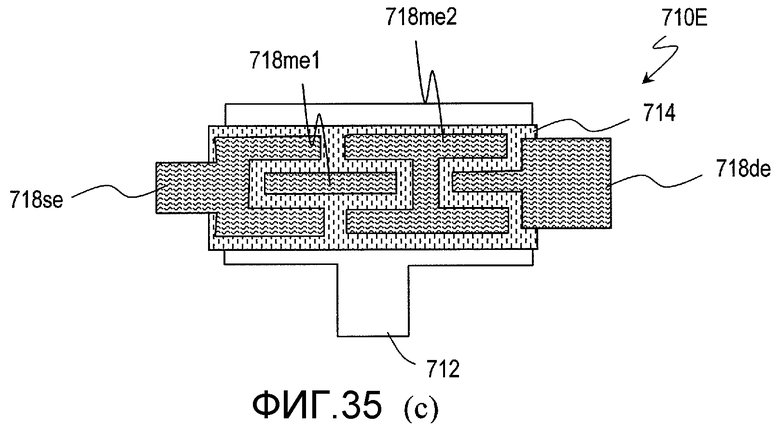

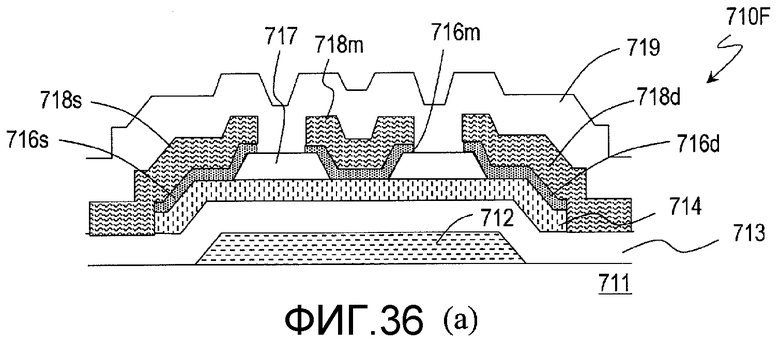

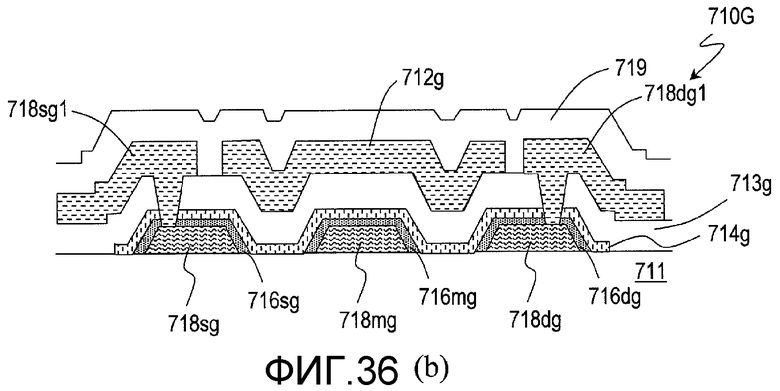

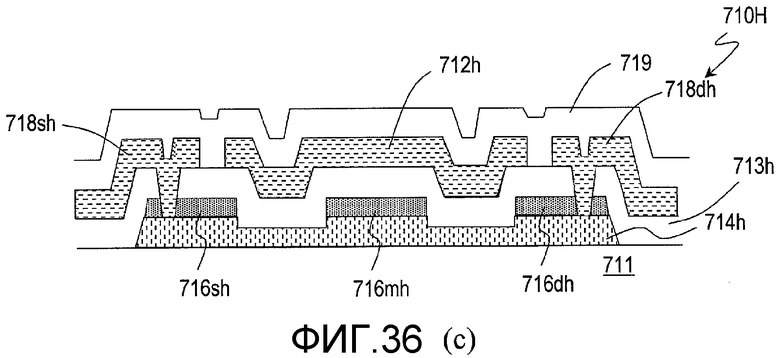

Фиг.36(a) - схематический вид с верху, показывающий тонкопленочный транзистор 710F по варианту осуществления настоящего изобретения, (b) - схематический вид сверху, показывающий тонкопленочный транзистор 710G по варианту осуществления настоящего изобретения, а (c) - схематический вид сверху, показывающий тонкопленочный транзистор 710H по варианту осуществления настоящего изобретения.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Полупроводниковое устройство по настоящему изобретению имеет схему, включающую в себя множество тонкопленочных транзисторов и по меньшей мере один диод. Тонкопленочные транзисторы, включенные в схему по настоящему изобретению все имеют одинаковый тип проводимости (все являются P-канальными TFT или все являются N-канальными TFT). В настоящем описании изобретения, такая схема указывается ссылкой как «схема, сформированная одноканальными TFT».

В настоящем изобретении, если тип проводимости множества тонкопленочных транзисторов, имеющих одинаковый тип проводимости, является N-типом, электрод катодной стороны по меньшей мере одного диода присоединяется к линии, которая присоединена к затвору одного из множества тонкопленочных транзисторов. Если тип проводимости множества тонкопленочных транзисторов является P-типом, электрод анодной стороны по меньшей мере одного диода присоединяется к линии, которая присоединена к затвору одного из множества тонкопленочных транзисторов. Другой диод, скомпонованный так, чтобы его направление протекания тока было противоположно по меньшей мере одному диоду, не сформирован на линии.

Настоящее изобретение широко применимо к схемам возбуждения и подложкам активной матрицы устройств отображения, или устройствам отображения, использующим таковые. Например, для относительно большого устройства отображения, такого как тонкий телевизор ЖКД (с жидкокристаллическим дисплеем), предпочтительно, чтобы полупроводниковая пленка, имеющая более низкую подвижность, чем поликремний, такая как пленка аморфного кремния, пленка микрокристаллического кремния и пленка IGZO, используется не только для пиксельных TFT, но также схемных TFT, используемых в периферийных схемах, таких как схемы возбуждения, но такие TFT типично являются одноканальными TFT. То есть, они являются N-канальными TFT или P-канальными TFT, и не образуют CMOS.

Далее, со ссылкой на чертежи, будут подробно описаны проблемы, которые должны быть решены настоящим изобретением.

Схема, сформированная одноканальными TFT, имеет проблему, что ток утечки отключенного состояния возрастает, и вероятно должна возникать некорректная работа, по сравнению со схемами, включающими в себя CMOS, используемые в LPS или однокристальных ИС. Причина является следующей. С CMOS, пороговое значение может регулироваться посредством использования этапа легирования. В противоположность, нормально, с одноканальным TFT, для того чтобы снижать себестоимость, этап легирования не выполняется, а потому, пороговое значение не может регулироваться. Таким образом, подпороговая область характеристик Id-Vg находится около Vg=0[В], и вероятно, что возникает утечка закрытого состояния.

Настоящие изобретатели провели исследования для обнаружения причины вышеприведенной проблемы и, как результат, обнаружили, что, когда положительный или отрицательный заряд подается на затвор одноканального TFT, пороговое значение TFT смещается в положительном или отрицательном направлении в зависимости от полярности заряда, приложенного к нему. Также было обнаружено, что с N-канальным одноканальным TFT, ток утечки отключенного состояния возрастает, только когда пороговое значение смещается в отрицательном направлении.

Фиг.3(a) и 3(b) - графики, показывающие результаты нагрузочных испытаний, при которых затвор N-канального TFT на аморфном кремнии заряжается положительным зарядом (Vg=20 В), и результаты нагрузочных испытаний, при которых затвор заряжается отрицательным зарядом (Vg=-20 В). При обоих нагрузочных испытаниях, напряжение исток-сток предполагается имеющим значение 0 В. Вертикальная ось графика представляет величину заряда (ΔVth) порогового значения Vth N-канального TFT на аморфном кремнии, а горизонтальная ось представляет время нагрузки. Величина ΔVth порогового значения является значением, полученным вычитанием порогового значения до прикладывания нагрузки из порогового значения после того, как приложена нагрузка, через предопределенный период времени.

Как может быть видно из результатов, показанных на фиг.3(a), когда положительный заряд прикладывается к затвору N-канального TFT на аморфном кремнии, пороговое значение смещается в положительном направлении, тем самым, увеличивая пороговое значение. С другой стороны, как показано на фиг.3(b), когда отрицательный заряд прикладывается к затвору, пороговое значение смещается в отрицательном направлении, тем самым, уменьшая пороговое значение.

Хотя ток утечки отключенного состояния затвора (ток утечки отключенного состояния) не увеличивается, когда пороговое значение TFT смещается в положительном направлении, ток утечки отключенного состояния затвора (ток утечки отключенного состояния) увеличивается, когда оно смещается в отрицательном направлении.

Фиг.4 - график, показывающий характеристики тока (Id) - напряжения (Vg) TFT на аморфном кремнии. Предполагается, что длина L канала TFT на аморфном кремнии имеет значение 4 мкм, ширина W канала имеет значение 24 мкм, напряжение Vd стока имеет значение 10 В, а напряжение VSS истока имеет значение -5 В. Предполагается, что температура измерения является комнатной температурой. По существу, никакого тока Id(off) не протекает, когда затвор находится в отключенном состоянии (Vg=VSS), до того, как смещается пороговое значение, как указано кривой 510. Однако, когда пороговое значение смещается в отрицательном направлении, ток Id(off) отключенного состояния затвора существенно возрастает, как указано кривой 512.

Когда ток Id(off) отключенного состояния затвора возрастает, схема, включающая в себя этот TFT, может работать некорректно. В тех случаях, когда схема по настоящему варианту осуществления является затворным формирователем, может быть возможным, что не выдается никакого сигнала. Наоборот, даже если пороговое значение смещается в положительном направлении, ток Id(off) отключенного состояния затвора не возрастает, и является маловероятным, что возникает некорректная работа схемы, обусловленная утечкой отключенного состояния.

На основании результатов исследования, описанных выше, настоящие изобретатели обнаружили, что в схеме, сформированной одноканальными TFT, TFT необходимо защищаться только от заряда, имеющего такую полярность, которая увеличивает ток утечки отключенного состояния TFT, и не нужно защищаться от заряда, имеющего другую полярность, таким образом, приходя к настоящему изобретению.

То есть, в полупроводниковом устройстве, имеющем схему, включающую в себя N-канальный TFT в качестве одноканального TFT по настоящему изобретению, необходимо формировать защитный диод (диод D2 в схеме защиты по фиг.1) только для подавления зарядки затвора N-канального TFT отрицательным зарядом. С другой стороны, в полупроводниковом устройстве, имеющем схему, включающую в себя P-канальный TFT в качестве одноканального TFT, необходимо формировать защитный диод (диод D1 в схеме защиты по фиг.1) только для подавления зарядки затвора P-канального TFT положительным зарядом. Поэтому, поскольку количество диодов для защиты от ESD может быть уменьшено на 1/2, можно уменьшать размер схемы от традиционных технологий наряду с предотвращением некорректной работы схем, обусловленной ESD. Когда применяется к схеме сдвигового регистра, который не включает в себя линию VDD, больше не нужно прокладывать трассу линии VDD с целью формирования схемы защиты от ESD, можно более эффективно уменьшать размер схемы.

(Первый вариант осуществления)

Первый вариант осуществления полупроводникового устройства по настоящему изобретению далее будет описан со ссылкой на чертежи.

Полупроводниковое устройство по настоящему изобретению имеет схему, включающую в себя множество TFT и защитный диод для защиты по меньшей мере одного из множества TFT от ESD. Множество TFT все являются N-канальными TFT или все являются P-канальными TFT (одноканальная конфигурация). Защитный диод предусмотрен на линии, которая присоединена к затвору TFT, который должен быть защищен.

Фиг.5(a) - схема, иллюстрирующая участок схемы 520 по настоящему варианту осуществления. Схема 520 включает в себя N-канальный тонкопленочный транзистор 522, линию 524, присоединенную к затвору тонкопленочного транзистора 522, линию 526 VDD и схему защиты, включающую в себя защитный диод D2. Защитный диод D2 имеет структуру, в которой, например, исток и затвор TFT закорочены друг на друга, и также указывается ссылкой как «диод типа TFT».

Фиг.6 - схематический вид в поперечном разрезе, иллюстрирующий защитный диод D2. Защитный диод D2 включает в себя электрод 530 затвора, полупроводниковый слой 534, сформированный на электроде 530 затвора, с пленкой 532 изоляции затвора, вставленной между ними, а также первый электрод 536 (электрод истока) и второй электрод 538 (электрод стока), электрически присоединенные к противоположным краям полупроводникового слоя 534. Предполагается, что ток течет с истока на сток. Контактный слой 540 сформирован между полупроводниковым слоем 534 и каждым из первого и второго электродов 536 и 538. Первый электрод 536 присоединен к электроду 530 затвора на контактном отверстии 542. Участок 544 (канальный участок) полупроводникового слоя 534, вставленного между двумя электродами 536 и 538, перекрывается с электродом 530 затвора. В защитном диоде D2, ток течет с первого электрода 536 на второй электрод 538 через канальный участок 544 полупроводникового слоя 534. В настоящем варианте осуществления, первый электрод 536 (анодная сторона) и электрод 530 затвора защитного диода D2 присоединены к линии 526 VSS, показанной на фиг.5(a), а второй электрод 538 (катодная сторона) присоединен к линии 524.

Фиг.5(a) вновь будет подвергнут ссылке. Как описано выше, поскольку тонкопленочный транзистор 522 имеет N-канал, если отрицательный бросок напряжения ESD прикладывается к затвору тонкопленочного транзистора 522, пороговое значение может смещаться в отрицательном направлении, тем самым, повышая утечку отключенного состояния. С этой схемой 520, когда отрицательный бросок напряжения ESD подается на линию 524, бросок напряжения ESD может шунтироваться защитным диодом D2 на линию 526 VSS, тем самым, подавляя увеличение утечки отключенного состояния, обусловленной прикладыванием отрицательного броска напряжения ESD к затвору тонкопленочного транзистора 522.

С другой стороны, когда положительный бросок напряжения ESD подается на линию 524, бросок напряжения ESD прикладывается непосредственно к затвору тонкопленочного диода 522, так как нет схемы защиты для шунтирования положительного заряда. В этом случае, однако, поскольку пороговое значение тонкопленочного транзистора 522 смещается в положительном направлении, утечка отключенного состояния не увеличивается вследствие смещения порогового значения.

Таким образом, с настоящим вариантом осуществления, можно подавлять увеличение утечки отключенного состояния тонкопленочного транзистора 522, обусловленной ESD. Несмотря на то, что два защитных диода разных направлений протекания тока предусмотрены для каждой линии при традиционных технологиях, с настоящим вариантом осуществления можно подавлять рост утечки отключенного состояния тонкопленочного транзистора 522 посредством предоставления одного защитного диода D2 для каждой линии 524, тем самым, уменьшая размер схемы от традиционных технологий.

Фиг.7 - график, иллюстрирующий характеристики защитного диода D2 по настоящему варианту осуществления. Горизонтальная ось графика представляет напряжение Vdiode (В) на защитном диоде D2, а вертикальная ось представляет ток (A), протекающий через защитный диод D2. Напряжение Vdiode выражается в качестве VSS-Vg (Vg: потенциал линии 24). В этом примере предполагается, что ширина W канала защитного диода D2 имеет значение 20 мкм, а длина L канала имеет значение 16 мкм.

Как может быть видно из фиг.7, когда отрицательный заряд подается на линию 524, тем самым, прикладывая положительное напряжение (VSS-Vg>0) защитного диода D2 (прямое смещение), ток протекает с первого электрода на второй электрод защитного диода D2, а потому, можно шунтировать отрицательный заряд с линии 524 на линию 256 VSS.

С другой стороны, если потенциал Vg находится в пределах рабочего диапазона напряжений (VSS≤Vg≤VDD) тонкопленочного транзистора 522, никакой ток не протекает через защитный диод D2, даже если отрицательное напряжение (VSS-Vg<0) прикладывается к защитному диоду D2 (обратное смещение).

Несмотря на то, что ширина W канала и длина L канала защитного диода D2 не ограничены конкретными значениями, типично предпочтительно, чтобы ширина W канала была большой (например, 10 мкм или больше), в каком случае, большая величина заряда может разряжаться, когда подается ESD. Более предпочтительно, ширина W канала имеет значение 20 мкм или большее. Если длина L канала велика (например, 5 мкм или более), велико сопротивление нагрузки, и можно подавлять утечку, возникающую через защитный диод D2 во время нормальной работы. С другой стороны, если ширина W канала и длина L канала слишком велики, это приводит к увеличению размера схемы, а потому, предпочтительно, чтобы ширина W канала имела значение 1000 мкм или меньше, а длина L канала имела значение 50 мкм или меньше.

Схема 520 по настоящему варианту осуществления может включать в себя P-канальный тонкопленочный транзистор вместо N-канального тонкопленочного транзистора 522. В этом случае, схема защиты, присоединенная к затвору P-канального тонкопленочного транзистора, включает в себя защитный диод D1, имеющий структуру, в которой сток и затвор закорочены друг на друга, как показано на фиг.5(b). Электрод катодной стороны (сток) защитного диода D1 присоединен к линии VDD, а электрод анодной стороны (исток) присоединен к линии 524', присоединенной к затвору P-канального тонкопленочного транзистора 522'. Схема защиты не включает в себя никакого диода, скомпонованного, так что его направление протекания тока является противоположным таковому у защитного диода D1. Таким образом, когда положительный бросок напряжения ESD прикладывается к линии 524', бросок напряжения ESD может шунтироваться на линию VDD, а потому, можно предохранять пороговое значение P-канального тонкопленочного транзистора от смещения в положительном направлении.

Схема 520 типично включает в себя множество TFT одинакового типа проводимости и схему защиты от ESD для защиты по меньшей мере одного из множества TFT от ESD. Схема защиты от ESD включает в себя защитный диод D2, который эффективен против ESD той полярности, которая увеличивает утечку в отключенном состоянии TFT, который должен защищаться, и не включает в себя защитный диод D1, который эффективен против ESD противоположной полярности. Схеме по настоящему варианту осуществления требуется включать в себя только по меньшей мере одну схему защиты, описанную выше, и схема защиты, описанная выше, может быть предусмотрена для каждого из двух или более TFT. Может быть TFT, защищенный схемой защиты, включающей в себя два защитных диода D1 и D2.

Настоящий вариант осуществления предпочтительно применяется к полупроводниковому устройству, включающему в себя схему, чьим пиковым значением напряжения является 20 В или более. С таким полупроводниковым устройством, пороговое значение TFT, включенного в схему, смещается на очень большие величины, а потому, можно получать особенно резко выраженный эффект, предусматривая схему защиты, описанную выше.

Схема 520 по настоящему варианту осуществления может быть сдвиговым регистром, который, например, сформирован (изготовленным за одно целое) монолитным с жидкокристаллической панелью отображения. Далее будет описана конфигурация сдвигового регистра по настоящему варианту осуществления.

Фиг.8(a) - схематический вид сверху жидкокристаллической панели 600 отображения по варианту осуществления настоящего изобретения, а фиг.8(b) показывает схематическую структуру одного пикселя. Фиг.8(a) показывает структуру подложки 601 активной матрицы жидкокристаллической панели 600 отображения и не показывает жидкокристаллический слой и противоположную подложку. Жидкокристаллическое устройство отображения получается посредством предоставления подсветки, источника питания, и т.д., в жидкокристаллической панели 600 отображения.

Затворный формирователь 610 и истоковый формирователь 620 формируются составляющими одно целое с подложкой 601 активной матрицы. Множество пикселей сформированы в области отображения жидкокристаллической панели 600 отображения, и области подложки 601 активной матрицы, соответствующие пикселям, обозначены номером 632 ссылки. Истоковый формирователь 620 не обязан формироваться составляющим одно целое с подложкой 601 активной матрицы. Отдельно изготовленная ИС истокового формирователя, или тому подобное, может быть установлено известным способом.

Как показано на фиг.8(b), подложка 601 активной матрицы включает в себя пиксельный электрод 601P, соответствующий одному пикселю жидкокристаллической панели 600 отображения. Пиксельный электрод 601P присоединен к истоковой магистральной линии 601S через пиксельный TFT 601T. Электрод затвора TFT 601T присоединен к затворной магистральной линии 601G.

Выход затворного формирователя 610 присоединен к затворной магистральной линии 601G, и затворные магистральные линии 601G сканируются последовательным по линиям образом. Выход истокового формирователя 620 присоединен к истоковой магистральной линии 601S, и напряжение сигнала отображения (напряжение шкалы яркостей) подается на него.

Затем, фиг.9 - структурная схема, иллюстрирующая конфигурацию сдвигового регистра 610B, включенного в затворный формирователь 610. Сдвиговый регистр 610B поддерживается изолирующей подложкой, такой как стеклянная подложка, формирующая подложку 601 активной матрицы. TFT, образующие сдвиговый регистр 610B, предпочтительно формируются одним и тем же технологическим процессом с пиксельными TFT 601T, сформированными в области отображения подложки 601 активной матрицы.

Фиг.9 схематически показывает только пять каскадов с n-2 по n+2 из множества каскадов сдвигового регистра 610B. Множество каскадов имеют по существу идентичную структуру и каскадно включены. Выход из каждого каскада сдвигового регистра 610B выдается на одну затворную магистральную линию 601G жидкокристаллической панели 600 отображения. Такой сдвиговый регистр 610B, например, описан в выложенной публикации № 8-87893 патента Японии. Раскрытие выложенной публикации № 8-87893 патента Японии включено в материалы настоящей заявки посредством ссылки.

Фиг.10 - принципиальная схема, показывающая конфигурацию, используемую в одном из каскадов сдвигового регистра 610B, и фиг.11 показывает формы сигнала у входных/выходных сигналов и форму сигнала напряжения netA каждого каскада сдвигового регистра 610B. Фиг.12 показывает формы сигнала выходных сигналов из пяти каскадов с n-2 по n+2 сдвигового регистра 610B. Как показано на фиг.12, сдвиговый регистр 610B последовательно выдает выходные сигналы Gout из каскадов.

Как показано на фиг.10, каждый каскад сдвигового регистра 610B включает в себя первый транзистор MG для выдачи выходного сигнала Gout, и множество вторых транзисторов (MHd, MKd, MMd и MNd), чья область истока или область стока электрически присоединены к электроду затвора первого транзистора MG. На фиг.10, первый транзистор MG является так называемым нагрузочным транзистором, а линия, присоединенная к электроду затвора первого транзистора MG, указывается ссылкой как netA. В настоящем варианте осуществления, эти транзисторы все являются N-канальными тонкопленочными транзисторами. Диод D2a (защитный диод) для защиты от ESD предусмотрен на линии 550, присоединенной к затвору второго транзистора MKd. Конфигурация защитного диода D2a может быть подобной конфигурации, описанной выше со ссылкой на фиг.6. Электрод катодной стороны защитного диода D2a присоединен к линии 550, а электрод анодной стороны присоединен к заземлению или VSS.

Выходной сигнал Gout выдается с каждого каскада на затворную магистральную линию 601G только во время периода записи пикселя. Что касается одного каскада, конфигурация такова, что потенциал Gout зафиксирован в VSS на большей части одного периода кадра (периода, в течение которого все затворные магистральные линии 601G последовательно выбираются, и до тех пор, пока не выбрана предметная затворная магистральная линия).

Посредством сигнала S (выходного сигнала Gout(n-1) предыдущего каскада, netA предварительно заряжается. В таком случае, транзисторы MHd, MKd и MNd, чьи область истока или область стока присоединены к netA, находятся в отключенном состоянии.

Затем, когда тактовый сигнал CK является высоким, netA поднимается. Затем, входной сигнал Gout(n) выдается на (nуюзатворную магистральную линию 601G, таким образом, включая пиксельный TFT 601T, присоединенный к затворной магистральной линии 601G, и подавая напряжение сигнала отображения на пиксельный электрод 601P с истоковой магистральной линии 601S. То есть, жидкокристаллический конденсатор, сформированный пиксельным электродом 601P, противоэлектродом (не показан) и жидкокристаллическим слоем (не показан) между ними, заряжается.

После этого, посредством сигнала R сброса (выходным сигналом Gout (n+1) следующего каскада), потенциалы netA и Gout опускаются до VSS.

В течение периода, в котором выходной сигнал Gout (n) не выводится, netA и потенциал Gout зафиксированы на VSS транзистором MKd и транзистором ML, соответственно, с использованием тактового сигнала CK и тактового сигнала CKB.

Здесь, конденсатор CAP1 поддерживает потенциал netA и содействует выходу. Транзистор MJ приводит потенциал выходного сигнала Gout в низкое состояние в ответ на сигнал R сброса. Транзистор ML приводит потенциал выходного сигнала Gout в низкое состояние в ответ на тактовый сигнал CKB. Один раз за кадр (период вертикального сканирования), сигнал CLR очистки подается на все каскады сдвигового регистра, чтобы перевести netA в низкое состояние для всех каскадов во время интервала гашения обратного хода кадровой развертки (интервала от того, когда осуществляет вывод оконечный каскад сдвигового регистра, до того когда осуществляет вывод первый каскад). Отметим, что сигнал CLR очистки также служит в качестве сигнала сброса для оконечного каскада сдвигового регистра.

С установкой защитного диода D2a, настоящий вариант осуществления имеет следующие преимущества.

С целью сравнения, фиг.13 показывает схему (схему справочного примера), имеющую конфигурацию, подобную таковой у схемы, показанной на фиг.10, за исключением того, что отсутствует защитный диод D2a. Ради простоты, элементы, подобные фиг.10, обозначены сходными номерами ссылки и не будут дополнительно описаны ниже. Схема по справочному примеру, показанная на фиг.13, описана в заявке № 2008-297297 на выдачу патента Японии настоящего заявителя (неопубликованной). Раскрытие заявки № 2008-297297 на выдачу патента Японии включено в материалы настоящей заявки посредством ссылки.

Схема по справочному примеру легко подвергается влиянию внешнего ESD, поскольку второй транзистор MKd (N-канальный TFT) для самонастройки netA присоединен непосредственно к внешнему сигналу CK. Если отрицательный бросок напряжения ESD прикладывается с линии 550 к второму транзистору MKd, утечка отключенного состояния второго транзистора MKd возрастает, тем самым, повышая вероятность, что схема работает некорректно.

В противоположность, с настоящим вариантом осуществления, поскольку защитный диод D2a предусмотрен на линии 550, как показано на фиг.10, даже если отрицательный бросок напряжения ESD подается на линию 550, отрицательный бросок напряжения ESD шунтируется на внешнюю схему через защитный диод D2a и не прикладывается ко второму транзистору MKd. Поэтому, можно сдерживать увеличение утечки отключенного состояния второго транзистора MKd, и можно предохранять схему от некорректной работы вследствие ESD.

Диод, который дает току течь в направлении, противоположном направлению протекания тока защитного диода D2a, не предусмотрен на линии 550. Если пытаются дополнительно предусмотреть диод для обеспечения протекания тока в противоположном направлении на линии 550, необходимо не только сформировать такой диод, но также проложить трассу линии VDD, которая не используется в этой схеме, в качестве линии, на которую шунтируется заряд (положительный заряд) с линии 550 через диод. Таким образом, размер схемы значительно возрастает. В противоположность, в настоящем варианте осуществления, поскольку необходимо формировать только один защитный диод D2a на линии 550, можно надлежащим образом защищать линию 550 и второй транзистор MKd от ESD наряду с подавлением увеличения размера схемы.

В схеме по настоящему варианту осуществления, транзистор, который должен защищаться защитным диодом, не ограничен вторым транзистором MKd. Можно предусматривать защитный диод для защиты других транзисторов вместо второго транзистора MKd или в дополнение к второму транзистору MKd.

Еще один пример схемы по настоящему варианту осуществления далее буде описан со ссылкой на фиг.14-18.

В схеме, показанной на фиг.14, защитный диод D2b предусмотрен на линии 552, присоединенной к затвору второго транзистора MHd. Электрод катодной стороны защитного диода D2b присоединен к линии 552, а электрод анодной стороны присоединен к заземлению или VSS.

В схеме по справочному примеру, показанному на фиг.13, второй транзистор MHd для опускания потенциала с netA, присоединен непосредственно к внешнему сигналу R, а потому, легко подвергается влиянию ESD, подаваемого извне. Когда отрицательный бросок напряжения ESD прикладывается к второму транзистору MHd с линии 552, утечка отключенного состояния транзистора MHd возрастает. Как результат, напряжение на выходном транзисторе MG снижается, что может заставлять схему работать некорректно. В противоположность, в примере, показанном на фиг.14, поскольку защитный диод D2b предусмотрен на линии 552, можно сдерживать прикладывание отрицательного броска напряжения ESD к транзистору MHd с линии 552. Поэтому, можно предохранять схему от некорректной работы вследствие ESD.

На схеме, показанной на фиг.15, защитный диод D2c предусмотрен на линии 554, присоединенной к затвору транзистора ML. Электрод катодной стороны защитного диода D2c присоединен к линии 554, а электрод анодной стороны присоединен к заземлению или VSS.

В схеме по справочному примеру (фиг.13), транзистор ML присоединен непосредственно к внешнему сигналу CKB, а потому, легко подвергается влиянию ESD, подаваемого извне. В противоположность, в примере, показанном на фиг.15, защитный диод D2c предусмотрен на линии 554, а потому, можно сдерживать прикладывание отрицательного броска напряжения ESD, подаваемого на линию 554, от прикладывания к транзистору ML. Поэтому, можно сдерживать увеличение утечки отключенного состояния транзистора ML, обусловленное ESD.

На схеме, показанной на фиг.16, защитный диод D2d предусмотрен на линии 556, присоединенной к затвору транзистора MNd. Электрод катодной стороны защитного диода D2d присоединен к линии 556, а электрод анодной стороны присоединен к заземлению или VSS.

В схеме по справочному примеру (фиг.13), второй транзистор MNd присоединен непосредственно к внешнему сигналу CLR, а потому, легко подвергается влиянию ESD, подаваемого извне. В противоположность, в примере, показанном на фиг.16, защитный диод D2b предусмотрен на линии 554, а потому, можно сдерживать прикладывание отрицательного броска напряжения ESD, подаваемого на линию 554, от прикладывания ко второму транзистору MNd. Поэтому, можно сдерживать увеличение утечки отключенного состояния транзистора MNd, обусловленное ESD.

На схеме, показанной на фиг.17, защитный диод D2e предусмотрен на линии netA, присоединенной к затвору выходного транзистора MG. Электрод катодной стороны защитного диода D2e присоединен к netA, а электрод анодной стороны заземлен.

Если утечка отключенного состояния выходного транзистора MG увеличивается вследствие ESD, форма сигнала выхода Gout может быть притупленной, или выходной транзистор MG может претерпевать неудачу в том, чтобы включаться. В примере, показанном на фиг.17, поскольку защитный диод D2 предусмотрен между выходным транзистором MG и вторым транзистором MHd на netA, можно подавлять прикладывание броска напряжения ESD к выходному транзистору MG и предотвращать вышеприведенную проблему, которая обусловлена увеличением утечки отключенного состояния выходного транзистора MG.

Схема по настоящему варианту осуществления может включать в себя один из защитных диодов с D2a по D2e или может включать в себя множество защитных диодов. Из защитных диодов с D2a по D2e, эффект защиты от ESD является более высоким в порядке защитных диодов D2a, D2b, D2c, D2d и D2e. Как показано на фиг.18, могут присутствовать все защитные диоды с D2a по D2e, описанные выше. Таким образом, можно более эффективно предотвращать некорректную работу схемы, обусловленную ESD.

В тех случаях, когда схема по настоящему варианту осуществления имеет одноканальную конфигурацию PMOS, защитный диод (защитный диод D1, показанный на фиг.1) может быть предусмотрен на по меньшей мере одной из линий с 550 по 558, так что положительный заряд может шунтироваться.

Предпочтительно, чтобы транзистор и защитный диод, включенные в схему по настоящему варианту осуществления, формировались посредством использования одной и той же полупроводниковой пленки. Полупроводниковая пленка может быть пленкой аморфного кремния, пленкой микрокристаллического кремния, металл-оксид-полупроводниковой пленкой (например, пленкой IGZO), и т. д.

В вышеприведенном примере, вторые транзисторы MHd, MKd, MMd и MNd имеют многоканальную структуру (в материалах настоящей заявки, двухканальную структуру), но они, взамен, имеют одноканальную структуру. В частности, в тех случаях, когда этим транзисторы сформированы посредством использования пленки микрокристаллического кремния, предпочтительно, чтобы эти транзисторы имели многоканальную структуру (двухканальную структуру в вышеприведенном примере). Далее будет описана причина для этого.

Если netA поднимается, большое напряжение (Vds) прикладывается между истоком и стоком второго транзистора (в отключенном состоянии), чей исток или сток присоединены к netA. Напряжение netA, являющееся поднятым, снижается вследствие тока утечки второго транзистора, чей исток или сток присоединен к netA, до того, как оно падает в ответ на тактовый сигнал CK (низкий), как это предполагается. По мере того, как напряжение netA снижается, выходной сигнал Gout не переключается в высокое состояние, или форма сигнала у выходного сигнала Gout притупляется, претерпевая неудачу в том, чтобы подавать достаточное напряжение на пиксельный электрод, таким образом, снижая качество отображения.

В тех случаях, когда сдвиговый регистр сформирован посредством использования TFT на микрокристаллическом кремнии, имеющего одноканальную структуру, поскольку эти TFT имеют относительно большой ток утечки, такие дефекты, как описанные выше, должны происходить более вероятно вследствие тока утечки. В противоположность, поскольку ток утечки в подпороговой области TFT на микрокристаллическом кремнии, который имеет многоканальную структуру, является меньшим, чем у TFT на микрокристаллическом кремнии, который имеет одноканальную структуру, можно ослаблять притупление формы сигнала netA и выходного сигнала Gout.

Если двухканальная структура применяется для по меньшей мере одного TFT из множества вторых транзисторов, ток утечки может уменьшаться для по меньшей мере одного транзистора. В тех случаях, когда двухканальная структура применяется для некоторых TFT из множества вторых транзисторов, предпочтительно, чтобы двухканальная структура применялась для транзисторов MHd, ML и MMd, у которых напряжение Vds исток-сток является наивысшим. Электрод затвора транзистора MHd присоединен к выходу предыдущего каскада (Gout(n-1)), а его электрод истока или электрод стока присоединен к электроду затвора выходного транзистора MG (netA) или VSS. Электрод затвора транзистора MNd присоединен к линии тактового сигнала CK, а его электрод истока или электрод стока присоединен к электроду затвора выходного транзистора MG (netA) или VSS. Транзистор MMd имеет свой электрод затвора и электрод истока присоединенными друг к другу (диодное соединение), и выход (сигнал S) предыдущего каскада подается на его электрод затвора. Электрод стока транзистора MMd присоединен к электроду затвора транзистора MG (netA). Понятно, что многоканальная структура предпочтительно применяется для всех из множества вторых транзисторов ввиду характеристик.

«Пленка микрокристаллического кремния» означает пленку, имеющую смешанное состояние между кристаллической фазой микрокристаллических частиц и аморфной фазой. Объемный процент аморфной фазы в пленке микрокристаллического кремния, например, может регулироваться в диапазоне от 5% или более и 95% или менее. Объемный процент аморфной фазы предпочтительно имеет значение 5% или более и 40% или менее, и можно эффективно улучшать отношение включенного состояния/отключенного состояния TFT, так как в этом диапазоне можно получать желательную пленку микрокристаллического кремния с небольшим дефектом пленки. Когда рамановская спектроскопия рассеяния, использующая видимый свет, выполняется на пленке микрокристаллического кремния, спектр имеет наивысший пик на длине волны 520 cm-1, который является пиком кристаллического кремния, и имеет широкий пик на длине волны 480 cm-1, который является пиком аморфного кремния. Пиковая высота аморфного кремния около 480 cm-1, например, имеет значение 1/30 или более и 1 или менее пиковой высоты кристаллического кремния, видимого около 520 cm-1.

С целью сравнения, когда рамановская спектроскопия рассеяния выполняется на пленке поликристаллического кремния, никакой аморфный компонент почти не обнаруживается, причем, пиковая высота для аморфного кремния является по существу нулевой. Есть случаи, где аморфная фаза остается локально зависящей от условий кристаллизации при формировании пленки поликристаллического кремния, но даже в таких случаях, объемный процент аморфной фазы в пленке поликристаллического кремния обычно является меньшим, чем 5% с пиковой высотой для аморфного кремния при рамановской спектроскопии рассеяния, обычно являющейся меньшей, чем 1/30 пиковой высоты для поликристаллического кремния.

Такая пленка микрокристаллического кремния может формироваться посредством способа CCP (плазменного с емкостной связью) или способа плазменного CVD высокой плотности, такого как ICP (плазменного с индуктивной связью). Отношение пиковых интенсивностей, описанное выше, может настраиваться схемой устройства плазменного CVD и условиями осаждения.

Как описано выше, принимая во внимание полярность броска напряжения ESD и направление, в котором смещается пороговое значение TFT вследствие броска напряжения ESD, настоящий вариант осуществления предусматривает схему защиты, которая эффективна только против броска напряжения ESD, имеющего такую полярность, которая увеличивает ток утечки отключенного состояния TFT, и не предусматривает схему защиты, которая эффективна против броска напряжения ESD другой полярности. Поэтому, можно снижать сокращать количество схем защиты и уменьшать размеры схемы.

Конфигурация схемы сдвигового регистра по настоящему варианту осуществления не ограничена показанными на фиг.10 и 14-18. Настоящий вариант осуществления также применим к другим сдвиговым регистрам, например, проиллюстрированным в заявке № 2008-297297 на выдачу патента Японии. К тому же, в других сдвиговых регистрах, можно получать результаты, подобные описанным выше, особенно, предусматривая защитный диод по настоящему варианту осуществления в тонкопленочном транзисторе, присоединенном непосредственно к внешнему сигналу.

Схема по настоящему варианту осуществления не ограничена сдвиговыми регистрами. Например, настоящий вариант осуществления применим к DAC (цифро-аналоговым преобразователям), TG, защелкам, схемам источника питания, с которыми можно получать результаты, подобные описанным выше.

[Другие конфигурации защитного диода]

Конфигурация защитного диода по настоящему варианту осуществления не ограничена описанной выше со ссылкой на фиг.6. Например, в тех случаях, когда полупроводниковый слой защитного диода формируется посредством использования полупроводниковой пленки, имеющей более высокую подвижность чем аморфный кремний (например, пленки микрокристаллического кремния, металл-оксид-полупроводниковой пленки), ток легче протекает через полупроводниковый слой, и ток может протекать через защитный диод, возможно даже в время нормальной работы. Для того чтобы предотвратить такую проблему, область низкого сопротивления, которая будет описана ниже, может формироваться в полупроводниковом слое.

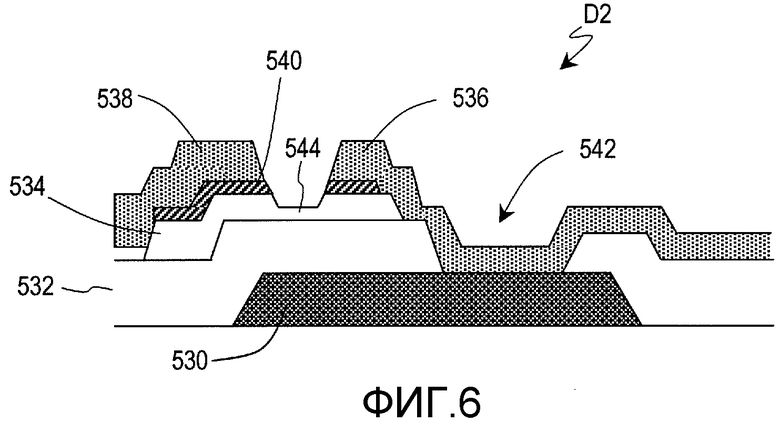

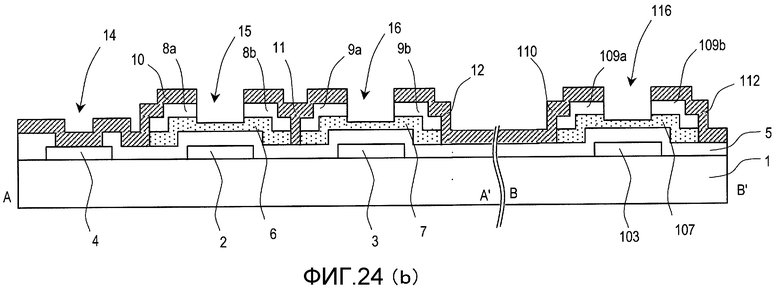

Фиг.19 - схема, иллюстрирующая полупроводниковое устройство, включающее в себя другой защитный диод по настоящему варианту осуществления, при этом, фиг.19(a) - вид сверху полупроводникового устройства, а фиг.19(b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по фиг.1(a).

Полупроводниковое устройство по настоящему варианту осуществления включает в себя подложку 1, а также диод 201 и тонкопленочный транзистор 301, сформированные на подложке 1. Диод 201 и тонкопленочный транзистор 301 сформированы посредством использования одной и той же полупроводниковой пленки. Тонкопленочный транзистор 301, например, является вторым транзистором сдвигового регистра, а диод 201 является защитным диодом для защиты второго транзистора от ESD.

В материалах настоящей заявки, полупроводниковая пленка формируется посредством использования пленки микрокристаллического кремния. Тонкопленочный транзистор 301 является обратносмещенным TFT с вытравленным каналом, который имеет структуру с нижним затвором, а диод 201 является обратносмещенным TFT с вытравленным каналом, который имеет структуру с нижним затвором, с электродом затвора и электродом истока, присоединенными друг к другу.

Тонкопленочный транзистор 301 включает в себя электрод 103 затвора, сформированный на подложке 1, слой 5 изоляции затвора, сформированный с тем чтобы покрывать электрод 103 затвора, слой 107 микрокристаллического кремния, сформированный на слое 5 изоляции затвора, электрод 110 истока, сформированный на слое 107 микрокристаллического кремния, с контактным слоем 109a, вставленным между ними, и электрод 112 стока, сформированный на слое 107 микрокристаллического кремния, с контактным слоем 109b, вставленным между ними.

Слой 107 микрокристаллического кремния включает в себя канальную область 107c, а также первую область 107a и вторую область 107b, расположенные на противоположных сторонах канальной области 107c. Первая область 107a электрически присоединена к электроду 110 истока контактным слоем 109a. Вторая область 107b электрически присоединена к электроду 112 стока контактным слоем 109b. Участок 116 зазора сформирован в канальной области 107c.

Диод 201 включает в себя электрод 2 затвора, проводящий слой и соединительную линию 4, сформированную на подложке 1, слой 5 изоляции затвора, сформированный, с тем чтобы покрывать электрод 2 затвора и соединительную линию 4, слой 6 микрокристаллического кремния, размещенный на слое 5 изоляции затвора, с тем чтобы перекрываться с электродом 2 затвора, слой 7 микрокристаллического кремния, размещенный на слое 5 изоляции затвора, с тем чтобы перекрываться с проводящим слом 3, первый электрод 10 (электрод истока), сформированный на слое 6 микрокристаллического кремния, с контактным слоем 8a, вставленным между ними, промежуточный электрод 11, сформированный на слоях 6 и 7 микрокристаллического кремния, с контактными слоями 8b и 9a, вставленными между ними, и второй 12 (электрод стока), сформированный на слое 7 микрокристаллического кремния с контактным слоем 9b, вставленным между ними.

Слой 6 микрокристаллического кремния включает в себя канальную область 6c, а также первую область 6a и промежуточную область 6b, расположенные на противоположных сторонах канальной области 6c. Первая область 6a электрически присоединена к электроду 10 истока контактным слоем 8a. Промежуточная область 6b электрически присоединена к промежуточному электроду 11 контактным слоем 8b. Подобным образом, слой 7 микрокристаллического кремния включает в себя область 7d, которая служит в качестве резистора (в дальнейшем, указываемую ссылкой как «резистивная область»), а также промежуточную область 7a и вторую область 7b, расположенные на противоположных сторонах резистивной области 7d. Промежуточная область 7a электрически присоединена к промежуточному электроду 11, с контактным слоем 9a, вставленным между ними. Вторая область 7b электрически присоединена к электроду 12 стока, с контактным слоем 9b, вставленным между ними. Участки 15 и 16 зазора сформированы в канальной области 6c и резистивной области 7d.

В настоящем варианте осуществления, электрод 2 затвора, проводящий слой 3 и соединительная линия 4 сформированы одной и той же проводящей пленкой. Электрод 2 затвора размещен, с тем чтобы перекрываться с канальной областью 6c слоя 6 микрокристаллического кремния, и управляет проводимостью канальной области 6c. Электрод 2 затвора присоединен к соединительной линии 4, а соединительная линия 4 электрически присоединена к электроду 10 истока на контактном отверстии 14, которое является проемом, предусмотренным в слое 5 изоляции затвора. Хотя не показано на фигурах, электрод 2 затвора и соединительная линия 4 электрически присоединены к электроду 103 затвора тонкопленочного транзистора 301.

С другой стороны, проводящий слой 3 размещен, с тем чтобы перекрываться со слоем 7 микрокристаллического кремния, то есть, так, чтобы он мог управлять проводимостью резистивной области 7d. Отметим, однако, что проводящий слой 3 не присоединен к другим электродам и линиям, таким как электрод 10 истока, но является плавающим.

Слои 107, 6 и 7 микрокристаллического кремния в тонкопленочном транзисторе 301 и диоде 201 включают в себя множество столбчатых микрокристаллических частиц и границы зерен кристаллов аморфной фазы. Объемный процент аморфной фазы в слоях 107, 6 и 7 микрокристаллического кремния, например, имеет значение от 5% до 40%. Пиковая высота для аморфной фазы при рамановской спектроскопии рассеяния имеет значение от 1/3 до 1/10 пиковой высоты для микрокристаллического участка. Слой аморфного кремния или слой поликристаллического кремния может использоваться в качестве активного слоя вместо слоев 107, 6 и 7 микрокристаллического кремния. Пленка, изготовленная из металл-оксид-полупроводника, такого как полупроводниковая пленка Zn-O (ZnO), полупроводниковая пленка In-Ga-Zn-O (IGZO), полупроводниковая пленка In-Zn-O (IZO) и полупроводниковая пленка Zn-Ti-O (ZTO), может использоваться в качестве активного слоя.

Контактные слои 109a, 109b, 8a, 8b, 9a и 9b в тонкопленочном транзисторе 301 и диоде 201 предусмотрены, для того чтобы улучшать электрическую проводимость между слоями 107, 6 и 7 микрокристаллического кремния и соответствующими электродами 110, 112, 10, 11 и 12. В настоящем варианте осуществления, эти контактные слои формируются одной и той же пленкой кремния n+-типа. Эти контактные слои каждый может быть одиночным слоем из слоя поликристаллического кремния, слоя микрокристаллического кремния, слоя аморфного кремния, или тому подобного, или могут иметь слоистую структуру, включающую в себя по меньшей мере один из этих слоев. В тех случаях, где пленка металл-оксид-полупроводника используется вместо слоя микрокристаллического кремния в качестве активного слоя, никакой контактный слой может не использоваться.

Пассивация 13 предусмотрена на верхнем участке электродов 110, 112, 10, 11 и 12 в тонкопленочном транзисторе 301 и диоде 201, с тем чтобы покрывать участки 116, 15 и 16 зазора и окружающую зону. Пассивация 13 может быть пленкой неорганического материала, такого как нитрид кремния, органической пленкой, такой как акриловый полимер или их слоистая пленка.

Хотя не показано на фигурах, проем, через который электрический сигнал, такой как предопределенное напряжение подается на электроды 110 и 10 истока и электроды 112 и 12 стока, может быть предусмотрен по необходимости в пассивации 13 посредством способа, такого как фотолитография. Электроды 110 и 10 истока и электроды 112 и 12 стока могут иметь конфигурацию, такую что электрический сигнал может вводиться извне посредством надлежащего соединения с проемами и соединительными линиями.

Далее будет описана работа тонкопленочного транзистора 301 и диода 201.

В тонкопленочном транзисторе 301, ток протекает, главным образом, между электродом 110 истока и электродом 112 стока, когда сопротивление канальной области 107c достаточно уменьшено напряжением, приложенным к электроду 103 затвора. Затем, ток протекает через первую область 107a, канальную область 107c и вторую область 107b слоя 107 микрокристаллического кремния с электрода 110 истока через контактный слой 109a. Затем он течет через контактный слой 109b, чтобы достичь электрода 112 стока.

В диоде 201, ток протекает, главным образом, между электродом 10 истока и электродом 12 стока, когда сопротивление канальной области 6c достаточно уменьшено напряжением, приложенным к электроду 2 затвора. Затем, ток протекает через первую область 6a, канальную область 6c и промежуточную область 6b слоя 6 микрокристаллического кремния с электрода 10 истока через контактный слой 8a. Затем он течет через контактный слой 8b, чтобы достичь промежуточного электрода 11. Подобным образом, после промежуточного электрода 11, он течет через контактный слой 9a сквозь промежуточную область 7a, резистивную область 7d и вторую область 7b слоя 7 микрокристаллического кремния в этом порядке, а затем, он протекает через контактный слой 9b, чтобы достичь электрода стока.

Как описано выше, проводящий слой 3 под слоем 7 микрокристаллического кремния не присоединен к другим электродам или линиям, а потому, никакое напряжение не прикладывается непосредственно к проводящему слою 3. Таким образом, первая область 7a, резистивная область 7d и вторая область 7b слоя 7 микрокристаллического кремния всегда имеет высокие значения сопротивления и служит в качестве резисторов, но не в качестве коммутационных элементов. В диоде 201, поскольку такие резисторы расположены между электродом 10 истока и электродом 12 стока, сопротивление между ними (сопротивление включенного состояния) может быть увеличено. Поэтому, даже когда диод 201 формируется посредством использования микрокристаллического кремния, имеющего высокую подвижность, можно предохранять ток от чрезмерного протекания через диод 201. Поэтому, диод 201, например, может использоваться подходящим образом в применениях, таких как диод для короткозамкнутого кольца.

Несмотря на то, что слой 7 микрокристаллического кремния на стороне электрода 12 стока не перекрывается с электродом 2 затвора на фиг.19, результаты, подобные описанным выше, также могут получаться, когда слой 7 микрокристаллического кремния перекрывается с электродом 2 затвора, и слой 6 микрокристаллического кремния на стороне электрода 10 истока не перекрывается с электродом 2 затвора. То есть, результаты, подобные описанным выше, могут получаться даже с конфигурацией, где электрод 2 затвора и проводящий слой 3 меняются по кругу.

Несмотря на то, что полупроводниковый слой (активный слой) тонкопленочного транзистора и диода является одиночным слоем из слоя микрокристаллического кремния, или тому подобного, в настоящем варианте осуществления и варианте осуществления, который будет описан ниже, он, например, может иметь слоистую структуру из слоя микрокристаллического кремния и слоя аморфного кремния. Подобным образом, электрод затвора, проводящий слой, электрод истока, промежуточный электрод и электрод стока также не обязаны формироваться одиночным проводящим слоем, таким как металлический слой, но могут иметь слоистую структуру одинаковых или разных проводящих слоев.

Подложка для поддержки тонкопленочного транзистора и диода может быть изолирующей подложкой, такой как пластмассовая подложка, вместо стеклянной подложки. В качестве альтернативы, может использоваться подложка из нержавеющей стали, имеющая изолирующую пленку на ее поверхности. Подложка не должна быть прозрачной подложкой.

Более того, тонкопленочный транзистор и диод по настоящему варианту осуществления и варианту осуществления, который будет описан ниже, не должны включать в себя пленку пассивации.

<Способ для изготовления полупроводникового устройства>

Затем, примерный способ для изготовления полупроводникового устройства, показанного на фиг.19, будет описан со ссылкой на чертежи.

Как показано на фиг.20, способ для изготовления полупроводникового устройства включает в себя этап 71 формирования электрода затвора по формированию электрода затвора, этап 72 формирования слоя изоляции затвора-полупроводникового слоя по формированию островкового полупроводникового слоя, чтобы был слоем изоляции затвора и активным слоем, этап 73 формирования электрода истока-стока по формированию электродов истока и стока, этап 74 отделения истока-стока по электрическому разделению электродов истока и стока друг от друга, и этап 75 формирования пассивации.

Каждый этап далее будет подробно описан со ссылкой на фиг.21-24. Фиг.21-24 - принципиальные схемы, иллюстрирующие этапы способа для изготовления полупроводникового устройства. Фиг.21(a) - вид сверху, а FIG. 21(b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B', показанных на фиг.21(a). Это подобным образом применяется к фиг.22-24, при этом (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' соответствующего вида сверху.

(1) Этап 71 формирования электрода затвора Как показано на фиг.21(a) и 21(b), металлическая пленка затвора формируется на подложке 1 и подвергается формированию рисунка, с тем чтобы сформировать электрод 103 затвора тонкопленочного транзистора 301, и электрод 2 затвора, проводящий слой 3 и соединительную линию 4 диода 201. Соединительная линия 4 и электрод 2 затвора сформированы прилегающими друг к другу в пределах единого рисунка. Проводящий слой 3 формируется в рисунке, отдельном от электрода 2 затвора и соединительной линии 4.

Более точно, прежде всего, молибден (Mo) осаждается до толщины 0,2 мкм, чтобы сформировать металлическую пленку затвора (не показана) на подложке 1, такой как стеклянная подложка, посредством способа распыления с использованием газообразного аргона (Ar). Температура подложки 1 при формировании металлической пленки затвора имеет значение от 200 до 300°C.

Затем, пленка резистного рисунка (не показана) из фоторезистного материала формируется на металлической пленке затвора, и металлическая пленка затвора подвергается формированию рисунка с использованием пленки резистного рисунка в качестве маски (этап фотолитографии). Это дает электрод 103 затвора тонкопленочного транзистора 301 и электрод 2 затвора, проводящий слой 3 и соединительную линию 4 диода 201. Например, способ влажного травления используется для травления металлической пленки затвора. Раствор, содержащий в себе от 10 до 80 весовых % фосфорной кислоты, от 1 до 10 весовых % азотной кислоты, от 1 до 10 весовых % уксусной кислоты и равновесную воду, может использоваться в качестве травителя. После травления, пленка резистного рисунка удаляется с использованием состава для удаления, содержащего в себе органическую щелочь.

Материал металлической пленки затвора может быть единообразным металлическим, таким как оксид индия и олова (ITO), вольфрам (W), медь (Cu), хром (Cr), тантал (Ta), алюминий (Al) и титан (Ti), а также молибден (Mo), или материалом, полученным смешиванием азота, кислорода или другого металла с ними. Металлическая пленка затвора может быть одиночным слоем, использующим материал, перечисленный выше, или может иметь слоистую структуру. Например, электрод 2 затвора может быть слоистой пленкой Ti/Al/Ti титана и алюминия, слоистой пленкой Ti/Cu/Ti титана и меди или слоистой пленкой Mo/Cu/Mo меди и молибдена.

Способом для формирования металлической пленки затвора может быть способ осаждения из паровой фазы, или тому подобный, а также способ напыления. Толщина металлической пленки затвора не ограничена никаким конкретным значением. Способ для травления металлической пленки затвора не ограничен способом влажного травления, описанным выше, но также может быть способом сухого травления, или тому подобным, использующим газообразный хлор (Cl2), газообразный трихлористый бор (BCl3), газообразный CF4 (четырехфтористый углерод), O2 (кислород), и т.д.

(2) Этап 72 формирования слоя изоляции затвора - полупроводникового слоя. Затем, слой 5 изоляции затвора, пленка микрокристаллического кремния и пленка кремния n+-типа формируются в этом порядке на электродах 2 и 103 затвора, проводящем слое 3 и соединительной линии 4, и пленка микрокристаллического кремния и пленка кремния n+-типа подвергаются формированию рисунка. Это приводит к площадочным обработанным пленкам 118, 17 и 18 микрокристаллического кремния и обработанным пленкам 120, 19 и 20 кремния n+-типа, как показано на фиг.22(a) и 22(b). Затем, контактное отверстие 14 для обнажения участка соединительной линии 4 через него предусматривается в слое 5 изоляции затвора.

Более точно, прежде всего, слой 5 изоляции затвора (например, толщина: 0,4 мкм), изготовленный из нитрида кремния (SiNx), формируется способом усиленного плазмой химического осаждения из паровой фазы (PECVD) на подложке 1 с электродом 2 затвора, и т.д., сформированными на нем. В настоящем варианте осуществления, слой 5 изоляции затвора формируется в условиях температуры подложки: от 250 до 300°C, давления: от 50 до 300 Па и плотности электрической мощности от 10 до 20 мВт/см2 с использованием камеры осаждения, имеющей конструкцию электродов с параллельными пластинами (емкостной связью). Газовая смесь силана (SiH4), аммиака (NH3) и азота (N2) используется в качестве газа осаждения.

Затем, пленка микрокристаллического кремния (например, толщина: 0,12 мкм) формируется посредством использования такой же камеры, как камера осаждения, используемая для формирования слоя 5 изоляции затвора. В настоящем варианте осуществления, пленка микрокристаллического кремния формируется при условиях температуры подложки: от 250 до 300°C, давления: от 50 до 300 Па и плотности электрической мощности: от 1 до 30 мВт/см2, с использованием газообразного силана, разбавленного газообразным водородом, в качестве газа осаждения. Относительный расход между силаном (SiH4)и водородом (H2) имеет значение от 1:200 до 1:1000.

Более того, пленка кремния n+-типа (например, толщина: 0,05 мкм) формируется с использованием такой же камеры осаждения, как описанная выше. В настоящем варианте осуществления, формирование пленки кремния n+-типа является по существу таким же, как формирование пленки микрокристаллического кремния, но газовая смесь силана (SiH4), водорода (H2) и фосфина (PH3) используется в качестве газа осаждения.

Затем, пленка резистного рисунка (не показана) из фоторезистного материала формируется на слое 5 изоляции затвора, а пленка микрокристаллического кремния и пленка кремния n+-типа подвергаются формированию рисунка с использованием пленки резистного рисунка в качестве маски (этап фотолитографии). Это приводит к площадочным обработанным пленкам 118, 17 и 18 микрокристаллического кремния и обработанным пленкам 120, 19 и 20 кремния n+-типа. Способ сухого травления, главным образом, с использованием газообразного хлора (Cl2), например, для травления пленки микрокристаллического кремния и пленки кремния n+-типа. После травления, пленка резистного рисунка удаляется с использованием состава для удаления, содержащего в себе органическую щелочь.

Более того, формируется пленка резистного рисунка (не показана) из фоторезистного материала, и контактное отверстие 14 формируется в слое 5 изоляции затвора с использованием пленки резистного рисунка в качестве маски (этап фотолитографии). Способ сухого травления, использующий комбинацию газообразного CF4 (четырехфтористого углерода), O2 (кислорода), и т.д., например, может использоваться для формирования контактного отверстия 14. После травления, пленка резистного рисунка удаляется с использованием состава для удаления, содержащего в себе органическую щелочь.

(3) Этап 73 формирования электрода истока-стока Проводящая пленка, которая должна использоваться для формирования электрода истока-стока, формируется на обработанных кремния n+-типа пленках 120, 19 и 20, и слое 5 изоляции затвора. В настоящем варианте осуществления, проводящая пленка (например, толщина: 0,2 мкм) формируется осаждением молибдена до толщины 0,2 мкм на поверхности подложки 1 способом напыления с использованием газообразного аргона (Ar). Температура подложки во время формирования проводящей пленки имеет значение от 200 до 300°C.

Затем, как показано на фиг.23(a) и 23(b), пленка 21 резистного рисунка формируется на проводящей пленке по проводящей пленке, и проводящая пленка подвергается формированию рисунка с использованием этой маски, таким образом, получая электрод 110 истока и электрод 112 стока тонкопленочного транзистора 301, и электрод 10 истока, промежуточный электрод 11 и электрод 12 стока диода 201.

Проводящая пленка, например, может подвергаться формированию рисунка с использованием способа влажного травления. В настоящем варианте осуществления, раствор, содержащий в себе от 10 до 80 весовых % фосфорной кислоты, от 1 до 10 весовых % азотной кислоты, от 1 до 10 весовых % уксусной кислоты и водный остаток, используется в качестве травителя. Пленка 21 резистного рисунка на электроде 10 истока, промежуточном электроде 11 и электроде 12 стока не удаляется даже после травления и остается неудаленной на протяжении следующего этапа.

Материал проводящей пленки может быть единообразным металлическим, таким как оксид индия и олова (ITO), вольфрам (W), медь (Cu), хром (Cr), тантал (Ta), алюминий (Al) и титан (Ti), а также молибден (Mo), или материалом, полученным смешиванием азота, кислорода или другого металла с ними. Электрод 10 истока может быть одиночным слоем, использующим материал, перечисленный выше, или может иметь слоистую структуру. Например, проводящая пленка 2 может быть слоистой пленкой Ti/Al/Ti титана и алюминия, слоистой пленкой Ti/Cu/Ti титана и меди или слоистой пленкой Mo/Cu/Mo меди и молибдена.