Предлагаемое изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано, преимущественно, для защиты входов и выходов высокочастотных металл-диэлектрик полупроводниковых (МДП) микросхем от электростатических разрядов.

Тенденции развития полупроводниковой промышленности непосредственно связаны с уменьшением минимальных топологических размеров проектирования интегральных микросхем, что приводит к большей чувствительности устройств по отношению к внешним факторам и, в частности, к электростатическим разрядам. Для субмикронных технологий особенно важно обеспечить равномерное распределение стрессового тока после пробоя, своевременное включение защитного элемента и быстрый отвод тока с наименьшим рассеиванием тепла. Один из путей защиты состоит в дополнительном использовании устройств защиты на входные и выходные выводы (а также шины питания) интегральной микросхемы. Устройство защиты должно иметь минимальное паразитное сопротивление и емкость, чтобы минимизировать падение напряжения на этом элементе и уменьшить дополнительную нагрузочную емкость защищаемого устройства, в случае ее использования в выходном буфере.

Известно устройство защиты входов интегральных микросхем от перенапряжения, состоящее из двух каскадов. Первый содержит две шунтирующие цепи для различных величин входного напряжения и дополнительный резистор с большим сопротивлением. Второй каскад содержит шунтирующую цепь в виде МДП - с толстым окислом и дополнительный резистор с большим сопротивлением (см. Заявка Франции №2323232, H01L 19/00, 1976 г.).

Однако в связи с тем, что устройство имеет на входе резисторы большого номинала, его функциональные возможности ограничены областью применения для микросхем низкого быстродействия.

Известно устройство защиты входов интегральных микросхем от перенапряжения, включающее резистор, соединенный с двумя последовательно соединенными диодами, которые соединены один - с общей шиной питания, а второй - с общей шиной, свободный конец резистора соединен с входной шиной (Патент Великобритании №1305391, Н01L 19/00, 1970 г.).

Устройство может применяться для быстродействующих микросхем. Однако данная микросхема обладает инерционностью, в результате чего при попадании на вход интегральной микросхемы высокого потенциала статического электричества вероятность пробоя подзатворного окисла резко увеличивается.

Наиболее близким к заявленному изобретению является известное из уровня техники устройство защиты входов интегральных схем со структурой МДП, содержащее два полевых (ключевых) транзистора, два нагрузочных резистора, два диода, шину питания, общую шину, входную и выходную шины, при этом диоды соединены последовательно и включены между шиной питания и общей шиной, первый резистор включен между входной шиной и общей точкой соединения диодов, исток первого ключевого транзистора подключен к общей шине, его сток - к истоку второго ключевого транзистора и к входной шине, а сток второго транзистора подключен к упомянутой шине питания (Авторское свидетельство №1083362, Н03К 17/08, 1981 г.).

Однако основным недостатком известного из уровня техники решения по отношению к заявленному изобретению является то, что в рабочем режиме при положительной или отрицательной полярности стрессового напряжения в нем открывается только один из ключевых транзисторов, вследствие этого необходимо вводить в схему мощные транзисторы большой площади, что в конечном итоге приводит к его значительным топологическим размерам.

Задача, на решение которой направлено заявленное изобретение, заключается в уменьшении электрической емкости и площади на кристалле устройства защиты выводов интегральных схем со структурой МДП от электростатических разрядов за счет уменьшения площади его функциональных элементов, при сохранении качественных характеристик.

Данный технический результат достигается посредством того, что в устройство защиты выводов интегральных схем со структурой МДП от электростатических разрядов, содержащее два ключевых транзистора, два нагрузочных резистора, входную шину, шину питания и шину земли, при этом исток одного из ключевых транзисторов соединен с входной шиной, согласно изобретению дополнительно введены два управляющих транзистора, с возможностью разделения разрядного тока на две равновеликие составляющие и функционального обеспечения протекания разрядного тока по двум ключевым транзисторам одновременно.

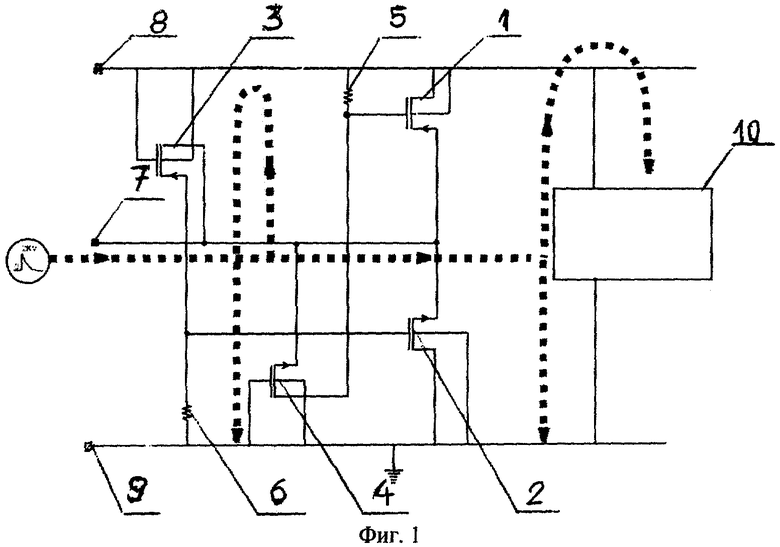

Предлагаемое изобретение поясняется чертежами, где:

- на Фиг.1 изображена структурная схема устройства защиты выводов интегральных схем со структурой МДП от электростатических разрядов при положительной полярности напряжения электростатического разряда;

- на Фиг.2 изображена структурная схема устройства защиты выводов интегральных схем со структурой МДП от электростатических разрядов при отрицательной полярности напряжения электростатического разряда.

Устройство защиты выводов интегральных схем со структурой МДП от электростатических разрядов содержит ключевой (р-канальный) транзистор 1 и ключевой (n-канальный) транзистор 2, которые обеспечивают протекание разрядного тока большой величины, управляющий (р-канальный) транзистор 3 и управляющий (n-канальный) транзистор 4, которые, в свою очередь, обеспечивают разделение тока на две равновеликие (одинаковые) составляющие, а также нагрузочный резистор 5 и нагрузочный резистор 6, функционально служащие нагрузками ключевому транзистору 1 и ключевому транзистору 2 соответственно. Истоки ключевого транзистора 1 и ключевого транзистора 2 соединены между собой и с входной шиной 7 (функционально являющейся и общей шиной), а их стоки соединены с шиной 8 питания и шиной 9 земли соответственно. Затвор ключевого транзистора 1 и сток управляющего транзистора 4 через нагрузочный резистор 5 подключены к шине 8 питания, а затвор ключевого транзистора 2 и исток управляющего транзистора 3 через нагрузочный резистор 6 подключены к шине 9 земли. При этом затвор управляющего транзистора 4 соединен с шиной 9 земли, а его исток - с входной шиной 7, а затвор управляющего транзистора 3 соединен с шиной 8 питания, а его сток - с упомянутой входной шиной 7.

Устройство работает следующим образом.

Наиболее часто электростатический разряд (ЭСР) возникает между контактной площадкой входного сигнала и контактной площадкой одной из шин питания. Есть вероятность возникновения ЭСР также между контактными площадками входного и выходного сигналов или контактными площадками шин питания. ЭСР может иметь как положительную, так и отрицательную полярность по отношению к потенциалам шины питания.

При электрическом пробое полупроводниковых приборов области пробоя столь малы, что их максимальный разогрев происходит за время, меньшее времени разряда. Фактором, определяющим возникновение отказа, является напряжение на затворе (для транзисторов с МДП структурой) или тепловая мощность разрядного тока (для биполярных транзисторов и полевых транзисторов с затвором Шотки).

Основная функция устройства защиты состоит в ограничении напряжения на затворах входных МДП элементов путем переключения разрядного тока из входных и выходных цепей в шину земли. Проблемными являются входные элементы защиты, поскольку они, с одной стороны, должны обеспечивать соответствующий уровень защиты от ЭСР, а с другой, должны иметь минимальное паразитное сопротивление и емкость, чтобы минимизировать падение напряжения на этом элементе и уменьшить дополнительную емкость защищаемого устройства.

В момент подачи на вывод устройства разрядного напряжения ключевой транзистор 1 и ключевой транзистор 2 открыты, а при нормальном режиме работы (при рабочем напряжении) полезный сигнал, поступающий на вход, проходит в общую интегральную схему (не показана), при этом ключевые транзисторы закрыты, т.е. устройство защиты не работает.

Интегральная схема наиболее уязвима при подаче отрицательного разрядного напряжения на контактную площадку входной шины 7, при оборванной шине 9 земли и положительного разрядного напряжения при оборванной шине 8 питания.

При положительной полярности напряжения электростатического разряда (до 2000 В) ток поступает на входную шину 7 (см. Фиг.1 - пунктирной линией показано протекание разрядного тока) и далее протекает через ключевой транзистор 1 и далее через элемент 10 защиты цепей питания на шину 9 земли, в тоже время управляющий транзистор 3 открывает ключевой транзистор 2.

При отрицательной полярности напряжения электростатического разряда (до -2000 В) ток вытекает через входную шину 7 (см. Фиг.2 - пунктирной линией показано протекание разрядного тока), протекая через ключевой транзистор 2 и далее через элемент 10 защиты цепей питания на шину 9 земли, в то же время управляющий транзистор 4 открывает ключевой транзистор 1.

Таким образом, при возникновении ЭСР на входной шине 7 как при отрицательной полярности напряжения электростатического разряда, так и при положительной полярности происходит разделение разрядного тока на две равновеликие составляющие (на одинаковые два плеча) и функционально обеспечивается протекание разрядного тока по двум ключевым транзисторам 1 и 2 одновременно, что ведет к уменьшению вдвое сопротивления в цепи разрядного тока и (при наличии двух дополнительных транзисторов) дает возможность использовать в устройстве защиты менее мощные ключевые транзисторы, и соответственно уменьшить его массогабаритные характеристики в целом.

Результаты испытаний показали, что уменьшение площади ключевых транзисторов в 2 раза не приводит к изменению предельно допустимого ЭСР (характеристика стойкости интегральных микросхем к ЭСР), величина которого по прежнему в пределах 2000 В, но по сравнению с известным техническим решением позволяет уменьшить площадь (с учетом управляющих транзисторов) устройства защиты входов интегральных микросхем от ЭСР в 1,5 раза и его электрическую емкость в 1,6 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫХОДНОЙ КАСКАД ДЛЯ КМОП МИКРОСХЕМ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2014 |

|

RU2560822C1 |

| УСТРОЙСТВО ЗАЩИТЫ ВЫВОДОВ МИКРОСХЕМЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2012 |

|

RU2523115C1 |

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КНС (КРЕМНИЙ НА САПФИРЕ), КНИ (КРЕМНИЙ НА ИЗОЛЯТОРЕ) СТРУКТУРАХ | 2011 |

|

RU2467431C1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ ПИТАНИЯ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КРЕМНИЕВЫХ ПЛАСТИНАХ С ПРОВОДИМОСТЬЮ N-ТИПА | 2013 |

|

RU2585882C2 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

Изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано преимущественно для защиты входов и выходов высокочастотных металлооксидных полупроводниковых (МОП) микросхем от электростатических разрядов. Устройство содержит ключевой (р-канальный) транзистор (Т)(1) и ключевой (n-канальный) Т(2), которые обеспечивают протекание разрядного тока большой величины, управляющий симметричный (р-канальный) Т(3) и управляющий симметричный (n-канальный) Т(4), которые, в свою очередь, обеспечивают разделение тока на две равновеликие (одинаковые) составляющие, а также нагрузочные резисторы (Р)(5) и (6). Истоки Т(1) и Т(2) соединены между собой и с входной шиной (7) (являющейся общей шиной), а их стоки соединены с шиной (8) питания и шиной (9) земли соответственно. Затвор Т(1) и сток Т(4) через Р(5) подключены к шине (8), а затвор Т(2) и исток Т(3) через Р(6) подключены к шине (9). При этом затвор Т(4) соединен с шиной (9), а его исток - с входной шиной (6), а затвор Т(3) соединен с шиной (8), а его сток - с входной шиной (7). При возникновении электростатического разряда на входной шине (7) обеспечивается протекание разрядного тока по Т(1) и (2) одновременно, что ведет к уменьшению вдвое сопротивления в цепи разрядного тока и дает возможность использовать в устройстве защиты менее мощные ключевые Т. 2 ил.

Устройство защиты выводов интегральных схем со структурой МДП от электростатических разрядов, содержащее два ключевых транзистора, два нагрузочных резистора, входную шину, шину питания и шину земли, при этом исток одного из ключевых транзисторов соединен с входной шиной, отличающееся тем, что в него дополнительно введены два управляющих транзистора, с возможностью разделения разрядного тока на две равновеликие составляющие и функционального обеспечения протекания разрядного тока по двум ключевым транзисторам одновременно, причем истоки ключевого транзистора (1) и ключевого транзистора (2) соединены между собой и с входной шиной, а их стоки соединены с шиной питания и шиной земли соответственно, затвор ключевого транзистора (1) и сток управляющего транзистора (4) через нагрузочный резистор (5) подключены к шине питания, а затвор ключевого транзистора (2) и исток управляющего транзистора (3) через нагрузочный резистор (6) подключены к шине земли, при этом затвор управляющего транзистора (4) соединен с шиной земли и его исток - с входной шиной, а затвор и исток управляющего транзистора (3) соединен с шиной питания и с входной шиной соответственно.

| US 6249410 B1, 19.01.2001 | |||

| Устройство защиты входов интегральных схем со структурой МДП | 1981 |

|

SU1083362A1 |

| RU 2003111439 A, 20.11.2004 | |||

| RU 93044493 А, 20.01.1996 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2007-10-10—Публикация

2005-12-13—Подача