Предлагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах широко используются логические элементы «2-И» (ЛЭ), реализованные на основе эмиттерно-связанной логики [1-12], работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами.

В работе [13], а также монографиях соавтора настоящей заявки [14-15] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока. Заявляемое устройство «2-И» относится к этому типу логических элементов.

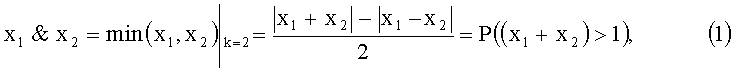

Ближайшим прототипом заявляемого устройства является логический элемент «2-И», представленный в патенте US 3.508.076, фиг.1. Он содержит первый 1 и второй 2 входные коммутаторы кванта тока I0, управляемые источниками входных логических напряжений 3 и 4.

Существенный недостаток известного логического элемента «2-И» состоит в том, что он, используя потенциальные двоичные сигналы, обладает усложненной структурой связей, нелинейностью рабочих режимов элементов и критичностью параметров структуры ЛЭ и входных сигналов, что в конечном итоге приводит к снижению его быстродействия.

Основная задача предлагаемого изобретения состоит в создании логического элемента «2-И», в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов, определяемое состоянием входных потенциальных двоичных сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [14-15].

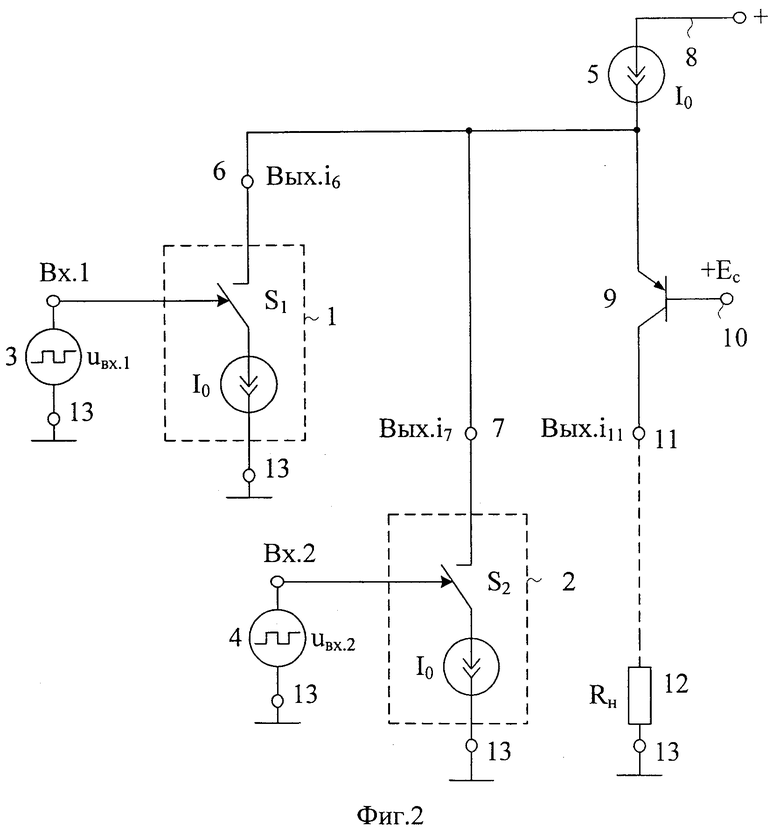

Поставленная задача решается тем, что в логическом элементе «2-И», содержащем первый 1 и второй 2 входные коммутаторы кванта тока I0, управляемые источниками входных логических напряжений 3 и 4, токостабилизирующий двухполюсник 5, включенный между объединенными токовыми выходами 6, 7 первого 1 и второго 2 входных коммутаторов квантов тока I0 и шиной 8 источников питания, предусмотрены новые элементы и связи - токовые выходы 6, 7 первого 1 и второго 2 входных коммутаторов кванта тока I0 соединены с эмиттером дополнительного транзистора 9, база которого связана с источником опорного напряжения 10, а коллектор является логическим токовым выходом устройства 11, причем в качестве токостабилизирующего двухполюсника 5 используется источник опорного тока, выходной ток которого кратен кванту тока I0.

Схема многозначного логического элемента «2-И»-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

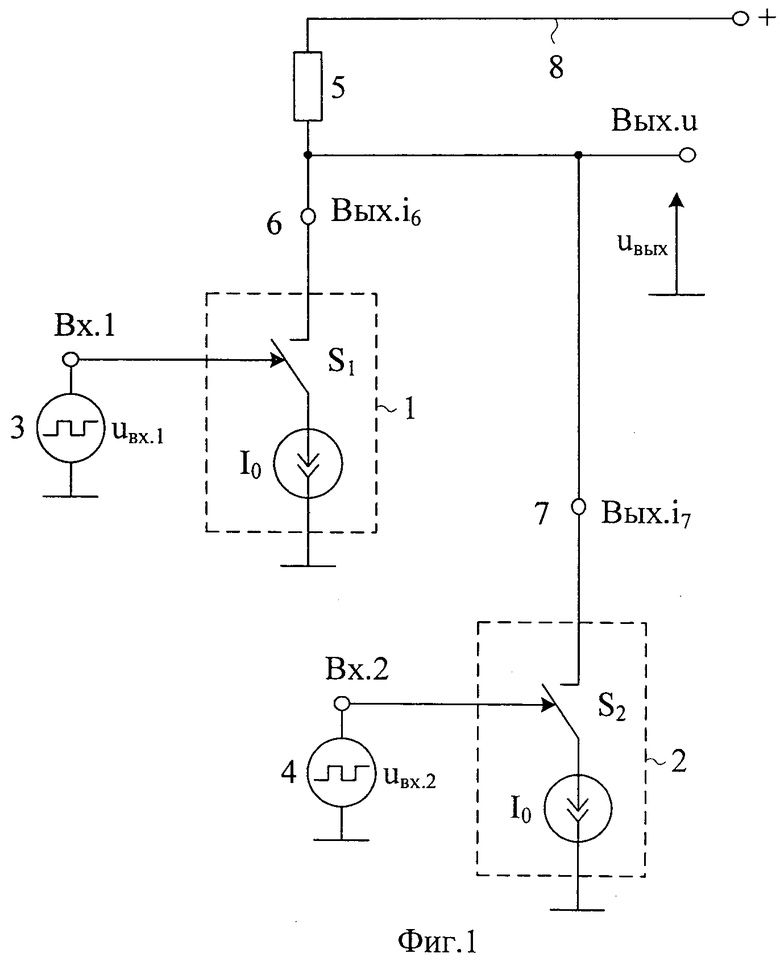

На чертеже фиг.3 приведена одна из возможных схем первого 1 (или второго 2) входного коммутатора кванта тока I0.

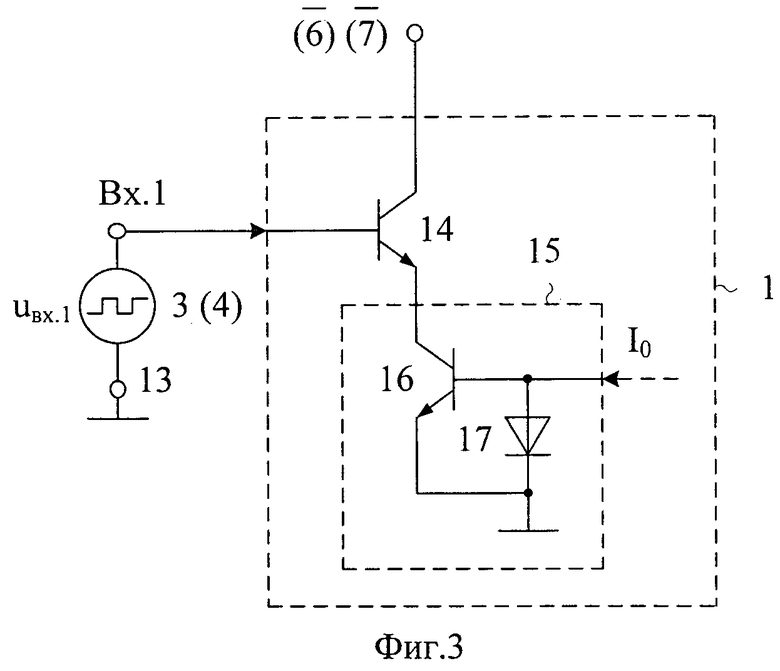

На чертеже фиг.4 приведена схема первого 1 (или второго 2) входного коммутатора кванта тока I0, реализованного в соответствии с п.2, п.3 формулы изобретения.

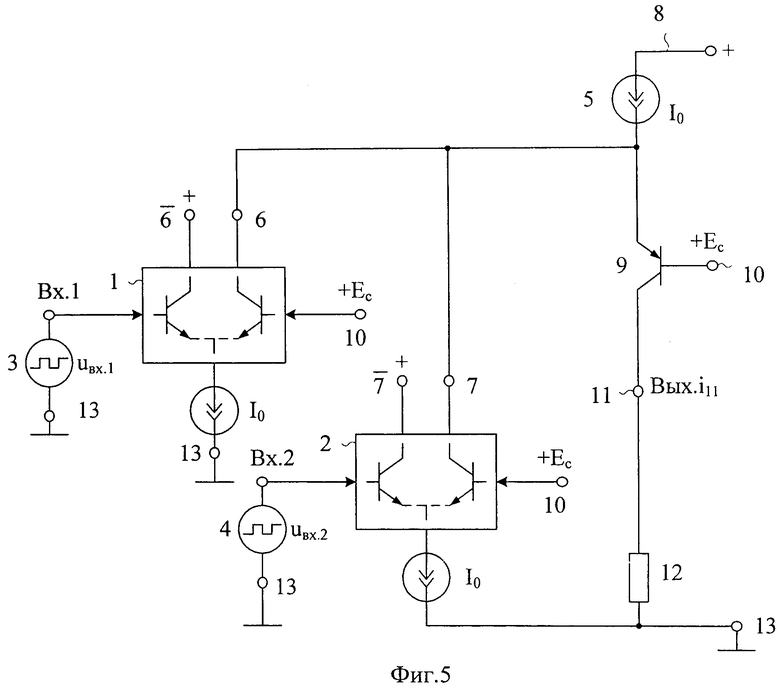

На чертеже фиг.5 приведена схема логического элемента фиг.2, в котором входные коммутаторы 1, 2 квантов тока 10 реализованы на основе дифференциальных каскадов фиг.4.

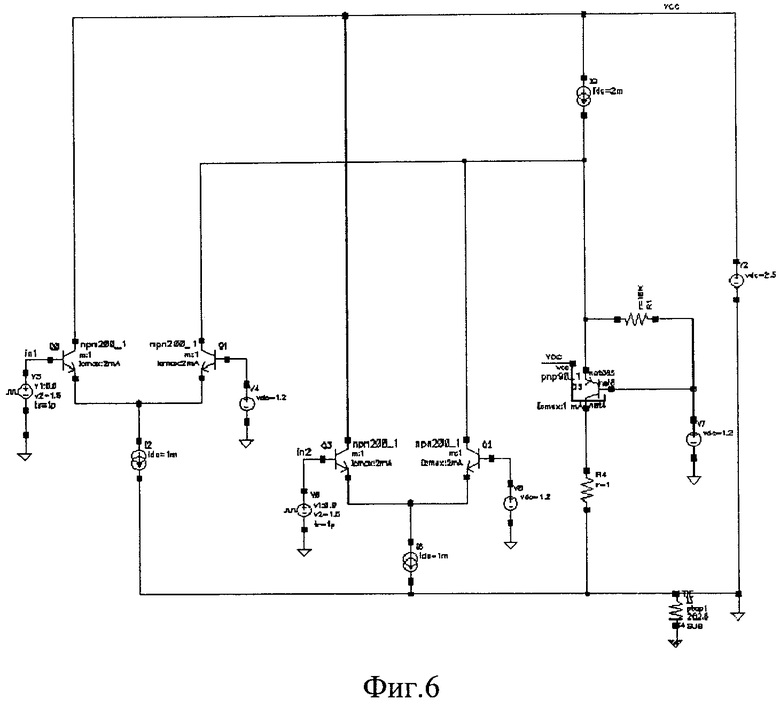

На чертеже фиг.6 показана схема неинвертирующего логического элемента «2-И» фиг.5 в среде Cadance на моделях SiGe транзисторов.

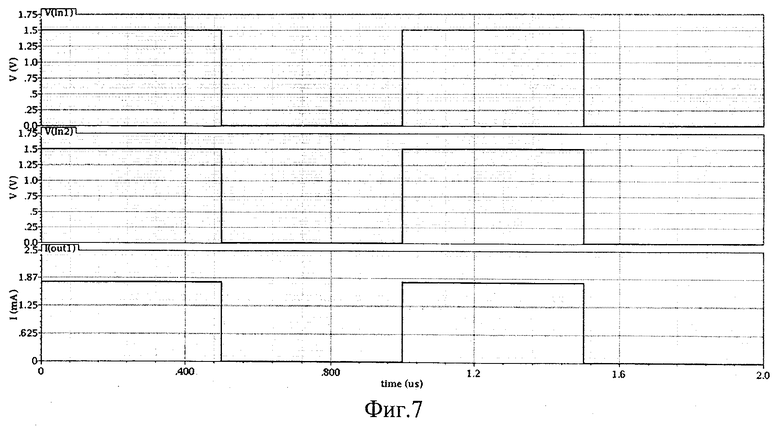

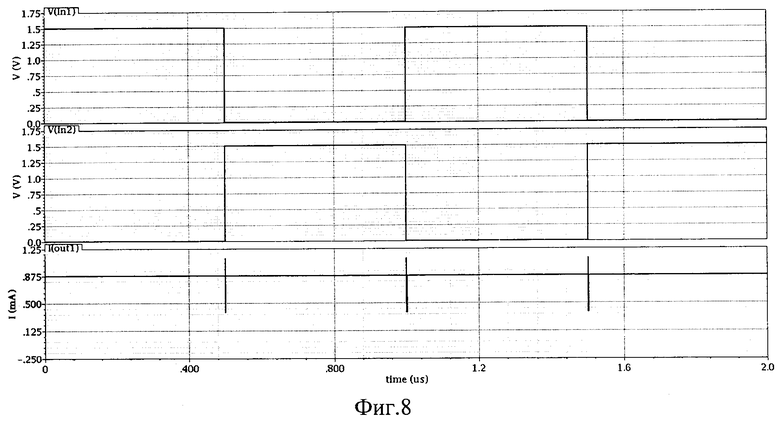

На чертеже фиг.7 приведен график переходного процесса на входах и выходах ЛЭ фиг.6 при подаче на входы синфазных сигналов (X1=1, Х2=1; Х1=0, Х2=0), а на чертеже фиг.8 - переходный процесс на входах и выходах ЛЭ фиг.6 при подаче на входы прямоугольных импульсов, сдвинутых друг относительно друга на 90 градусов (X1=1, Х2=0).

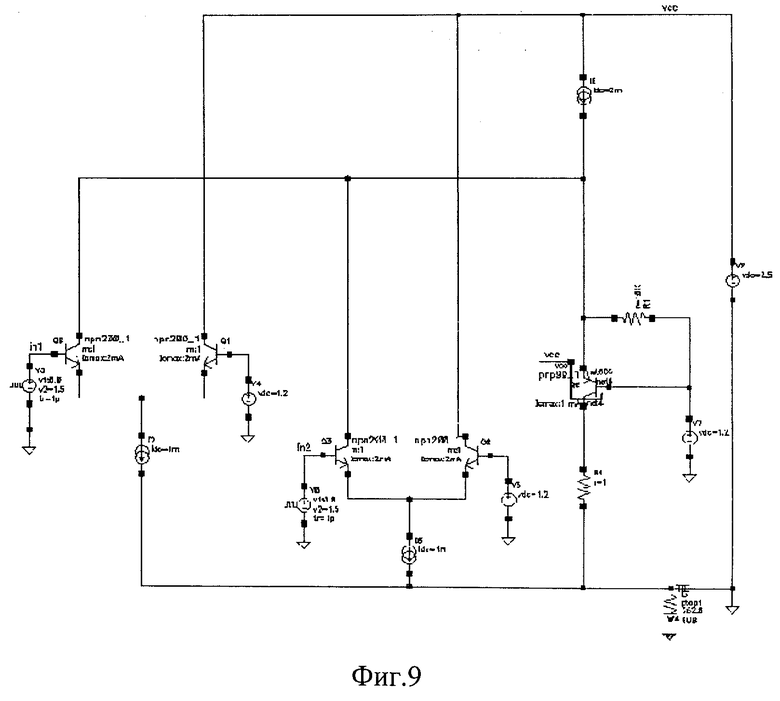

На чертеже фиг.9 представлена схема инвертирующего логического элемента «2-И» на основе каскода в среде Cadance на моделях SiGe интегральных транзисторов.

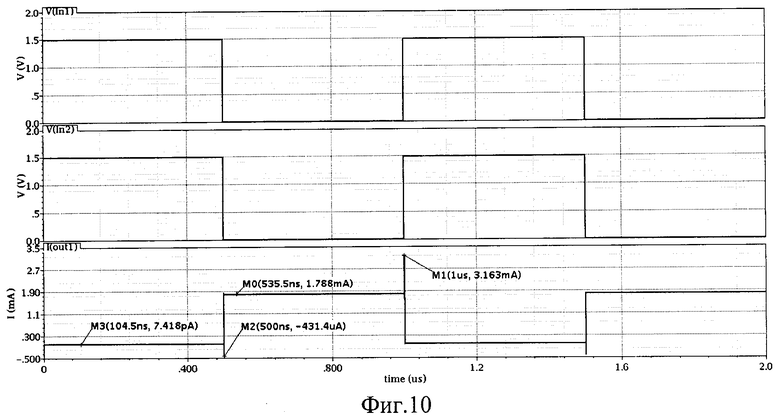

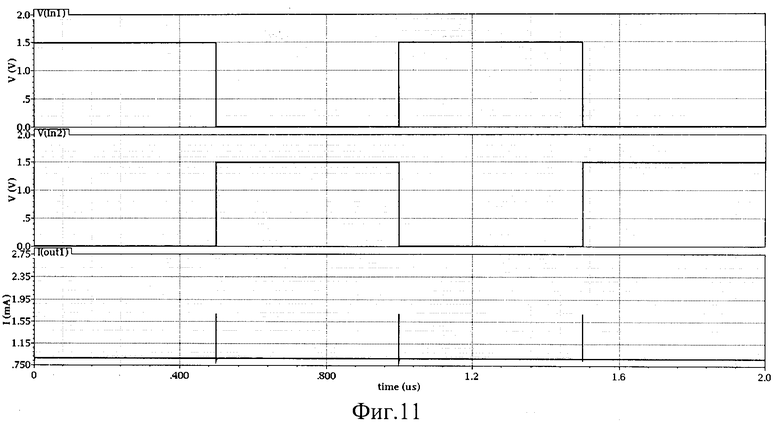

На чертеже фиг.10 показан переходный процесс на входах и выходах при подаче на входы синфазных сигналов (X1=1, Х2=1; Х1=0, Х2=0), а на чертеже фиг.11 - переходный процесс на входах и выходах при подаче на входы прямоугольных импульсов, сдвинутых друг относительно друга на 90 градусов (Х1=1, Х2=0).

Логический элемент «2-И» с многозначным внутренним представлением сигналов фиг.2 содержит первый 1 и второй 2 входные коммутаторы кванта тока I0, управляемые источниками входных логических напряжений 3 и 4, токостабилизирующий двухполюсник 5, включенный между объединенными токовыми выходами 6, 7 первого 1 и второго 2 входных коммутаторов квантов тока I0 и шиной 8 источников питания. Токовые выходы 6, 7 первого 1 и второго 2 входных коммутаторов кванта тока I0 соединены с эмиттером дополнительного транзистора 9, база которого связана с источником опорного напряжения 10, а коллектор является логическим токовым выходом устройства 11, причем в качестве токостабилизирующего двухполюсника 5 используется источник опорного тока, выходной ток которого кратен кванту тока I0. В частном случае нагрузкой ЛЭ является двухполюсник 12, моделирующий влияние нагрузки ЛЭ на работу схемы и включенный между выходом устройства 11 и общей шиной источника питания 13.

На чертеже фиг.3 показан частный случай построения входных коммутаторов 1, 2 квантов тока I0, которые реализованы на транзисторах 13, 15 и р-n переходе 16.

На чертеже фиг.4, в соответствии с пп.2, 3 формулы изобретения каждый из входных коммутаторов 1, 2 кванта тока I0, управляемых источниками входных логических напряжений 3, (4), выполнен в виде дифференциальных каскадов на первом 18 и втором 19 входных транзисторах, эмиттеры которых связаны с источником 20 кванта тока I0 I0, база первого 18 входного транзистора соединена с источником входного логического напряжения 3, (4), база второго 19 входного транзистора соединена с источником опорного напряжения 10, причем коллекторы первого 18 и второго 19 входных транзисторов соединены с инвертирующими

Рассмотрим работу логического элемента «2-И» фиг.2. Синтез логической функции «2-И» производится на основе ее многозначного аналога, описываемого выражением

где k - значность логики, Р((х1+х2)>а) предикат [14, 15];

х1, х2 - входные логические сигналы.

Реализация предиката в соответствии с (1) производится сложением токовых сигналов с выходов токовых зеркал 5 и 6 и вычитанием из этой суммы кванта тока, формируемого опорным источником 11. При этом выходное значение предиката соответствует логическому нулю (отсутствие тока), если сумма х1+х2 меньше либо равна единице, и соответствует логической единице (наличие кванта тока), если сумма х1+х2 больше единицы.

На вход логического элемента «2-И» по чертежу фиг.2 от источников входных логических напряжений 3 и 4 поступают сигналы, управляющие состоянием ключей S1 и S2 входных коммутаторов 1, 2 квантов тока I0, которые передают ток I0 в эмиттер транзистора 9.

В выключенном состоянии каждый ключ S{, S2 отключен от точки суммирования. При этом сумма их токов в точке суммирования равна нулю. При включенном состоянии одного из ключей значение соответствующего кванта тока принимает величину I0 («1»), а значение их суммы в точке суммирования равно «1». При включенном состоянии обоих ключей значения квантов тока равны «1», а значение их суммы в точке суммирования равно «2». К этой сумме добавляется квант тока I0 источника тока 5 противоположного направления. При этом разность токов в точке суммирования принимается равной «0», если сумма токов ключей больше или равна «1», и равной «1», если сумма токов ключей равна «0». Результат вычитания поступает через транзистор 9 на токовый выход устройства 11.

Как видно из приведенного описания реализация логической функции «2-И» здесь производится формированием алгебраической суммы квантов выходных токов ключей S1, S2 (выходных коммутаторов 1 и 2) с квантом выходного тока источника 5 и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Отличием логического элемента по схеме фиг.5 является реализация входных коммутаторов тока 1, 2 (токовых ключей S2) в виде дифференциальных каскадов. Вариант такой реализации приведен на чертеже фиг.4. Дифференциальный каскад фиг.4 производит коммутацию кванта тока I0. При этом источник тока 20 при любом состоянии входного логического сигнала не выходит из активного режима, что повышает быстродействие схемы.

Показанные на чертежах фиг.7, фиг.8 и фиг.10-фиг.11 результаты моделирования подтверждают указанные свойства заявляемых схем. Следует отметить, что кратковременные импульсы на выходе ЛЭ, возникающие в момент переключения входных сигналов, характерные и для других известных логических элементов, определяются различными временами переключения входных коммутаторов квантов тока 1, 2 и могут быть устранены в реальных схемах средствами технологии.

Таким образом, рассмотренные схемотехнические решения логического элемента «2-И» характеризуются многозначным состоянием внутренних сигналов и двоичным представлением сигнала на его токовом выходе и могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Авторское свидетельство СССР SU 892729

2. Патентная заявка WO 2004/112247

3. Патент US 4.001.603

4. Патент US 4.359.653

5. Патент US 6.157.693, fig.5

6. Патент US 5.216.295

7. Патент US 3.758.791, fig.5

8. Патент US 4.593.211

9. Патент US 4.347.446

10. Патент US 4.516.039, fig.5

11. Патент US 4.970.416

12. Патент US 4.605.871, fig.2

13. Малюгин В.Д. Реализация булевых функций арифметическими полиномами.// Автоматика и телемеханика, 1982. №4. С.84-93.

14. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел.// Монография. - Таганрог: ТРТУ, 2001. - 147 с.

15. Чернов Н.И. Линейный синтез цифровых структур АСОИУ.// Учебное пособие. Таганрог. - ТРТУ, 2004 г., 118 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "2-И" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2513717C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИСКЛЮЧАЮЩЕЕ ИЛИ" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2506695C1 |

| ОДНОРАЗРЯДНЫЙ ПОЛНЫЙ СУММАТОР С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2504074C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "И" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2509412C1 |

| КОМПАРАТОР ТОКОВ С ГИСТЕРЕЗИСОМ | 2016 |

|

RU2642339C1 |

| K-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "МИНИМУМ" | 2014 |

|

RU2553070C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕСТРОГОГО СРАВНЕНИЯ НА НЕРАВЕНСТВО ДВУХ МНОГОЗНАЧНЫХ ПЕРЕМЕННЫХ | 2014 |

|

RU2547233C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ НА РАВЕНСТВО ДВУХ МНОГОЗНАЧНЫХ ПЕРЕМЕННЫХ | 2014 |

|

RU2549142C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "И" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2509413C1 |

Изобретение относится к области вычислительной техники, автоматики и может использоваться в различных системах автоматического управления, передачи информации и т.п. Технический результат заключается в повышении быстродействия и создании элементной базы вычислительных устройств, работающих на принципах многозначной линейной алгебры. Логический элемент «2-И» с многозначным внутренним представлением сигналов содержит первый (1) и второй (2) входные коммутаторы кванта тока I0, управляемые источниками входных логических напряжений (3) и (4), токостабилизирующий двухполюсник (5), включенный между объединенными токовыми выходами (6), (7) первого (1) и второго (2) входных коммутаторов квантов тока I0 и шиной (8) источников питания. Токовые выходы (6), (7) первого (1) и второго (2) входных коммутаторов кванта тока I0 соединены с эмиттером дополнительного транзистора (9), база которого связана с источником опорного напряжения (10), а коллектор является логическим токовым выходом устройства (11), причем в качестве токостабилизирующего двухполюсника (5) используется источник опорного тока, выходной ток которого кратен кванту тока I0. 2 з.п. ф-лы, 11 ил.

1. Логический элемент «2-И» с многозначным внутренним представлением сигналов, содержащий первый (1) и второй (2) входные коммутаторы кванта тока I0, управляемые источниками входных логических напряжений (3) и (4), токостабилизирующий двухполюсник (5), включенный между объединенными токовыми выходами (6), (7) первого (1) и второго (2) входных коммутаторов квантов тока I0 и шиной (8) источников питания, отличающийся тем, что токовые выходы (6), (7) первого (1) и второго (2) входных коммутаторов кванта тока I0 соединены с эмиттером дополнительного транзистора (9), база которого связана с источником опорного напряжения (10), а коллектор является логическим токовым выходом устройства (11), причем в качестве токостабилизирующего двухполюсника (5) используется источник опорного тока, выходной ток которого кратен кванту тока I0.

2. Логический элемент «2-И» с многозначным внутренним представлением сигналов по п.1, отличающийся тем, что каждый из входных коммутаторов (1), (2) кванта тока I0, управляемых источниками входных логических напряжений (3), (4), выполнен в виде дифференциальных каскадов на первом (18) и втором (19) входных транзисторах, эмиттеры которых связаны с источником (20) кванта тока I0, база первого (18) входного транзистора соединена с источником входного логического напряжения (3), (4), база второго (19) входного транзистора соединена с источником опорного напряжения (10), причем коллектор первого (18) входного транзистора соединен с инвертирующим токовым выходом

3. Логический элемент «2-И» с многозначным внутренним представлением сигналов по п.1, отличающийся тем, что каждый из входных коммутаторов (1) и (2) кванта тока I0, управляемых источниками входных логических напряжений (3), (4), выполнен в виде дифференциальных каскадов на первом (18) и втором (19) входных транзисторах, эмиттеры которых связаны с источником (20) кванта тока I0, база первого (18) входного транзистора соединена с источником входного логического напряжения (3), (4), база второго (19) входного транзистора соединена с источником опорного напряжения (10), причем коллектор второго (19) входного транзистора соединен с неинвертирующим токовым выходом (6), (7) каждого из входных коммутаторов (1) и (2) кванта тока I0.

| US 3508076, 21.04.1970 | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Логический элемент | 1974 |

|

SU513503A1 |

| Логический элемент | 1984 |

|

SU1173551A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

Авторы

Даты

2014-04-20—Публикация

2012-09-11—Подача