Изобретение относится к импульсной технике и может быть использовано в цифровых интегральных схемах.

Цель изобретения - уменьшение потребляемой мощности и увеличение быстродействия.

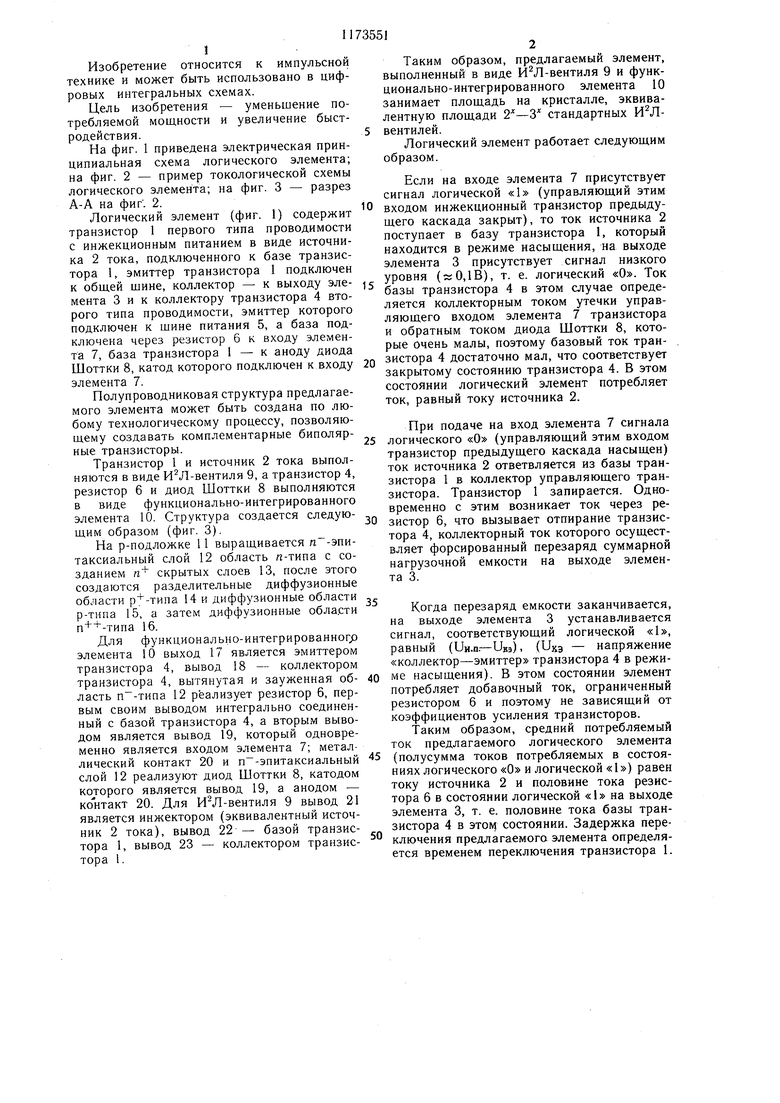

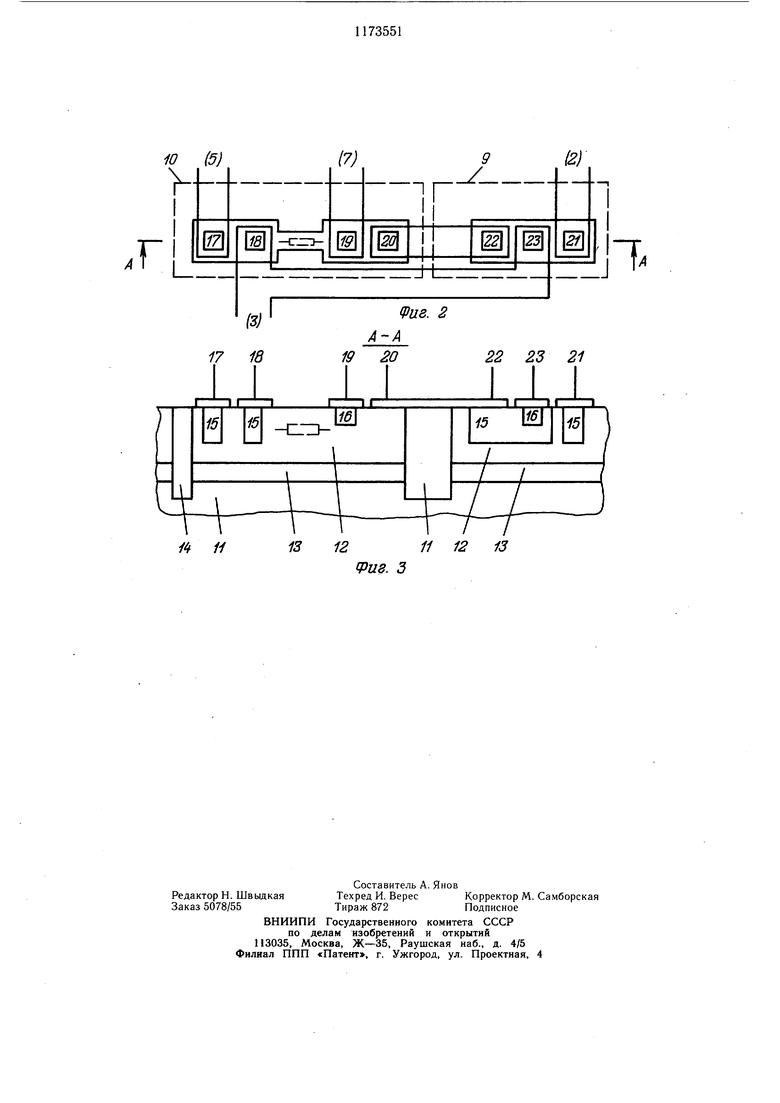

На фиг. 1 приведена электрическая принципиальная схема логического элемента; на фиг. 2 - пример токологической схемы логического элемента; на фиг. 3 - разрез А-А на фиг . 2.

Логический элемент (фиг. 1) содержит транзистор 1 первого типа проводимости с инжекционным питанием в виде источника 2 тока, подключенного к базе транзистора 1, эмиттер транзистора 1 подключен к общей щине, коллектор - к выходу элемента 3 и к коллектору транзистора 4 второго типа проводимости, эмиттер которого подключен к шине питания 5, а база подключена через резистор 6 к входу элемента 7, база транзистора 1 - к аноду диода Шоттки 8, катод которого подключен к входу элемента 7.

Полупроводниковая структура предлагаемого элемента может быть создана по любому технологическому процессу, позволяющему создавать комплементарные биполярные транзисторы.

Транзистор 1 и источник 2 тока выполняются в виде И Л-вентиля 9, а транзистор 4, резистор 6 и диод Шоттки 8 выполняются в виде функционально-интегрированного элемента 10. Структура создается следующим образом (фиг. 3).

На р-подложке 11 выращивается п -эпитаксиальный слой 12 область п-типа с созданием п скрытых слоев 13, после этого создаются разделительные диффузионные области р+-типа 14 и диффузионные области р-типа 15, а затем диффузионные области п++-типа 16.

Для функционально-интегрированногр элемента 10 выход 17 является эмиттером транзистора 4, вывод 18 - коллектором транзистора 4, вытянутая и зауженная область п -типа 12 реализует резистор 6, первым своим выводом интегрально соединенный с базой транзистора 4, а вторым выводом является вывод 19, который одновременно является входом элемента 7; металлический контакт 20 и п -эпитаксиальный слой 12 реализуют диод Шоттки 8, катодом которого является вывод 19, а анодом - контакт 20. Для И Л-вентиля 9 вывод 21 является инжектором (эквивалентный источник 2 тока), вывод 22- базой транзистора 1, вывод 23 - коллектором транзистора 1.

Таким образом, предлагаемый элемент, выполненный в виде И Л-вентиля 9 и функционально-интегрированного элемента 10 занимает площадь на кристалле, эквивалентную площади 2-3 стандартных И Лвентилей.

Логический элемент работает следующим образом.

Если на входе элемента 7 присутствует сигнал логической «1 (управляющий этим

0 входом инжекционный транзистор предыдущего каскада закрыт), то ток источника 2 поступает в базу транзистора 1, который находится в режиме насыщения, на выходе элемента 3 присутствует сигнал низкого уровня (:sO,lB), т. е. логический «О. Ток базы транзистора 4 в этом случае определяется коллекторным током утечки управляющего входом элемента 7 транзистора и обратным током диода Шоттки 8, которые очень малы, поэтому базовый ток транQ зистора 4 достаточно мал, что соответствует закрытому состоянию транзистора 4. В этом состоянии логический элемент потребляет ток, равный току источника 2.

При подаче на вход элемента 7 сигнала 5 логического «О (управляющий этим входом транзистор предыдущего каскада насыщен) ток источника 2 ответвляется из базы транзистора 1 в коллектор управляющего транзистора. Транзистор 1 запирается. Одновременно с этим возникает ток через резистор 6, что вызывает отпирание транзистора 4, коллекторный ток которого осуществляет форсированный перезаряд суммарной нагрузочной емкости на выходе элемента 3.

Когда перезаряд емкости заканчивается, на выходе элемента 3 устанавливается сигнал, соответствующий логической «1, равный (Уи-п.-UBS), (Ujig - напряжение «коллектор-эмиттер транзистора 4 в режиме насыщения). В этом состоянии элемент потребляет добавочный ток, ограниченный резистором 6 и поэтому не зависящий от коэффициентов усиления транзисторов.

Таким образом, средний потребляемый ток предлагаемого логического элемента

5 (полусумма токов потребляемых в состояниях логического «О и логической «1) равен току источника 2 и половине тока резистора 6 в состоянии логической «I на выходе элемента 3, т. е. половине тока базы транзистора 4 в этоц состоянии. Задержка переключения предлагаемого элемента определяется временем переключения транзистора 1.

17)

10 (5)

Г

I 19 20

Л.

9(2)

пг

Ш Ш Ш .|-j

TzrJ J f

(риг. 2

A-A

22 23 21

JLL

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1983 |

|

SU1150734A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Запоминающий элемент | 1982 |

|

SU1277209A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Логический вентиль | 1980 |

|

SU940308A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ, со-, держащий транзистор первого типа проводимости с инжекционным питанием, эмиттер которого подключен к общей шине, коллектор - к выходу элемента и к коллектору транзистора второго типа проводимости, эмиттер которого подключен к шине питания, отличающийся тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, введен диод Шоттки, анод которого подключен к базе транзистора первого типа проводимости, а катод - ко входу элемента и через резистор - к базе транзистора второго типа проводимости.

J 1211 12

/« //

7 7

13

VU8. 3

| УСТАНОВКА ДЛЯ ВЫБИВКИ ЛИТЕЙНЫХ ФОРМ И ВИБРАЦИОННОЕ ВЫБИВНОЕ УСТРОЙСТВО | 1990 |

|

RU2015840C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство согласования | 1976 |

|

SU557438A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-08-15—Публикация

1984-02-16—Подача