Область техники

Настоящее изобретение имеет отношение к устройству захвата изображения и системе захвата изображения.

Уровень техники

Примеры устройства захвата изображения, используемого в электронной видеокамере или электронном фотоаппарате, включают в себя датчик MOS или датчик адреса X-Y. Датчик адреса X-Y получает сигнал из пикселя, расположенного в заданной позиции, посредством указания адреса. С помощью этого датчик адреса X-Y реализует "режим считывания всех пикселей", в котором получаются сигналы всех пикселей, и "режим сокращенного считывания", в котором пропускаются некоторые строки и столбцы, и сигналы получаются из других пикселей.

В документе PTL 1 представлено первое средство хранения, которое хранит адрес, по которому должно быть выполнено сканирование затвора, и второе средство хранения, которое хранит адрес, по которому должно быть выполнено считывающее сканирование, с тем чтобы, например, выполнить сложную операцию затвора в "режиме сокращенного считывания". Кроме того, документ PTL 1 также раскрывает метод совместного использования пикселей, где множество пикселей совместно использует плавающую диффузионную область, которая временно содержит заряд, сохраненный в пикселях, и которая является частью транзисторов, содержащихся в пикселях, а также схему для выбора пикселей в упомянутом методе.

Список литературы

Патентная литература

PTL 1: Выложенный патент Японии № 2008-288903

Раскрытие изобретения

Техническая проблема

Однако если раскрытая в документе PTL 1 схема используется в датчике изображения, который использует метод совместного использования пикселей, выбор пикселя может быть выполнен ненадлежащим образом, и в соответствии с этим может быть выполнена недопустимая операция.

Задача настоящего изобретения состоит в том, чтобы обеспечить устройство захвата изображения, систему захвата изображения и способ управления устройством захвата изображения, которые препятствуют выполнению недопустимой операции, даже когда используется метод совместного использования пикселей.

Решение проблемы

Настоящее изобретение обеспечивает устройство захвата изображения, содержащее пиксельную матрицу, включающую в себя множество пикселей, расположенных в матрице, и блок выбора строки, который выбирает одну из строк пикселей и который содержит блок формирования адреса, который формирует сигнал адреса, соответствующий адресу одной из строк пикселей, способом мультиплексирования с временным разделением, декодер, который декодирует сигнал адреса, сформированный блоком формирования адреса, и выдает результирующее декодированное значение, первый блок хранения, который хранит декодированное значение, соответствующее адресу одной из строк пикселей, из которых должны быть считаны сигналы, и второй блок хранения, который хранит декодированное значение, соответствующее адресу одной из строк пикселей, которые должны быть инициализированы. Среди пикселей, расположенных в матрице, несколько пикселей, включенных в смежные строки, формируют множество блоков пикселей, имеющих соответствующие совместно используемые транзисторы, и блок выбора строки дополнительно содержит третий блок хранения, который хранит декодированное значение, соответствующее одному из блоков пикселей, содержащему совместно используемые транзисторы.

Полезные результаты изобретения

В соответствии с настоящим изобретением, даже когда используется метод совместного использования пикселей, пиксели могут быть выбраны должным образом, и может быть предотвращена недопустимая операция.

Краткое описание чертежей

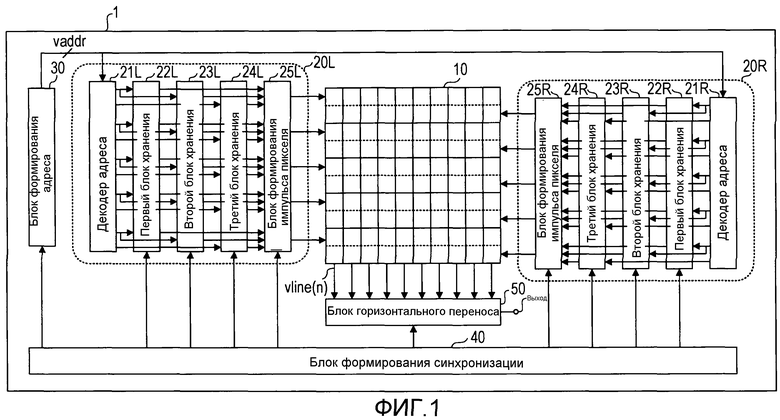

Фиг. 1 - блок-схема, иллюстрирующая устройство захвата изображения в соответствии с настоящим изобретением.

Фиг. 2 - принципиальная схема, иллюстрирующая конфигурацию устройства захвата изображения в соответствии с первым вариантом осуществления.

Фиг. 3 - временная диаграмма, иллюстрирующая работу устройства захвата изображения в соответствии с первым вариантом осуществления.

Фиг. 4 - принципиальная схема, иллюстрирующая конфигурацию устройства захвата изображения в соответствии со вторым вариантом осуществления.

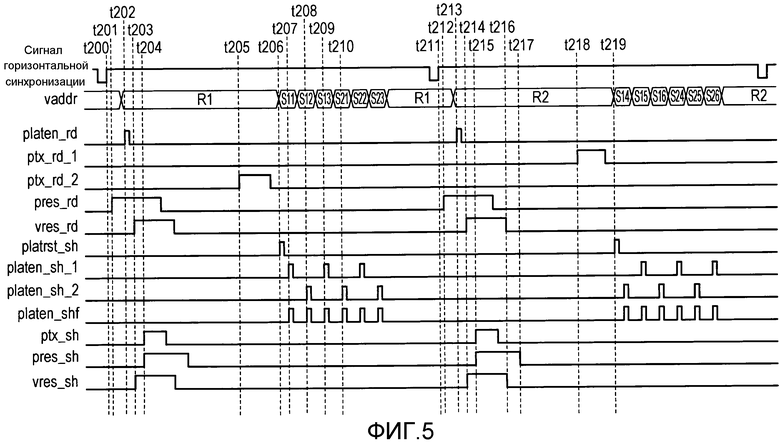

Фиг. 5 - временная диаграмма, иллюстрирующая работу устройства захвата изображения в соответствии со вторым вариантом осуществления.

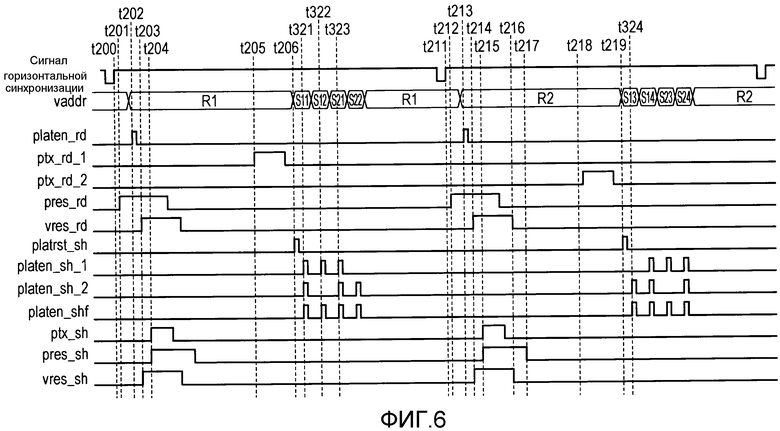

Фиг. 6 - временная диаграмма, иллюстрирующая работу устройства захвата изображения в соответствии с третьим вариантом осуществления.

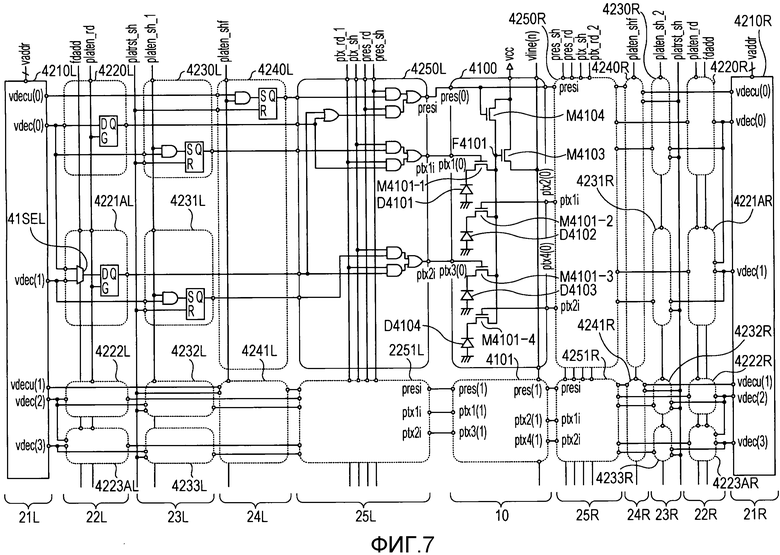

Фиг. 7 - принципиальная схема, иллюстрирующая конфигурацию устройства захвата изображения в соответствии с четвертым вариантом осуществления.

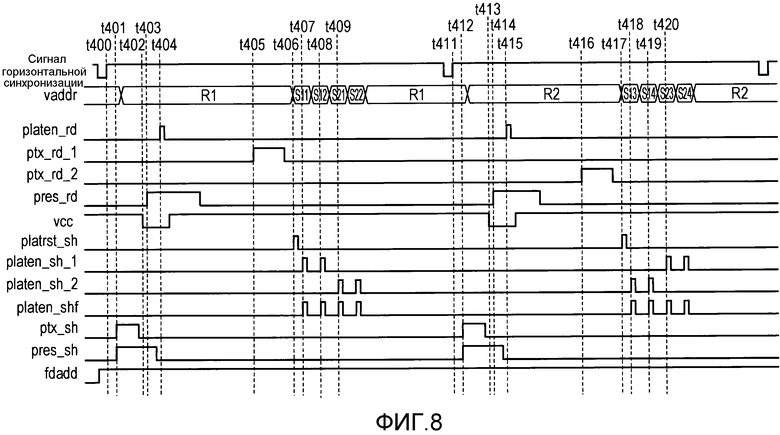

Фиг. 8 - временная диаграмма, иллюстрирующая работу устройства захвата изображения в соответствии с четвертым вариантом осуществления.

Фиг. 9 - принципиальная схема, иллюстрирующая конфигурацию устройства захвата изображения в соответствии с пятым вариантом осуществления.

Фиг. 10 - временная диаграмма, иллюстрирующая работу устройства захвата изображения в соответствии с пятым вариантом осуществления.

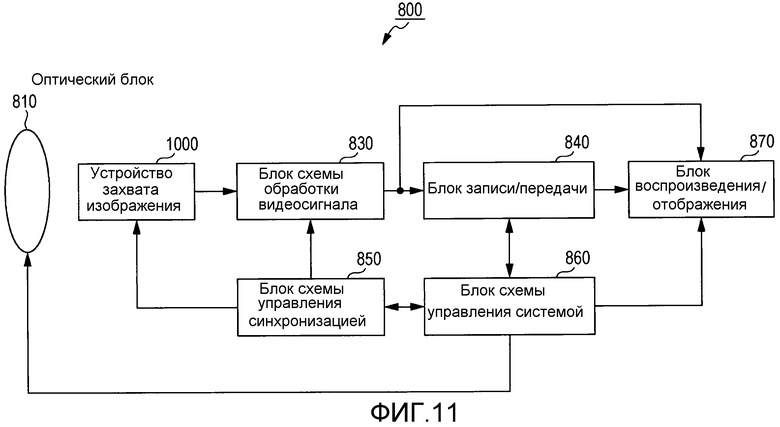

Фиг. 11 - блок-схема, иллюстрирующая систему захвата изображения в соответствии с шестым вариантом осуществления.

Осуществление изобретения

Чтобы разъяснить преимущество настоящего изобретения, будут подробно описаны проблемы, которые могут возникнуть в конфигурации, описанной в документе PTL 1.

Обычно используется метод выбора пикселей в области пикселей, включающей в себя пиксели, расположенные в матрице, с использованием множества блоков выбора строки. В качестве примера будет описан случай, в котором пиксели в строках с нечетными номерами выбираются с использованием одного из двух блоков выбора строки и пиксели в строках с четными номерами выбираются с использованием другого блока выбора. В предположении, что пиксели в первой и второй строках, смежных друг с другом, совместно используют плавающую диффузионную область (в дальнейшем называемую "FD-областью"), пикселями в первой строке управляет один из блоков выбора строки, и пикселями во второй строке управляет другой блок выбора строки.

Когда два пикселя, которые совместно используют FD-область, используются в качестве одного блока пикселей и множество блоков пикселей расположены в матрице, операция затвора может быть выполнена над пикселем в первой строке, содержащимся в некотором блоке пикселей, и операция затвора может не выполняться над пикселем во второй строке, содержащимся в том же самом блоке пикселей.

Когда в этом случае используется схема, описанная в документе в PTL 1, в схеме, которая управляет пикселями в первой строке, защелка, используемая для выбора строки затвора, выдает "1", тогда как в схеме, которая управляет пикселями во второй строке, защелка, используемая для выбора строки затвора, выдает "0". При этом, когда подается сигнал STR для выполнения операции затвора, схема, которая управляет пикселями в первой строке, выдает сигнал RST со значением "1", тогда как схема, которая управляет пикселями во второй строке, выдает сигнал RST со значением "0". Таким образом, разные сигналы выдаются от двух разных схем выбора, и поэтому неясно, должны ли переключатели, которыми управляют сигналы RST, быть в проводящих состояниях или нет. В соответствии с этим может быть выполнена недопустимая операция.

Первый вариант осуществления

Первый вариант осуществления настоящего изобретения будет описан со ссылкой на сопроводительные чертежи.

Фиг. 1 является блок-схемой, иллюстрирующей устройство захвата изображения в соответствии с настоящим изобретением. Устройство 1 захвата изображения содержит пиксельную матрицу 10, блоки 20L и 20R выбора строки, блок 30 формирования адреса, блок 40 формирования синхронизации и блок 50 горизонтального переноса. Эти компоненты могут быть расположены на одной полупроводниковой подложке, и некоторые из них могут быть расположены на другой полупроводниковой подложке.

Пиксельная матрица 10 включает в себя множество пикселей, расположенных в виде матрицы. Пиксели в смежных строках совместно используют схемы. В дальнейшем множество пикселей, которые совместно используют схемы, называется "блоком пикселей". Таким образом, пиксельная матрица 10 включает в себя множество блоков пикселей, расположенных в виде матрицы.

Пиксельная матрица 10 расположена между блоков 20L и 20R выбора строки. Блок 20L выбора строки выбирает пиксели в строках с нечетным номером в пиксельной матрице 10, тогда как блок 20R выбирает пиксели в строках с четными номерами в пиксельной матрице 10. В частности, блок 20L выбора строки, служащий в качестве первой схемы выбора строки, и блок 20R выбора строки, служащий в качестве второй схемы выбора строки, выполнены с возможностью поочередно выбирать строки пикселей в пиксельной матрице 10.

Кроме того, блок 20L выбора строки содержит декодер 21L адреса, первый блок 22L хранения, второй блок 23L хранения, третий блок 24L хранения и блок 25L формирования импульса пикселя. Декодер 21L адреса выдает декодированное значение, полученное посредством декодирования значения адреса, сформированного блоком 30 формирования адреса, и выбирает адрес, соответствующий значению адреса.

Первый блок 22L хранения хранит декодированное значение, выданное декодером 21L адреса. Выходная информация первого блока 22L хранения используется в качестве адреса строки, из которой сигналы считываются из пикселей, содержащихся в пиксельной матрице 10.

Второй блок 23L хранения хранит декодированное значение, выданное декодером 21L адреса. Выходная информация второго блока 23L хранения используется в качестве адреса строки, в которой сбрасываются блоки фотоэлектрического преобразования, содержащиеся в пикселях в пиксельной матрице 10.

Третий блок 24L хранения хранит декодированное значение, выданное декодером 21L адреса. Выходная информация третьего блока 24L хранения используется для управления элементом, совместно используемым множеством пикселей, содержащихся в блоке пикселей пиксельной матрицы 10.

Блок 30 формирования адреса формирует значение адреса на основе сигнала, выданного из блока 40 формирования синхронизации, и подает сформированное значение адреса на блоки 20L и 20R выбора строки. Блок 30 формирования адреса выдает сигнал адреса vaddr способом мультиплексирования с временным разделением таким образом, что один декодер адреса выбирает множество адресов. В частности, блок формирования адреса включает в себя множество схем, которые формируют значения адресов, выбирает выходную информацию одной из схем на основе сигнала, поданного от блока 40 формирования синхронизации, и выдает выбранную выходную информацию в качестве адреса сигнала vaddr.

Блок 40 формирования синхронизации подает сигнал, используемый для управления синхронизацией, когда блок 30 формирования адреса формирует значение адреса, и подает сигнал, используемый для управления синхронизацией операций блоков 20L и 20R выбора строки и блока 50 горизонтального переноса.

Блок 50 горизонтального переноса выдает сигналы, считанные из пиксельной матрицы 10, через вертикальные сигнальные линии vline(n) с выходного вывода. В частности, блок 50 горизонтального переноса включает в себя усилители, аналого-цифровые (AD) преобразователи, схемы CDS и запоминающие схемы линии, которые обеспечены для отдельных вертикальных сигнальных линий vline(n), и сигналы, считанные из пиксельной матрицы 10, последовательно выводятся с выхода с использованием схемы горизонтального сканирования. Запоминающие схемы линии могут представлять собой аналоговую память или цифровую память, например SRAM и схемы защелок.

Блоки 20L и 20R выбора строки имеют одинаковые конфигурации, и поэтому описание блока 20R выбора строки опущено. Схема горизонтального сканирования может состоять из декодера, чтобы можно было получить доступ к произвольной строке. Таким образом, произвольный доступ реализован в комбинации с блоками 20L и 20R выбора строки. Очевидно, что сканирование последовательно выполняется в порядке адресов, даже когда блок выбора строки и схема горизонтального сканирования состоят из декодеров.

Фиг. 2 является подробной принципиальной схемой конфигурации, показанной на фиг. 1, за исключением блока 40 формирования синхронизации и блока 50 горизонтального переноса.

Пиксельная матрица 10 включает в себя множество блоков 1100, 1101 и т.д. пикселей, которые расположены в ней, и на фиг. 2 подробно показаны блоки пикселей, расположенные в матрице из четырех строк и одного столбца. Блок 1100 пикселей содержит четыре пикселя. Пиксель в первой строке содержит фотодиод D1101, который представляет собой блок фотоэлектрического преобразования, транзистор M1101-1 переноса, транзистор M1103 усиления, транзистор M1104 сброса, служащий в качестве блока сброса, и транзистор M1105 выбора. Когда транзистор M1101-1 переноса приведен в проводящее состояние, заряд, сохраненный в фотодиоде D1101, переносится в узел затвора транзистора M1103 усиления. Хотя это не показано, затвор транзистора M1103 усиления соединен с плавающей диффузионной областью, служащей в качестве первого основного электрода транзистора M1101-1 переноса на полупроводниковой подложке, и заряд фотодиода переносится в плавающую диффузионную область. В дальнейшем плавающая диффузионная область называется "FD-областью". Транзистор M1103 усиления имеет первый основной электрод, который принимает подачу напряжения питания vcc, и второй основной электрод, который соединен с одной из вертикальных сигнальных линий vline(n) через транзистор M1105 выбора. Когда транзистор M1105 выбора приведен в проводящее состояние, транзистор M1103 усиления формирует схему истокового повторителя вместе с токовым истоком, соединенным с вертикальной сигнальной линией vline(n), и выдает сигнал, соответствующий потенциалу FD-области. Первый основной электрод транзистора M1104 сброса соединен с FD-областью. Когда транзистор M1104 сброса приведен в проводящее состояние, он сбрасывает FD-область в соответствии с потенциалом, поданным на второй электрод. Пиксель во второй строке содержит фотодиод D1102, транзистор M1101-2 переноса, транзистор M1103 усиления, транзистор M1104 сброса, служащий в качестве блока сброса, и транзистор M1105 выбора. Аналогичным образом каждый из пикселей в третьей и четвертой строках содержит фотодиод, транзистор переноса, транзистор усиления и транзистор сброса. Эти четыре пикселя совместно используют транзистор M1103 усиления, транзистор M1104 сброса и транзистор M1105 выбора. Как в случае блока пикселей 1100, в каждом блоке 1101, 1102 и т.д. пикселей транзистор M1103 усиления, транзистор M1104 сброса и транзистор M1105 выбора совместно используются пикселями в смежных четырех строках.

Декодер 21L адреса принимает сигнал адреса vaddr, выдаваемый из блока 30 формирования адреса на основе управляющего сигнала, выданного из блока 40 формирования синхронизации. Сигнал адреса vaddr представляет собой n-битовый сигнал, например представляет блок пикселей с использованием старших (n-1) битов и представляет пиксели в пределах блока пикселей с использованием n битов. На фиг. 2 декодированное значение vdecu(x) установлено с использованием n битов (0≤×≤(2^(n-1))-1), и декодированное значение vdec(y) установлено с использованием младших n битов (0≤y≤(2^n)-1). Следует отметить, что когда блок пикселей содержит два пикселя, блок пикселей представлен m битами сигнала адреса, имеющего m битов.

Множество первых схем 1220L, 1221L и т.д. хранения, содержащихся в первом блоке 22L хранения, содержат соответствующие D-защелки, которые хранят 1-битовые данные. D-защелка, содержащаяся в первой схеме 1220L хранения, имеет D-вход с выводом vdec(0) декодера 21L адреса, и G-вход, соединенный с линией, которая передает сигнал platen_rd. Первые схемы 1221L, 1222L и т.д. хранения также содержат соответствующие D-защелки, но их D-выходы соединены с другими выходами декодера 21L адреса. Линия, которая передает сигнал platen_rd, также соединена с другими схемами 1221L, 1222L и т.д. хранения.

Вторые схемы 1230L, 1231L и т.д. хранения, которые содержатся во втором блоке 23L хранения, содержат соответствующие логические схемы "И" и соответствующие SR-защелки, имеющие S-входы, соединенные с соответствующими выходами логических схем "И". Первый вход логической схемы "И" соединен с выходом vdec(0) декодера 21L адреса, и второй вход соединен с линией, которая передает сигнал platen_sh_1. R-вход SR-защелки соединен с линией, которая передает сигнал platrst_sh_1. Линия, которая передает сигнал platrst_sh, также соединена с другими вторыми схемами 1231L, 1232L и т.д. хранения, содержащимися во втором блоке хранения.

Третьи схемы 1240L, 1241L и т.д. хранения, содержащиеся в третьем блоке 24L хранения, содержат соответствующие логические схемы "И" и соответствующие SR-защелки, имеющие S-входы, соединенные с выходами соответствующих логических схем "И". Первый вход логической схемы "И" соединен с выходом vdecu(0) декодера 21L адреса, и второй вход соединен с линией, которая передает сигнал platen_shf. R-вход SR-защелки соединен с линией, которая передает сигнал platrst_sh. Линии, которые передают сигналы platen_shf и platrst_sh, также соединены с другими третьими схемами 1241L, 1242L и т.д. хранения, содержащимися в третьем блоке хранения.

Каждая из схем 1250L, 1251L и т.д. формирования импульса пикселя, содержащихся в блоке 25L формирования импульса пикселя, включает в себя логические схемы "И" и логические схемы "ИЛИ". Однако конфигурации схем не ограничены конфигурацией этого варианта осуществления. Схема 1250L формирования импульса пикселя выдает сигналы presi, pseli, ptx1i и ptx2i, которые будут поданы на блок 1100 пикселей как сигналы pres(0), psel(0), ptx1(0) и ptx3(0). Сигнал presi формируется как логическое "ИЛИ" логического "И" выхода логической схемы "ИЛИ", которая выдает логическое "ИЛИ" первых схем 1220L и 1221L хранения и сигнала pres_rd, и логического "И" выхода третьей схемы 1240L хранения и сигнала pres_sh. Сигнал pseli формируется как логическое "ИЛИ" выхода схемы "ИЛИ", которая выдает логическое "ИЛИ" первых схем 1220L и 1221L хранения и сигнала psel. Далее, сигнал ptx1i формируется как логическое "ИЛИ" логического "И" выхода первой схемы 1220L хранения и сигнала ptx_rd_1 и логического "И" выхода второй схемы 1230L хранения и сигнала ptx_sh. Сигнал ptx2i формируется как логическое "ИЛИ" логического "И" первой схемы 1221L хранения и сигнала ptx_rd_1 и логического "И" выхода второй схемы 1231L хранения и сигнала ptx_sh.

Будет описана конфигурация блока 20R выбора строки, отличающаяся от конфигурации блока 20L выбора строки. Поскольку блок 20R выбора строки управляет пикселями в строках пиксельной матрицы 10 с четными номерами, он отличается от блока 20L выбора строки тем, что вывод сигналов из блока 25R формирования импульса пикселя подается на пиксели в строках с четными номерами. Таким образом, второй блок 23R хранения принимает сигнал platen_sh_2 вместо сигнала platen_sh_1, подаваемый на второй блок 23L хранения. Аналогичным образом, блок 25R формирования импульса пикселя принимает сигнал ptx_rd_2 вместо сигнала ptx_rd_1, подаваемого на блок 25L формирования импульса пикселя. В других блоках на блоки 20L и 20R выбора строки подаются те же самые сигналы.

Следует отметить, что сигналы platen_rd, platen_sh_1, platen_sh_2, platrst_sh, platen_shf, ptx_rd_1, ptx_rd_2, ptx_sh, pres_rd, pres_sh и psel формируются блоком 40 формирования синхронизации.

Далее будет описана работа устройства 1 захвата изображения, показанного на фиг. 1 и 2, со ссылкой на временную диаграмму, показанную на фиг. 3. Когда обозначения L и R специально не указываются в дальнейшем описании, блоки 20L и 20R выбора строки выполняют одну и ту же операцию.

Здесь в качестве примера будет описан случай, когда в пиксельной матрице 10 сигналы считываются из пикселей в первой строке, четвертой строке, седьмой строке и так далее, и операция затвора выполняется в дополнение к группе с первой по третью строки над группой с четвертой по шестую строки, группой с седьмую по девятую строки и так далее, группой с N-й по (N+2)-ю строки, группой с (N+3)-й по (N+5)-ю строки, группой с (N+6)-ю по (N+8)-ю строки и так далее. Операция затвора означает сброс фотодиодов и также упоминается как инициализация пикселей. Предполагается, что в момент времени t100, показанный на фиг. 3, SR-защелки, содержащиеся во втором и третьем блоках 23 и 24 хранения, поддерживают низкий уровень.

Сначала сигнал горизонтальной синхронизации подается от внешнего устройства, которое не показано, на блок 40 формирования синхронизации в момент времени t100, блок 40 формирования синхронизации переводит сигнал platen_rd на высокий уровень в момент времени t101. В момент времени t102, поскольку значение R1 сигнала адреса vaddr, поданного от блока 30 формирования адреса, равно "0", только выходы vdecu(0) и vdec(0) среди выходов декодера 21 адреса переведены на высокий уровень. Таким образом, выход D-защелки первой схемы 1220 хранения переведен на высокий уровень. Сигнал горизонтальной синхронизации определяет период горизонтальной синхронизации, в котором считываются сигналы, соответствующие пикселям для строки.

Когда сигнал psel переводится на высокий уровень в момент времени t102, транзистор M1005 выбора, содержащийся в блоке 1100 пикселей, переводится на высокий уровень посредством логического "И" выходов D-защелок, содержащихся в первых схемах 1220L и 1220R хранения, и сигнала psel. Таким образом, транзистор M1003 усиления, содержащийся в блоке 1100 пикселей, формирует истоковый повторитель вместе с токовым истоком, который не показан, соединенным с вертикальными сигнальными линиями vline(n), и подает сигнал, соответствующий потенциалу FD-области F1101, на одну соответствующую линию из вертикальных сигнальных линий vline(n).

Когда сигнал pres_rd переводится на высокий уровень в момент времени t103, сигнал pres(0), который должен быть подан на блок 1100 пикселей, переводится на высокий уровень посредством логического "И" сигнала pres_rd и выходов первых схем 1220L и 1220R хранения.

В период времени с момента t103 до момента t105 транзистор M1104 сброса, содержащийся в блоке 1100 пикселей, переводится в проводящее состояние, и FD-область F1101 сбрасывается. При этом сигнал, имеющий уровень, соответствующий сбросу FD-области F1101, подается на одну соответствующую линию из вертикальных сигнальных линий vline(n), и сигнал содержит шумовой компонент, сформированный транзистором M1104 сброса, транзистором M1004 усиления и FD-областью F1101. В конфигурации, в которой блок 50 горизонтального переноса содержит схему CDS, сигналы, поданные на вертикальные сигнальные линии vline(n) в этом периоде, подвергаются выборке.

Когда сигнал ptx_rd_1 переводится на высокий уровень в момент времени t106, сигнал ptx1(0), который должен быть подан на блок 1100 пикселей, переводится на высокий уровень посредством логического "И" сигнала ptx_rd_1 и выхода защелки, содержащейся в первой схеме 1220L хранения, и, таким образом, транзистор M1001-1 переноса переводится в проводящее состояние. Посредством этого заряды, сохраненные в фотодиоде D1101, переносятся в FD-область F1101, и в соответствии с этим изменяется потенциал FD-области F1101, и изменяется уровень сигнала, поданного на одну соответствующую линию из вертикальных сигнальных линий vline(n). Сигнал изменяется на величину заряда, сформированного посредством фотоэлектрического преобразования относительно уровня, полученного сразу после сброса FD-области F1101. В соответствии с этим шумовой компонент может быть уменьшен посредством получения разности между сигналом и шумовым компонентом, сохраненным в схеме CDS.

В момент времени t107 значение сигнала адреса vaddr, подаваемого от блока 30 формирования адреса, изменяется с R1 на S11. Следует отметить, что значение "S11" представляет адрес пикселя, который должен быть сброшен (чтобы быть подвергнутым операции затвора), и равно "0" в этот момент. В соответствии с этим среди сигналов, подаваемых от декодера 21 адреса, только сигналы vdecu(0) и vdec(0) переведены на высокий уровень.

Кроме того, в момент времени t107 сигнал platrst_sh переводится на высокий уровень, и в соответствии с этим SR-защелки второго и третьего блоков 23 и 24 хранения сбрасываются.

В момент времени t108 сигналы platen_sh_1, platen_sh_2, platen_shf переводятся на высокий уровень. Выходы SR-защелок, содержащихся во вторых схемах 1230L и 1230R хранения, переводятся на высокий уровень вследствие логического "И" сигналов platen_sh_1, platen_sh_2 и сигнала vdec(0). Кроме того, выходы из третьих схем 1240L и 1240R хранения переводятся на высокий уровень посредством логического "И" сигналов platen_shf и vdecu(0).

После этого значение сигнала адреса vaddr, подаваемое от блока 30 формирования адреса, изменяется на S12. При этом значение S12 равно "1". В соответствии с этим среди сигналов, подаваемых от декодера 21 адреса, только сигналы vdecu(0) и vdec(1) переведены на высокий уровень.

В момент времени t109 сигналы platen_sh_1 и platen_shf переводятся на высокий уровень. Выход из SR-защелки второй схемы 1231L хранения переводится на высокий уровень посредством логического "И" сигналов platen_sh_1 и vdec(1). Кроме того, выходы из SR-защелок третьих схем 1240L и 1240R хранения переводятся на высокий уровень посредством логического "И" сигналов platen_shf и vdecu(0).

Посредством описанных выше операций, выполняемых с момента времени t107 до момента времени t109, вторые схемы 1230L, 1230R и 1231L хранения и третьи схемы 1240L и 1240R хранения, соответствующие пикселям, содержащимся в строках с первой по третью, устанавливаются на высокий уровень.

Следует отметить, что адреса, соответствующие пикселям в третьей строке, устанавливаются с использованием значения S12, и вторая схема 1231L хранения устанавливается с использованием сигнала platen_sh_1, и одновременно третьи схемы 1240L и 1240R хранения устанавливаются с использованием сигнала platen_shf. В этом варианте осуществления пиксели, содержащиеся в строках с первой по третью, сбрасываются в блоке 1100 пикселей, чтобы сбросить строки с первой по третью, но пиксели, содержащиеся в четвертой строке, не сбрасываются. В конфигурации, раскрытой в документе PTL 1, транзисторы сброса должны включаться для пикселей в строках с первой по третью, тогда как транзисторы сброса должны выключаться для пикселей в четвертой строке, и, таким образом, может быть выполнена недопустимая операция. С другой стороны, в настоящем изобретении третий блок хранения обеспечен, чтобы управлять транзисторами, совместно используемыми множеством пикселей, содержащихся в блоке пикселей. Таким образом, даже в случае, когда некоторые пиксели, содержащиеся в блоке пикселей, сброшены, а другие пиксели не сброшены, может быть выполнена надлежащая операция.

С момента времени t110 операция, начинающаяся с момента времени t107, аналогичным образом выполняется над строками с N-й по (N+2)-ю таким образом, чтобы защелки вторых и третьих блоков хранения были установлены. Посредством описанной выше операции пиксели в шести строках, включающих в себя строки с первой по третью и с N-й по (N+2)-ю, устанавливаются в качестве пикселей, которые будут подвергнуты операции затвора. На фиг. 3 показан пример, в котором сигнал адреса vaddr установлен равным S22 и после этого изменяется на R1. Однако значение сигнала адреса vaddr может остаться равным S22.

Блок 40 формирования синхронизации заставляет описанную выше схему CDS выполнить операцию выборки после того, как сигнал ptx_rd_1, который был переведен на высокий уровень в момент времени t105, переводится на низкий уровень. Затем, после того как сигналы, которые были обработаны схемой CDS, сохранены в памяти линии, блок 40 формирования синхронизации управляет блоком 50 горизонтального переноса таким образом, что блок 50 горизонтального переноса выдает с выхода сигналы, соответствующие пикселям в первой строке.

В момент времени t111 начинается операция считывания пикселей в пятой строке. Операция считывания, выполняемая над четвертой строкой, аналогична операции, выполняемой над первой строкой, описанной со ссылкой на период времени с момента t100 до момента t111.

Поскольку пиксели, содержащиеся в четвертой строке, содержатся в четвертой строке блока 1100 пикселей, в момент времени t117 подается сигнал ptx_rd_2 вместо сигнала ptx_rd_1. Кроме того, с момента времени t118 устанавливаются вторые и третьи блоки хранения, соответствующие пикселям, содержащимся в строках с четвертой по шестую и с (N+3)-й по (N+5)-ю. Однако, поскольку пиксели в четвертой строке содержатся в четвертой строке блока 1100 пикселей, моменты времени, когда подаются сигналы platen_sh_1 и platen_sh_2, отличаются от моментов времени при операции считывания, выполняемой над второй строкой.

Когда сигналы ptx_sh и pres_sh переводятся на высокий уровень в момент времени t115, транзисторы сброса и транзисторы переноса пикселей, содержащихся в строках с первой по третью и с N-й по (N+2)-ю, включаются. В соответствии с этим пиксели в строках с первой по третью и с N-й по (N+2)-ю сбрасываются.

Как описано выше, в соответствии с настоящим вариантом осуществления, поскольку адреса сохраняются в третьем блоке хранения для управления совместно используемыми элементами, содержащимися в одном и том же блоке пикселей, даже когда пиксели, которые должны быть сброшены, и пиксели, которые не должны быть сброшены, содержатся в одном и том же блоке пикселей, может быть выполнена надлежащая операция.

Второй вариант осуществления

Со ссылкой на чертежи будет описан второй вариант осуществления настоящего изобретения. Фиг. 4 является подробной принципиальной схемой конфигурации, показанной на фиг. 1, за исключением блока 40 формирования синхронизации и блока 50 горизонтального переноса.

Пиксельная матрица 10 содержит множество блоков 2100, 2101 и т.д. пикселей, расположенных в ней. На фиг. 2 подробно показаны блоки пикселей, расположенные в матрице с четырьмя строками и одним столбцом. Блок 2100 пикселей содержит два пикселя. Пиксель в первой строке содержит фотодиод D2101, служащий в качестве блока фотоэлектрического преобразования, транзистор M2101 переноса, служащий в качестве блока переноса, транзистор M2103 усиления, служащий в качестве блока вывода пикселя, и транзистор M2104 сброса, служащий в качестве блока сброса. Когда транзистор M2101 переноса приведен в проводящее состояние, заряд, сохраненный в фотодиоде D2101, переносится в узел затвора транзистора M2103 усиления. Хотя это не показано, на полупроводниковой подложке затвор транзистора M2103 усиления соединен с FD-областью, служащей в качестве первого основного электрода транзистора M2101 переноса, и заряд, поданный от фотодиода, переносится в FD-область. Транзистор M2103 усиления имеет первый основной электрод, который принимает напряжение питания vcc, и второй основной электрод, соединенный с одной соответствующей линией из вертикальных сигнальных линий vline(n). Транзистор M2103 усиления и токовый исток, соединенный с вертикальными сигнальными линиями vline(n), формируют истоковый повторитель, который выдает сигнал, соответствующий потенциалу FD-области. Транзистор M2104 сброса имеет первый основной электрод, соединенный с FD-областью. Когда транзистор M2104 приведен в проводящее состояние, он сбрасывает FD-область на основе потенциала, поданного на его второй основной электрод. Пиксель во второй строке содержит фотодиод D2102, транзистор M2102 переноса, транзистор M2103 усиления, служащий в качестве блока вывода пикселя, и транзистор M2104 сброса, служащий в качестве блока сброса. Эти два пикселя совместно используют транзистор M2103 усиления и транзистор M2104 сброса. Как и блок 2100 пикселей, каждый блок 2101, 2102 и т.д. пикселей имеет два пикселя в двух смежных строках, которые совместно используют транзистор усиления и транзистор сброса. Как видно из этого описания, пиксели в этом варианте осуществления отличаются от пикселей в первом варианте осуществления тем, что каждый из пикселей не содержит транзистор выбора.

Декодер 21L адреса принимает сигнал адреса vaddr, поданный от блока 30 формирования адреса в соответствии с управляющим сигналом, поданным от блока 40 формирования синхронизации. Сигнал адреса vaddr представляет собой n-битовый сигнал и имеет значение, соответствующее одному из пикселей в строках с нечетными номерами, содержащихся в блоках пикселей, расположенных в пиксельной матрице 10. Например, когда сигнал адреса vaddr имеет значение, соответствующее "1", декодер 21L адреса выдает сигнал vdec(1) на высоком уровне, и другие выходные сигналы vdec(0), vdec(2) и т.д. находятся на низком уровне.

Множество схем 2220L, 2221L и т.д. хранения, содержащиеся в первом блоке 22L хранения, содержат D-защелки, каждая из которых хранит 1-битовые данные. D-защелка, содержащаяся в схеме 2220L хранения, имеет D-вход, соединенный с выходом vdec(0) декодера 21L адреса, и G-вход, соединенный с линией, используемой для передачи сигнала platen_rd. Как и схема 2220L хранения, каждая из первых схем 2221L, 2222L и т.д. хранения содержит D-защелки. Однако разные выходы подаются от декодера 21L адреса на разные D-защелки. Линия, используемая для передачи сигнала platen_rd, также соединена совместно с первыми схемами 2221L, 2222L и т.д. хранения.

Каждая из вторых схем 2230L, 2231L и т.д. хранения, содержащихся во втором блоке 23L хранения, содержит логическую схему "И" и SR-защелку, имеющую S-вход, соединенный с выходом логической схемы "И". Первый вход логической схемы "И" соединен с выходом vdec(0) декодера 21L адреса, и второй вход соединен с линией, используемой для передачи сигнала platen_sh_l. R-вход SR-защелки соединен с линией, используемой для передачи сигнала platrst_sh. Линия, используемая для передачи сигнала platrst_sh, также соединена совместно со вторыми схемами 2231L, 2232L и т.д. хранения.

Каждая из третьих схем 2240L, 2241L и т.д. хранения, содержащихся в третьем блоке 24L хранения, содержит логическую схему "И" и SR-защелку, имеющую S-вход, соединенный с выходом логической схемы "И". Первый вход логической схемы "И" соединен с выходом vdec(0) декодера 21L адресов, и второй вход соединен с линией, используемой для передачи сигнала platen_shf. R-вход SR-защелки соединен с линией, используемой ля передачи сигнала platrst_sh. Линии, которые передают сигналы platen_shf и platrst_sh, соединены совместно с другими схемами 2241L, 2242L и т.д. хранения, содержащимися в третьем блоке хранения.

Каждая из схем 2250L, 2251L и т.д. формирования импульса пикселя, содержащихся в блоке 25L формирования импульса пикселя, содержит логические схемы "И" и схемы "ИЛИ". Однако конфигурации схем не ограничены конфигурацией этого варианта осуществления. Схема 2250L формирования импульса пикселя выдает сигналы vresi, presi и ptxi, которые предоставлены как сигналы vres(0), pres(0) и ptxi(0), блоку 2100 пикселей. Сигнал vresi формируется как логическое "ИЛИ" логического "И" выхода схемы 2220L хранения и сигнала vres_rd и логического "И" выхода третьей схемы 2240L хранения и сигнала vres_sh. Сигнал presi формируется как логическое "ИЛИ" логического "И" выхода схемы 2220L хранения и сигнала pres_rd и логического "И" выхода третьей схемы 2240L хранения и сигнала pres_sh. Кроме того, сигнал ptxi формируется как логическое "ИЛИ" логического "И" выхода схемы 2220L хранения и сигнала ptx_rd_1 и логического "И" выхода второй схемы 2230L хранения и сигнала ptx_sh.

Будут описаны части блока 20R выбора строки, отличающиеся от частей блока 20L выбора строки.

Поскольку блок 20R выбора строки управляет пикселями в строках с четными номерами, содержащимися в пиксельной матрице 10, сигналы, выводимые из блока 25R формирования импульса пикселя, подаются на пиксели в строках с четными номерами, которые отличаются от блока 20L выбора строки. Таким образом, сигнал platen_sh_2 подается на второй блок 23R хранения вместо сигнала platen_sh_1, подаваемого на второй блок 23L хранения. Аналогичным образом сигнал ptx_rd_2 подается на блок 25R формирования импульса пикселя вместо сигнала ptx_rd_1, подаваемого на блок 25L формирования импульса пикселя. Другие сигналы, подаваемые на блок 20R выбора строки, являются такими же, как сигналы, которые подаются на блок 20L выбора строки.

Следует отметить, что сигналы platen_rd, platen_sh_1, platen_sh_2, platrst_sh, platen_shf, ptx_rd_1, ptx_rd_2, ptx_sh, pres_rd, pres_sh, vres_rd и vres_sh формируются блоком 40 формирования синхронизации.

Далее будет описана работа устройства 1 захвата изображения, показанного на фиг. 1 и 2, со ссылкой на временную диаграмму, показанную на фиг. 5. В дальнейшем, когда обозначения L и R специально не указываются, блоки 20L и 20R выбора строки выполняют одну и ту же операцию.

Здесь будет описан иллюстративный случай, в котором сигналы считываются из пикселей во второй строке, пятой строке, восьмой строке и так далее в пиксельной матрице 10, и пиксели, содержащиеся в трех строках, включающих в себя интересующий пиксель и пиксели до и после интересующего пикселя, то есть строки с первой по третью, строки с четвертой по шестую, строки с седьмой по девятую и так далее, и, кроме того, пиксели в строках с N-й по (N+2)-ю, строки с (N+3)-й по (N+5)-ю, строки с (N+6)-й по (N+8)-ю и так далее будут подвергнуты операции затвора. Следует отметить, что в момент времени t100, показанный на фиг. 5, SR-защелки второго и третьего блоков 23 и 24 хранения содержат низкий уровень.

Когда сигнал горизонтальной синхронизации подается на блок 40 формирования синхронизации от внешнего устройства, которое не показано, в момент времени t200, блок 40 формирования синхронизации выдает сигнал pres_rd в момент времени t201 и дополнительно выдает сигнал platen_rd в момент времени t202. Значение R1 сигнала адреса vaddr, подаваемое от блока 30 формирования адреса в момент времени t202, равно "0", и, таким образом, только выход vdec(0) среди выходов декодера 21 адреса переведен на высокий уровень. Таким образом, выход D-защелки первой схемы хранения переводится на высокий уровень. Таким образом, с использованием логического "И" вывода D-защелки и сигнала pres_rd сигнал pres(0), который должен быть подан на блок 2100 пикселей, переводится на высокий уровень.

Когда сигнал vres_rd переводится на высокий уровень в момент времени t203, сигнал vres(0), подаваемый на блок 2100 пикселей, переводится на высокий уровень посредством логического "И" сигнала vres_rd и выхода из первой схемы 2220 хранения.

В промежуток времени с момента t203 до момента t204 транзистор M2104 сброса, содержащийся в блоке 2100 пикселей, находится в проводящем состоянии. Таким образом, FD-область F2101 сбрасывается сигналом vres(0), находящимся на высоком уровне, и блок пикселей переходит в выбранное состояние, в котором выход этого блока пикселей подается на одну соответствующую линию из вертикальных сигнальных линий vline(n). При этом сигнал, имеющий уровень, соответствующий сбросу FD-области F2101, подается на вертикальную сигнальную линию vline(n), и сигнал содержит шумовой компонент, сформированный транзистором M2103 усиления, транзистором M2104 сброса и FD-областью F2101. Если блок 50 горизонтального переноса содержит схему CDS, сигналы, поданные на вертикальные сигнальные линии vline(n) до момента времени t205, подвергаются выборке.

Когда сигнал ptx_rd_2 переводится на высокий уровень в момент времени t205, сигнал ptx2(0), который должен быть подан на блок 2100 пикселей, переводится на высокий уровень посредством логического "И" сигнала ptx_rd_2 и выхода защелки первой схемы 2220R хранения, и, таким образом, транзистор M2102 переноса переводится в проводящее состояние. Посредством этого заряд, сохраненный в фотодиоде D2102, переносится в FD-область F2101, и в соответствии с этим изменяется потенциал FD-области F2101, и изменяется уровень сигнала, подаваемого на вертикальную сигнальную линию vline(n). В это время уровень сигнала изменяется на величину, соответствующую величине зарядов, сформированных посредством фотоэлектрического преобразования, относительно уровня, полученного сразу после сброса FD-области F2101. Таким образом, шумовой компонент может быть уменьшен посредством получения разности между сигналом и шумовым компонентом, сохраненным в схеме CDS. Таким образом, операция считывания сигналов из пикселей во второй строке завершается.

В момент времени t206 значение сигнала адреса vaddr, выдаваемого блоком 30 формирования адреса, изменяется с R1 на S11. Значение S11 представляет адрес пикселя, который будет сброшен (чтобы быть подвергнутым операции затвора), и значение S11 равно "0" в этот момент. Таким образом, среди выходов из декодера 21 адреса только выход vdec(0) переводится на высокий уровень.

Кроме того, сигнал platrst_sh переводится на высокий уровень в момент времени t206. Посредством этого SR-защелки второго и третьего блоков 23 и 24 хранения сбрасываются.

В момент времени t207 сигналы platen_sh_1 и platen_shf переводятся на высокий уровень. Выход SR-защелки второй схемы 2230L хранения и выход SR-защелки третьей схемы 2240 хранения переводятся высокий уровень посредством логического "И" сигнала platen_sh_1 и выхода vdec(0) и логического "И" сигнала platen_shf и выхода vdec(0), соответственно.

После этого значение сигнала адреса vaddr, выдаваемое блоком 30 формирования адреса, изменяется на S12. При этом значение S12 равно "0". Таким образом, среди выходов декодера 21 адреса только выходной сигнал vdec(0) переводится на высокий уровень.

В момент времени t208 сигналы platen_sh_2 и platen_shf переводятся на высокий уровень. Выход SR-защелки второй схемы 2230R хранения и выход SR-защелки третьей схемы 2240 хранения переводятся на высокий уровень.

После этого значение сигнала адреса vaddr, выдаваемое блоком 30 формирования адреса, изменяется на S13. При этом значение S13 равно "1". В соответствии с этим среди выходных сигналов декодера 21 адресов только сигнал vdec(1) переводится на высокий уровень.

В момент времени t209 сигналы platen_sh_1 и platen_shf переводятся на высокий уровень. Выход SR-защелки второй схемы 2231L хранения и выход SR-защелки третьей схемы 2241 хранения переводятся на высокий уровень посредством логического "И" сигнала platen_sh_1 и сигнала vdec(1) и логического "И" сигнала platen_shf и сигнала vdec(1), соответственно.

Посредством операции, выполняемой в промежуток времени с момента t206 до момента t209, вторые схемы 2230L, 2230R и 2231L хранения и третьи схемы 2240L, 2240R и 2241L хранения устанавливаются на высокий уровень.

Следует отметить, что адреса, соответствующие пикселям в третьей строке, устанавливаются с использованием значения S13, и вторая схема 2231L хранения устанавливается с использованием сигнала platen_sh_1, и одновременно третьи схемы 2241L и 2241R хранения устанавливаются с использованием сигнала platen_shf. Поскольку строки с первой по третью должны быть сброшены в этом варианте осуществления в блоке 2101 пикселей, пиксели в одной из строк (в третьей строке) сбрасываются, и пиксели в другой строке (в четвертой строке) не сбрасываются. В конфигурации, раскрытой в документе PTL 1, транзисторы сброса должны включаться для пикселей, содержащихся в третьей строке, тогда как транзисторы сброса должны включаться для пикселей, содержащихся в четвертой строке, и в соответствии с этим может быть выполнена недопустимая операция. С другой стороны, в настоящем изобретении третий блок хранения обеспечен для управления транзисторами, совместно используемыми множеством пикселей, содержащихся в блоке пикселей. Посредством этого, даже когда некоторые пиксели, содержащиеся в блоке пикселей, сброшены и другие пиксели, содержащиеся в этом же блоке пикселей, не сброшены, может быть выполнена надлежащая операция.

С момента времени t210 такая же операция выполняется над строками с N-й по (N+2)-ю, и защелки соответствующих второго и третьего блоков хранения устанавливаются. Посредством этой операции пиксели в шести строках, то есть в строках с первой по третью и в строках с N-й по (N+2)-ю, устанавливаются как пиксели, которые должны быть подвергнуты операции затвора. На фиг. 5 показан случай, в котором значение сигнала адреса vaddr изменяется на R1 после того, как сигнал адреса vaddr установлен равным значению S23. Однако значение может остаться равным S23.

Блок 40 формирования синхронизации заставляет описанную выше схему CDS выполнить операцию выборки после того, как сигнал ptx_rd_2, который был переведен на высокий уровень в момент времени t205, переводится на низкий уровень. Затем блок 40 формирования синхронизации управляет блоком 50 горизонтального переноса таким образом, что после того, как сигналы, которые были обработаны схемой CDS, были сохранены в памяти линии, с выхода выдаются сигналы, соответствующие пикселям во второй строке.

В момент времени t211 начинается операция считывания пикселей в пятой строке. Операция считывания, выполняемая над пятой строкой, является такой же, как операция считывания, выполняемая над второй строкой, которая выполняется в период времени с момента t200 до момента t211.

Поскольку пиксели в пятой строке содержатся в первой строке блока 2102 пикселей, сигнал ptx_rd_1 подается в момент времени t218 вместо сигнала ptx_rd_2. Кроме того, хотя с момента времени t219 вторые и третьи блоки хранения, соответствующие строкам с четвертой по шестую и строкам с (N+3)-й по (N+5)-ю, установлены, поскольку пиксели в четвертой строке соответствуют второй строке блока 2101 пикселей, моменты времени, когда подаются сигналы platen_sh_1 и platen_sh_2, отличаются от моментов времени при операции считывания, выполняемой над второй строкой.

Когда сигнал vres_sh переводится на высокий уровень в момент времени t214, сигналы vresi, соответствующие пикселям в строках с первой по третью и в строках с N-й по (N+2)-ю, переводятся на высокий уровень посредством соответствующих логических "И" сигнала vres_sh и выходов третьего блока 24 хранения, соответствующих строкам с первую по третью и строкам с N-й по (N+2)-ю.

Когда сигналы ptx_sh и pres_sh переводятся на высокий уровень, транзисторы сброса и транзисторы переноса пикселей в строках с первой по третью и в строках с N-й по (N+2)-ю включаются посредством логических "И" сигналов ptx_sh и pres_sh и соответствующих выходов второго блока хранения и индивидуальных выходов третьего блока хранения, соответственно. Посредством этого пиксели в строках с первой по третью и с N-й по (N+2)-ю инициализируются. После этого сигнал ptx_sh переводится на низкий уровень, и транзисторы переноса выключаются.

Хотя сигнал vres_sh переводится на низкий уровень в момент времени t216, поскольку сигнал pres_sh находится в состоянии с высоким уровнем до момента времени t217, потенциалы FD-областей пикселей в строках с первой по третью и в строках с N-й по (N+2)-ю изменяются на потенциалы, соответствующие сигналу vres_sh на низком уровне. Поскольку потенциал сигнала vres_sh на низком уровне установлен таким образом, что транзисторы усиления не включены, пиксели в строках с первой по третью и в строках с N-й по (N+2)-ю переводятся в невыбранное состояние в промежуток времени с момента t216 до момента t217. Таким образом, адреса пикселей, которые будут подвергнуты операции затвора, сохраняются посредством выполнения операции, начатой в момент времени t206, и операция затвора выполняется при операции, начатой в момент времени t215, и после этого к моменту времени t217 выполняется операция установки пикселей в невыбранное состояние.

Как описано выше, в соответствии с настоящим вариантом осуществления, поскольку адреса сохранены в третьем блоке хранения для управления совместно используемым элементом в одном и том же блоке пикселей, даже когда в одном и том же блоке пикселей некоторые пиксели сброшены, а другие пиксели не сброшены, может быть выполнена надлежащая операция.

Третий вариант осуществления

Третий вариант осуществления настоящего изобретения будет описан со ссылкой на сопроводительные чертежи. Работа этого варианта осуществления отличается от работы второго варианта осуществления. В дальнейшем будут главным образом описаны части, отличающиеся от второго варианта осуществления.

Фиг. 6 является временной диаграммой, иллюстрирующей работу устройства захвата изображения в соответствии с этим вариантом осуществления. Моменты времени, в которые выполняются те же самые операции, которые показаны на фиг. 5, обозначены так же, как на фиг. 5. Как и в случае второго варианта осуществления, будет описан иллюстративный случай, в котором сигналы считываются из пикселей во второй строке, пятой строке, восьмой строке и т.д. в пиксельной матрице 10, и операции затвора (сбросу фотодиодов) подвергаются пиксели, соответствующие трем строкам, включающим в себя интересующую строку, имеющую пиксели, в которых выполняется считывание, и строки до и после интересующей строки, то есть строки с первой по третью, строки с четвертой по шестую, строки с седьмой по девятую, а также строки с N-й по (N+2)-ю, строки с (N+3)-й по (N+5)-ю, с (N+6)-й по (N+8)-ю. В момент времени t200, показанный на фиг. 6, SR-защелки второго и третьего блоков 23 и 24 хранения поддерживают низкий уровень.

В этом варианте осуществления операция, начинающаяся с момента времени t321 после момента времени t206, отличается от второго варианта осуществления.

Во втором варианте осуществления SR-защелки второй схемы 2230L хранения и третьей схемы 2240 хранения устанавливаются в момент времени t207, и после этого SR-защелки второй схемы 2230R хранения и третьей схемы 2240 хранения устанавливаются в момент времени t208.

С другой стороны, в этом варианте осуществления сигналы platen_sh_1 и platen_sh_2 переводятся на высокий уровень в момент времени t321, посредством чего устанавливаются SR-защелки вторых схем 2230L и 2230R хранения. При работе второго варианта осуществления для того, чтобы установить адреса строк затвора с первой по третью, требуются три операции. Однако в соответствии с этим вариантом осуществления адреса трех строк затвора могут быть установлены посредством двух операций.

В соответствии с этим вариантом осуществления, поскольку адреса сохранены в третьем блоке хранения таким образом, чтобы управлять совместно используемыми элементами в одном и том же блоке пикселей, даже когда некоторые пиксели сбрасываются, а другие пиксели в том же самом блоке пикселей не сбрасываются, может быть выполнена надлежащая операция. Кроме того, в соответствии с этим вариантом осуществления, поскольку адреса строки затвора могут быть установлены в пределах более короткого промежутка времени по сравнению со вторым вариантом осуществления, может быть достигнуто быстродействие устройства захвата изображения.

Четвертый вариант осуществления

Четвертый вариант осуществления настоящего изобретения будет описан со ссылкой на сопроводительные чертежи. Фиг. 7 является подробной принципиальной схемой конфигурации, показанной на фиг. 1, за исключением блока 40 формирования синхронизации и блока 50 горизонтального переноса. В дальнейшем будут главным образом описаны части, отличающиеся от второго варианта осуществления.

В устройстве захвата изображения этого варианта осуществления пиксели в смежных четырех строках совместно используют транзистор M4103 усиления и транзистор M4104 сброса и составляют единый блок пикселей, что отличается от устройства захвата изображения, показанного на фиг. 4. Кроме того, в этом варианте осуществления первый основной электрод транзистора M4103 усиления и первый основной электрод транзистора M4104 сброса соединены друг с другом и принимают напряжение питания vcc.

Кроме того, конфигурация декодера адреса отличается от декодера 21 адреса устройства захвата изображения, показанного на фиг. 4. Декодер 21L адреса этого варианта осуществления принимает сигнал адреса vaddr, выдаваемый из блока 30 формирования адреса в соответствии с управляющим сигналом, выдаваемым из блока 40 формирования синхронизации. Сигнал адреса vaddr является, например, n-битовым сигналом, представляет блок пикселей с использованием старших n-1 битов и представляет пиксели, содержащиеся в блоке пикселей, с использованием n битов. На фиг. 7 значение vdecu(x) устанавливается с использованием старших n-1 битов (0≤×≤(2^(n-1))-1), и значение vdec(y) устанавливается с использованием n битов (0≤y≤(2^n)-1), Следует отметить, что когда блок пикселей включает в себя два пикселя, блок пикселей представлен посредством m битов сигнала адреса, имеющего m битов.

Кроме того, устройство захвата изображения этого варианта осуществления отличается от устройства захвата изображения второго варианта осуществления тем, что первый блок 22L хранения имеет селекторы, которые выбирают сигналы, подаваемые на D-входы D-защелок, так что заряды, сохраненные во множестве фотодиодов, содержащихся в одном и том же блоке пикселей, могут быть добавлены друг к другу.

Первый блок 22L хранения содержит первые схемы 4220L, 4222L и т.д. хранения, которые не содержат селекторы, и первые схемы 4221AL, 4223AL и т.д. хранения, которые содержат селекторы. D-защелка, содержащаяся в первой схеме 4220L хранения, имеет D-вход, соединенный с выходом vdec(0) декодера 21L адреса, и G-вход, соединенный с линией, используемой для передачи сигнала platen_rd. С другой стороны, D-защелка, содержащаяся в первой схеме 4221AL хранения, имеет D-вход, соединенный с выходом селектора 41SEL, и G-вход, соединенный с линией, используемой для передачи сигнала platen_rd. Селектор 41SEL соединен с выходом vdec(0) и выходом vdec(1) из выходов декодера 4210L адреса и передает выходную информацию с выхода vdec(0) или vdec(1) D-защелке с использованием сигнала fdadd. Селектор 41SEL выдает сигнал vdec(0), когда сигнал fdadd находится на высоком уровне, тогда как селектор 41SEL выдает сигнал vdec(1), когда сигнал fdadd находится на низком уровне. Первые схемы 4222L, 4223AL и т.д. хранения сконфигурированы аналогичным образом. Следует отметить, что линия, используемая для передачи сигнала platen_rd, соединена вместе с другими схемами 4222L, 4223AL и т.д. хранения, содержащимися в первом блоке 22L хранения. Кроме того, линия, используемая для передачи сигнала fdadd, также соединена с другими схемами 4223AL и т.д. хранения, содержащимися в первом блоке 22L хранения.

Хотя в качестве примера описан случай, в котором каждая из схем 4250L, 4251L и т.д. формирования импульса пикселя, содержащихся в блоке 25L формирования импульса пикселя, имеет логические схемы "И" и схемы "ИЛИ", конфигурации схем не ограничены конфигурацией этого варианта осуществления. Схема 4250L формирования импульса пикселя выдает сигналы presi, ptx1i и ptx2i, которые подаются в качестве сигналов pres(0), ptx1(0) и ptx3(0) на блок 4100 пикселей. Сигнал presi формируется как логическое "ИЛИ" логического "И" выхода схемы "ИЛИ", которая выдает логическое "ИЛИ" первых схем 4220L и 4221L хранения и сигнала pres_rd, и логического "И" выхода третьей схемы 4240L хранения и сигнала pres_sh. Сигнал ptx1i формируется как логическое "ИЛИ" логического "И" выхода первой схемы 4220L хранения и сигнала ptx_rd_1 и логического "И" выхода второй схемы 4230L хранения и сигнала ptx_sh. Сигнал ptx2i формируется как логическое "ИЛИ" логического "И" выхода первой схемы 4221L хранения и сигнала ptx_rd_1 и логического "И" выхода второй схемы 4231L хранения и сигнала ptx_sh.

Будут описаны части блока 20R выбора строки, которые отличаются от частей блока 20L выбора строки. Поскольку блок 20R выбора строки управляет пикселями в строках с четными номерами в пиксельной матрице 10, сигналы, выдаваемые из блока 25R формирования импульса пикселя, подаются на пиксели в строках с четными номерами, что отличается от блока 20L выбора строки. Таким образом, второй блок 23R хранения принимает сигнал platen_sh_2 вместо сигнала platen_sh_1, подаваемого на второй блок 23L хранения. Аналогичным образом, блок 25R формирования импульса пикселя принимает сигнал ptx_rd_2 вместо сигнала ptx_rd_1, подаваемого на блок 25L формирования импульса пикселя. Другие сигналы, подаваемые на блок 20R выбора строки, являются такими же, как подаваемые на блок 20L выбора строки.

Следует отметить, что сигналами platen_rd, platen_sh_1, platen_sh_2, platrst_sh, platen_shf, fdadd, ptx_rd_1, ptx_rd_2, ptx_sh, pres_rd, pres_sh и vcc управляет блок 40 формирования синхронизации.

Далее будет описана работа устройства захвата изображения, показанного на фиг. 1 и 7, со ссылкой на временную диаграмму, показанную на фиг. 8. В дальнейшем, когда обозначения L и R специально не указываются, блоки 20L и 20R выбора строки выполняют одну и ту же операцию.

Здесь будет описан иллюстративный случай, в котором сигналы пикселей в первой и третьей строках, во второй и четвертой строках и так далее добавляются друг к другу, и считываются результирующие сигналы, и, в дополнение к пикселям в первой и третьей строках, второй и четвертой строках и так далее, пиксели в N-й и (N+2)-й строках, в (N+1)-й и (N+3)-й строках и так далее подвергаются операции затвора (сбросу фотодиодов). В течение описанного ниже периода сигнал fdadd находится на высоком уровне, селекторы 41SEL, 43SEL и т.д. выдают сигналы vdec(0), vdec (2) и т.д., соответственно. Предполагается, что на фиг. 8 в момент времени t300 SR-защелки второго и третьего блоков 23 и 24 хранения поддерживают низкий уровень.

Сначала, когда в момент времени t400 сигнал горизонтальной синхронизации подается на блок 40 формирования синхронизации от внешнего устройства, которое не показано, блок 40 формирования синхронизации выдает сигналы ptx_sh и pres_sh в момент времени t401. Однако, поскольку SR-защелки второго и третьего блоков хранения поддерживают низкий уровень, сигналы presi, ptx1i и ptx2i, выдаваемые из блока 25 формирования импульса пикселя, находятся на низком уровне.

В момент времени t402 сигнал vcc переводится на низкий уровень, но операция изменения состояния на невыбранное состояние не выполняется ни на одном блоке пикселей, поскольку сигнал presi находится на низком уровне.

Сигнал pres_rd переводится на высокий уровень в момент времени t403, и сигнал platen_rd переводится на высокий уровень в момент времени t404. Поскольку значение R1 равно "0", среди выходов декодера 21L адресов только выходы vdecu(0) и vdec(0) переводятся на высокий уровень. При этом, поскольку сигнал fdadd находится на высоком уровне, селектор 41SEL выдает сигнал vdec(0). В соответствии с этим, когда сигнал platen_rd переводится на высокий уровень в момент времени t404, выходы D-защелок первых схем 4220L и 4221AL хранения переводятся на высокий уровень. Поскольку сигнал pres_rd находится на высоком уровне, сигнал pres(0) переводится на высокий уровень посредством логического "И" сигнала pres_rd и выхода первой схемы 4220L хранения. Посредством этого транзистор M4104 сброса блока 4100 пикселей переводится в проводящее состояние. В этом состоянии, когда напряжение питания vcc переводится на высокий уровень, FD-область F4101 сбрасывается посредством напряжения питания vcc, и блок пикселей переходит в выбранное состояние, в котором сигнал, выдаваемый из блока пикселей, подается на одну соответствующую линию из вертикальных сигнальных линий vline(n). Сигнал, подаваемый на вертикальную сигнальную линию vline(n), имеет уровень, соответствующий сбросу FD-области F4101, и сигнал содержит шумовой компонент, сформированный транзистором M4103 усиления, транзистором M4104 сброса и FD-областью F4101. В конфигурации, содержащей блок 50 горизонтального переноса, имеющий схему CDS, сигнал, подаваемый на вертикальную сигнальную линию vline(n), подвергается выборке до момента времени t405.

Когда сигнал ptx_rd_1 переводится на высокий уровень в момент времени t405, сигнал ptx1(0) переводится на высокий уровень посредством логического "И" сигнала ptx_rd_1 и выхода первой схемы 4220L хранения, и, кроме того, сигнал ptx3(0) переводится на высокий уровень посредством логического "И" сигнала ptx_rd_1 и выхода первой схемы 4221AL хранения. Посредством этого транзисторы M4101-1 и M4101-3 переноса переводятся в проводящее состояние, и заряды, сохраненные в фотодиодах D4101 и D4103, переносятся в FD-область F4101. Потенциал FD-области F4101 изменяется вследствие перенесенных в нее зарядов, и в соответствии с этим изменяется уровень сигнала, подаваемого на вертикальную сигнальную линию vline(n). Сигнал изменяется на величину, соответствующую величине заряда, сформированного посредством фотоэлектрического преобразования, относительно уровня, полученного после сброса FD-области F4101. Таким образом, шумовой компонент может быть уменьшен посредством получения разности между сигналом и шумовым компонентом, сохраненным в схеме CDS. Таким образом, операция считывания сигналов из пикселей в первой и третьей строках завершается.

В момент времени t406 значение сигнала адреса vaddr, выдаваемого из блока 30 формирования адреса, изменяется с R1 на S11. Значение S11 представляет адрес пикселя, который должен быть сброшен (чтобы быть подвергнутым операции затвора), и равно "0" в этот момент. В соответствии с этим среди выходов декодера 21 адресов только сигналы vdecu(0) и vdec(0) переводятся на высокий уровень.

Кроме того, в момент времени t406 сигнал platrst_sh переводится на высокий уровень. Посредством этого сбрасываются SR-защелки второго и третьего блоков хранения.

В момент времени t407 сигналы platen_sh_1 и platen_shf переводятся на высокий уровень, и, таким образом, выходы SR-защелок второй схемы 4230L хранения и третьих схем 4240L и 4240R хранения переводятся на высокий уровень.

После этого значение сигнала адреса vaddr изменяется с S11 на S12. При этом значение S12 равно "1", и среди выходов декодера 21 адресов только сигналы vdecu(0) и vdec(1) переводятся на высокий уровень.

В момент времени t408 сигналы platen_sh_1 и platen_shf переводятся на высокий уровень, и, таким образом, SR-защелки второй схемы 4231L хранения и третьих схем 4240L и 4240R хранения переводятся на высокий уровень.

Посредством операции, выполняемой с момента времени t406 до момента времени t408, вторые схемы 4230L и 4231L хранения и третьи схемы 4240L и 4240R хранения, соответствующие первой и третьей строкам, переводятся на высокий уровень.

Следует отметить, что адреса, соответствующие пикселям в третьей строке, устанавливаются с использованием значения S12, и вторая схема 4231L хранения устанавливается с использованием сигнала platen_sh_l, и одновременно третьи схемы 4240L и 4240R хранения устанавливаются с использованием сигнала platen_shf. Поскольку первая и третья строки в блоке 4100 пикселей должны быть сброшены в этом варианте осуществления, пиксели в первой и третьей строках сбрасываются, и пиксели во второй и четвертой строках не сбрасываются. В конфигурации, раскрытой в документе PTL 1, транзисторы сброса должны быть включенными для пикселей, содержащихся в первой и третьей строках, тогда как транзисторы сброса должны быть выключенными для пикселей, содержащихся во второй и четвертой строках, и в соответствии с этим может быть выполнена недопустимая операция. С другой стороны, в настоящем изобретении третий блок хранения обеспечен для управления транзисторами, совместно используемыми множеством пикселей, содержащихся в блоке пикселей. Посредством этого, даже когда некоторые пиксели, содержащиеся в блоке пикселей, сбрасываются, а другие пиксели, содержащиеся в блоке пикселей, не сбрасываются, может быть выполнена надлежащая операция.

Операция, выполняемая с момента времени t407, также выполняется над строками с N-й по (N+2)-ю с момента времени t409 таким образом, чтобы были установлены соответствующие защелки вторых и третьих блоков хранения. Посредством описанной выше операции пиксели во всех четырех строках, то есть в первой и третьей строках и в N-й и (N+2)-й строках, устанавливаются как пиксели, которые должны подвергаться операции затвора. При этом, поскольку пиксели в N-й строке расположены в строке с четным номером блока пикселя, сигнал platen_sh_2 подается вместо сигнала platen_sh_1. Хотя фиг. 8 показывает случай, в котором значение сигнала адреса vaddr, которое было установлено равным S22, изменяется на R1, значение может остаться равным S22.

Блок 40 формирования синхронизации заставляет описанную выше схему CDS выполнить операцию выборки после того, как сигнал ptx_rd_1, который был переведен на высокий уровень в момент времени t405, переводится на низкий уровень. Затем блок 40 формирования синхронизации управляет блоком 50 горизонтального переноса таким образом, что после того, как сигналы, обработанные схемой CDS, были сохранены в памяти линии, блок 50 горизонтального переноса выдает сигнал, полученный посредством сложения друг с другом выдаваемых с выхода сигналов, соответствующих пикселям в первой и третьей строках.

В момент времени t411 начинается операция считывания пикселей во второй и четвертой строках. Операция считывания, выполняемая над второй и четвертой строками, является такой же, как операция считывания, выполняемая над первой и третьей строками, которая выполняется с момента времени t400 до момента времени t411.

Поскольку пиксели во второй и четвертой строках расположены во второй и четвертой строках блока 4100 пикселей, сигнал ptx_rd_2 подается в момент времени 416 вместо сигнала ptx_rd_1.

Кроме того, хотя второй и третий блоки хранения, соответствующие второй и четвертой строкам и (N+1)-й и (N+3)-й строкам, установлены с момента времени t417, поскольку пиксели во второй и четвертой строках расположены во второй и четвертой строках блока 4100 пикселей, моменты времени, когда подаются сигналы platen_sh_1 и platen_sh_2, отличаются от моментов времени при операции считывания, выполняемой над второй строкой. Здесь предполагается, что пиксели в (N+1)-й и (N+3)-й строках соответствуют пикселям в строках с нечетными номерами блока пикселей.

Когда сигналы ptx_sh и pres_sh переводятся на высокий уровень в момент времени t412, транзисторы сброса и транзисторы переноса пикселей в первой и третьей строках и в N-й и (N+2)-й строках включаются посредством логического "И" сигналов ptx_sh и pres_sh и выхода второго блока хранения или третьего блока хранения. Посредством этого пиксели в первой и третьей строках и N-й и (N+2)-й строках сбрасываются.

Как описано выше, в соответствии с этим вариантом осуществления, поскольку адреса сохранены в третьем блоке хранения для управления элементами, которые совместно используются в одном и том же блоке пикселей, даже когда некоторые пиксели в блоке пикселей должны быть сброшены, а другие пиксели в этом же блоке пикселей не должны быть сброшены, может быть выполнена надлежащая операция. Кроме того, в соответствии с этим вариантом осуществления, поскольку в первом блоке хранения содержатся селекторы, заряды пикселей, содержащихся в одном и том же блоке пикселей, могут быть добавлены друг к другу в FD-области.

В настоящем и предыдущих вариантах осуществления блоки 20L и 20R выбора пикселей расположены на противоположных сторонах со вставленной между ними пиксельной матрицей 10 для простоты чертежей. Однако блоки 20L и 20R выбора строки могут быть расположены на одной стороне пиксельной матрицы 10.

Пятый вариант осуществления

Пятый вариант осуществления настоящего изобретения будет описан со ссылкой на сопроводительные чертежи. Фиг. 9 является подробной принципиальной схемой конфигурации, показанной на фиг. 1, за исключением блока 40 формирования синхронизации и блока 50 горизонтального переноса. В дальнейшем главным образом описаны части, отличающиеся от второго варианта осуществления.

В устройстве захвата изображения этого варианта осуществления пиксели в смежных двух строках совместно используют транзистор M5103 усиления и транзистор M5104 сброса и составляют блок пикселей, который имеет такую же конфигурацию, как конфигурация, показанная на фиг. 4.

Этот вариант осуществления отличается от второго варианта осуществления тем, что для пиксельной матрицы обеспечен только один блок 20 выбора строки.

Кроме того, блок 20 выбора строки содержит декодер 21 адреса, первый блок 22 хранения, второй блок 23 хранения, третий блок 24 хранения и блок 25 формирования импульса пикселя. Декодер 21 адреса декодирует значение адреса, сформированное блоком 30 формирования адреса, и выбирает адрес, соответствующий значению адреса.

Первый блок 22 хранения хранит результат декодирования, выполненного декодером 21 адреса. Сигнал, выданный из первого блока 22 хранения, используется в качестве адреса строки, содержащейся в пиксельной матрице 10, которая содержит пиксели, из которых должны быть считаны сигналы.

Второй блок 23 хранения хранит результат декодирования, выполненного декодером 21 адреса. Сигнал, выданный из второго блока 23 хранения, используется в качестве адреса строки, содержащейся в пиксельной матрице 10, которая содержит пиксели, имеющие блоки фотоэлектрического преобразования, которые должны быть сброшены.

Третий блок 24 хранения хранит результат декодирования, выполненного декодером 21 адресов. Сигнал, выданный из третьего блока 24 хранения, используется в качестве адреса блока пикселей, содержащего FD-область пикселя, который выполняет операцию снятия выбора в пиксельной матрице 10.

Блок 30 формирования адреса формирует значение адреса в соответствии с сигналом, выдаваемым из блока 40 формирования синхронизации, и подает значение адреса на блок 20 выбора строки.

Блок 40 формирования синхронизации выдает сигнал, используемый для управления синхронизацией, когда блок 30 формирования адреса формирует значение адреса, и выдает сигнал, используемый для управления синхронизацией, когда работают блок 20 выбора строки и блок 50 горизонтального переноса.

Блок 50 горизонтального переноса используется для выдачи сигнала, считанного из пиксельной матрицы 10 через одну соответствующую линию из вертикальных сигнальных линий vline(n) с выхода. В частности, блок 50 горизонтального переноса содержит усилители, аналого-цифровые преобразователи, схемы CDS, схемы выборки и хранения и т.п., которые обеспечены для отдельных вертикальных сигнальных линий vline(n), и последовательно выдает сигналы на выход с использованием схемы горизонтального сканирования.

Декодер 21 адреса принимает сигнал адреса vaddr, который выдан из блока 30 формирования адреса в соответствии с управляющим сигналом, выданным из блока 40 формирования синхронизации. Сигнал адреса vaddr представляет собой n-битовый сигнал, представляющий блок пикселей с использованием старших n-1 битов и представляющий пиксели в блоке пикселей с использованием младших n битов. На фиг. 9 значение vdecu(x) устанавливается с использованием старших n-1 битов, и значение vdec(y) устанавливается с использованием младших n битов. Следует отметить, что когда блок пикселей содержит два пикселя, блок пикселей представлен посредством m битов сигнала адреса из m битов.

Каждая из множества первых схем 5220, 5221 и т.д. хранения, содержащихся в первом блоке 22 хранения, содержит D-защелку, которая хранит однобитовые данные. D-защелка, содержащаяся в первой схеме 5220 хранения, имеет D-вход, соединенный с выходом vdec(0) декодера 21 адресов, и G-вход, соединенный с линией, используемой для подачи сигнала platen_rd. Хотя первые схемы 5221, 5222 и т.д. хранения также содержат соответствующие D-защелки аналогично схеме 5220 хранения, D-входы соединены с другими выходами декодера 21 адреса. Линия, используемая для передачи сигнала platen_rd, соединена совместно с другими схемами 5221, 5222 и т.д. хранения, содержащимися в первом блоке хранения.

Каждая из вторых схем 5230, 5231 и т.д. хранения, содержащихся во втором блоке 23 хранения, имеет логическую схему "И" и SR-защелку, имеющую S-вход, соединенный с выходом логической схемы "И". Первый вход логической схемы "И" соединен с выходом vdec(0) декодера 21L адресов, и второй вход логической схемы "И" соединен с линией, используемой для передачи сигнала platen_sh. R-вход SR-защелки соединен с линией, используемой для передачи сигнала platrst. Линия, используемая для передачи сигнала platrst, также соединена совместно с другими вторыми схемами 5231, 5232 и т.д. хранения, содержащимися во втором блоке хранения.

Каждая из третьих схем 5240, 5241 и т.д. хранения, содержащихся в третьем блоке 24 хранения, содержит логическую схему "И" и SR-защелку, имеющую S-вход, соединенный с выходом логической схемы "И". Первый вход логической схемы "И" соединен с выходом vdecu(0) декодера 21 адресов, и второй вход логической схемы "И" соединен с линией, используемой для передачи сигнала platen_rdf. R-вход SR-защелки соединен с линией, используемой для передачи сигнала platrst. Линии, используемые для передачи сигнала platen_rd и platrst, также соединены совместно с другими третьими схемами 5241, 5242 и т.д. хранения, содержащимися в третьем блоке хранения.

Хотя в качестве примера показан случай, в котором каждая из схем 5250, 5251 и т.д. формирования импульса пикселя, содержащихся в блоке 25 формирования импульса пикселя, содержит логические схемы "И" и логические схемы "ИЛИ", конфигурации схем не ограничены конфигурацией этого примера. Схема 5250 формирования импульса пикселя выдает сигналы vresi, presi, ptx1i, и ptx2i, которые подаются как сигналы vres(0), pres(0), ptx1(0) и ptx2(0), соответственно, на блок 5100 пикселей. Сигнал vresi формируется как логическое "ИЛИ" логического "И" логического "ИЛИ" первых схем 5220 и 5221 хранения и сигнала vres_rd и логического "И" логического "ИЛИ" вторых схем 5230 и 5231 хранения и сигнала vres_sh. Сигнал presi формируется как логическое "ИЛИ" логического "И" логического "ИЛИ" выхода схемы "ИЛИ", которая выдает логическое "ИЛИ" первых схем 5220 и 5221 хранения и выхода третьей схемы 5240 хранения и сигнала pres_rd и логического "И" выхода схемы "ИЛИ", которая выдает логическое "ИЛИ" вторых схем 5230 и 5231 хранения и сигнала pres_sh. Затем сигнал ptx1i формируется как логическое "ИЛИ" логического "И" выхода первой схемы 5220 хранения и сигнала ptx_rd и логического "И" выхода второй схемы 5230 хранения и сигнала ptx_sh. Сигнал ptx2i формируется как логическое "ИЛИ" логического "И" первой схемы 5221 хранения и сигнала ptx_rd и логического "И" выхода второй схемы 5221 хранения и сигнала ptx_sh.

Следует отметить, что сигналы vres_rd, vres_sh, platen_rd, platen_sh, platrst, platen_rdf, ptx_rd, ptx_sh, pres_rd и pres_sh формируются блоком 40 формирования синхронизации.

Далее со ссылкой на временную диаграмму, показанную на фиг. 10, будет описана работа устройства захвата изображения, показанного на фиг. 9.

Здесь будет описан иллюстративный случай, в котором сигналы считываются из пикселей в первой строке, четвертой строке, седьмой строке и так далее в пиксельной матрице 10, и операция затвора (сброс фотодиодов) выполняется над пикселями в строках с шестой по восьмую, в то время как операция считывания выполняется над четвертой строкой, операция затвора выполняется над пикселями в строках с одиннадцатой к тринадцатую, в то время как операция считывания выполняется над седьмой строкой, и аналогичным образом операция затвора выполняется над следующими пикселями. На фиг. 10 в момент времени t500 SR-защелки второго и третьего блоков 23 и 24 хранения поддерживают низкий уровень.

Сначала, когда сигнал горизонтальной синхронизации подается на блок 40 формирования синхронизации от внешнего устройства, которое не показано, в момент времени t500, блок 40 формирования синхронизации переводит сигнал platen_rd на высокий уровень в момент времени t501. Поскольку значение R1 сигнала адреса vaddr, выдаваемого из блока 30 формирования адреса во время, когда сигнал platen_rd переведен на низкий уровень, равно "0", только выходы vdecu(0) и vdec(0) среди выходов декодера 21 адреса переводятся на высокий уровень. Таким образом, выход D-защелки первой схемы 5220 хранения переводится на высокий уровень.

Поскольку сигнал vres_rd переведен на высокий уровень в момент времени t501, сигнал vres(0) переводится на высокий уровень посредством логического "И" сигнала vres_rd и выхода первой схемы 5240 хранения.

Кроме того, хотя сигнал vres_sh переведен на высокий уровень в момент времени t501, сигналы vres(n), иные, чем сигнал vres(0), остаются на низком уровне, поскольку SR-защелки второго блока 23 хранения выдают сигналы в низком уровне.

После этого, когда сигнал pres_rd переведен на высокий уровень, сигнал pres(0) переводится на высокий уровень посредством логического "И" сигнала pres_rd и выхода первой схемы 5220 хранения. Посредством этого транзистор M5104 сброса переводится в проводящее состояние, и FD-область сбрасывается в соответствии с сигналом vres(0), который находится на высоком уровне. При этом сигнал, имеющий уровень, соответствующий сбросу FD-области F5101, подается на одну соответствующую линию из вертикальных сигнальных линий vline(n). Сигнал содержит шумовой компонент, сформированный транзистором M5103 усиления, транзистором M5104 сброса и FD-областью 5101. Когда блок 50 горизонтального переноса содержит схему CDS, сигналы, подаваемые на вертикальные сигнальные линии vline(n) к моменту времени t505, подвергаются выборке.

Кроме того, хотя сигналы ptx_sh и pres_sh переводятся на высокий уровень наряду с сигналом pres_rd, сигналы pres(n), иные чем сигнал pres(0) SR-защелок второго и третьего блоков и все сигналы ptx1(n) и ptx2(n) остаются на низком уровне.

Когда сигнал platrst переводится на высокий уровень в момент времени t502, SR-защелки второго и третьего блоков хранения сбрасываются.

Когда сигнал platen_rdf переводится на высокий уровень в момент времени t503, SR-защелка третьей схемы 5240 хранения устанавливается на высокий уровень посредством логического "И" сигнала platen_rdf и сигнала vdecu(0).

Когда сигнал ptx_rd переводится на высокий уровень в момент времени t504, сигнал ptx1(0) переводится на высокий уровень посредством логического "И" сигнала ptx_rd и выхода первой схемы 5220 хранения. Посредством этого транзистор M5101 переноса переводится в проводящее состояние, и заряд, сохраненный в фотодиоде D5101, подается в FD-область F5101. В соответствии с этим изменяется потенциал FD-области F5101, и изменяется уровень сигнала, подаваемого на одну соответствующую линию из вертикальных сигнальных линий vline(n). Поскольку сигнал изменяется на величину, соответствующую количеству заряда, сформированного посредством фотоэлектрического преобразования, относительно уровня, полученного сразу после сброса FD-области F5101, шумовой компонент может быть уменьшен посредством получения разности между сигналом и шумовым компонентом, сохраненным в схеме CDS. Таким образом, операция считывания сигналов из пикселей в первой строке завершается.

В момент времени t505 значение сигнала адреса vaddr, выдаваемого из блока 30 формирования адреса, изменяется с R1 на S11. Значение S11 представляет адрес пикселя, который должен быть сброшен (чтобы быть подвергнутым операции затвора) в следующем периоде горизонтальной синхронизации, и значение S11 равно "5" в этом варианте осуществления. Таким образом, среди выходов декодера 21 адресов только сигналы vdecu(2) и vdec(5) переводятся на высокий уровень, и схемы хранения с первой по третью, соответствующие пикселям в шестой строке, выполняют операции.

В момент времени t506 сигнал platen_sh переводится на высокий уровень, и, таким образом, только SR-защелка второй схемы 5235 хранения (не показана) устанавливается на высокий уровень.

С момента времени t507 сигнал адреса vaddr изменяется таким образом, что он соответствует пикселям в седьмой строке, пикселям в восьмой строке и пикселям в строках с N-й по (N+2)-ю, и вторая схема хранения устанавливается на высокий уровень в соответствии с синхронизацией сигнала platen_sh.