Предлагаемое изобретение относится к вычислительной технике, в частности к контрольным устройствам, и может быть использовано в научных исследованиях и технике, где необходимо определять время наступления постепенного отказа, оптимальный период технического обслуживания и очередной период регламентированного технического обслуживания изделия, для заданного коэффициента готовности, осуществляя гибкую стратегию технического обслуживания.

Известно устройство для определения оптимального периода технического обслуживания изделия, содержащее пять сумматоров, блок умножения, блок нелинейности, четыре элемента памяти, интегратор, два таймера, блок деления, три элемента задержки, два триггера, элемент ИЛИ, два компаратора, три ключа, при этом первый вход первого сумматора является первым входом устройства, первый вход блока умножения является вторым входом устройства, первый вход первого элемента памяти является третьим входом устройства, первый вход элемента ИЛИ является четвертым входом устройства, второй вход первого сумматора подключен к выходу блока умножения, второй вход которого соединен с первым входом интегратора и выходом блока нелинейности, первый вход которого подключен к выходу первого элемента памяти, второй вход которого подключен к выходу первого триггера, первому входу второго триггера, входу таймера, второму входу блока нелинейности, второму входу интегратора, выход которого соединен со вторым входом второго сумматора, первый вход которого подключен к первому входу четвертого сумматора, выходу таймера, входу третьего элемента задержки, выход второго сумматора соединен с первым входом третьего сумматора, второй вход которого подключен к выходу первого и второму входу четвертого сумматора, выход третьего сумматора подключен ко второму входу блока деления, первый вход которого соединен с выходом четвертого сумматора и входом второго элемента задержки, выход которого соединен с входом второго элемента памяти, управляющий вход которого подключен к выходу второго триггера, управляющим входам третьего, четвертого элементов памяти, первого, второго, третьего ключей, входу второго таймера, второму входу второго триггера, первый вход второго триггера соединен с выходом первого компаратора, вход которого соединен с входом четвертого элемента памяти и выходом первого элемента задержки, вход которого подключен к выходу блока деления, выход четвертого элемента памяти соединен с входом второго ключа, выход которого является первым выходом устройства, выход второго элемента памяти соединен со входом первого ключа, выход которого соединен со вторым входом второго компаратора, первый вход которого подключен к выходу пятого сумматора, первый вход которого подключен к выходу второго таймера, выход третьего элемента задержки подключен к входу третьего элемента памяти, выход которого подключен к входу третьего ключа, выход которого подключен к второму входу пятого сумматора и является вторым выходом устройства, выход второго компаратора соединен со вторым входом элемента ИЛИ, выход которого подключен к второму входу первого триггера /патент РФ №2206123, МПК G07C 3/08, 2003/.

Устройство позволяет определить период технического обслуживания изделия с учетом интенсивности постепенных отказов, но не учитывает внезапные отказы, возникающие при работе изделия под током и в выключенном состоянии. Таким образом, устройство имеет ограниченную область применения.

Известно также устройство для определения оптимального периода технического обслуживания изделия, содержащее блок памяти, два блока деления, блок нелинейности, два блока умножения, вычитатель, четыре элемента задержки, таймер, три сумматора, два компаратора, мультивибратор, элемент ИЛИ, три элемента памяти, три ключа, причем первый выход блока памяти соединен с первым входом второго блока деления, второй вход которого подключен к выходу второго блока умножения, первый и второй входы которого объединены и подключены к входу первого элемента задержки, входу таймера, первому входу интегратора, первому входу вычитателя, выход второго блока деления соединен с входом блока нелинейности, выход которого подключен к второму входу интегратора и второму входу первого блока умножения, первый вход которого подключен к второму выходу блока памяти, выход интегратора подключен к второму входу вычитателя и второму входу третьего сумматора, первый вход которого подключен к выходу второго сумматора, первому входу первого блока деления, входу четвертого блока задержки, второй вход второго сумматора соединен с выходом вычитателя, первый вход второго сумматора подключен к выходу первого сумматора и первому входу первого компаратора, второй вход которого подключен к четвертому выходу блока памяти, первый и второй входы первого сумматора подключены к третьему выходу блока памяти и выходу первого блока умножения соответственно, второй вход первого компаратора подключен к четвертому входу блока памяти, первый вход первого блока умножения подключен к второму выходу блока памяти, первый вход таймера соединен с управляющими входами первого, второго, третьего элементов памяти, первого, второго, третьего ключей, вторым входом триггера, выходом мультивибратора, второй вход таймера соединен с выходом второго элемента задержки, вход которого подключен к первому входу триггера, вход которого соединен с пятым входом блока памяти, выход третьего сумматора подключен ко второму входу первого блока деления, выход которого подключен к входу третьего элемента задержки и второму входу второго компаратора, выход которого соединен с вторым входом элемента ИЛИ, выход которого подключен к входу мультивибратора, первый вход второго компаратора соединен с выходом третьего элемента задержки и входом второго элемента памяти, выход которого подключен к входу второго ключа, выход которого является вторым выходом устройства, выход вычитателя подключен к входу четвертого элемента задержки, выход которого соединен с входом третьего элемента памяти, выход которого подключен к входу третьего ключа, выход которого является третьим выходом устройства, выход первого элемента задержки соединен с входом первого элемента памяти, выход которого подключен к входу первого ключа, выход которого является первым выходом устройства /патент РФ №2347272, МПК G07C 3/08, 2009/.

Устройство позволяет определить период технического обслуживания изделия с учетом интенсивности постепенных отказов (интенсивность распределена по закону Релея, который не всегда приемлем) и не учитывает внезапные отказы, возникающие при работе изделия под током и в выключенном состоянии.

Наиболее близким по технической сущности к предлагаемому техническому решению является устройство для определения оптимального периода технического обслуживания изделия, содержащее блок памяти, таймер, четыре вычитателя, четыре блока деления, два блока определения абсолютного значения, два сумматора, компаратор, ключ, элемент памяти, три умножителя, блок извлечения квадратного корня, при этом первый выход блока памяти подключен к входу таймера, первый вход первого вычитателя подключен к третьему выходу блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выхода блока памяти, первый вход второго вычитателя подключен к четвертому выходу блока памяти, первый и второй входы блока первого блока деления подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения подключены к первым входам второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления подключен к пятому выходу блоку памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входам третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления подключен к второму входу компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого умножителя подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к первому входу третьего блока умножения, на первый вход которого поступает сигнал с выхода элемента памяти, выход третьего блока умножения подключен к входу блока извлечения квадратного корня, выход которого является вторым выходом устройства /патент РФ №111327, МПК G07C 3/00, 2011/.

Устройство позволяет определить время наступления постепенного отказа и с учетом этого оптимальный период технического обслуживания, но не определяет очередной период регламентированного технического обслуживания с учетом заданного коэффициента готовности изделия.

Задачей, на решение которой направлено заявляемое изобретение, является расширение области применения устройства за счет определения очередного периода регламентированного технического обслуживания изделия с учетом заданного коэффициента готовности изделия.

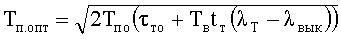

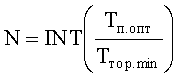

Для достижения указанного технического результата в известное устройство, содержащее блок памяти, таймер, четыре вычитателя, четыре блока деления, два блока определения абсолютного значения, два сумматора, компаратор, ключ, элемент памяти, три умножителя, блок извлечения квадратного корня, при этом первый выход блока памяти подключен к входу таймера, первый вход первого вычитателя подключен к третьему выходу блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выхода блока памяти, первый вход второго вычитателя подключен к четвертому выходу блока памяти, первый и второй входы блока первого блока деления подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения подключены к первым входам второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления подключен к пятому выходу блоку памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входам третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления подключен к второму входу компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого умножителя подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к первому входу третьего блока умножения, на первый вход которого поступает сигнал с выхода элемента памяти, выход третьего блока умножения подключен к входу блока извлечения квадратного корня, выход которого является вторым выходом устройства, согласно изобретению дополнительно введены пятый и шестой блоки деления, блок выделения целой части, вычитающий счетчик, четвертый блок умножения, третий сумматор, второй элемент памяти, второй ключ и второй компаратор, причем тринадцатый выход блока памяти подключен к первым входам пятого блока деления и четвертого блока умножения, второй вход пятого блока деления соединен с выходом блока извлечения квадратного корня, восьмой выход блока памяти связан с первым входом третьего сумматора, второй вход которого подключен к выходу четвертого блока умножения и входу второго элемента памяти, выход пятого блока деления через блок выделения целой части подключен к первому входу вычитающего счетчика, выход которого соединен со вторым входом четвертого блока умножения, выход третьего сумматора связан с первым входом шестого блока деления, второй вход которого подключен к выходу первого элемента памяти, четырнадцатый выход блока памяти соединен с вторым входом второго компаратора, первый вход которого связан с выходом шестого блока деления, первый выход второго компаратора соединен с вторым входом вычитающего счетчика, второй выход второго компаратора подключен ко второму входу второго ключа, первый вход которого соединен с выходом второго элемента памяти, выход второго ключа является третьим выходом устройства.

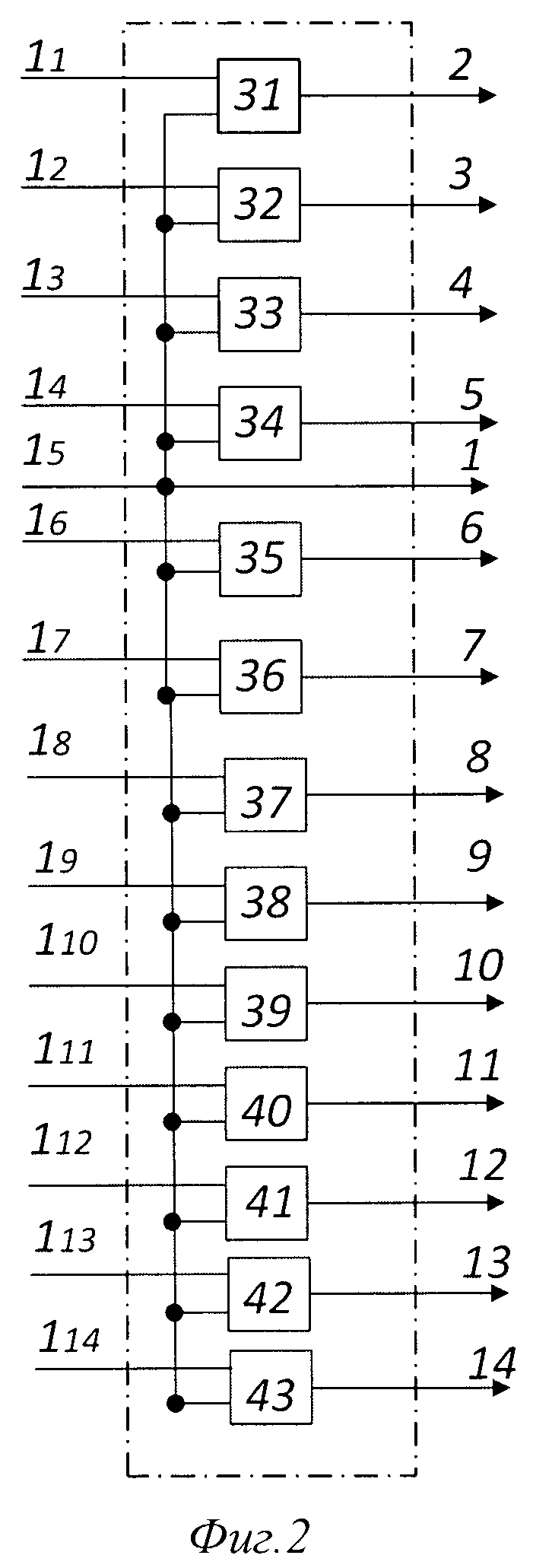

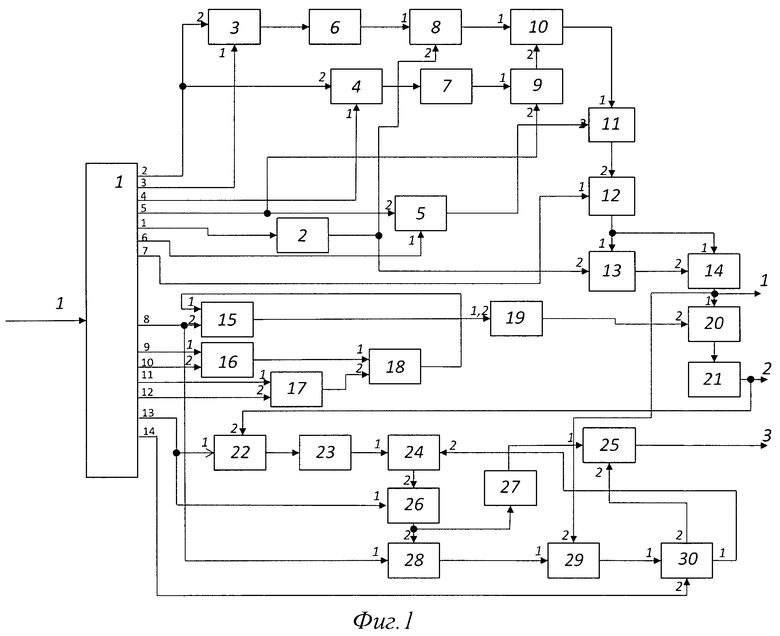

На фиг.1 приведена схема предлагаемого устройства; на фиг.2 - схема блока памяти.

Устройство содержит блок памяти 1, таймер 2, первый и второй вычитатели 3 и 4 соответственно, первый блок деления 5, первый и второй блоки определения абсолютного значении 6 и 7 соответственно, второй и третий блоки деления 8 и 9 соответственно, третий вычитатель 10, четвертый блок деления 11, первый компаратор 12, первый ключ 13, первый элемент памяти 14, первый сумматор 15, четвертый вычитатель 16, первый и второй блоки умножения 17 и 18 соответственно, второй сумматор 19, третий блок умножения 20, блок извлечения квадратного корня 21, пятый блок деления 22, блок выделения целой части 22, вычитающий счетчик 24, второй ключ 25, четвертый блок умножения 26, второй элемент памяти 27, третий сумматор 28, шестой блок деления 29, второй компаратор 30, причем первый выход блока памяти 1 подключен к датчику таймера 2, первый вход первого вычитателя 3 соединен с третьим выходом блока памяти 1, вторые входы первого 3 и второго 4 вычитателей объединены и подключены ко второму выходу блока памяти 1, первый вход второго вычитателя 4 соединен с четвертым выходом блока памяти 1, первый и второй входы первого блока деления 5 подключены соответственно к шестому и пятому выходам блока памяти 1, выходы первого 3 и второго 4 вычитателей через первый 6 и второй 7 блоки определения абсолютного значения соединены с первыми входами второго 8 и третьего 9 блоков деления соответственно, второй вход второго блока деления 8 подключен к выходу таймера 2 и второму входу ключа 13, второй вход третьего блока деления 9 соединен с пятым выходом блока памяти 1, выходы второго 8 и третьего 9 блоков деления подключены соответственно к первому и второму входу третьего вычитателя 10, выход которого подключен к первому входу четвертого блока деления 11, второй вход которого связан с выходом первого блока деления 5, выход четвертого блока деления 11 соединен со вторым входом компаратора 12, первый вход которого подключен к седьмому выходу блока памяти 1, выход компаратора 12 соединен с первым входом ключа 13 и первым входом элемента памяти 14, выход ключа 13 подключен ко второму входу элемента памяти 14, выход которого является первым выходом устройства, второй вход сумматора 15 подключен к восьмому выходу блока памяти 1, девятый и десятый выходы блока памяти 1 подключены к первому и второму входам четвертого вычитателя 16 соответственно, первый и второй входы первого умножителя 17 подключены к одиннадцатому и двенадцатому выходам блока памяти 1, выход четвертого вычитателя 16 и первого блока умножения 17 подключены к первому и второму входам второго блока умножения 18 соответственно, выход которого подключен к первому входу первого сумматора 15, выход которого соединен с первым и вторым входами второго сумматора 19, выход которого подключен к второму входу третьего блока умножения 20, первый вход которого связан с выходом элемента памяти 14, выход третьего блока умножения 20 подключен к входу блока извлечения квадратного корня 21, выход которого является вторым выходом устройства, тринадцатый выход блока памяти 1 подключен к первым входам пятого блока деления 22 и четвертого блока умножения 26, второй вход пятого блока деления 22 соединен с выходом блока извлечения квадратного корня 21, восьмой выход блока памяти 1 связан с первым входом третьего сумматора 28, второй вход которого подключен к выходу четвертого блока умножения 26 и входу второго элемента памяти 27, выход пятого блока деления 22 через блок выделения целой части 23 подключен к первому входу вычитающего счетчика 24, выход которого соединен с вторым входом четвертого блока умножения 26, выход третьего сумматора 28 связан с первым входом шестого блока деления 29, второй вход которого подключен к выходу первого элемента памяти 14, четырнадцатый выход блока памяти 1 соединен со вторым входом второго компаратора 30, первый вход которого связан с выходом шестого блока деления 29, первый выход второго компаратора 30 соединен со вторым входом вычитающего счетчика 24, второй выход второго компаратора 30 подключен к второму входу второго ключа 25, первый вход которого соединен с выходом второго элемента памяти 27, выход второго ключа является третьим выходом устройства.

Блок памяти 1 содержит третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый элементы памяти 31-43 соответственно.

Устройство работает следующим образом.

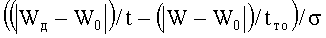

На вход 11 блока памяти 1 поступает номинальное значение определяющего параметра W0. На вход 12 блока памяти 1 поступает допустимое значение определяющего параметра Wд (верхняя либо нижняя граница параметра). На вход 13 поступает текущее значение параметра W. На вход 14 поступает значение tто, т.е предыдущее значение времени начала технического обслуживания(ТО), при котором было определено W. На вход 16 поступает значение D дисперсии определяющего параметра. На вход 17 поступает u1-ε значение квантиля стандартного нормального распределения (соответствующее вероятности безотказной работы). На вход 18 поступает значение τто, среднее время проведения одной профилактики. На вход 19 поступает λт - интенсивность внезапных отказов при работе под током. На вход 110 поступает значение λвык - интенсивность внезапных отказов в выключенном состоянии. На вход 111 поступает значение Tв - среднее время устранения одной неисправности. На вход 112 поступает значение tт - время работы изделия под током. На вход 113 поступает значение Tтор.min - минимальный период проведения регламентированного технического обслуживания изделия. На вход 114 поступает Кг.зад - значение заданного коэффициента готовности изделия. На вход 15 поступает управляющий сигнал, необходимый для записи в элементы памяти 31-43 сигналов W0, Wд, W, tто, D, u1-ε, τто, λт, λвык, Tв, tт, Tтор.min, Kг.зад. Значения W0, Wд, W, tто, D, u1-ε, τто, λт, λвык, Tв, tт, Tто

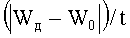

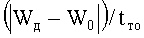

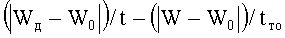

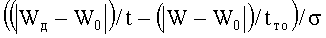

p.min, Kг.зад с входов элементов памяти поступают соответственно на второй, третий, четвертый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый выходы блока памяти 1. Управляющий сигнал с входа 15 поступает на первый выход блока памяти 1. По управляющему сигналу, поступающему с первого выхода блока памяти 1 на вход таймера 2, таймер включается в работу и на его выходе формируется сигнал Uвых=t, который поступает на второй вход второго блока деления 8, на второй вход ключа 13. Со второго выхода блока памяти 1 значение W0 поступает на второй вход первого вычитателя 3 и второй вход второго вычитателя 4. С третьего входа блока памяти 1 значение Wд поступает на первый вход первого вычитателя 3. С четвертого выхода блока памяти 1 значение W поступает на первый вход второго вычитателя 4. С пятого выхода блока памяти 1 значение tто поступает на второй вход первого блока деления 5 и второй вход третьего блока деления 9. С седьмого выхода блока памяти 1 значение u1-ε поступает на 1 первый вход компаратора 12. Значение сигнала Wд -W0 с выхода первого вычитателя 3 поступает на вход первого блока определения абсолютного значения 6, с выхода которого сигнал -

Таким образом, предлагаемое устройство позволяет определить время наступления постепенного отказа, оптимальный период технического обслуживания изделия, а также очередной регламентированный период технического обслуживания с учетом заданного коэффициента готовности. Устройство успешно прошло испытание и используется при планировании технического обслуживания изделий.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ХАРАКТЕРИСТИК ГОТОВНОСТИ ИЗДЕЛИЯ К ПРИМЕНЕНИЮ | 2020 |

|

RU2748389C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ХАРАКТЕРИСТИК ГОТОВНОСТИ ИЗДЕЛИЯ К ПРИМЕНЕНИЮ | 2019 |

|

RU2720382C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2007 |

|

RU2347272C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ЭКСПЛУАТАЦИОННЫХ ХАРАКТЕРИСТИК ИЗДЕЛИЯ | 2010 |

|

RU2452027C2 |

| Устройство для определения оптимального времени начала проведения технического обслуживания изделия | 1991 |

|

SU1800468A1 |

| Устройство для определения времени начала технического обслуживания изделия | 1991 |

|

SU1800469A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОЙ ПРОГРАММЫ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ СИСТЕМЫ | 2007 |

|

RU2358320C2 |

| УСТРОЙСТВО КОНТРОЛЯ ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ НА БАЗЕ ТЕХНОЛОГИИ Ethernet | 2014 |

|

RU2546560C1 |

| Устройство для определения оптимального периода технического обслуживания изделия | 1990 |

|

SU1755309A1 |

| Устройство для определения оптимального периода технического состояния изделия | 1990 |

|

SU1767510A1 |

Изобретение относится к устройству для определения оптимального периода технического обслуживания изделия. Технический результат заключается в расширении функциональных возможностей устройства за счет возможности определения очередного периода регламентированного технического обслуживания изделия с учетом заданного коэффициента готовности изделия. Устройство содержит блок памяти, таймер, четыре вычитателя, шесть блоков деления, два блока определения абсолютного значения, три сумматора, два компаратора, два ключа, два элемента памяти, четыре умножителя, блок извлечения квадратного корня, блок выделения целой части, вычитающий счетчик. 2 ил.

Устройство для определения оптимального периода технического обслуживания изделия, содержащее блок памяти, таймер, четыре вычитателя, четыре блока деления, два блока определения абсолютного значения, два сумматора, компаратор, ключ, элемент памяти, три умножителя, блок извлечения квадратного корня, при этом первый выход блока памяти подключен к входу таймера, первый вход первого вычитателя соединен с третьим выходом блока памяти, вторые входы первого и второго вычитателей объединены и подключены ко второму выходу блока памяти, первый вход второго вычитателя соединен с четвертым выходом блока памяти, первый и второй входы блока первого блока деления подключены соответственно к шестому и пятому выходам блока памяти, выходы первого и второго вычитателей через первый и второй блоки определения абсолютного значения соединены с первыми входами второго и третьего блоков деления соответственно, второй вход второго блока деления подключен к выходу таймера и второму входу ключа, второй вход третьего блока деления соединен с пятым выходом блока памяти, выходы второго и третьего блоков деления подключены соответственно к первому и второму входам третьего вычитателя, выход которого подключен к первому входу четвертого блока деления, на второй вход которого поступает сигнал с выхода первого блока деления, выход четвертого блока деления соединен с вторым входом компаратора, первый вход которого подключен к седьмому выходу блока памяти, выход компаратора соединен с первым входом ключа и первым входом элемента памяти, выход ключа подключен к второму входу элемента памяти, выход которого является первым выходом устройства, второй вход первого сумматора подключен к восьмому выходу блока памяти, девятый и десятый выходы блока памяти подключены к первому и второму входам четвертого вычитателя соответственно, первый и второй входы первого блока умножения подключены к одиннадцатому и двенадцатому выходам блока памяти, выход четвертого вычитателя и первого блока умножения подключены к первому и второму входам второго блока умножения соответственно, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым и вторым входами второго сумматора, выход которого подключен к первому входу третьего блока умножения, первый вход которого связан с выходом элемента памяти, выход третьего блока умножения соединен с входом блока извлечения квадратного корня, выход которого является вторым выходом устройства, отличающееся тем, что в него согласно изобретению введены пятый и шестой блоки деления, блок выделения целой части, вычитающий счетчик, четвертый блок умножения, третий сумматор, второй элемент памяти, второй ключ и второй компаратор, причем тринадцатый выход блока памяти подключен к первым входам пятого блока деления и четвертого блока умножения, второй вход пятого блока деления соединен с выходом блока извлечения квадратного корня, восьмой выход блока памяти связан с первым входом третьего сумматора, второй вход которого подключен к выходу четвертого блока умножения и входу второго элемента памяти, выход пятого блока деления через блок выделения целой части подключен к первому входу вычитающего счетчика, выход которого соединен со вторым входом четвертого блока умножения, выход третьего сумматора связан с первым входом шестого блока деления, второй вход которого подключен к выходу первого элемента памяти, четырнадцатый выход блока памяти соединен со вторым входом второго компаратора, первый вход которого связан с выходом шестого блока деления, первый выход второго компаратора соединен со вторым входом вычитающего счетчика, второй выход второго компаратора подключен ко второму входу второго ключа, первый вход которого соединен с выходом второго элемента памяти, выход второго ключа является третьим выходом устройства.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2007 |

|

RU2347272C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2001 |

|

RU2206123C2 |

| EP 1918885 A2, 07.05.2008 | |||

| US 5995886 A1, 30.11.1999 | |||

| US 8285437 B2, 09.10.2012 | |||

Авторы

Даты

2014-12-27—Публикация

2013-06-27—Подача