1. Область техники

Изобретение относится к электронной технике обработки видеосигналов и может быть использовано в устройствах, в том числе малогабаритных, с автономным питанием от аккумуляторных батарей, осуществляющих декодирование входного композитного видеосигнала телевизионного формата и отображение движущихся изображений на дисплеях различного физического принципа действия, включая микродисплеи.

2. Уровень техники

Декодеры композитных видеосигналов являются основой построения электронных схем, управляющих работой устройств отображения неподвижных и движущихся изображений на дисплеях различного физического принципа действия, включая микродисплеи. На современном уровне развития микроэлектроники видеодекодеры реализуются, как правило, на основе специализированных больших интегральных схем (БИС), осуществляющих декодирование входного композитного видеосигнала, выделение из него яркостной и цветоразностной составляющих, представленных в аналоговой или цифровой форме и преобразование форматов видеосигналов для обеспечения совместимости с видеоинтерфейсом дисплея или микродисплея определенного типа. В качестве примера можно привести декодирующее устройство типа O4 фирмы TekGear, описанное в статье "Compact Drive Electronics with Luminance Control and WF05-optic mount for eMagin SVGA+& SVGA-3D OLED Microdisplays", www.tekgear.com. Это устройство реализовано на нескольких БИС и имеет габаритные размеры в плане 38,1×16,9 мм, в то время как сам микродисплейный модуль SVGA+фирмы eMagin имеет существенно меньшие габаритные размеры: 19,8×15,2×4,5 мм ("SVGA+Rev3 Series 852×600 active matrix OLED Microdisplay", www.emagin.com). Таким образом, уменьшение габаритных размеров управляющей электроники, а также снижение потребляемой мощности являются актуальными задачами при построении различных устройств отображения видеоинформации, в особенности для малогабаритных систем отображения нашлемного типа с втономным питанием. Решение этих задач возможно по пути расширения функциональных возможностей БИС видеодекодеров до уровня Систем-на-Кристалле (БИС СнК) на основе современных полупроводниковых технологий, что позволит существенно сократить количество электронных компонентов и, как следствие, - уменьшить габаритные размеры и потребляемую мощность управляющей электроники систем отображения видеоинформации.

Известны устройства - видеодекодеры, осуществляющие цифровое декодирование аналогового видеосигнала, состоящие из аналого-цифрового преобразователя, блока цифровой обработки и цифрового постпроцессора, к выходу которого подключается дисплей с цифровым входным интерфейсом (см. патент US 20100040133 A1, МКИ H04N 7/12, опубликован 18.02.2010 и патент US 8233529 B2, МКИ H04N 7/12, опубликован 31.07.2012). Недостатком данного устройства является невозможность его подключения к стандартным видеомониторам и дисплеям, включая микродисплеи, имеющих входной цифровой или аналоговый интерфейс RGB.

Известно также устройство - композитный видеодекодер, осуществляющий декодирование композитного видеосигнала, состоящее из входного блока аналоговой обработки сигнала, аналого-цифрового преобразователя, блока цифровой обработки и блока параллельно-последовательного преобразования, на выходе которого образуется поток видеоданных в последовательном формате (см. патент США US 6300985, МКИ: H04N 9/78, опубликован 9.14.2001). Недостатком данного устройства также является его ограниченные функциональные возможности, выражающиеся в несовместимости выходного интерфейса композитного видеодекодера с входными видеоинтерфейсами стандартных видеомониторов, дисплеев и микродисплеев.

Наиболее близким аналогом по технической сущности к предлагаемому решению - прототипом, является устройство многостандартного видеодекодера, описанное в патенте US 6833875 B1, МКИ H04N 9/78, опубликован 21.12.2004. Видеодекодер состоит из входного блока аналоговой обработки сигнала, блока цифровой обработки и блока цифрового выходного интерфейса компонентного видеовыхода Yout, Uout, Vout, выходные сигналы которого могут подключаться к мониторам и дисплеям, имеющим аналогичный входной цифровой интерфейс.

Недостатком данного устройства являются ограниченные функциональные возможности, выражающиеся в несовместимости выходного интерфейса мульти-стандартного видеодекодера с широкораспространенными входными цифровыми и аналоговыми видеоинтерфейсами типа RGB стандартных видеомониторов, дисплеев и микродисплеев, не имеющих редкоиспользуемого входного цифрового интерфейса Yout, Uout, Vout. Кроме того, в рассматриваемом прототипе цифрового видеодекодера отсутствуют технические средства для преобразования чересстрочного формата композитного видеосигнала в прогрессивный формат, в котором работает большинство современных видеомониторов, дисплеев и микродисплеев.

Указанные недостатки устраняются в заявляемом изобретении, задачами которого являются:

- расширение функциональных возможностей цифрового декодера композитного видеосигнала;

- обеспечение возможности непосредственного согласования видеодекодера с видеомониторами, дисплеями и микродисплеями различных типов, имеющих стандартный цифровой или аналоговый интерфейс RGB;

- корректное преобразование форматов представления видеосигнала из чересстрочного в прогрессивный;

- программируемость режимов работы цифрового декодера композитного видеосигнала при помощи двухпроводного интерфейса;

Перечисленные выше усовершенствования видеодекодера превращают цифровой декодер композитного видеосигнала при его реализации в форме однокристальной БИС в законченную Систему-на-Кристалле (СнК), позволяющую минимизировать требуемое количество дополнительных электронных компонентов, уменьшить габаритные размеры и мощность потребления управляющей электроники, построенной на основе предлагаемого видеодекодера, что особенно актуально при построении малогабаритных систем отображения информации с батарейным питанием.

3. Раскрытие изобретения.

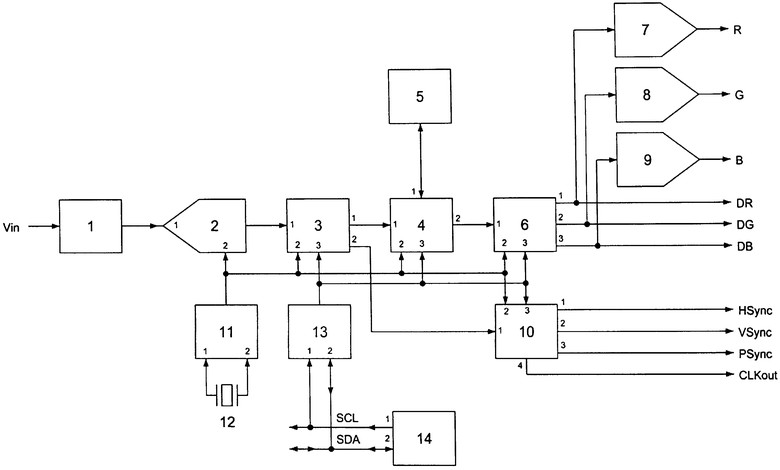

Сущность заявляемого изобретения поясняется чертежом 1, на котором изображена блок-схема однокристального цифрового декодера композитного видеосигнала.

На чертеже1 приняты следующие обозначения:

1 - блок аналоговой обработки сигнала;

2 - аналого-цифровой преобразователь (АЦП);

3 - блок цифровой обработки;

4 - блок менеджера памяти;

5 - блок оперативного запоминающего устройства (ОЗУ);

6 - цифровой блок матрицирования RGB и масштабирования;

7 - первый блок цифроаналогового преобразователя (ЦАП канала R);

8 - второй блок цифроаналогового преобразователя (ЦАП канала G);

9 - третий блок цифроаналогового преобразователя (ЦАП канала В);

10 - блок формирования синхросигналов;

11 - блок тактового генератора;

12 - кварцевый резонатор;

13 - блок последовательного двухпроводного интерфейса;

14 - управляющий микроконтроллер

В цифровой видеодекодер, содержащий блок аналоговой обработки сигнала 1, аналого-цифровой преобразователь (АЦП) 2 и блок цифровой обработки 3, дополнительно введены блок менеджера памяти 4, блок оперативного запоминающего устройства (блок ОЗУ) 5, цифровой блок матрицирования RGB и масштабирования 6, три блока 7, 8, 9 цифроаналоговых преобразователей (ЦАП) компонентных сигналов R, G и В, блока формирования синхросигналов 10, блока тактового генератора 11, кварцевого резонатора 12, блока последовательного двухпроводного интерфейса 13 и управляющего микроконтроллера 14, первый и второй выходы которого образуют двухпроводную шину управления, представленную в виде сигналов SCL и SDA и подключены к первому и второму входу блока последовательного двухпроводного интерфейса 13. Выход блока 13, представляет собой регистровую шину данных, подключен к третьему входу блока цифровой обработки 3, третьему входу блока менеджера памяти 4, третьему входу блока матрицирования RGB и масштабирования 6 и третьему входу блока формирования синхросигналов 10, на первом выходе которого формируется сигнал строчной синхронизации HSync, на втором выходе - сигнал кадровой синхронизации VSync, на третьем выходе - сигнал синхронизации полей изображения PSync, а на четвертом выходе - сигнал синхронизации выходных данных CLKout, причем входной аналоговый композитный видеосигнал Vin подается на вход блока аналоговой обработки 1, выход которого соединен с первым входом аналого-цифрового преобразователя 2, выход которого соединен с первым входом блока цифровой обработки 3, первый выход которого соединен с первым входом блока менеджера памяти 4, первый выход которого соединен с блоком ОЗУ 5 при помощи двунаправленной шины, а второй выход соединен с первым входом цифрового блока матрицирования RGB и масштабирования 6, первый выход которого, являющийся цифровым выходом компонентного сигнала DR, подключен ко входу первого блока цифроаналогового преобразователя 7, выход которого является аналоговым выходом компонентного сигнала R, второй выход цифрового блока матрицирования RGB и масштабирования 6, являющийся цифровым выходом компонентного сигнала DG, подключен ко входу второго блока цифроаналогового преобразователя 8, выход которого является аналоговым выходом компонентного сигнала G, третий выход цифрового блока матрицирования RGB и масштабирования 6, являющийся цифровым выходом компонентного сигнала DB, подключен ко входу третьего блока цифроаналогового преобразователя 9, выход которого является аналоговым выходом компонентного сигнала В, при этом выводы кварцевого резонатора 12 подключены к первому и второму входам блока тактового генератора 11, выход которого соединен со вторым входом аналого-цифрового преобразователя 2, вторым входом блока цифровой обработки 3, вторым входом блока менеджера памяти 4, вторым входом цифрового блока матрицирования RGB и масштабирования 6 и вторым входом блока формирования синхросигналов 10, а второй выход блока цифровой обработки 3 соединен с первым входом блока формирования синхросигналов 10.

В соответствии с заявляемым изобретением однокристальный цифровой декодер композитного видеосигнала работает следующим образом.

Входной аналоговый композитный видеосигнал Vin поступает на вход блока аналоговой обработки 1, в котором усиливается, нормируется по амплитуде и фильтруется аналоговым фильтром нижних частот с частотой среза, не превышающей половины частоты дискретизации сигнала аналого-цифрового преобразователя 2 для исключения спектральных искажений при осуществлении преобразования сигнала из аналоговой формы в цифровую. Дополнительно в блоке аналоговой обработки осуществляется "привязка" уровня черного входного видеосигнала к определенному потенциалу во входном диапазоне сигналов АЦП. Блок АЦП 2 преобразует видеосигнал в цифровую форму. Работа блока АЦП, а также работа всех цифровых блоков видеодекодера синхронизируется тактовым сигналом, поступающим с выхода блока тактового генератора 11 с подключенным к нему кварцевым резонатором 12. Непрерывный поток цифровых данных разрядностью 8 бит поступает с выхода АЦП на вход блока цифровой обработки 3, в котором осуществляется цифровое декодирование композитного видеосигнала и его разделение на яркостную Y и цветоразностные Cr, Cb составляющие. На выходе блока цифровой обработки образуется поток чересстрочной развертки изображения формата YCrCb 4:2:2, который через блок менеджера памяти 4 направляется в ОЗУ 5 для буферизации кадра изображения. Тот же блок менеджера памяти 4 управляет процессом выборки данных из ОЗУ 5, причем в процессе чтения ОЗУ осуществляется переупорядочение буферизованных данных таким образом, чтобы на выходе блока менеджера памяти 4 получить прогрессивный формат развертки изображения. Поток видеоданных на выходе блока менеджера памяти 4 по-прежнему представлен в виде яркостной Y и цветоразностных компонент Cr, Cb, поэтому, для того, чтобы обеспечить совместимость представления видеосигналов с интерфейсами стандартных мониторов, дисплеев и микродисплеев, этот поток поступает на вход цифрового блока матрицирования RGB 6, в котором дополнительно осуществляется масштабирование сигналов с учетом требуемого графического разрешения монитора или дисплея. Выходы блока матрицирования RGB и масштабирования 6 представляют собой цифровые компонентные видеовыходы DR, DG и DB и могут быть подключены непосредственно к мониторам, дисплеям и микродисплеям, имеющим цифровой RGB интерфейс. Для того чтобы заявленный видеодекодер можно было подключать к устройствам отображения информации, имеющим только аналоговый RGB интерфейс, выходы DR, DG и DB блока матрицирования RGB и масштабирования 6 подключаются к входам соответствующих блоков ЦАП 7, 8 и 9, на выходах которых образуются аналоговые выходные видеосигналы RGB. Передача видеосигналов, представленных как в аналоговой, так и в цифровой форме, на устройства отображения должно сопровождаться синхросигналами строчной и кадровой частоты HSync и VSync, а в случае цифрового интерфейса - еще и выходной тактовой пиксельной частотой CLKout. Для выработки этих сигналов служит блок формирования синхросигналов 10, на входы которого поступают сигналы системной тактовой частоты с выхода блока тактового генератора 11 и сигналы синхронизации со второго выхода блока цифровой обработки 3. Дополнительно блок формирования синхросигналов 10 вырабатывает сигнал синхронизации полей изображения PSync, позволяющий идентифицировать четные и нечетные поля кадра для чересстрочных систем отображения. Цифровые блоки обработки сигнала 3, менеджера памяти 4, матрицирования RGB и масштабирования 6 и блок формирования синхросигналов 10 имеют в своем составе ряд регистров, изменяя содержимое которых, можно управлять режимами работы видеодекодера и значением ряда характеристик формируемых им выходных сигналов. Эти регистры образуют регистровый файл с уникальными адресами регистров и имеют общую регистровую шину, подключенную к выходу блока последовательного двухпроводного интерфейса 13. Входы блока 13 подключаются при помощи двухпроводной шины (сигналы SCL и SDA) к управляющему микроконтроллеру 14, под управлением которого можно изменять режимы работы видеодекодера и характеристики его выходных сигналов для удовлетворения конкретным характеристикам подключенного к видеодекодеру устройства отображения (монитору, дисплею или микродисплею).

Для того чтобы обеспечить возможность подключения к стандартным видеомониторам и дисплеям, включая микродисплеи, имеющих входной цифровой или аналоговый интерфейс RGB, в однокристальный цифровой декодер композитного видеосигнала дополнительно введены цифровой блок матрицирования RGB и масштабирования 6 с выходом в виде цифровых компонентных сигналов DR, DG и DB, три блока 7, 8, 9 цифроаналоговых преобразователей (ЦАП) компонентных сигналов R, G и В, блок формирования синхросигналов 10.

Для преобразования чересстрочного формата композитного видеосигнала в прогрессивный формат, в котором работает большинство современных видеомониторов, дисплеев и микродисплеев, в однокристальный цифровой декодер композитного видеосигнала дополнительно введены блок менеджера памяти 4, блок оперативного запоминающего устройства (блок ОЗУ) 5.

Для того чтобы обеспечить программируемость режимов работы, в цифровой декодер композитного видеосигнала дополнительно введены двухпроводная шина (сигналы SCL и SDA) и управляющий микроконтроллер 14, под управлением которого можно изменять режимы работы видеодекодера и характеристики его выходных сигналов для удовлетворения конкретным характеристикам подключенного к видеодекодеру устройству отображения (монитору, дисплею или микродисплею).

4. Задачи изобретения.

Однокристальный цифровой декодер композитного видеосигнала осуществляет цифровое декодирование аналогового видеосигнала и предназначен для решения следующих задач.

Непосредственное согласование видеодекодера с видеомониторами, дисплеями и микродисплеями различных типов, имеющих стандартный цифровой или аналоговый интерфейс RGB;

Корректное преобразование форматов представления видеосигнала из чересстрочного в прогрессивный;

Программируемость режимов работы цифрового декодера композитного видеосигнала при помощи двухпроводного интерфейса и управляющего микроконтроллера.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБРАБОТКИ ИЗОБРАЖЕНИЯ, СПОСОБ ОБРАБОТКИ ИЗОБРАЖЕНИЯ И СИСТЕМА ПЕРЕДАЧИ ДАННЫХ | 2009 |

|

RU2507584C2 |

| СИСТЕМА И СПОСОБ УПРАВЛЕНИЯ ПРОГРАММИРУЕМЫМ МУЛЬТИМЕДИЙНЫМ КОНТРОЛЛЕРОМ | 2006 |

|

RU2483461C2 |

| ЦИФРОВОЙ МАЛОГАБАРИТНЫЙ USB ОСЦИЛЛОГРАФ | 2009 |

|

RU2402024C1 |

| СИСТЕМА ДИСПЛЕЯ | 1991 |

|

RU2119187C1 |

| Способ и устройство для преобразования цвета при универсальном видеокодировании (VVC) | 2020 |

|

RU2787810C1 |

| УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ЦВЕТНЫМ ЖИДКОКРИСТАЛЛИЧЕСКИМ ДИСПЛЕЕМ | 2005 |

|

RU2314574C2 |

| Способ и устройство для видеокодирования | 2020 |

|

RU2782516C1 |

| ПРЕОБРАЗОВАНИЕ ЦВЕТА ДЛЯ ВИДЕОКОДИРОВАНИЯ | 2020 |

|

RU2782437C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ ИЗОБРАЖЕНИЯ И СПОСОБ ЕГО РАБОТЫ | 2017 |

|

RU2719439C1 |

| УСТРОЙСТВО ЭКРАННОЙ ИНДИКАЦИИ ДЛЯ СИСТЕМЫ ОБРАБОТКИ ЦИФРОВОГО ВИДЕОСИГНАЛА | 1995 |

|

RU2146854C1 |

Изобретение относится к обработке видеосигналов и может быть использовано в устройствах, осуществляющих декодирование входного композитного видеосигнала телевизионного формата. Техническими результатами являются обеспечение возможности согласования видеодекодера с дисплеями различных типов, имеющих стандартный цифровой или аналоговый интерфейс RGB; обеспечение корректного преобразования форматов представления видеосигнала из чересстрочного в прогрессивный; а также обеспечение возможности программировать режимы работы цифрового декодера композитного видеосигнала при помощи двухпроводного интерфейса. Цифровой видеодекодер содержит блок аналоговой обработки сигнала, АЦП, блок цифровой обработки, блок менеджера памяти, ОЗУ, цифровой блок матрицирования RGB и масштабирования, первый, второй и третий блоки ЦАП компонентных сигналов R, G и В, блок формирования синхросигналов, блок тактового генератора, кварцевый резонатор, блок последовательного двухпроводного интерфейса и управляющий микроконтроллер. 1 ил.

Однокристальный цифровой декодер композитного видеосигнала, содержащий блок аналоговой обработки сигнала, аналого-цифровой преобразователь (АЦП) и блок цифровой обработки, отличающийся тем, что в него дополнительно введены блок менеджера памяти, блок оперативного запоминающего устройства (блок ОЗУ), цифровой блок матрицирования RGB и масштабирования, первый, второй и третий блоки цифроаналоговых преобразователей (ЦАП) компонентных сигналов R, G и В, блок формирования синхросигналов, блок тактового генератора, кварцевый резонатор, блок последовательного двухпроводного интерфейса и управляющий микроконтроллер, первый и второй выходы которого образуют двухпроводную шину управления, представленную в виде сигналов SCL и SDA, и подключены к первому и второму входу блока последовательного двухпроводного интерфейса, выход которого, представляющий собой регистровую шину данных, подключен к третьему входу блока цифровой обработки, третьему входу блока менеджера памяти, третьему входу блока матрицирования RGB и масштабирования и третьему входу блока формирования синхросигналов, на первом выходе которого формируется сигнал строчной синхронизации HSync, на втором выходе - сигнал кадровой синхронизации VSync, на третьем выходе - сигнал синхронизации полей изображения PSync, а на четвертом выходе - сигнал синхронизации выходных данных CLKout, причем входной аналоговый композитный видеосигнал Vin подается на вход блока аналоговой обработки, выход которого соединен с первым входом аналого-цифрового преобразователя, выход которого соединен с первым входом блока цифровой обработки, первый выход которого соединен с первым входом блока менеджера памяти, первый выход которого соединен с блоком ОЗУ при помощи двунаправленной шины, а второй выход соединен с первым входом цифрового блока матрицирования RGB и масштабирования, первый выход которого, являющийся цифровым выходом компонентного сигнала DR, подключен ко входу первого блока цифроаналогового преобразователя, выход которого является аналоговым выходом компонентного сигнала R, второй выход цифрового блока матрицирования RGB и масштабирования, являющийся цифровым выходом компонентного сигнала DG, подключен ко входу второго блока цифроаналогового преобразователя, выход которого является аналоговым выходом компонентного сигнала G, третий выход цифрового блока матрицирования RGB и масштабирования, являющийся цифровым выходом компонентного сигнала DB, подключен ко входу третьего блока цифроаналогового преобразователя, выход которого является аналоговым выходом компонентного сигнала В, при этом выводы кварцевого резонатора подключены к первому и второму входам блока тактового генератора, выход которого соединен со вторым входом аналого-цифрового преобразователя, вторым входом блока цифровой обработки, вторым входом блока менеджера памяти, вторым входом цифрового блока матрицирования RGB и масштабирования и вторым входом блока формирования синхросигналов, а второй выход блока цифровой обработки соединен с первым входом блока формирования синхросигналов.

| US 6833875 B1, 21.12.2004 | |||

| US 6300985 B1, 09.10.2001 | |||

| US 6271888 B1, 07.08.2001 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2009 |

|

RU2413387C1 |

Авторы

Даты

2014-12-27—Публикация

2012-10-04—Подача