Область техники

Изобретение относится к области силовой электроники. Оно основано на способе работы преобразовательной схемы и устройстве для его осуществления согласно ограничительной части независимых пунктов формулы изобретения.

Уровень техники

Прямые преобразователи, в частности матричные преобразователи, имели в прошлом скорее академичное значение. Однако сегодня прямые преобразователи приобретают все большее значение прежде всего в промышленной сфере, поскольку с помощью прямого преобразователя без применения дорогостоящей промежуточной схемы постоянного напряжения или промежуточной схемы постоянного тока входное напряжение или входной ток первой амплитуды и первой частоты может преобразовываться непосредственно в выходное напряжение или выходной ток второй амплитуды и второй частоты. Такой прямой преобразователь раскрыт, например, в US 6,900,998 В2. В нем прямой преобразователь имеет n=3 входных фазовых выводов и р=3 выходных фазовых выводов, т.е. прямой преобразователь согласно US 6.900.998 В2 выполнен трехфазным со стороны входа и выхода. Кроме того, прямой преобразователь согласно US 6,900,998, В2 содержит девять фазовых модулей с соответственно двухполюсной коммутационной ячейкой для коммутации положительного и отрицательного напряжения между полюсами, при этом каждый выходной фазовый вывод последовательно соединен с каждым входным фазовым выводом непосредственно через коммутационную ячейку. Такая коммутационная ячейка содержит управляемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии. Фазовые модули прямого преобразователя согласно патенту US 6,900,998 В2 содержат только коммутационные ячейки без индуктивностей. Следовательно, напряжение на каждой ветви, т.е. на каждой двухполюсной коммутационной ячейке, не может задаваться таким образом, чтобы обеспечивалось непрерывное прохождение тока от входного фазного вывода к выходному фазному выводу, вследствие чего не может достигаться активное регулирование тока соответствующей ветвью и соответствующим фазовым модулем. Токи выходных фазовых выводов фазовых модулей подаются дискретно на отдельные фазовые модули, т.е. токи отдельных фазовых модулей выполняют прерывные функции, совершающие скачки на отдельных участках от нуля до текущего значения тока на соответствующем выходном фазовом выводе. Подача тока на выходные фазовые выводы фазовых модулей и их отвод от них требуют применения сложного алгоритма управления, решаемого с помощью трудоемких таблиц. При этом необходимо иметь в виду, что никогда не должны закорачиваться отдельные фазы с образованием контура напряжения, так как общее напряжение для двух фазовых модулей в обычном случае не является точно одинаковым. Одновременно никогда не должно прерываться прохождение тока в выводах, т.е. фазовые модули должны всегда коммутироваться точно одновременно, что означает значительную трудоемкость управления. Кроме того, подключение и отключение полных токов величины ведет к появлению большого действующего тока (ток RMS) с соответственно большими потерями в конструктивных элементах, в частности в силовых полупроводниковых ключах.

По разным причинам мощность фазового модуля и, в частности, также мощность всех коммутационных ячеек фазового модуля может в среднем отклоняться от нуля в том случае, когда, например, фазовый модуль содержит несколько коммутационных ячеек. Причиной могут служить недостаточное управление, неустановившиеся рабочие режимы, определенные симметрии между коммутирующими действиями и токами, вызываемыми фазовыми модулями, или также конструктивное различие между отдельными компонентами. Если среднее отклонение по напряжению емкостных накопителей энергии всех коммутационных ячеек фазового модуля не равно нулю, то может произойти значительное отклонение напряжения на фазовом модуле, это приводит к нерегулируемому току, циркулирующему в фазовых модулях.

Кроме того, при использовании прямого преобразователя по патенту US 6,900,998 В2 невозможен или же очень ограничен обмен электрической энергией между отдельными ветвями. Если же прямой преобразователь в состоянии передавать электрическую энергию в большом количестве, то необходимо обеспечить мощность коммутационных ячеек из US 6,900,998 В2 соответствующей величины, что приводит к огромной площади, занимаемой таким прямым преобразователем, и к значительным расходам. Вследствие этого и системы с использованием таких прямых преобразователей также требуют соответственно большую занимаемую площадь и являются соответственно дорогостоящими.

В WO 2008/067788 А1 описан способ работы преобразовательной схемы согласно WO 2007/023064 А1, которой регулируется количество энергии в коммутационных ячейках. Раскрытый в WO 2008/067788 А1 способ касается только вариантов выполнения преобразовательной схемы по WO 2007/023064 А1, в которых три фазы одной системы соединены с двумя фазами другой системы. В «Оп Dynamics and Voltage Control of the Modular Multilevel Converter» Power Electronics and Applications, 2009, EPE 2009, 13th European Conference on IEEE, 18.09.2009», описан другой способ работы преобразовательной схемы, при котором каждый фазовый модуль содержит несколько двухполюсных, последовательно соединенных между собой коммутационных ячеек и каждая коммутационная ячейка имеет регулируемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии. Кроме того, также в WO 2008/067784 А1 описан общий способ работы преобразовательной схемы.

Раскрытие изобретения

Поэтому задачей изобретения является создание способа работы преобразовательной схемы, в частности, прямого преобразователя, с помощью которого (способа) могут быть уменьшены нежелательные циркулирующие токи с помощью фазовых модулей схемы преобразователя. Также задачей изобретения является создание устройства, с помощью которого может особо просто осуществляться способ согласно изобретению.

Указанные задачи решаются с помощью признаков пункта 1 и пунктов 5, 8 формулы изобретения. В зависимых пунктах формулы приведены предпочтительные варианты развития изобретения.

Преобразовательная схема, в частности, прямого преобразователя содержит n входных фазовых выводов и р выходных фазовых выводов, при этом n>2 и р>2. Кроме того, преобразовательная схема имеет n.р двухполюсных коммутационных ячеек для коммутирования по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, причем каждый выходной фазовый вывод последовательно соединен с каждым входным фазовым выводом через коммутационную ячейку. Каждая коммутационная ячейка содержит управляемые двунаправленные полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии. Согласно способу силовые полупроводниковые ключи коммутационных ячеек управляются посредством управляющего сигнала. Согласно изобретению к каждому последовательному соединению подключена по меньшей мере одна индуктивность, причем коммутационная ячейка вместе с индуктивностью образует фазовый модуль, и для каждого фазового модуля формируется управляющий сигнал напряжения на основе опорного сигнала в отношении напряжения на фазовом модуле и на основе сигнала напряжения на катушке индуктивности. Кроме того, сигнал напряжения формируется также посредством индуктивности на основе промежуточного задаваемого значения тока через фазовый модуль. В результате того, что соответствующее промежуточное задаваемое значение тока используется в соответствующем фазовом модуле для формирования сигнала напряжения на индуктивности и, следовательно, при формировании управляющего сигнала, то может быть обеспечен режим, при котором нежелательные циркулирующие токи через фазовые модули схемы преобразователя могут быть предпочтительно сведены к нулю. Кроме того, можно эффективно воздействовать или точно задавать влияние циркулирующих токов на токи в выходных фазовых выводах. Также способ согласно изобретению позволяет распределять токи входных и выходных фазовых выводов непрерывно между отдельными фазовыми модулями разными долями. Описанный здесь способ пригоден для схем преобразователя с любым количеством фаз.

Выполненное согласно изобретению устройство для осуществления способа работы преобразовательной схемы содержит предназначенную для формирования управляющего сигнала схему управления для каждого фазового модуля, при этом схема управления соединена с силовыми полупроводниковыми ключами коммутационных ячеек фазового модуля. В каждом фазовом модуле для формирования сигнала управления на схему управления подается сумма из опорного сигнала в отношении напряжения на фазовом модуле и сигнала напряжения на индуктивности. Наконец, для каждого фазового модуля предусмотрен первый вычислительный блок для формирования сигнала напряжения на индуктивности на основе промежуточного заданного значения тока фазового модуля. В качестве альтернативы также возможно, чтобы для всех фазовых модулей предусматривался первый общий вычислительный блок для формирования сигнала напряжения на индуктивности соответствующего фазового модуля на основе промежуточного значения тока через фазовый модуль.

Следовательно, выполненное согласно изобретению устройство для осуществления способа работы преобразовательной схемы является очень легко и не дорого реализуемым, так как схемные затраты могут поддерживаться на чрезвычайно низком уровне, при этом требуется лишь незначительное количество компонентов. С помощью такого устройства особо легко осуществим способ согласно изобретению.

Эта и другие задачи, преимущества и признаки настоящего изобретения приводятся в нижеследующем подробном описании предпочтительных вариантов выполнения изобретения со ссылками на чертежи.

Краткое описание чертежей

На чертежах представлено:

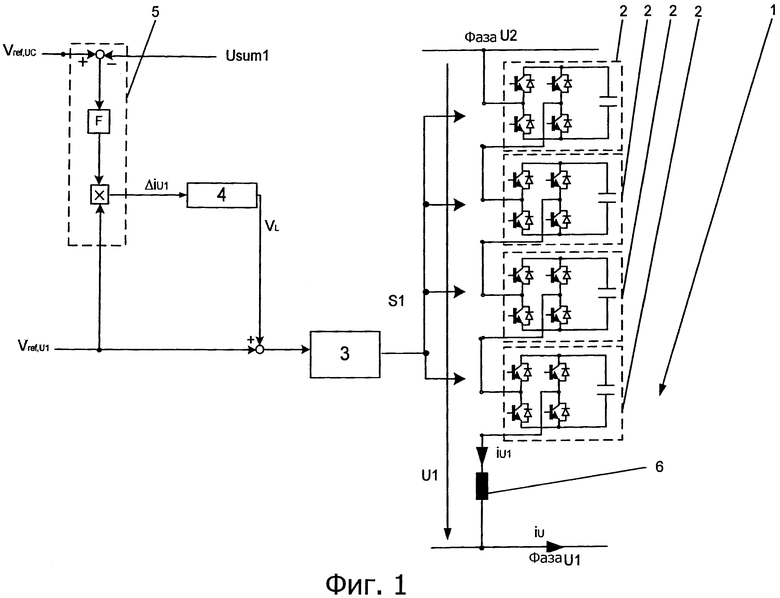

фиг.1 - первый вариант выполнения устройства согласно изобретению для осуществления способа работы преобразовательной схемы согласно изобретению;

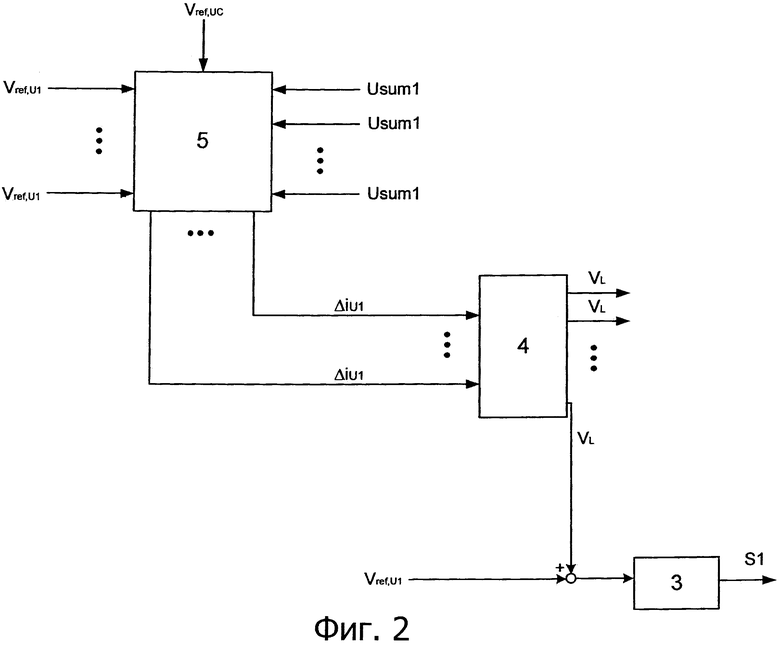

фиг.2 - второй вариант выполнения устройства согласно изобретению для осуществления способа работы преобразовательной схемы согласно изобретению;

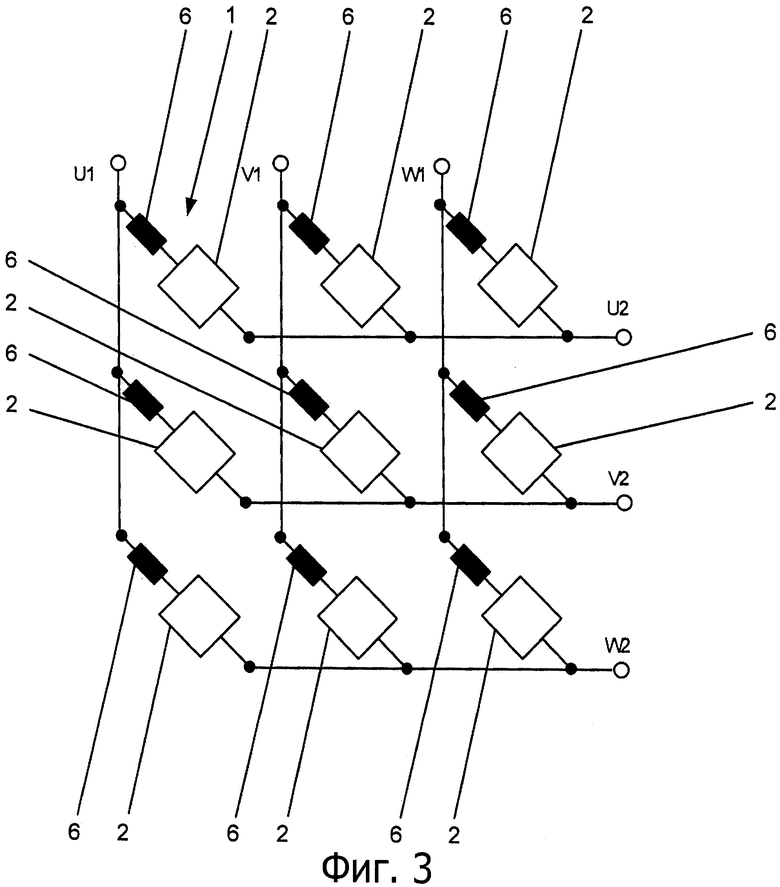

фиг.3 - первый вариант выполнения преобразовательной схемы, в частности, прямого преобразователя;

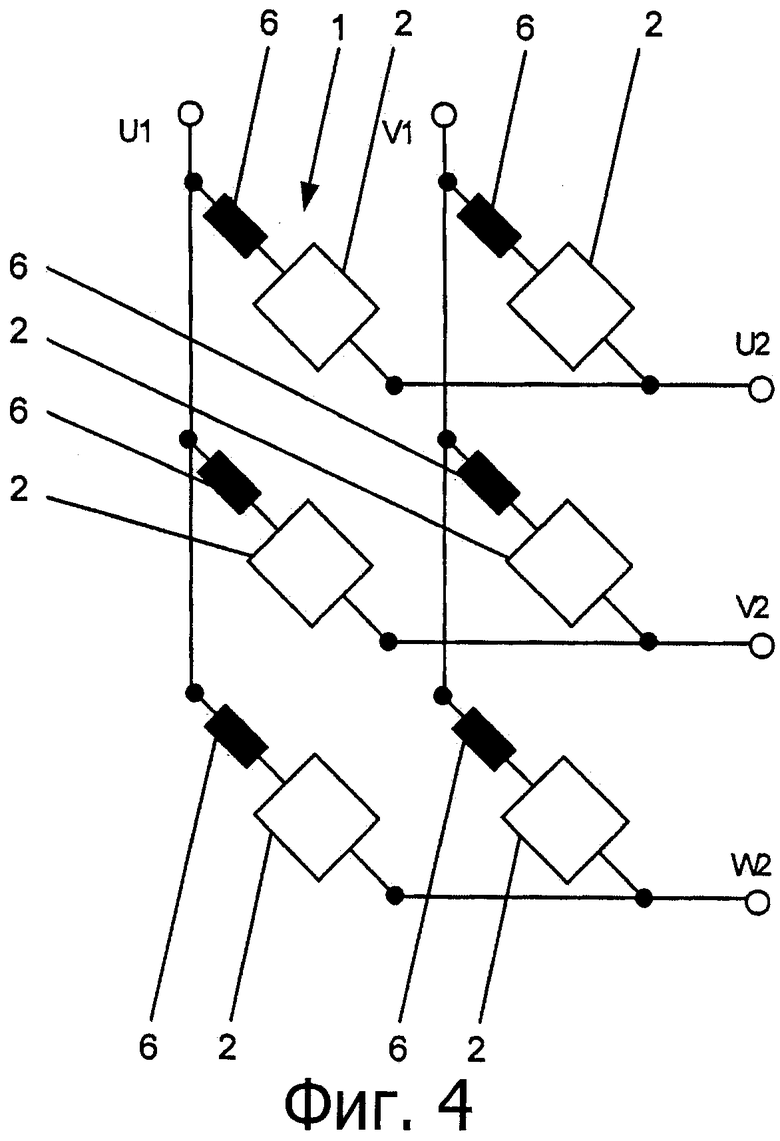

фиг.4 - второй вариант выполнения преобразовательной схемы, в частности, прямого преобразователя;

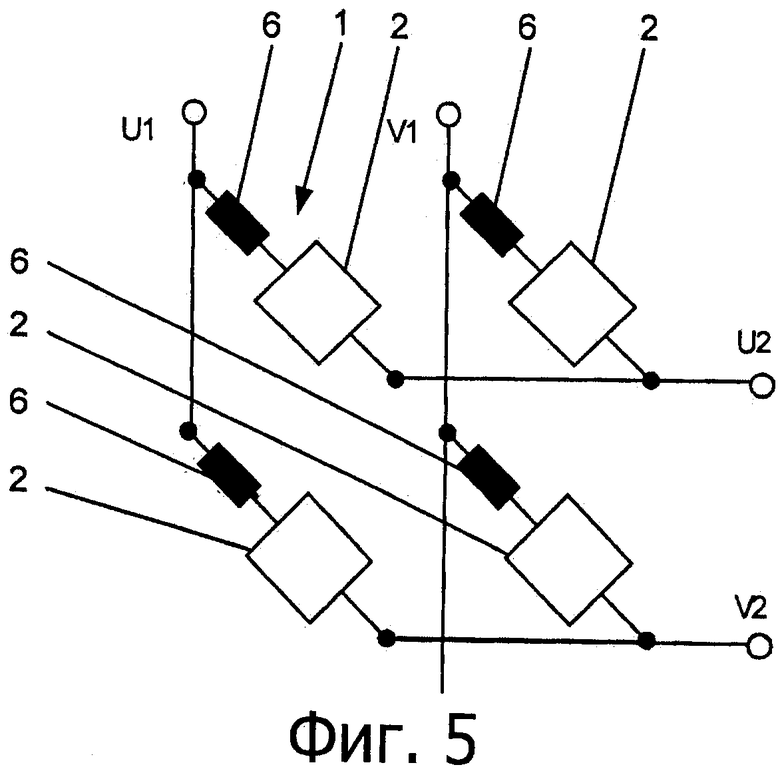

фиг.5 - третий вариант выполнения преобразовательной схемы, в частности, прямого преобразователя.

Указанные на чертежах позиции и их значения представлены в их перечне. В принципе одинаковые элементы на фигурах обозначены одинаковыми позициями. Описанные варианты выполнения являются примерами предмета изобретения и не имеют ограничивающего значения.

Осуществление изобретения

На фиг.1 представлен первый вариант выполнения устройства согласно изобретению для осуществления способа работы преобразовательной схемы согласно изобретению, при этом в целях большей наглядности на фиг.1 показан только один фазовый модуль 1 преобразовательной схемы, который подробнее описан ниже. Схема преобразователя, в частности прямого преобразователя, обеспечивающего преобразование входного напряжения или входного тока первой амплитуды непосредственно в выходное напряжение или выходной ток второй амплитуды и второй частоты, содержит, как правило, n входных фазовых выводов U1, V1, W1 и р выходных фазовых выводов U2, V2, W2, при этом n>2 и р>2. Кроме того, схема преобразователя, в частности прямого преобразователя, содержит n.р двухполюсных коммутационных ячеек для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, причем каждый выходной фазовый вывод U2, V2, W2 последовательно соединен с каждым входным фазовым выводом U1, V1, W1 соответственно через коммутационную ячейку 2. На фиг.3, в качестве примера, изображено такое последовательное соединение для схемы преобразователя с n=3 входных фазовых выводов U1, V1, W1 и р=3 выходных фазовых выводов U2, V2, W2. Кроме того, на фиг.4 показана схема преобразователя с n=2 входных фазовых выводов U1, V1, W1 и p=3 выходных фазовых выводов U2, V2, W2, на фиг.3 показана схема преобразователя с n=2 входных фазовых выводов U1, V1, W1 и р=2 выходных фазовых выводов U2, V2, W2. Как правило, каждая коммутационная ячейка 2 содержит управляемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии. Соответствующий управляемый силовой полупроводниковый ключ выполнен, в частности, в виде запираемого тиристора (GTO - Gate Turn-Off Thyristor) или в виде интегрированного тиристора с коммутирующим управляющим электродом (IGCT - Integrated Gate Commutated Thyristor) с соответственно встречно-включенным диодом. Однако также возможно выполнить управляемый силовой полупроводниковый ключ, например, в виде силового МОП-транзистора с дополнительным встречно-включенным диодом или в виде биполярного транзистора с изолированным затвором (IGBT) с дополнительным встречно-включенным диодом.

Согласно способу в каждом фазовом модуле 1 силовые полупроводниковые ключи коммутационных ячеек 2 управляются посредством управляющего сигнала S1. Управляющий сигнал S1 предпочтительно смещен по времени для каждой коммутационной ячейки 2, вследствие чего каждая коммутационная ячейка 2 может управляться предпочтительно со смещением по времени.

Согласно изобретению в каждую ветвь, т.е. в упомянутое выше соединение между выходным фазовым выводом U2, V2, W2 и входным фазовым выводом U1, V2, W2, подключена по меньшей мере одна индуктивность 6 через соответствующую двухполюсную коммутационную ячейку 2, причем коммутационная ячейка 2 образует вместе с такой индуктивностью 6 фазовый модуль 1, и для каждого фазового модуля 1 управляющий сигнал S1 формируется из опорного сигнала Vref.U1, в отношении напряжения U1 на фазовом модуле 1, и из сигнала VL напряжения на индуктивности 6. Кроме того, сигнал VL напряжения на индуктивности 6 формируется из промежуточного задаваемого значения ΔiU1 тока iU1 через фазовый модуль 1. Следовательно, промежуточное задаваемое значение ΔiU1 тока является промежуточной переменной. Индуктивность 6 в каждой линии последовательного соединения, т.е. в каждой ветви между входным фазовым выводом U1, V1, W1 и выходным фазовым выводом U2, V2, W2, предпочтительно позволяет регулировать напряжение посредством коммутационных ячеек 2 таким образом, что может обеспечиваться непрерывное протекание тока от входного фазового вывода U1, V1, W1 на выходной фазовый вывод U2, V2, W2, в результате чего возможно активное регулирование тока через соответствующую ветвь. Кроме того, схема преобразователя делает возможным почти любой обмен электрической энергией между отдельными ветвями. В результате того, что соответствующее промежуточное задаваемое значение ΔiU1 тока в соответствующем фазовом модуле 1 участвует в формировании сигнала VL напряжения через индуктивность 6 и, следовательно, в формировании соответствующего управляющего сигнала S1, то может быть обеспечено положение, при котором нежелательные циркулирующие токи могут быть уменьшены в фазовом модуле 1 преобразовательной схемы или же сведены к нулю. Предпочтительно, чтобы указанные выше операции не приводили к нежелательным изменениям токов iu на выходных фазовых выводах U2, V2, W2 фазовых модулей 1, т.е. не должно оказываться нежелательное воздействие на токи iu. Кроме того, можно эффективно или точно задавать воздействие необходимых для регулирования циркулирующих токов на токи iu на выходных фазовых выводах U2, V2, W2.

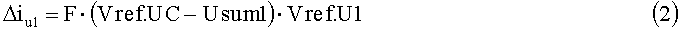

Для формирования сигнала VL напряжения на индуктивности 6 применяется следующая формула:

Следовательно, посредством фазового модуля 1 обеспечивается как бы предварительное управление током iu1.

Согласно фиг.1 каждая коммутационная ячейка 2 содержит, например, четыре двунаправленных силовых полупроводниковых ключа с управляемым односторонним направлением прохождения тока, соединенных по мостовой схеме, в частности полной мостовой схеме, и емкостной накопитель энергии, параллельно подключенный к мостовой схеме силовых полупроводниковых ключей, при этом фазовый модуль 1, как правило, дополнительно содержит по меньшей мере одну подключенную к линии последовательного соединения двухполюсную коммутационную ячейку 2 для коммутирования по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, при этом на фиг.1 в качестве примера показаны четыре коммутационных ячейки фазового модуля 1. Возможны также двухполюсные коммутационные ячейки 2, которые, как правило, выполнены в виде многоуровневых схем и могут коммутировать по меньшей мере одно положительное и по меньшей мере одно отрицательное напряжения между полюсами. Посредством упомянутого выше, практически любого обмена электрической энергией между отдельными ветвями и, следовательно, между отдельными коммутационными ячейками 2 становится возможным передавать в схеме преобразователя, в частности прямого преобразователя, большие количества электрической энергии, емкостные накопители энергии коммутационных ячеек 2 могут быть выполнены предпочтительно соответственно малого размера, что позволяет существенно уменьшить занимаемую площадь и заметно снизить затраты по сравнению с известными прямыми преобразователями. В результате системы с такими преобразовательными схемами могут занимать меньше места и быть соответственно не дорогостоящими. Кроме того, все фазовые модули 1 образуют в любое время замкнутые цепи напряжения. Возможные различия по напряжению между отдельными коммутационными ячейками 2 сглаживаются индуктивностью 6. Одновременно непрерывные токи через индуктивности 6 обеспечивают никогда не прерывающийся ток на выходных фазовых выводах U2, V2, W2 фазовых модулей 1.

Согласно не показанному в целях наглядности варианту выполнения схемы преобразователя, выполненного, в частности, в виде прямого преобразователя, к каждой линии последовательного соединения подключена по меньшей мере одна дополнительная двухполюсная коммутационная ячейка 2 для коммутирования по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, в результате чего коммутируемое напряжение, т.е. напряжение на всей линии последовательного соединения между входным фазовым выводом U1, V1, W1 и выходным фазовым выводом U2, V2, W2 может быть эффективно увеличено. Также возможно, чтобы к каждой коммутационной ячейке 2 была подключена по меньшей мере одна дополнительная двухполюсная коммутационная ячейка 2, выполненная, например, как описано выше, для параллельного коммутирования по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами. В результате может быть эффективно обеспечен более значительный ток, т.е. повышенная несущая способность по току, через всю линию последовательного соединения между входным фазовым выводом U1, V1, W1 и выходным фазовым выводом U2, V2, W2. Также возможно, чтобы к каждой линии последовательного соединения коммутационной ячейки 2 по меньшей мере с одной индуктивностью 6 была параллельно подключена по меньшей мере одна дополнительная линия последовательного соединения двухполюсной коммутационной ячейки 2 для коммутирования по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжения между полюсами по меньшей мере с одной дополнительной индуктивностью 6.

В целях защиты в случае неисправности коммутационной ячейки 2 может быть параллельно подключен к каждой коммутационной ячейке 2 элемент замыкания цепи накоротко.

В помощью соответствующего промежуточного задаваемого значения ΔiU1 тока в соответствующем фазовом модуле 1, которое участвует в формировании сигнала VL напряжения на индуктивности 6 и, следовательно, в формировании управляющего сигнала S1, возможно эффективно обеспечить равным нулю среднее отклонение напряжения на емкостных накопителях энергии всех коммутационных ячеек 2 фазового модуля 1, соответствующего вышеуказанным вариантам фазового модуля 1 с несколькими коммутационными ячейками 2.

Для каждого фазового модуля 1, содержащего в соответствии с приведенными выше вариантами несколько коммутационных ячеек 2, промежуточное задаваемое значение ΔiU1 тока iU1 формируется на основе суммы Usum1 напряжений UC1 на емкостных накопителях энергии коммутационных ячеек 2 фазового модуля 1 и задаваемой величины Vref.UC суммарного напряжения. Это происходит по следующей формуле:

Если фазовый модуль 1 содержит только одну коммутационную ячейку 2, то, естественно, сумма Usuml будет соответствовать напряжению UC1 на емкостном накопителе энергии этой единственной коммутационной ячейки 2 фазового модуля 1.

В соответствии с формулой (2) промежуточное задаваемое значение ΔiU1 тока iU1 через фазовый модуль 1 дополнительно формируется с помощью задаваемой регулирующей функции F. Предпочтительно для регулирующей функции F выбирается пропорциональная характеристика, поэтому регулирующая функция F имеет, например, следующий вид:

F=К,

где К - коэффициент пропорциональности. Разумеется, в отношении регулирующей функции F может выбираться в общем любая регулирующая характеристика. Выбором регулирующей функции F может эффективно задаваться очень специфичная регулирующая характеристика, которая ориентирована, например, на определенное применение преобразовательной схемы.

Опорный сигнал Vref.U1 в отношении напряжения U1 на фазовых модулях 1 обычно формируется старшей системой регулирования для регулирования тока iu1 через соответствующий фазовый модуль 1, вследствие чего способ согласно изобретению является зависимым для регулирования тока.

Соответствующее изобретению устройство для осуществления способа работы преобразовательной схемы содержит для каждого фазового модуля 1 управляющую схему 3, предназначенную для формирования управляющего сигнала S1, причем управляющая схема 3 соединена с силовыми полупроводниковыми ключами коммутационной ячейки 2 фазового модуля 1. Согласно варианту выполнения на фиг.1 в фазовом модуле 1 с несколькими коммутационными ячейками 2 управляющая схема 3 соединена с силовыми полупроводниковыми ключами коммутационных ячеек 2 фазового модуля 1. Согласно изобретению в каждом фазовом модуле 1 для формирования управляющего сигнала S1 на управляющую схему 3 подается сумма из опорного сигнала Vref.U1 в отношении напряжения U1 на фазовом модуле 1 и сигнала VL напряжения на индуктивности 6. Кроме того, для каждого фазового модуля 1 предусмотрен первый вычислительный блок 4 для формирования сигнала VL напряжения на индуктивности 6 на основе промежуточного задаваемого значения ΔiU1 тока iU1 через фазовый модуль 1. Первый вычислительный блок 4 формирует сигнал VL напряжения на индуктивности 6, в частности, по формуле (1), на основе промежуточного задаваемого значения ΔiU1 тока iU1 через фазовый модуль 1.

Кроме того, согласно фиг.1 для каждого фазового модуля 1 предусмотрен второй вычислительный блок 5 для формирования промежуточного задаваемого значения ΔiU1 тока iU1 через фазовый модуль 1 на основе суммы Usum1 напряжений UC1 на емкостных накопителях энергии коммутационных ячеек 2 фазового модуля 1 и задаваемого значения Vref.UC суммарного напряжения, промежуточного задаваемого значения ΔiU1 тока iU1, при этом формируется промежуточное задаваемое значение ΔiU1 тока iU1 через фазовый модуль 1, в частности, по формуле (2).

Второй вычислительный блок 5 дополнительно формирует указанное промежуточное задаваемое значение ΔiU1 тока iU1 через фазовый модуль 1 на основе задаваемой регулирующей функции F, как это, в частности, видно из формулы (2).

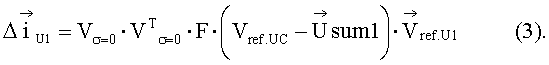

Альтернативный вариант выполнения устройства согласно изобретению на фиг.1 показан на фиг.2. В отличие от фиг.1 согласно альтернативному варианту выполнения на фиг.2 для всех фазовых модулей 1 предусмотрен общий первый вычислительный блок 4 для формирования сигнала VL напряжения на индуктивности 6 соответствующего фазового модуля 1 на основе промежуточного задаваемого значения ΔiU1 тока iU1 через фазовый модуль 1. Поэтому формирование сигналов VL напряжения на индуктивностях 6 фазовых модулей 1 проводится централизовано в единственном блоке. Как показано на фиг.2, для этой цели в общий первый вычислительный блок 4 вводятся суммы промежуточных задаваемых значений ΔiU1 тока iU1 через фазовые модули 1. В этом случае общий первый вычислительный блок 4 формирует сигнал VL напряжения на индуктивности 6 соответствующего фазового модуля 1 на основе соответствующей суммы промежуточных задаваемых значений ΔiU1 тока iU1 через соответствующий фазовый модуль 1. Общий первый вычислительный блок 4 формирует сигнал VL напряжения на индуктивности 6 соответствующего фазового модуля 1, в частности, по формуле (1).

Кроме того, согласно фиг.2 для всех фазовых модулей 1 предусмотрен общий второй общий вычислительный блок 5 для формирования промежуточного задаваемого значения ΔiU1 тока iU1 через все фазовые модули 1 на основе суммы Usum1 напряжений UC1 на емкостных накопителях энергии коммутационных ячеек 2 фазовых модулей 1 и задаваемого значения Vref.US суммарного напряжения, при этом промежуточное задаваемое значение ΔiU1 тока iU1 через фазовые модули 1 вычисляется, в частности, по формуле (3):

Таким образом, формирование токового промежуточного задаваемого значения ΔiU1 происходит централизовано в одном блоке. Необходимо упомянуть, что формула (3) представлена в виде векторного уравнения и промежуточные задаваемые значения ΔiU1 тока фазовых модулей 1 представляют собой элементы вектора

Общий второй вычислительный блок 5 формирует промежуточное задаваемое значение ΔiU1 тока iU1 через фазовые модули 1 на основе задаваемой регулирующей функции F, в частности, по формуле (3).

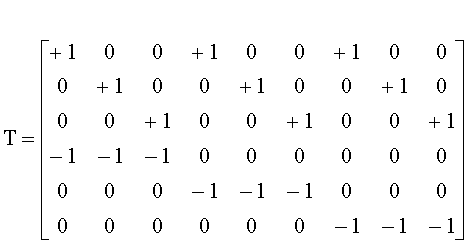

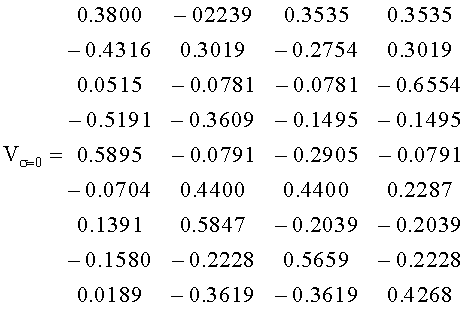

Согласно формуле (3) промежуточное задаваемое значение ΔiU1 тока iU1 через фазовый модуль 1 в каждом случае формируется в соответствии с указанным способом дополнительно на основе задаваемой развязывающей матрицы V, предназначенной для развязывания токов, циркулирующих через фазовые модули 1, от токов iU через выходные фазовые выводы U2, V2, W2. Сначала промежуточное задаваемое значение ΔiU1 тока отображается в подпространстве, ортогональном токам iU на выходных фазовых выводах U2, V2, W2 фазовых модулей 1, которые не подлежат изменению. Такое подпространство и необходимая для отображения развязывающая матрица V могут быть рассчитаны предварительно, например, на основе матрицы Т соединений, причем сингулярное разложение матрицы Т определяется как:

Т=UΣV*,

где: U - унитарная матрица, V* - сопряженная унитарной матрицы V и Σ - вещественная матрица, при этом все элементы матрицы Σ должны быть равны нулю вне главной диагонали. Vσ=0 являются столбцами в матрице V, для которой сингулярное число (соответствующий элемент в матрице Σ) равно нулю. Vσ=0 - указанные столбцы в развязывающей матрице V, которая является основанием для подпространства промежуточных задаваемых значений ΔiU1 тока, это подпространство ортогонально токам iu на выходных фазовых выводах фазовых модулей 1. Тогда VT σ=0 является транспонированной матрицей Vσ=0

Для преобразовательной схемы, в частности прямого преобразователя, например, на фиг.3, матрица Т соединений может быть представлена следующим образом:

Vσ=0 может быть представлено, например, следующим образом:

Вышеуказанное формирование промежуточных задаваемых значений ΔiU1 тока, соответствующее формуле (3), не вызывает изменения токов iu на выходных выводах фазовых модулей 1, т.е. на эти токи iu не оказывается воздействие.

Согласно фиг.2 общий второй вычислительный блок 5 формирует промежуточное задаваемое значение ΔiU1 тока iUi через фазовые модули 1 дополнительно на основе задаваемой развязывающей матрицы V, в частности, по формуле (3). Таким образом, промежуточные задаваемые значения ΔiU1 тока одновременно развязываются матрицей V.

В целом было показано, что изображенные на фигурах, в частности на фигурах 1 и 2, устройства согласно изобретению для осуществления способа работы преобразовательной схемы могут быть реализованы очень просто и не дорого, так как схемные затраты являются чрезвычайно низкими, при этом требуется только незначительное число компонентов для создания устройства. Таким образом, с помощью таких устройств особо просто осуществим способ, соответствующий изобретению.

Перечень позиций

1 фазовый модуль

2 коммутационная ячейка

3 управляющая схема

4 первый вычислительный блок

5 второй вычислительный блок

6 индуктивность

Изобретение относится к области электротехники и может быть использовано в преобразователях входного тока или входного напряжения. Технический результат - уменьшение нежелательных циркулирующих токов. В способе работы преобразовательная схема содержит n входных фазовых выводов (U1, V1, W1) и р выходных фазовых выводов (U2, V2, W2), где n≥2 и р≥2, (n-р) двухполюсных коммутационных ячеек (2) для коммутации, по меньшей мере, одного положительного и, по меньшей мере, одного отрицательного напряжений между полюсами. Каждый выходной фазовый вывод (U2, V2, W2) последовательно соединен с каждым входным фазовым выводом (U1, V1, W1) соответственно через коммутационную ячейку (2). Каждая коммутационная ячейка (2) содержит управляемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии; силовые полупроводниковые ключи коммутационных ячеек (2) управляются с помощью управляющего сигнала (S1). К каждому последовательному соединению подключена, по меньшей мере, одна индуктивность (6). Коммутационная ячейка (2) образует вместе с индуктивностью (6) фазовый модуль (1). Для каждого фазового модуля (1) формируется управляющий сигнал (S1) на основе опорного сигнала (Vref.U1) в отношении напряжения (U1) через фазовый модуль (1) и сигнала (VL) напряжения на индуктивности (6). Сигнал (VL) напряжения на индуктивности (6) формируется на основе промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовый модуль (1). 3 н. и 8 з.п. ф-лы, 5 ил.

1. Способ работы преобразовательной схемы, содержащей n входных фазовых выводов (U1, V1, W1) и р выходных фазовых выводов (U2, V2, W2), где n≥2 и р≥2, (n·р) двухполюсных коммутационных ячеек (2) для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, причем каждый выходной фазовый вывод (U2, V2, W2) последовательно соединен с каждым входным фазовым выводом (U1, V1, W1) через коммутационную ячейку (2), при этом каждая коммутационная ячейка (2) содержит управляемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии,

включающий управление силовыми полупроводниковыми ключами коммутационных ячеек (2) с помощью управляющего сигнала (S1),

отличающийся тем, что к каждому указанному последовательному соединению подключена по меньшей мере одна индуктивность (6), причем коммутационная ячейка (2) вместе с индуктивностью (6) образуют фазовый модуль (1), и для каждого фазового модуля (1) формируют управляющий сигнал (S1) на основе опорного сигнала (Vref.U1) в отношении напряжения (U1) на фазовом модуле (1) и сигнала (VL) напряжения на индуктивности (6), причем сигнал (VL) напряжения на индуктивности (6) формируют на основе промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовый модуль (1).

2. Способ по п.1, отличающийся тем, что каждая коммутационная ячейка (2) содержит четыре управляемых двунаправленных силовых полупроводниковых ключа с управляемым односторонним направлением прохождения тока, соединенных по мостовой схеме, и емкостной накопитель энергии, подключенный параллельно мостовой схеме силовых полупроводниковых ключей, при этом фазовый модуль (1) дополнительно содержит по меньшей мере одну двухполюсную коммутационную ячейку (2), включенную в указанное последовательное соединение, для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, при этом промежуточное задаваемое значение (ΔiU1) тока (iU1) через фазовый модуль (1) формируют на основе суммы (Usum1) напряжений (UC1) на емкостных накопителях энергии коммутационных ячеек (2) фазового модуля (1) и задаваемого значения (Vref.UC) суммарного напряжения.

3. Способ по п.2, отличающийся тем, что промежуточное задаваемое значение (ΔiU1) тока (iU1) через фазовый модуль (1) формируют дополнительно на основе задаваемой регулирующей функции (F).

4. Способ по п.3, отличающийся тем, что промежуточное задаваемое значение (ΔiU1) тока (iU1) через фазовый модуль (1) формируют дополнительно на основе задаваемой развязывающей матрицы (V), обеспечивающей развязывание токов, циркулирующих через фазовый модуль (1), от токов (iu) на выходных фазовых выводах (U2, V2, W2).

5. Устройство для осуществления способа работы преобразовательной схемы, которая содержит n входных фазовых выводов (U1, V1, W1) и р выходных фазовых выводов (U2, V2, W2), где n≥2 и р≥2, (n·р) двухполюсных коммутационных ячеек (2) для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, причем каждый выходной фазовый вывод (U2, V2, W2) последовательно соединен с каждым соответствующим входным фазовым выводом (U1, V1, W1) через коммутационную ячейку (2), при этом каждая коммутационная ячейка (2) содержит управляемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии,

содержащее управляющую схему (3), которая выполнена с возможностью генерировать управляющий сигнал (S1) и соединена с силовыми полупроводниковыми ключами коммутационных ячеек (2),

отличающееся тем, что к каждому указанному последовательному соединению подключена по меньшей мере одна индуктивность (6), причем коммутационная ячейка (2) вместе с индуктивностью (6) образуют фазовый модуль (1), при этом устройство выполнено с возможностью для каждого фазового модуля (1) сумму опорного сигнала (Vref.U1) в отношении напряжения (U1) на фазовом модуле (1) и сигнала (VL) напряжения на индуктивности (6) подавать на управляющую схему (3) для формирования управляющего сигнала (S1), причем устройство содержит для каждого фазового модуля (1) первый вычислительный блок (4) для формирования сигнала (VL) напряжения на индуктивности (6) на основе промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовый модуль (1).

6. Устройство по п.5, отличающееся тем, что каждая коммутационная ячейка (2) содержит четыре управляемых двунаправленных силовых полупроводниковых ключа с управляемым односторонним направлением прохождения тока, соединенных по мостовой схеме, и емкостной накопитель энергии, подключенный параллельно мостовой схеме силовых полупроводниковых ключей, причем фазовый модуль (1) дополнительно содержит по меньшей мере одну двухполюсную коммутационную ячейку (2), включенную в указанное последовательное соединение, для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, при этом устройство для каждого фазового модуля дополнительно содержит второй вычислительный блок (5), причем второй вычислительный блок (5) выполнен с возможностью формирования промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовый модуль (1) на основе суммы (Usum1) напряжений (UC1) на емкостных накопителях энергии коммутационных ячеек (2) фазового модуля (1) и задаваемого значения (Vref.UC) суммарного напряжения.

7. Устройство по п.6, отличающееся тем, что второй вычислительный блок (5) дополнительно выполнен с возможностью формировать промежуточное задаваемое значение (ΔiU1) тока (iU1) через фазовый модуль (1) на основе задаваемой регулирующей функции (F).

8. Устройство для осуществления способа работы преобразовательной схемы, которая содержит n входных фазовых выводов (U1, V1, W1) и р выходных фазовых выводов (U2, V2, W2), где n≥2 и р≥2, (n·р) двухполюсных коммутационных ячеек (2) для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, причем каждый выходной фазовый вывод (U2, V2, W2) последовательно соединен с каждым соответствующим входным фазовым выводом (U1, V1, W1) через коммутационную ячейку (2), при этом каждая коммутационная ячейка (2) содержит управляемые двунаправленные силовые полупроводниковые ключи с управляемым односторонним направлением прохождения тока и емкостной накопитель энергии,

содержащее управляющую схему (3), которая выполнена с возможностью генерировать управляющий сигнал (S1) и соединена с силовыми полупроводниковыми ключами коммутационных ячеек (2),

отличающееся тем, что к каждому указанному последовательному соединению подключена по меньшей мере одна индуктивность (6), причем коммутационная ячейка (2) вместе с индуктивностью (6) образуют фазовый модуль (1), при этом устройство выполнено с возможностью для каждого фазового модуля (1) сумму опорного сигнала (Vref.U1) в отношении напряжения (U1) на фазовом модуле (1) и сигнала (VL) напряжения на индуктивности (6) подавать на управляющую схему (3) для формирования управляющего сигнала (S1), причем устройство содержит для всех фазовых модулей (1) общий первый вычислительный блок (4) для формирования сигнала (VL) напряжения на индуктивности (6) соответствующего фазового модуля (1) на основе промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовый модуль (1).

9. Устройство по п.8, отличающееся тем, что каждая коммутационная ячейка (2) содержит четыре управляемых двунаправленных силовых полупроводниковых ключа с управляемым односторонним направлением прохождения тока, соединенных по мостовой схеме, и емкостной накопитель энергии, подключенный параллельно мостовой схеме силовых полупроводниковых ключей, причем фазовый модуль (1) дополнительно содержит по меньшей мере одну двухполюсную коммутационную ячейку (2), включенную в указанное последовательное соединение, для коммутации по меньшей мере одного положительного и по меньшей мере одного отрицательного напряжений между полюсами, при этом устройство для каждого фазового модуля дополнительно содержит общий второй вычислительный блок (5), причем общий второй вычислительный блок (5) выполнен с возможностью формирования промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовый модуль (1) на основе суммы (Usum1) напряжений (UC1) на емкостных накопителях энергии коммутационных ячеек (2) фазовых модулей (1) и задаваемого значения (Vref.UC) суммарного напряжения.

10. Устройство по п.9, отличающееся тем, что общий второй вычислительный блок (5) дополнительно выполнен с возможностью формирования промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовые модули (1) на основе задаваемой регулирующей функции (F).

11. Устройство по п.10, отличающееся тем, что общий второй вычислительный блок (5) дополнительно выполнен с возможностью формирования промежуточного задаваемого значения (ΔiU1) тока (iU1) через фазовые модули (1) на основе задаваемой развязывающей матрицы (V), обеспечивающей развязывание токов, циркулирующих по фазовым модулям (1), от токов (iu) на выходных фазовых выводах (U2, V2, W2).

| МАТРИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2004 |

|

RU2251199C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЯМОЙ СИЛОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2007 |

|

RU2379817C1 |

| DE 102005040543 A1, 01.03.2007 | |||

| US8144489 B2, 27.03.2012 | |||

| US 6900998 B2, 05.02.2004 | |||

| WO 2011082935 A1, 14.07.2011 | |||

Авторы

Даты

2015-01-10—Публикация

2010-11-12—Подача